Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Equi Ripple FIR Filter Design Paper

Caricato da

Chetan GowdaTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Equi Ripple FIR Filter Design Paper

Caricato da

Chetan GowdaCopyright:

Formati disponibili

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Design and Implementation of Equiripple FIR

Lowpass Filter on FPGA: A Case Study

Kaliprasanna Swain

Department of Electronics and Communication Engineering

G.I.T.A,Bhubaneswar,Odisha, India

Manoj Kumar Sahoo

Department of Electronics and Communication Engineering

G.I.T.A,Bhubaneswar,Odisha, India

Abstract- This paper demonstrates the design and implementation of Equiripple linear-phase FIR lowpass filter. The

filter is modeled using Simulink in Xilinx System Generator. The filter Coefficients are generated with the help of FDA

tools, and the System Generator tool is used for RTL code generation. Further the model is used as a filter block to

interface with ADC-DAC block in VHDL. The design has been prototyped on Spartan-3 DSP prototype board

XC3S500fg320 using Integrated Synthesis Environment (ISE) 13.1 tools all in one design suit from Xilinx. Finally the

filters are tested by using an audio signal as input and the output is observed in CRO & speaker both.

Keywords Equiripple Filter, FDA Tools, Simulink, Spartan-3, Xilinx System Generator, FPGA.

I. INTRODUCTION

The design of FIR filters using Windows methods leads to good performance filters. However, sometimes an FIR

filter needs to be designed which not only provides good performance, but also it should be optimal. Optimization is

the ability to specify a maximum error on each band of interest. This error is expressed as the absolute difference

between the ideal or the desired frequency response and the actual or resulting frequency response. One of the

techniques to design optimal FIR filters is to minimize a Chebyshev error criterion. The resulting filters are known

as Equiripple FIR filters.

To design a linear phase Equiripple FIR filter, the Parks-McClellan and Remez exchange methods are used. For

meeting the specific tolerance application Equiripple filters are mostly suited as it has equal ripple in both pass band

and stop band. In general, the modified Fourier Series [1] method is used where the passband frequency response is

monotonically decreasing and the maximum error is found at cutoff frequency.

But in this method, the error over the passband is spread out in an Equiripple fashion, such that at several points the

maximum error is same and error can be reduced. This method is called as the minimaxdesign or the Equiripple

design where the maximum error in the passband can be minimized.

p

s frequencies, ideal gains, and deviation (or

ripple) from the desired transfer function [2]. In terms of ripples, the transition band is most often assumed to be

arbitrary. An Equiripple FIR is a special class of FIR filter which is particularly effective in meeting such

specifications. The maximal deviations (ripple error) from the ideal transfer function are minimized by an Equiripple

design protocol. The Equiripple algorithm applies to a number of FIR design instances. The Magnitude response of

an Equiripple Lowpass filter is shown in Figure 1.

Vol. 5 Issue 2 March 2015

63

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Figure 1. Magnitude response of an Equiripple lowpass filter

II. PROPOSED MODEL

The digital filter can be designed by VHDL/Verilog HDL. In this case reconfiguration method is used so that the

design requires less time for any other application with minimum modification rather than fully structural recoding.

This design process FIRst the fixed floating number representation is realized,then converted to an integer based

representation which is more suitable for a hardware design process. The FPGA is preferred as a programmable

device than any DSP or microcontroller due to memory, speed of operation and flexible architecture. The proposed

model is given as in figure 2.

Figure 2. Purposed Model

.

III. FILTER IMPLEMENTATION TECHNOLOY

The details design flow of a DSP system using Xilinx System Generator FPGA is shown in figure 3. The following

implementation methodology is identified. Various steps [3] [4] according to flow graph are:

Vol. 5 Issue 2 March 2015

64

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Figure 3. Design flow for DSP system design on Xilinx FPGA

Step 1: Design the Filter using FDA tool.

The Filter Design and Analysis Tool (FDA Tool) is a powerful graphical user interface (GUI) in the Signal

Processing Toolbox for designing and analyzing digital filters of required specification. The different response

types such as highpass, lowpass, bandstop, differentiator, integrator etc. and different design methods such as IIR,

FIR are available to implement the filter. These windows can be customized by providing order of the filter, cutoff,

sampling, passband and stop-band frequencies and magnitude specifications. By quickly setting filter performance

specifications, by importing filters from MATLAB workspace or by adding, moving or deleting poles and zeros,

digital FIR and IIR filter can be designed using FDA tool. It can also be used for analyzing filters, such as

magnitude and phase response plots and pole-zero plots. Design specifications for Lowpass filter using FDA tool is

given in table 1.

Table -1 FDA tool specification

Response type

Order of filter

Passband Frequency, fp

Stopband frequency, fs

Sample frequency, fsamp

Density factor

Lowpass

120

5kHz

10kHz

250kHz

16

Step 2: Create Simulink Model

The Xilinx System Generator for DSP [5] [6] [7] is a system level modeling and design tool that facilitates

for Xilinx FPGA design and has the ability to work at a higher level of abstraction. It enables the use of the

Mathworks graphical model based Simulink design environment for FPGA design. The System Generator integrates

itself with Simulink and FPGA designs are captured by using the Xilinx specific Blockset. Thus, designing a

hardware model in Simulink is as simple as designing any other Simulink model with the only difference being the

use of Xilinx Blockset instead of those found in Simulink. The System Generator uses the Xilinx ISE software and

Xilinx IP cores generators to convert a designed model into the equivalent HDL code. The remaining FPGA

implementation steps, including synthesis, place and route, etc. are automatically performed to generate a bit file

that is downloaded onto the FPGA.

Vol. 5 Issue 2 March 2015

65

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Figur 4. Top module of lowpass filter using XSG

Figure 4 shows the top module of both the filter using Xilinx System Generator.

The gateway in blocks: The inputs into the Xilinx portion of the Simulink design considering as fixed point

data in binary format, Boolean and discrete type for a digital design.

The gateway out blocks: The outputs from the Xilinx portion of the Simulinkdesign, it manages all digital

data types with proper buffering.

FDA tools block: The FDA tool block is used for the frequency, order parameter passing and weight

generating interface with the fixed point environment which are used in later on implementation stages.

Xilinx System generator: Xilinx System generator (XSG) is the fixed point analysis environment which can

be used as integer based analysis, generation of RTL level of RTL code, co-hardware library and block for

a fix FPGA IC technology.

Step 3: Implement Simulink model with the help of MATLAB.

The FIR filter is tested with a signal and the response of the filter is observed in Scope block. Here, we

observe the floating point architecture, which helps to match the section given through FDA tools and later change

into fixed floating point architecture by using Gateway in/out in presence of XSG. Figue 5 has shown the

simulation result using Simulink.

Figure 5. Netlist generation of low pass filter

Step 4: Generate the code using Xilinx System Geneator

Vol. 5 Issue 2 March 2015

66

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Xilinx System Generator (XSG) as a code generator provides an equivalent synthesizable HDL code or

RTL code and the test-bench for design is created with respect to the clock speed of the board and process timing,

which is used as a component or sub-system in Xilinx ISE. The generation of the code depends on the block and

supported IP use in the design for an FPGA family and accordingly the structure of a design is built up and

interface. Fig.6 shows the code generated by XSG.

Figure 6. Netlist generation of low pass filter

Step 5: Simulate and debug the logic program and make necessary corrections to design of Step 3.

Step 6: Simulate and generate RTL schematic and check for resource utilization.

The logic program is simulated and debugged and necessary correction is made to meet the output and

further RTL schematic is generated and resource utilization is checked as shown in Fiure 7 and Figure 8.

Figure 7. Lowpass filter Simulation

Vol. 5 Issue 2 March 2015

67

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Figure 8. Lowpass RTL Design

Step 7: Run an automatic place and route program. This will place the logic block in appropriate places in FPGA

and then route the interconnection between logic blocks.

An automatic place and route program was run to place the logic block in appropriate places in FPGA and

then the interconnection between logic blocks were routed. Figure 9 and Figure 10 have shown the device summary

and the area utility for lowpass filter.

Figure 9. Lowpass device summary

Figure 10. Area utility figure showing the route path for lowpass filter

Step 8: Generation of Bit file and then programmed it and the implementation is carried by giving an audio signal

as input and the output is observed on a CRO and Speaker separately as shown in Figure 11.

Vol. 5 Issue 2 March 2015

68

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

Figure 11. Experimental Setup for passing the audio signal through the filter

IV. OBSERVATION

After the implementation is carried out on Spartan-3 DSP prototype board XC3S500fg320 using Integrated

Synthesis Environment (ISE) 13.1 tools, an audio signal is given as Input and the Output is observed on a CRO and

speaker separately as shown in experimental setup Figure 11 and Figure 12 and 13 have shown the result when the

audio signal is passed before and after the lowpass filter. By listening the output audio signal in speaker, we

observed that the low tonal peak is suppressed.

Figure 12. Input test audio signal directly observed in CRO before lowpass filtering

Figure 13. Output audio signal directly observed in CRO after lowpass filtering

V. CONCLUSION

Vol. 5 Issue 2 March 2015

69

ISSN: 2278-621X

International Journal of Latest Trends in Engineering and Technology (IJLTET)

This paper describes a step by step approach towards the design and implementation of Equiripple linearphase FIR lowpass filter using Simulink in Xilinx system generator. Subsequently, it is synthesized and

implemented on FPGA by using the VHDL language. It is revealed that the feasibility of designing process has

greatly increased by using Matlab toolbox FDA tools when calculating the filter coefficients. Simulation results

show that the FIR filter designed, fully complies with design requirements. The design is also tested by passing an

audio signal and performance of the filter is checked both by loud speaker and oscilloscope. The above design can

be modified or redesigned as an all pass digital filter with a single output mode or multi output mode.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

B. A. Shenoi, Introduction to digital signal processing and filter design, JOHN WILEY & SONS, INC., pp.280- 285, 2006

UweMeyer - Baese, Digital signal processing with field programmable gate arrays, 3rd ed., Tsinghua University Press, Beijing, pp. 175

177, 2007

B. Mamatha1, V.V.S.V.S. Ramachandram, Design and implementation of 120 order FIR filter based on FPGA, International Journal of

Engineering Sciences & Emerging Technologies, Vol. 3, Issue. 1, 2012.

H. V. Dixit, V. Gupta, IIR filters using Xilinx System Generator for FPGA Implementation, IJERA, Vol. 2, Issue 5, 2012.

ISE 13.2, Quick Start Tutorial, Xilinx.

Xilinx System Generator for DSP User Guide, r10.1.1, April 2008.

Nexys3 Board Reference Manual Revision: December 28, 2011, www.digilentinc.com

Vol. 5 Issue 2 March 2015

70

ISSN: 2278-621X

Potrebbero piacerti anche

- Design and Implementation of An Optimized Video Compression Technique Used in Surveillance System For Person Detection With Night Image EstimationDocumento13 pagineDesign and Implementation of An Optimized Video Compression Technique Used in Surveillance System For Person Detection With Night Image EstimationChetan GowdaNessuna valutazione finora

- 03 Point ProcessingDocumento62 pagine03 Point ProcessingChetan GowdaNessuna valutazione finora

- Verilog Quiz # 1Documento2 pagineVerilog Quiz # 1Chetan GowdaNessuna valutazione finora

- Question BankDocumento4 pagineQuestion BankChetan GowdaNessuna valutazione finora

- Lesson Plan-VLSI DesignDocumento6 pagineLesson Plan-VLSI DesignChetan GowdaNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Pw5 Transformer v1Documento5 paginePw5 Transformer v1Hairul Anuar MasrolNessuna valutazione finora

- Energy Conserrvation PresentationDocumento49 pagineEnergy Conserrvation PresentationshreemantiNessuna valutazione finora

- Vco-151215121140 Import PPTDocumento60 pagineVco-151215121140 Import PPTRizwan SPNessuna valutazione finora

- TM - 5ce - 2016Documento48 pagineTM - 5ce - 2016Jf OngNessuna valutazione finora

- CEF02N6: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocumento5 pagineCEF02N6: N-Channel Logic Level Enhancement Mode Field Effect TransistorAbel RodriguezNessuna valutazione finora

- Apple k94 Chopin 820-3069-A PCB PDFDocumento3 pagineApple k94 Chopin 820-3069-A PCB PDFJose Antonio Pool PootNessuna valutazione finora

- Solis Manual RHI (3-6) K 5G ENX V1,5Documento41 pagineSolis Manual RHI (3-6) K 5G ENX V1,5alessio “furiosbomba” lo medicoNessuna valutazione finora

- Distribution TransformerDocumento2 pagineDistribution Transformeranon_765971Nessuna valutazione finora

- HK SS Super Simples 50 - 60 - 70 - 80 A 200 ADocumento4 pagineHK SS Super Simples 50 - 60 - 70 - 80 A 200 Asindico440Nessuna valutazione finora

- D-Jet ECUDocumento39 pagineD-Jet ECUStanescu OctavianNessuna valutazione finora

- Banner S18UIADocumento9 pagineBanner S18UIAXavieltNessuna valutazione finora

- Multimag Cyble DN15 20 MID Brochure EnglishDocumento4 pagineMultimag Cyble DN15 20 MID Brochure EnglishdaskirNessuna valutazione finora

- Digital vs. Analog - Tait Radio AcademyDocumento3 pagineDigital vs. Analog - Tait Radio AcademySukhirthan SenthilkumarNessuna valutazione finora

- Diagrama Hydraulico Caterpillar 950 GCDocumento11 pagineDiagrama Hydraulico Caterpillar 950 GCJose PichinteNessuna valutazione finora

- (52621001078) DM - DM Half Inch Flex Jumper Spec SheetDocumento2 pagine(52621001078) DM - DM Half Inch Flex Jumper Spec SheetmicroqualNessuna valutazione finora

- Brochure SRT 4672 - enDocumento2 pagineBrochure SRT 4672 - enbejanNessuna valutazione finora

- Gerber P2C™ 600 User's ManualDocumento61 pagineGerber P2C™ 600 User's ManualSHER1303Nessuna valutazione finora

- DCS OverviewDocumento23 pagineDCS OverviewMaulana HidayatullahNessuna valutazione finora

- Hall Effect Pickup Ignition Controller: DIP16 SO16Documento11 pagineHall Effect Pickup Ignition Controller: DIP16 SO16SWNessuna valutazione finora

- Ece4010 Satellite-Communication TH 1.0 37 Ece4010Documento2 pagineEce4010 Satellite-Communication TH 1.0 37 Ece4010AYUSH GURTUNessuna valutazione finora

- Manual Newly CS-1600 30Documento20 pagineManual Newly CS-1600 30vijaaigNessuna valutazione finora

- 132 EC - A 10 - VIT - Chennai - Meggger & Multimeter - JE QTNDocumento4 pagine132 EC - A 10 - VIT - Chennai - Meggger & Multimeter - JE QTNDr. Chandan SharmaNessuna valutazione finora

- Dpi 150Documento4 pagineDpi 150Chirag SharmaNessuna valutazione finora

- Fan Wall Technology Versus Centrifugal FansDocumento3 pagineFan Wall Technology Versus Centrifugal FansWilliam Greco100% (1)

- High Power Rectifier Diodes - 5SYA 2029Documento9 pagineHigh Power Rectifier Diodes - 5SYA 2029Paola LainesNessuna valutazione finora

- Industrial Disaster ManagementDocumento68 pagineIndustrial Disaster ManagementMaheshchandra Yadav100% (1)

- Life Cycle Management of Power Transformers Using Transformer Protection RelayDocumento7 pagineLife Cycle Management of Power Transformers Using Transformer Protection RelaycuamiNessuna valutazione finora

- Wrong Answer SummaryDocumento3 pagineWrong Answer Summaryavishek mishraNessuna valutazione finora

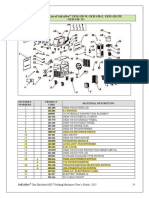

- 13.4. Spare Part List of Gekamac GKM 420-2GDocumento2 pagine13.4. Spare Part List of Gekamac GKM 420-2GBa MamadouNessuna valutazione finora

- Control Engineering Is Based On The Foundations of Feedback Theory and Linear System Analysis, and It GeneratesDocumento38 pagineControl Engineering Is Based On The Foundations of Feedback Theory and Linear System Analysis, and It GeneratesRajeev ValunjkarNessuna valutazione finora