Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Design and Development of Memory Management Unit For Mil-Std-1750 Processor

Caricato da

IAEME PublicationTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Design and Development of Memory Management Unit For Mil-Std-1750 Processor

Caricato da

IAEME PublicationCopyright:

Formati disponibili

International Journal of Electronics and Communication Engineering & Technology

(IJECET)

Volume 7, Issue 3, MayJune 2016, pp. 4652, Article ID: IJECET_07_03_006

Available online at

http://www.iaeme.com/IJECET/issues.asp?JType=IJECET&VType=7&IType=3

Journal Impact Factor (2016): 8.2691 (Calculated by GISI) www.jifactor.com

ISSN Print: 0976-6464 and ISSN Online: 0976-6472

IAEME Publication

DESIGN AND DEVELOPMENT OF

MEMORY MANAGEMENT UNIT FOR MILSTD-1750 PROCESSOR

Prasad. S.G and Dr Siva Yellampalli

VTU Extension Centre, UTL Technologies Limited, Bangalore, Karnataka, India

Naveen. V

Control and Digital Electronics Group, ISAC, Department of Space, Bangalore,

Karnataka, India

ABSTRACT

Processor Interface ASIC (PI ASIC) was widely used to provide processor

interface logics for MAR31750 Processor along with MA31751 Memory

Management Unit (MMU) chip. However with the diminishing availability of

MA31750 processors, use of the Mil-Std -1750 processor of Honeywell make

HX1750 as a replacement for the obsolete MAR 31750 Since HX-1750

processor does not have a compatible COTS MMU chip available, it was

decided to functionality of the existing MMU chip (MA31751) onto an FPGA

The remaining regular processor interface logics, similar to those in PI ASIC

are also housed inside the Processor Interface FPGA. Considering the

voluminous size of requirements, RTAX-1000S FPGA was chosen to

implement the processor interface logics. With a system clock of 24MHz and

an internal MMU inside the FPGA the cycle time for memory accesses has

considerably been reduced. The embedded SRAM blocks of the RTAX-1000S

FPGA are used as shared RAM between CPU and the 1553 device.

Key words: MMU, FPGA, ASIC, BPU

Cite this Article: Prasad. S. G, Dr Siva Yellampalli and Naveen. V, Design

and Development of Memory Management Unit for MIL-STD-1750

Processor, International Journal of Electronics and Communication

Engineering & Technology, 7(3), 2016, pp. 4652.

http://www.iaeme.com/IJECET/issues.asp?JType=IJECET&VType=7&IType=3

http://www.iaeme.com/IJECET/index.asp

46

editor@iaeme.com

Design and Development of Memory Management Unit for MIL-STD-1750 Processor

INTRODUCTION

A memory management unit (MMU), sometimes called (PMMU) paged memory

management unit. It is a computer hardware component for using accesses to memory

requested by the CPU. First performing the translation of virtual memory addresses to

physical addresses (i.e., virtual memory management), it is implemented as part of the

central processing unit, but it can also be in the form of a separate integrated circuit.

MMU is clearly performing the virtual memory management, bus arbitration, memory

protection, cache control and bank switchin.

ASIC VS FPGA

Table 1 PI ASIC versus PI FPGA

Processor Interface ASIC

Processor Interface FPGA

Designed for 12 MHz

Designed for 24 MHz

MMU external to ASIC

MMU to address up to 1M locations

Interface for Both Internal and External

Shared RAMs

Interface for Internal Shared RAM only

Employs existing EDAC for RAMs

Employs Core EDAC IP Core for Internal

RAM and existing EDAC for External RAM

Nature of Internal RAM : DP SRAM with

8K word of Memory

Nature of Internal RAM : SRAM with single

port, 8K word memory

I/O Decoding for some addresses not present

I/O Decoding for all I/O addresses present

EEPROM Interface logics absent

EEPROM Interface Logics provided

NEED FOR MMU

The HX-1750 processor can address a maximum of 64kB of memory through its

address lines which falls short of 1MB of memory observed on onboard. Thus, the

MMU caters to this need by providing extended addressing and making it possible for

the processor address 1 MB of memory.

DESIGN OF MMU

Memory Management Unit is implemented in RTAX-1000 FPGA. The design of

MMU is similar to that of the existing MA 31751 MMU chip [8]. The principal

function of memory management unit is to provide extended addressing to the

processor by means of address translation. The BPU of MA 31751 is not implemented

in the memory management unit design. The MMU module is designed only to

increase the memory addressing capability of the HX-1750 CPU.

The processor inputs the 16 bit Address (ADDR_VALID [15:0]) and the Address

State (AS [3:0]). The memory management unit performs address translation to output

the Physical Page Address which is referred to by Extended Address (EA [7:0]). The

extended 20 bit address is formed by the concatenation of EA [7:0] and the

ADDR_VALID [11:0] as shown in the figure 1.

http://www.iaeme.com/IJECET/index.asp

47

editor@iaeme.com

Prasad.S.G, Dr Siva Yellampalli and Naveen.V

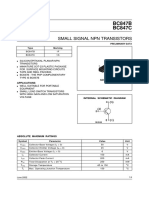

Figure 1 Generation of 20 bit Physical Address

The main memory (SRAM) is divided in to 256 pages of size 4kB each.

Therefore, the MMU may have an array of registers which contain the physical page

addresses (PPA) of all the pages available within the memory.

The MMU decodes the incoming processor address to classify the command as

either an operation on Instruction registers or Operand registers.

PAGE REGISTERS

The main memory is divided into 256 pages of 4k words each. The MMU maps the

system memory into these 4k word pages. A page is a block of physical page memory

which is uniquely specified by the PPA [3]. A given address within any page is

specified by the least significant twelve bits of the CPU address bus. Each page

register is 8 bit wide and contains the physical page address of a page in the main

memory. A total of 512 page registers divided into two groups of 256 registers each,

one dedicated for Instruction memory space and one for Operand memory space.

The MMU is initialized to provide a linear, one to one mapping of the PPA when

system reset occurs. The CPU may change the mapping when it is in privileged

instruction mode using XIO commands 5100 to 52FF as defined in MIL-STD-1750.

Two register banks, one for instruction and one for operand are created. Each bank is

implemented as an 8 bit word array of length 256.

Write Operation

The processor data is written into the specified 8 bit register address (REG_ADDR).

Write operation into the file registers occurs during the rising edge of the IOWR

(write clock (W_CLK)) and when the write enable (WE) is high.

Read Operation

Two 256 to 1 MUX are placed one outside each set of page registers (instruction and

operand page registers). Depending on the selection lines (REG_ADDR), the

http://www.iaeme.com/IJECET/index.asp

48

editor@iaeme.com

Design and Development of Memory Management Unit for MIL-STD-1750 Processor

multiplexer selects the content of required page register and relays it to the 2 to 1

multiplexer as show in figure 2. The 2 to 1 MUX selects between the signals

EA_INSTRUCTION and EA_OPERAND depending upon the selection line

REG_ADDR to output MMU_DATA_OUT. The data for processor read is always

available on EA [7:0]. The MMU data for processor read is routed to the processor

data bus in the data bus routing module when the enable MMU_DATA_CS is

activated.

Figure 2 Read/write logic on Page registers

Translation

Two 256 to 1 multiplexers are placed one outside each set of page registers

(instruction and operand page registers). Depending on the selection lines

(TRANS_ADR), the multiplexer selects the contents of required page register and

relays it to the 2 to 1 multiplexer. TRANS_ADR to the multiplexer is formed by the

concatenation of AS [3:0] and ADDR_VALID [3:0]. MMU_TRANS_PORT always

contains the contents of the register specified by TRANS_ADR.

MMU_TRANS_PORT is either EA_INSTRUCTION or EA_OPERAND depending

upon the bank which outputs MMU_TRANS_PORT.

The 2 to 1 multiplexer in the right hand corner [9]. Depending upon the value of

the selection line DI, either the EA_INSTRUCTION or the EA_OPERAND is

selected and relayed as the required EA [7:0] as an output of the memory management

unit module.

Identical to read, the translation operation is asynchronous. EA [7:0] is always

available outside the memory management unit module irrespective of any translation

enable. To make use of EA [7:0], the processor asserts the IOM signal to logic low.

The extended 20 bit address is formed by concatenation of EA [7:0] and the

ADDR_VALID [11:0].

http://www.iaeme.com/IJECET/index.asp

49

editor@iaeme.com

Prasad.S.G, Dr Siva Yellampalli and Naveen.V

SIMULATION AND RESULTS

The simulated results obtained using ModelSim simulator and the device utilization

obtained using Libero Microsemi.

The VHDL code for memory management unit module was simulated for all

combinations of Data, Address and Control signals.

Figure 3 Write operation timing waveform

Figure 4 Read operation timing waveform

http://www.iaeme.com/IJECET/index.asp

50

editor@iaeme.com

Design and Development of Memory Management Unit for MIL-STD-1750 Processor

Figure 5 the simulated result of the MMU

SL. No

Test case

Operand Register Read from Locations D200 to D2FF

Instruction Register Read from locations D100 to D1FF

Operand Register Write from Locations 5200 to 52FF

Instruction Register Write from Locations 5100 to 51FF

Operand Translation for TRANS_ADR values ranging from 00 to FF

Instruction Translate for TRANS_ADR values ranging from 00 to FF

Operand Register and Instruction Register Read with IOM =0

Operand and Instruction Translate with IOM=1

Table 2 List of FPGA Simulation Test Case

CONCLUSION AND FUTURE WORK

MMU for extending the 16 bit processor address to reference 1M words (20 bit

address) with the use of 256 Instruction and Operand page register each has been

designed, tested for implementation. This design work will optimize the board by

limiting the need for a dedicated memory management unit device and also helps to

tide over the obsolescence in the MIL-STD-1750 compatible MMU.

Microsemi RTAX1000S FPGA is used to realize the logics. Design and

implementation of the MMU will be done in Microsemis Libero environment using

VHDL language.

http://www.iaeme.com/IJECET/index.asp

51

editor@iaeme.com

Prasad.S.G, Dr Siva Yellampalli and Naveen.V

Future work can integrate the Block Protection Unit (BPU) for memory protection

into the design as with the case of the dedicated Memory Management Unit.

REFERENCES

[1]

ISRO ASIC /FPGA design and development guidelines.

[2]

John L. Hennsley and David A. Patterson, Computer Architecture A

quantitative approach, 2 edition Morgan Kaufmanns publishers inc. San

Francisco, California, 1996.

[3]

Memory management overview, Karl Ingstrm, Anders Daleby. Department of

Computer Engineering, University of Mlardalen, Sweden, 2001.

[4]

K.C. Chang, Digital Design & Modeling with VHDL & Synthesis IEEE

Computer society press.

[5]

Radiation-Hardended FPGAs Datasheet -Actel Corporation. See the Actel

website for the latest version of the datasheet. V3.1. Radiation-Hardened FPGAs.

Features www.actel.com/documents/RadHard_DS.pdf.

[6]

Processor Interface ASIC (PI-ASIC) design document.

[7]

Stefan Sjoholm, VHDL for Designers Pearson Prentice Hall.

[8]

MA31751 -User configurable, the MA31751 can perform as an MMU, a BPU or

both MMU and BPU, conforming to MA31751 devices can be used to give 16M

wordsoflogical.www.dynexsemi.com/assets/

SOS/Datasheets/DNX_MA31751_Jul02.pdf.

[9]

Operating system concepts, 4ed, A. Silberschatz and P.B Galvin, ISBN 0-20150480-4, 1994, Addison-Wesley.

[10]

J.K. Kishore, A memory management unit for satellite recovery experiment,

International Astronautical Congress 2007.

[11]

R. Revathi S. Sinthuja Dr. N. Manoharan and N. Rajendiran, Allocation of Power

in Relay Networks for Secured Communication, International Journal of

Advanced Research in Engineering & Technology, 6(8), 2015, pp. 135144.

[12]

Dhanya Pushkaran and Neethu Bhaskar, AES Encryption Engine for Many Core

Processor Arrays for Enhanced Security, International Journal of Electronics and

Communication Engineering & Technology, 5(12), 2014, pp. 106111.

http://www.iaeme.com/IJECET/index.asp

52

editor@iaeme.com

Potrebbero piacerti anche

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- (Edge) Multiple Choice Questions in Communications Engineering by Yu and CamachoDocumento98 pagine(Edge) Multiple Choice Questions in Communications Engineering by Yu and CamachoJohn Paulo Guerta Serrano80% (10)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- 11 Thyripol Main Project FileDocumento11 pagine11 Thyripol Main Project FileKirankumar Reddy100% (1)

- Transmitter Circuit Kit Ham Free Project Spy FM Bug How Do IDocumento7 pagineTransmitter Circuit Kit Ham Free Project Spy FM Bug How Do IanekwudohNessuna valutazione finora

- Analog IC Layout Services 1v2Documento14 pagineAnalog IC Layout Services 1v2KumarNessuna valutazione finora

- A Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiDocumento16 pagineA Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiIAEME PublicationNessuna valutazione finora

- How To Design A BGADocumento11 pagineHow To Design A BGAjackNessuna valutazione finora

- Voltage Control Gyanendra Sharma Npti DelhiDocumento56 pagineVoltage Control Gyanendra Sharma Npti DelhiNPTINessuna valutazione finora

- High Power CycloconverterDocumento7 pagineHigh Power Cycloconverternapster26Nessuna valutazione finora

- Re - 1991-10Documento100 pagineRe - 1991-10Anonymous kdqf49qbNessuna valutazione finora

- Impact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesDocumento10 pagineImpact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesIAEME PublicationNessuna valutazione finora

- Voice Based Atm For Visually Impaired Using ArduinoDocumento7 pagineVoice Based Atm For Visually Impaired Using ArduinoIAEME PublicationNessuna valutazione finora

- Broad Unexposed Skills of Transgender EntrepreneursDocumento8 pagineBroad Unexposed Skills of Transgender EntrepreneursIAEME PublicationNessuna valutazione finora

- A Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaDocumento9 pagineA Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaIAEME PublicationNessuna valutazione finora

- Modeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyDocumento14 pagineModeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyIAEME PublicationNessuna valutazione finora

- A Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurDocumento7 pagineA Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurIAEME PublicationNessuna valutazione finora

- Various Fuzzy Numbers and Their Various Ranking ApproachesDocumento10 pagineVarious Fuzzy Numbers and Their Various Ranking ApproachesIAEME PublicationNessuna valutazione finora

- Influence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiDocumento16 pagineInfluence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiIAEME PublicationNessuna valutazione finora

- A Multiple - Channel Queuing Models On Fuzzy EnvironmentDocumento13 pagineA Multiple - Channel Queuing Models On Fuzzy EnvironmentIAEME PublicationNessuna valutazione finora

- Application of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDDocumento19 pagineApplication of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDIAEME PublicationNessuna valutazione finora

- EXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESDocumento9 pagineEXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESIAEME PublicationNessuna valutazione finora

- Attrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesDocumento15 pagineAttrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesIAEME PublicationNessuna valutazione finora

- Role of Social Entrepreneurship in Rural Development of India - Problems and ChallengesDocumento18 pagineRole of Social Entrepreneurship in Rural Development of India - Problems and ChallengesIAEME PublicationNessuna valutazione finora

- Financial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelDocumento9 pagineFinancial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelIAEME PublicationNessuna valutazione finora

- Analysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsDocumento13 pagineAnalysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsIAEME PublicationNessuna valutazione finora

- Knowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentDocumento8 pagineKnowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentIAEME PublicationNessuna valutazione finora

- Optimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsDocumento13 pagineOptimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsIAEME PublicationNessuna valutazione finora

- Moderating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorDocumento7 pagineModerating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorIAEME PublicationNessuna valutazione finora

- Dealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsDocumento8 pagineDealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsIAEME PublicationNessuna valutazione finora

- Analysis On Machine Cell Recognition and Detaching From Neural SystemsDocumento9 pagineAnalysis On Machine Cell Recognition and Detaching From Neural SystemsIAEME PublicationNessuna valutazione finora

- A Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksDocumento10 pagineA Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksIAEME PublicationNessuna valutazione finora

- Sentiment Analysis Approach in Natural Language Processing For Data ExtractionDocumento6 pagineSentiment Analysis Approach in Natural Language Processing For Data ExtractionIAEME PublicationNessuna valutazione finora

- A Review of Particle Swarm Optimization (Pso) AlgorithmDocumento26 pagineA Review of Particle Swarm Optimization (Pso) AlgorithmIAEME PublicationNessuna valutazione finora

- A Overview of The Rankin Cycle-Based Heat Exchanger Used in Internal Combustion Engines To Enhance Engine PerformanceDocumento5 pagineA Overview of The Rankin Cycle-Based Heat Exchanger Used in Internal Combustion Engines To Enhance Engine PerformanceIAEME PublicationNessuna valutazione finora

- Formulation of The Problem of Mathematical Analysis of Cellular Communication Basic Stations in Residential Areas For Students of It-PreparationDocumento7 pagineFormulation of The Problem of Mathematical Analysis of Cellular Communication Basic Stations in Residential Areas For Students of It-PreparationIAEME PublicationNessuna valutazione finora

- Quality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceDocumento7 pagineQuality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceIAEME PublicationNessuna valutazione finora

- Prediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsDocumento13 paginePrediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsIAEME PublicationNessuna valutazione finora

- Ion Beams' Hydrodynamic Approach To The Generation of Surface PatternsDocumento10 pagineIon Beams' Hydrodynamic Approach To The Generation of Surface PatternsIAEME PublicationNessuna valutazione finora

- Evaluation of The Concept of Human Resource Management Regarding The Employee's Performance For Obtaining Aim of EnterprisesDocumento6 pagineEvaluation of The Concept of Human Resource Management Regarding The Employee's Performance For Obtaining Aim of EnterprisesIAEME PublicationNessuna valutazione finora

- Model QP-Physics For Electrical StreamDocumento3 pagineModel QP-Physics For Electrical StreamBruce LeeNessuna valutazione finora

- H Series An ManualDocumento5 pagineH Series An ManualraduldelNessuna valutazione finora

- Pub QuizDocumento4 paginePub QuizVan YangNessuna valutazione finora

- LICADocumento184 pagineLICAgkk001Nessuna valutazione finora

- PS410 Subwoofer: Service ManualDocumento19 paginePS410 Subwoofer: Service ManualAudio TecnologiaNessuna valutazione finora

- EMC For Dummies e News FinalDocumento26 pagineEMC For Dummies e News FinalWilson MartinezNessuna valutazione finora

- USB 1208 Series 1408FS DataDocumento9 pagineUSB 1208 Series 1408FS DataajayikayodeNessuna valutazione finora

- Electromagnetic InductionDocumento16 pagineElectromagnetic InductionOyeleke Oyekanmi0% (1)

- Cat Logo Parte 4 PDFDocumento4 pagineCat Logo Parte 4 PDFbird31Nessuna valutazione finora

- JBX-6300FSe2 12P 0329Documento6 pagineJBX-6300FSe2 12P 0329johnNessuna valutazione finora

- CATÁLOGOS Painel Fotovoltaico Alto Rendimento WURTH SOLAR WS11002 12V 12WDocumento4 pagineCATÁLOGOS Painel Fotovoltaico Alto Rendimento WURTH SOLAR WS11002 12V 12WRui HenriquesNessuna valutazione finora

- Manual Spirax Sarco Sx80Documento106 pagineManual Spirax Sarco Sx80armani_crupierNessuna valutazione finora

- CIL Coal India MT Electrical Question Paper For Management Trainees ExamDocumento7 pagineCIL Coal India MT Electrical Question Paper For Management Trainees ExamAshish Mahapatra100% (1)

- Digital Aud 25 A 1200WDocumento9 pagineDigital Aud 25 A 1200Wqlx4Nessuna valutazione finora

- V270SDocumento2 pagineV270SlainstanNessuna valutazione finora

- Samsung k15d ChassisDocumento38 pagineSamsung k15d ChassispahacerNessuna valutazione finora

- Characterization and Temperature-Dependent Conductivity of PolyanilineDocumento7 pagineCharacterization and Temperature-Dependent Conductivity of PolyanilineBianca Beatrice BaștiureaNessuna valutazione finora

- BOSCHDocumento3 pagineBOSCHU287Nessuna valutazione finora

- OSID Data SheetDocumento2 pagineOSID Data SheetRahul DevaNessuna valutazione finora

- FGM Fabrication TechniquesDocumento8 pagineFGM Fabrication Techniquesडॉ. कनिष्क शर्माNessuna valutazione finora

- Laboratory Report Cover SheetDocumento6 pagineLaboratory Report Cover SheetPre DatorNessuna valutazione finora

- DatasheetDocumento4 pagineDatasheetsergioNessuna valutazione finora