Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Rectifiers Experiment

Caricato da

Ali BaigCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Rectifiers Experiment

Caricato da

Ali BaigCopyright:

Formati disponibili

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

1. Experiment No.:

EC (EE) 391/01

2. Name of the Experiment:

Study of Ripple and Regulation characteristics of full wave

rectifier with and without capacitor filter

3. Objective of the Experiment:

To study of ripple and regulation characteristics of full wave

rectifier without and with capacitor filter

4. Working Principle:

Full Wave Rectifier (Without filter): CENTERTAP RECTIFIER:

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

1 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

Ripple factor:

Regulation:

The regulation indicates how D.C voltage varies as a function of load current. The percentage of

regulation is defined as

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

2 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

Ratio of rectification:

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

3 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

Full Wave Rectifier (With filter):

Here Xf should be smaller than RL . Because, current should pass through C and C should get

charge. If C value is very small, Xe will be large and hence current flows through R only and no

filtering action takes place. During +ve half cycle for a H W R circuit, with C filter, C gets

charged when the diode is conducting and gets discharged (when the diode is not conducting)

through RL. When the input voltage e = Em Sin rot is greater than the capacitor voltage, C gets

charged. When the input voltage is less than that of the capacitor voltage, C will discharge

through RL. The stored energy in the capacitor maintains the load voltage at a high value for a

long period. The diode conducts only for a short interval of high current. The waveforms are as

shown in Fig. .Capacitor opposes sudden fluctuations in voltage across it. So the ripple voltage is

minimized.

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

4 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

Center tap rectifier

Out put wave form

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

5 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

RIPPLE FACTOR FOR CAPACITOR FILTER:

Initially, the capacitor charges to the peak value V when the diode 0\ is conducting. When the

capacitor voltage is equal to the input voltage, the diode stops conduct or the current through the

diode 01 is zero. Now the capacitor starts discharging through RL depending upon the time

constant C.RL.Therefore, RL value is large. Rate of charging is different from rate of discharging.

When the voltage across the capacitor falls below the input voltage and when the diode 02 is

forward biased, the capacitor will again charge to the peak value Vm and the current through D2

becomes zero when Vc =Vm. Thus the diodes 01 and 02 conduct for a very short period 81 to 82

and 1t + 8 I to 1t + 82 respectively

OUT PUT WAVEFORM

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

6 of 10

WORK INSTRUCTION

Title:

Analog & Digital

Electronic Circuit Lab

ISO REF. 7.5.1

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

7 of 10

WORK INSTRUCTION

ISO REF. 7.5.1

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

5. Apparatus / Instruments Required:

Sl. No.

Item

Qty.

Makers Name

Range

6. Procedure for conducting the Experiment

i. Make the circuits as shown in figures.

ii. Full wave centre tap and full wave bridge rectifier (with & without filter for

each case).

iii. Connect the input & output terminals in dual trace CRO and observe the

waveforms. Now measure and record the output voltages and current Vdc, Vac,

and Idc and also record the input voltage Vrms from the secondary side of

transformer in loaded condition.

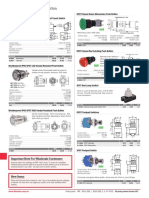

6.1. Circuit Diagrams

Without Filter:

D1

Vd

230V A.C

Supply

Vrms

Vrms

Rl

D2

Transformer

N.B. Full Wave Rectifier the transformer secondary must be centre tapped

Fig 1

With Filter:

Fig 2: Center tap rectifier

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

8 of 10

WORK INSTRUCTION

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

ISO REF. 7.5.1

6.2. Results:

Table 1:

Types of

Rectifier

V rms

volts

Vm=2

Vrms

In

Volt

Vdc

Volt

(theo)

Volt

(prac)

Idc

Vac

(Volts)

Ripple Factor

(mA)

theoretical

Full Wave

Centre tap

Ratio of Rectification

theoretical

practical

Vac/Vdc

0.48

2Vm/

Practical

Iac2 RL /

Irms2(RL+Rf)

.81

Table 2:

Percentage Error

Type of

rectifier

Output

Voltage

Rectification

Factor

Ripple Factor

Full Wave

Centre Tap

Table 3:

Sl.

No.

VFL(volt)

VNL(volt)

IL(mA)

% of voltage regulation

VNL-VFL/VFL*100%

7. Safety Precautions:

iv. Do not wear loose garments inside the laboratory.

v. Do not enter in the laboratory with the bare foots.

vi. Do not switch ON the circuits without permission of the concerned teacher.

vii. Do not touch the circuit haphazardly.

viii. Make sure that the circuit is switched OFF before leaving the laboratory.

8. Instructions for Writing the Report:

9

9

9

9

Title:

Analog & Digital

Electronic Circuit Lab

Attach the rough sheet with the final report.

The 1st Page of the report shall be as per the format shown in Annexure 1.

Write the final report as per the work instruction.

Draw the output voltage wave form as observed from CRO.

Prepared by:

SIC(s)

S.Mukherjee

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

9 of 10

WORK INSTRUCTION

NEOTIA INSTITUTE OF TECHNOLOGY,

MANAGEMENT AND SCIENCE

ISO REF. 7.5.1

ANNEXURE 1

NAME: ___________________________________________________________

ROLL NO.:_____________

DEPARTMENT: _____________________

DATE OF SUBMISSION: _________

DATE OF EXPERIMENT: _______

CO-WORKERS

NAME

ROLL NO.

1._______________________________

_________________

2._______________________________

_________________

3._______________________________

_________________

4._______________________________

_________________

TITLE:________________________________________________________________________

________________________________________________________________________

OBJECTIVE:

________________

Marks Obtained

Title:

Analog & Digital

Electronic Circuit Lab

Prepared by:

SIC(s)

S.Mukherjee

_________________

Signature of the

Sessional in - charge

Approved

by: HOD

Dr. A. Sil

Doc No.

Issue

No.

Revision

No.

Effective

Date

WI/EC(EE)391/01

01

00

17/07/12

Page

10 of

10

Potrebbero piacerti anche

- Cmos Co1 MaterialDocumento37 pagineCmos Co1 MaterialAli BaigNessuna valutazione finora

- K L University Department of Ece Computer Networks Lab Manual (15Cs2208) Python Basic ProgramsDocumento6 pagineK L University Department of Ece Computer Networks Lab Manual (15Cs2208) Python Basic ProgramsAli BaigNessuna valutazione finora

- The Difference Between Unicast, Multicast and Broadcast MessagesDocumento4 pagineThe Difference Between Unicast, Multicast and Broadcast MessagesAli BaigNessuna valutazione finora

- Network Layer Modified-15.09.2018Documento108 pagineNetwork Layer Modified-15.09.2018Ali BaigNessuna valutazione finora

- Aim: Write A Program To Find Out The Shortest Path Using Dijsktra Algorithm ProgramDocumento2 pagineAim: Write A Program To Find Out The Shortest Path Using Dijsktra Algorithm ProgramAli BaigNessuna valutazione finora

- Aim: Write A Program To Find Out The Shortest Path Using Dijsktra Algorithm ProgramDocumento2 pagineAim: Write A Program To Find Out The Shortest Path Using Dijsktra Algorithm ProgramAli BaigNessuna valutazione finora

- 19EC2105 ADC: Pulse Modulation SystemsDocumento33 pagine19EC2105 ADC: Pulse Modulation SystemsAli BaigNessuna valutazione finora

- Skills For Health OMS 2003 PDFDocumento90 pagineSkills For Health OMS 2003 PDFDiego WeinsteinNessuna valutazione finora

- Life Skills EducationDocumento40 pagineLife Skills EducationAli BaigNessuna valutazione finora

- Python Programming: Prerequisites Required Tools/PackagesDocumento2 paginePython Programming: Prerequisites Required Tools/PackagesAli BaigNessuna valutazione finora

- Life Skills EducationDocumento40 pagineLife Skills EducationAli BaigNessuna valutazione finora

- 521279S Multiratefiltering PDFDocumento25 pagine521279S Multiratefiltering PDFAejaz AamerNessuna valutazione finora

- 9 - Life Skills - Class - VIII PDFDocumento292 pagine9 - Life Skills - Class - VIII PDFStalin Ramesh100% (1)

- Welcom E: Communication Signals & Systems DesignDocumento7 pagineWelcom E: Communication Signals & Systems DesignAli BaigNessuna valutazione finora

- Cmos Co1 MaterialDocumento37 pagineCmos Co1 MaterialAli BaigNessuna valutazione finora

- Presentation MathDocumento20 paginePresentation MathAli BaigNessuna valutazione finora

- Life Skills: Dr.A.Srinath Professor & Hod-Me K L Deemed To Be UniversityDocumento40 pagineLife Skills: Dr.A.Srinath Professor & Hod-Me K L Deemed To Be UniversityAli BaigNessuna valutazione finora

- Ap PDFDocumento88 pagineAp PDFAnanth Nag Kumar VarreNessuna valutazione finora

- Amplitude ModulationDocumento30 pagineAmplitude ModulationAli BaigNessuna valutazione finora

- The 8051 Microcontroller and Embedded Systems Using Assembly and C PDFDocumento542 pagineThe 8051 Microcontroller and Embedded Systems Using Assembly and C PDFAli Baig67% (3)

- Income Tax Calculator FY 2017 18Documento11 pagineIncome Tax Calculator FY 2017 18Ali BaigNessuna valutazione finora

- True ALMDocumento12 pagineTrue ALMAli BaigNessuna valutazione finora

- Blooms Taxonomy Action Verbs-1Documento1 paginaBlooms Taxonomy Action Verbs-1api-238364969100% (1)

- PIC Microcontroller Architecture and ApplicationsDocumento8 paginePIC Microcontroller Architecture and ApplicationsAli Baig100% (1)

- Blockages To Service Sustainability of W PDFDocumento12 pagineBlockages To Service Sustainability of W PDFAli BaigNessuna valutazione finora

- Fiber Optic System Design-Step-byStepDocumento17 pagineFiber Optic System Design-Step-bySteptommishNessuna valutazione finora

- Notes From Wavelet Theory and ApplicationsDocumento14 pagineNotes From Wavelet Theory and ApplicationsAli BaigNessuna valutazione finora

- K P SomanDocumento177 pagineK P SomanMeetDaveNessuna valutazione finora

- Prototyping Scalable Smart Villages Final 030916Documento11 paginePrototyping Scalable Smart Villages Final 030916Ali BaigNessuna valutazione finora

- Multi Rate 1Documento22 pagineMulti Rate 1pra_zara2637Nessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (120)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Constructional Details of Poly Fuse: Poly Fuse-A Resettable Thermal Fuse - Electrical Seminar Topic With PPT Slide ShowDocumento3 pagineConstructional Details of Poly Fuse: Poly Fuse-A Resettable Thermal Fuse - Electrical Seminar Topic With PPT Slide Showsinu66Nessuna valutazione finora

- Half-Wave Rectifier: Electronic Devices and CircuitsDocumento22 pagineHalf-Wave Rectifier: Electronic Devices and Circuitsanon_376305376Nessuna valutazione finora

- 4265 FBDocumento22 pagine4265 FBSteve SmithNessuna valutazione finora

- Chapter 2Documento16 pagineChapter 2Aly AshrafNessuna valutazione finora

- Safety Operations On Medium Voltage SwitchgearDocumento8 pagineSafety Operations On Medium Voltage SwitchgearKamugasha KagonyeraNessuna valutazione finora

- Gemini-BPM500 PreampDocumento12 pagineGemini-BPM500 PreampAristoteles CarreñoNessuna valutazione finora

- A TV Pattern Generator Part1Documento4 pagineA TV Pattern Generator Part1riverajluizNessuna valutazione finora

- Electric and Hybrid Vehicles Design Fundamentals S... - (Chapter 9. Control of AC Machines)Documento26 pagineElectric and Hybrid Vehicles Design Fundamentals S... - (Chapter 9. Control of AC Machines)Iria LlausiNessuna valutazione finora

- Rly3-Ossd2: Safety RelaysDocumento6 pagineRly3-Ossd2: Safety RelaysTapir ConstantinoNessuna valutazione finora

- Duro-Test Lamp Catalog 1985Documento34 pagineDuro-Test Lamp Catalog 1985Alan Masters100% (2)

- Main/Reserve SwitchDocumento1 paginaMain/Reserve SwitchbaazizNessuna valutazione finora

- IRDH265Documento4 pagineIRDH265pukyssNessuna valutazione finora

- Electrical Machines Laboratory - HresDocumento60 pagineElectrical Machines Laboratory - HresFrancisco A Torres VNessuna valutazione finora

- 4 2 03Documento3 pagine4 2 03RotoniaNessuna valutazione finora

- Maltese Cross TubeDocumento18 pagineMaltese Cross TubeNiekey JohnNessuna valutazione finora

- Linde Service GuideDocumento5 pagineLinde Service GuideMário AndradeNessuna valutazione finora

- Rectifying CircuitsDocumento13 pagineRectifying Circuitssina981Nessuna valutazione finora

- Electronics 2 Lecture NotesDocumento13 pagineElectronics 2 Lecture NotesRex LeopardNessuna valutazione finora

- User Manual Sps SeriesDocumento28 pagineUser Manual Sps SeriesMe MeNessuna valutazione finora

- TD261, A Td262.a Td263ab Td264.a Td265.a Td266.a Td271.a Td272.a Td273.a.b Td274.a TD275, A TD276, ADocumento2 pagineTD261, A Td262.a Td263ab Td264.a Td265.a Td266.a Td271.a Td272.a Td273.a.b Td274.a TD275, A TD276, AZé Pontes DetCordNessuna valutazione finora

- Emergency Buttons CatalogDocumento1 paginaEmergency Buttons CatalogGokulakrishna RNessuna valutazione finora

- Inter-M QD4240 - QD4480 Operating ManualDocumento14 pagineInter-M QD4240 - QD4480 Operating ManualIgnacio Arias AriasNessuna valutazione finora

- Operating Instructions VAF32: Mechanical InstallationDocumento3 pagineOperating Instructions VAF32: Mechanical InstallationCông ThànhNessuna valutazione finora

- CB CatalogueDocumento79 pagineCB CatalogueXung Lệnh HồNessuna valutazione finora

- 2N5294 2N5296 2N5298 NPN Silicon Transistor DescriptionDocumento4 pagine2N5294 2N5296 2N5298 NPN Silicon Transistor DescriptionVenu Gopal Rao AggressNessuna valutazione finora

- Switch Amplifier KHA6-SH-Ex1: FunctionDocumento5 pagineSwitch Amplifier KHA6-SH-Ex1: FunctionandreNessuna valutazione finora

- Galaxy Electrical MMBD4148A/CA/CC/SE: Surface Mount Switching Diode FeaturesDocumento4 pagineGalaxy Electrical MMBD4148A/CA/CC/SE: Surface Mount Switching Diode Featuresmauricio alfonsoNessuna valutazione finora

- Schematic Diagram: MODEL: 32WL66A / 32WL66E / 32WL66R / 32WL66TDocumento38 pagineSchematic Diagram: MODEL: 32WL66A / 32WL66E / 32WL66R / 32WL66TSasha HesenliNessuna valutazione finora

- Main Panel: Agarwall VillaDocumento15 pagineMain Panel: Agarwall VillaEr.AROCKIA STEPHAN VSGNessuna valutazione finora

- RCF Approved ListDocumento53 pagineRCF Approved ListAmitabh Sharma50% (2)