Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Teo JK

Caricato da

RzOliveiraTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Teo JK

Caricato da

RzOliveiraCopyright:

Formati disponibili

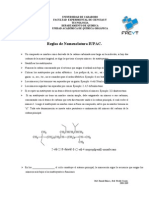

Introduccin al biestable JK

En el curso EloTrain-6 "Biestable JK" se deduce mediante su modo de

funcionamiento que en un biestable JK se excluye el estado

indeterminado.

Biestable JK

En el caso del biestable JK aqu empleado se trata de un componente

controlado por flanco nico.

(Tambin existen biestables controlados por los dos flancos y reciben la

denominacin de biestables JK maestro esclavo. Estos se abordan en el siguiente

ejercicio).

Las denominaciones "J" para la entrada de activacin y "K" para la de reset se han

elegido arbitrariamente (por tanto el nombre no tiene ninguna relacin con la

funcin, al contrario de lo que ocurre con el biestable RS). En ocasiones se emplea

"J" con el significado de "jump" y "K" con el de "kill", lo que tiene relacin con las

funciones de activacin y reset.

El biestable JK utilizado en los diagramas de montaje y del circuito del

curso EloTrain-6 solo posee la entrada esttica de activacin (set) S. La

entrada de reset esttica est siempre en el nivel bajo.

El componente 74 HC 112 aqu utilizado posee adicionalmente otras dos entradas

para la de activacin (J), reset (K) y de reloj (C), siendo estas las entradas

estticas de activacin (S) y reset (R).

Estas entradas estticas

(asncronas) S y R, al igual que la

entrada de reloj C, estn

invertidas (nivel LOW activo), es

decir, la funcin se activa en la

entrada mediante un nivel bajo.

La entrada de reloj reacciona

ante un flanco negativo (cambio

de la seal de reloj de nivel alto a

bajo).

Si se utiliza una configuracin

con mdulos mltiples (en este

caso doble) como es el caso del

74HC112, se agregan nmeros a

la identificacin para garantizar

una asignacin inequvoca.

Entradas de activacin y reset estticas:

Independientemente de las entradas J, K y C, es vlida la siguiente tabla de verdad:

Funcin

Entradas

Salidas

Activacin asncrona

Reset asncrono

Indeterminado (*)

por tanto, el biestable se activa con S=LOW y pasa al estado de reset con R=LOW.

Deben evitarse la aparicin de los estados S =LOW y R=LOW al mismo tiempo,

pues si tras este estado de operacin ambas entradas cambian simultneamente

de LOW a HIGH, el estado de salida de Q Y Q es imprevisible.

(*)

La respuesta del circuito integrado para este estado "prohibido" viene especificada

por el fabricante y puede variar.

Los circuitos integrados de Texas Instruments, Hitachi o STMicroelectronics

suponen para S=LOW y R=LOW los estados Q=HIGH y Q=HIGH.

Activacin y reset dinmicos:

En el caso de que las entradas de activacin y reset S y R tengan el nivel HIGH

(por tanto S y R LOW) es aplicable la siguiente tabla de verdad:

Funcin

Entradas

Salidas

Cambiar (toggle)

Reset (carga de "0")

Activacin (carga de "1")

Un cambio (memorizar)

: Flanco de bajada, cambio de nivel de alto a bajo de la seal de reloj C.

q : Valor en la salida Q antes del actual impulso de reloj C.

q : Valor en la salida Q antes del actual impulso de reloj C.

Contenidos de aprendizaje

Una vez realizado el ejercicio, los estudiantes estarn en condiciones de:

Describir el funcionamiento de un biestable JK controlado por un flanco

mediante su cronograma de seal en el tiempo.

Constatar que las entradas R o S pueden actuar independientemente de la

seal de reloj y de la asignacin de las entradas para aceptacin de datos (J y

K), por lo que son estticas.

Simplificar la tabla de verdad de un biestable JK controlado por un flanco y

reconocer los smbolos grficos normalizados.

Interconectar un biestable JK como un biestable D o T.

Requisitos

Para un exitoso aprendizaje del curso se requiere:

Elaborar tablas de verdad.

Conocimientos de circuitos bsicos.

Potrebbero piacerti anche

- SistemadetelecomunicacionenunentornoDocumento7 pagineSistemadetelecomunicacionenunentornopathtrakNessuna valutazione finora

- Cktos y Sus ElementosDocumento36 pagineCktos y Sus ElementosAnonymous lrrwBxUYNessuna valutazione finora

- APM Codigos de AveriaDocumento4 pagineAPM Codigos de AveriaPedro Ruiz Aguirre81% (21)

- Check List de Revisión de DiseñoDocumento11 pagineCheck List de Revisión de DiseñoYuly GómezNessuna valutazione finora

- Un Analisis Sobre Los Generadores en General Con Un Enfoque Sobre Los Generadores Que Se Encuentra A BordoDocumento23 pagineUn Analisis Sobre Los Generadores en General Con Un Enfoque Sobre Los Generadores Que Se Encuentra A BordoSebastian CurbeloNessuna valutazione finora

- Induccion Motorola ExpoDocumento27 pagineInduccion Motorola ExpoMire L. AvNessuna valutazione finora

- Laboratorio No 4Documento3 pagineLaboratorio No 4Diego MejíaNessuna valutazione finora

- Midiendo Intensidad de Luz Con LDRDocumento1 paginaMidiendo Intensidad de Luz Con LDRcarlos zetinoNessuna valutazione finora

- 8 - Audi Q7 - Caja de TransferenciaDocumento36 pagine8 - Audi Q7 - Caja de TransferenciaWaldino Aparicio100% (1)

- Teoria de Las Comunicaciones TDTDocumento40 pagineTeoria de Las Comunicaciones TDTeloy breña garciaNessuna valutazione finora

- Inspección VisualDocumento6 pagineInspección VisualProspero Alfonso Cumpa GuzmanNessuna valutazione finora

- Amplificador Estereo de 1000 WattsDocumento18 pagineAmplificador Estereo de 1000 Wattsmilton100% (1)

- Examen Electronica BasicaDocumento3 pagineExamen Electronica BasicaaugustoNessuna valutazione finora

- Respuesta en FrecuenciaDocumento80 pagineRespuesta en FrecuenciaRoberto MamaniNessuna valutazione finora

- Ceramicos y AsfaltoDocumento6 pagineCeramicos y AsfaltoJavier Pillaca CámaraNessuna valutazione finora

- Condutivmetro CM42 - OperaoDocumento40 pagineCondutivmetro CM42 - OperaoFelipeOliveiraNessuna valutazione finora

- Curso de InmovilizadoresDocumento100 pagineCurso de InmovilizadoresAnonymous Ek100RdbcH95% (22)

- Lista de Precios General Servicios CP Digital 2016 PDFDocumento3 pagineLista de Precios General Servicios CP Digital 2016 PDFedwan matheus morenoNessuna valutazione finora

- Practicas Del 19 Al 23 de PLC Siemens 1414 DC/DC/DCDocumento13 paginePracticas Del 19 Al 23 de PLC Siemens 1414 DC/DC/DCFirefallsNessuna valutazione finora

- Xm2100gtx EsDocumento2 pagineXm2100gtx EsSabrina HarrisNessuna valutazione finora

- Estos Son Los Conectores de Alimentación Tienen Los PortátilesDocumento8 pagineEstos Son Los Conectores de Alimentación Tienen Los PortátilesLOPEZ ROJALES ALBERTONessuna valutazione finora

- PilarejealgDocumento6 paginePilarejealgAlexander GF0% (1)

- Vizualisador Señal 4-20 Ma PRelectronics Lerbakken 10 DK-8410 Rode PDFDocumento25 pagineVizualisador Señal 4-20 Ma PRelectronics Lerbakken 10 DK-8410 Rode PDFMarcelo OlivaresNessuna valutazione finora

- Practica 2Documento7 paginePractica 2Ilse VarelaNessuna valutazione finora

- Revisión Diseño Electrico PolideportivoDocumento8 pagineRevisión Diseño Electrico Polideportivoignacio5173100% (1)

- Proceso de Anodizado Del AluminioDocumento13 pagineProceso de Anodizado Del AluminioLuisPa Flores100% (2)

- F.136 PTAR Trabajo EléctricoDocumento1 paginaF.136 PTAR Trabajo EléctricoMoises QuispeNessuna valutazione finora

- Configuracion Oscilador Interno de Pic 16f628aDocumento7 pagineConfiguracion Oscilador Interno de Pic 16f628aRomarys FigNessuna valutazione finora

- Reglas de Nomenclaturas IUPACDocumento4 pagineReglas de Nomenclaturas IUPACMaria Laura ManosalvaNessuna valutazione finora

- El Computador y Sus PartesDocumento8 pagineEl Computador y Sus PartesIU DigitalNessuna valutazione finora