Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Intro Pipe Lining

Caricato da

prashant94Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Intro Pipe Lining

Caricato da

prashant94Copyright:

Formati disponibili

Laundry Example

Ann, Brian, Cathy and Dave each

have one load of clothes to wash,

dry and fold

Pipelining

(Introduction)

CIT 595

Spring 2008

Washer takes 30 mins

Dryer takes 40 mins

Folder takes 20 mins

CIT 595

Sequential Laundry

Pipelined Laundry

Pipelined Laundry takes only 3.5 hours

Speedup = 6/3.5 = 1.7

Pipelining did not reduce completion time for one task but it helps the

throughput of the entire workload in turn decreasing the completion time

CIT 595

Entire workload takes 6 hours to complete

CIT 595

Instruction Level Pipelining

Instruction Level Pipelining: Big Picture

In instruction processing, each instruction goes

through

Each stage of the Instruction Processing Cycle takes 1 clock cycle

For each stage, one phase of instruction is carried out, and the stages

are overlapped

F->D->EA->OP->EX->S cycle

1 clock cycle = x time units per stage

The instruction cycle is divided into stages

One stage could contain more than one phase of the

instruction cycle or

one phase can be divided into two stages

If an instruction is in a particular stage of the cycle, the

rest of the stages are idle

We exploit this idleness to allow instructions to be executed in

parallel

Such parallel execution is called instruction-level pipelining

CIT 595

S1. Fetch instruction

S2. Decode opcode

S3. Evaluate Address

5

CIT 595

Theoretical Speedup due to Pipelining

theoretical speedup offered by a pipeline can be

determined as follows:

Let k be total number of stages and tp be the time per stage

Let n be the total number of tasks

The first task (instruction) requires k tp time to complete in a kstage pipeline.

The remaining (n - 1) tasks emerge from the pipeline one per

cycle

So the total time to complete the remaining tasks is (n - 1)tp

Theoretical Speedup due to Pipelining

The

S4. Fetch operands

S5. Execute

S6. Store result

If we take the time required to complete n tasks without a pipeline and

divide it by the time it takes to complete n tasks using a pipeline, we

find:

tn = k x tp

Thus, to complete n tasks using a k-stage pipeline requires:

If we take the limit as n approaches infinity, (k + n - 1) approaches n,

which results in a theoretical speedup of:

(k tp) + (n - 1)tp = (k + n - 1)tp

CIT 595

CIT 595

LC3 Hardwired Control (modified)

How Pipelining actually Implemented?

CONTROL

Since we are overlapping stages

All the control information plus data must be

remembered per instruction and must be carried through

each stage

This is achieved by placing a n-bit register that can

hold the control/data information in between each stage

Note: In this example only

instructions that can be performed

are the ones that update PC by 1

CIT 595

CIT 595

10

LC3 Pipelined Implementation

LC3 Pipelined Implementation

Data

Control

Evaluate Address and Execute are combined as they

both use ALU

S2/S3

S3/S4

S4/S5

S5/S6

CONTROL

Operand Fetch is separated into Register Fetch and

Memory Access

Store consists of only register writes

Memory Write is part of Memory Access

Thus we have a total of 6 stages

S1/S2

CIT 595

11

CIT 595

12

LC3 Pipelined Implementation

Impact on Clock Cycle due to Pipelining

Data

Control

The clock is sequencing the stages (instructions move

in lock step fashion)

S2/S3

S3/S4

S4/S5

S5/S6

CONTROL

Make sure that all work done in one stage gets done

on time before it moves to next stage

Hence, the clock cycle time should be as long as time

it takes through the longest pipe stage

This also includes the time for capturing data into registers in

between stages

Clock cycle time = max(t1,t2,t3,t4,t5,t6)

CIT 595

S1/S2

13

Impact on Clock cycle time due to Pipelining

CIT 595

14

Impact on Clock cycle time due to Pipelining

Recall

CPU Time =

time

program

time

=

cycle

Clock Cycle

time

cycles

instruction

CPI

instructions

program

5 stage

Instruction Count

10 stage clock cycle

time reduced by one half

If we lower the time per cycle, this will lower the

program execution time and hence improve performance

20 stage clock cycle

time reduced by one

fourth

This implies that we if we shorten the time per pipeline

stages, we will lower clock cycle time

This can be achieved by adding more pipe stages of

shorter duration

CIT 595

15

CIT 595

16

Cycles Per Instruction (CPI) with Pipelining

Why CPI is not always 1?

In pipelining, one instruction is in each stage

We assume that the pipeline can be kept filled at

all times

Since one instruction will be fetched (or finish) each

cycle, the average CPI will equal 1 (obviously we are

ignoring the very first instruction cold start)

However, this is not always the case

The situations that cause pipeline not to filled at all

times arises due to what is known as Pipeline

Hazards

CIT 595

However, CPI = 1 is barely achieved

17

CIT 595

18

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Simply Smart: P2500 SeriesDocumento2 pagineSimply Smart: P2500 SerieslamoladoNessuna valutazione finora

- USB Multi-Role Device Design by Example: John HydeDocumento121 pagineUSB Multi-Role Device Design by Example: John HydenandakishoreNessuna valutazione finora

- Lab Lecture-2Documento18 pagineLab Lecture-2ARIF ISHTEAKNessuna valutazione finora

- Adikavi Nannaya University: Unit-I TopicsDocumento139 pagineAdikavi Nannaya University: Unit-I TopicsHaritha rajeswari1810100% (1)

- English For Information Technology TEST 1 (Time: 90 Minutes)Documento30 pagineEnglish For Information Technology TEST 1 (Time: 90 Minutes)Lộc Ngô XuânNessuna valutazione finora

- Pivot3 Technology OverviewDocumento23 paginePivot3 Technology OverviewAdiNessuna valutazione finora

- Automated Enrollment SystemDocumento3 pagineAutomated Enrollment Systemlolo legaspiNessuna valutazione finora

- AEParts - HattelandDocumento4 pagineAEParts - HattelandFerdy Fer DNessuna valutazione finora

- TabletDocumento18 pagineTabletShruthi AnnappaNessuna valutazione finora

- Aikman Series Multiple Choice Questions CH# 1Documento9 pagineAikman Series Multiple Choice Questions CH# 1AdnanNessuna valutazione finora

- Activity Sheet 5.1 - Disassemble Computer SystemDocumento2 pagineActivity Sheet 5.1 - Disassemble Computer SystemLyssa BasNessuna valutazione finora

- DBS Puncher Order Guide 2021Documento1 paginaDBS Puncher Order Guide 2021Eric Parra OlivaresNessuna valutazione finora

- FANUC P/S Codes FANUC Program Errors (P/S Alarm)Documento15 pagineFANUC P/S Codes FANUC Program Errors (P/S Alarm)RISARALDA RISARALDANessuna valutazione finora

- SysReg XML A Profile-2023-12Documento6.170 pagineSysReg XML A Profile-2023-12davidcosmin98Nessuna valutazione finora

- Computer Practicals Assignment QuestionsDocumento2 pagineComputer Practicals Assignment Questionssudip kumarNessuna valutazione finora

- Dell PowerEdge R720 Spec SheetDocumento2 pagineDell PowerEdge R720 Spec SheetAdmaiNessuna valutazione finora

- Biography Bill GatesDocumento3 pagineBiography Bill GatesdadawqNessuna valutazione finora

- The Abstraction: Address Spaces: 13.1 Early SystemsDocumento9 pagineThe Abstraction: Address Spaces: 13.1 Early SystemsChrystian RodriguesNessuna valutazione finora

- ISPnub - Stand-Alone AVR in-System-Programmer Module - FischDocumento2 pagineISPnub - Stand-Alone AVR in-System-Programmer Module - FischNedim CurtNessuna valutazione finora

- 8.U-I. Input Output and Interrupt and RISC, CISC CharacteristicsDocumento23 pagine8.U-I. Input Output and Interrupt and RISC, CISC CharacteristicsJk RinkuNessuna valutazione finora

- SpindumpDocumento659 pagineSpindumpPFENessuna valutazione finora

- R. W. Marczytiski: Annals of The History of Computing Vol 2, No I JanuaryDocumento12 pagineR. W. Marczytiski: Annals of The History of Computing Vol 2, No I JanuaryGuldre1okkNessuna valutazione finora

- Sharp Digital Copiers Cross ReferenceDocumento4 pagineSharp Digital Copiers Cross ReferenceasdrefNessuna valutazione finora

- AssDocumento9 pagineAssJane SalvanNessuna valutazione finora

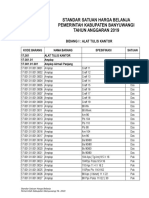

- Standart Harga 2019Documento515 pagineStandart Harga 2019Anonymous dWe4nB8cJhNessuna valutazione finora

- Concept Notes - Computer Lyst2449Documento234 pagineConcept Notes - Computer Lyst2449kasturi31391Nessuna valutazione finora

- VIMS History: SMCS - 7601Documento4 pagineVIMS History: SMCS - 7601lh100% (1)

- TrackMania Stadium Free Download IGGGAMESDocumento6 pagineTrackMania Stadium Free Download IGGGAMESkemas biruNessuna valutazione finora

- Forbes Marshall Arca Pvt. LTDDocumento1 paginaForbes Marshall Arca Pvt. LTDnagarajhebbarNessuna valutazione finora

- MPMC Course FileDocumento41 pagineMPMC Course FileKrishna ChaitanyaNessuna valutazione finora