Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

A Time-Domain Latch Interpolation Technique For

Caricato da

Sunil PandeyTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

A Time-Domain Latch Interpolation Technique For

Caricato da

Sunil PandeyCopyright:

Formati disponibili

A Time-domain Latch Interpolation Technique for

Low Power Flash ADCs

Jong-In Kim, Wan Kim, Barosaim Sung, and Seung-Tak Ryu

Department of EE, KAIST, Daejeon, Republic of Korea

Email : kji1308@kaist.ac.kr, stryu@ee.kaist.ac.kr

AbstractA Time-domain latch interpolation technique is

presented for low power flash analog-to-digital converter (ADC).

The proposed technique reduces the number of first stage latches

by half, and thus, reduce power consumption and hardware

complexity. A prototype 6bit 1GS/s flash ADC was designed for

concept proof in a 90nm CMOS process. The first stage

comparators are calibrated by adjusting body voltages. The ADC

core consumes 24mW at 1.2V supply. The measured INL and

DNL are 0.55LSB and 0.6LSB, respectively after calibration. The

SNDR and SFDR are 32.56dB and 43.53dB at 1GS/s with a

50MHz input.

I. INTRODUCTION

As emerging applications such as UWB and 60GHz WPAN

aim for high data-rate communication, ADCs for such systems

are required to have Giga hertz order sampling rate.

Traditionally, the most suitable ADC architecture for high

speed operation with low-to-medium resolution has been the

flash type. However, preamplifiers often required to relax the

effect of comparator offset and metastability increase the total

power consumption. In addition, the large input parasitic

capacitance by the preamplifiers has been a major drawback

for high-speed and low-power operation. One of the popular

design techniques for the above problem in flash ADCs is the

preamplifier interpolation scheme [1-3]. The technique

reduces the number of preamplifiers and generates the missing

information by interpolating the outputs of the two adjacent

preamplifiers. However, the static power consumption by the

preamplifiers, even though the number is reduced, is still the

major source of power consumption. Recently, several designs

have reported flash ADC structures that have no preamplifiers

[4-7]. However, the absence of the preamplifiers makes the

flash ADCs performance to be affected by comparator offset

serious. Thus, the preamplifier-less flash ADC often requires

complicated offset calibration scheme. In addition, even

though the offset problem could be solved in the preamplifierless structure, the kickback noise from the dynamic latch to

the input terminal and the reference ladder can seriously

degrade the signal integrity, which results in SNR degradation.

Thus, reduction of the number of latches will enhance the

circuit performance by reducing noise and power reduction.

In this paper, motivated by the discussion above, we propose

a time-domain latch interpolation technique to reduce the

number of dynamic comparators and to take many advantages

from it: reduced input capacitance, low power consumption,

less kickback noise, and reduced complexity for offset

calibration.

II. Time-domain Latch Interpolation Technique

Fig. 1 shows the representative schematic of the proposed

time-domain latch interpolation technique. It has a similar

structure to the preamplifier interpolation technique, but the

structure is composed of dynamic comparators (i.e. latches)

only. The first latch array, composed of L1 and L2, compares

the input signal (Vin) with their own references, Vref_k and

Vref_K+2. Note that one latch is missing between L1 and L2,

(a)

Fig. 1. Proposed time domain interpolation architecture.

978-1-4577-0223-5/11/$26.00 2011 IEEE

(b)

Fig. 2. Transient waveforms of Fig. 1.

(c)

which is supposed to compare V in with V ref_K+1 , where

Vref_K+1 is the center level of Vref_k and Vref_K+2. The latches in

the 2nd array (L4 - 6) amplify the outputs of the latches in the 1st

array. Latches are cascaded in three stages to compensate for

the insufficient time for latching, and thus, to reduce the

metastability problem as many designs do [3, 8]. CLK2 is a

delayed version of CLK1. L4 and L6 amplify the output of L1

and L2, respectively. L5 interpolates the outputs from L1 and

L2 and generates additional zero-crossing information by

utilizing the fact that the latching speed is logarithmically

proportional to the magnitude of the input difference [9].

Let us consider three different input cases to understand

the operational principle of the proposed technique: Vin = Vin1,

Vin2, and Vin3. When Vin = Vin1, where Vref_k > Vin > Vref_k+1,

the input to L1, Vin Vref_k, is negative and that to L2, Vin

Vref_k+2, is positive. Then, L1 regenerates its output to negative

direction (Vo1_k+ < Vo1_k-) and L2s output regenerates so that

Vo1_k+2+ > Vo1_k+2-. This operation is shown in Fig. 2(a). Since

|Vin Vref_k| < |Vin Vref_k+2|, the regeneration speed of L2 is

faster than that of L1 as Fig. 2(a) depicts. As long as the output

is in transition period (before they reach the digital level), the

two adjacent latches in the 1st array have difference in

amplitude at their output and the 2nd latch can interpolate them.

The input to the interpolation latch, L5, (VL5 > 0) is shown at

the lower part of Fig. 2(a). This results in L4 = 1, L5 = 1, and

L6 = 0. As a second case, when Vin = Vin2 = Vref_k+1, L1 and L2

will show identical output waveform, and thus, VL5 = 0 as Fig.

2(b) illustrates. This means that the interpolation latch (L5)

performs interpolation operation correctly as long as L1 and L2

generate correct outputs with negligible offsets. Similarly,

when Vin = Vin3 (Fig. 2(c)), the latches in the 1st array operate

oppositely to Fig. 2(a) and L4, L5, and L6 will produce 1, 0,

and 0, respectively.

III. Prototype 6-bit Flash ADC

A prototype 6bit flash ADC has been designed to verify

the proposed time-domain latch interpolation technique. The

structure is shown in Fig. 3. This ADC consists of an input

track-and-hold amplifier (THA), a resistor ladder, three stages

of latches with the proposed latch interpolation, a digital

encoder, calibration logic, and clock buffers.

A. Dynamic latch for the 1st stage

Fig. 4(a) shows the schematic of the proposed latch for the

use of the 1st stage. Compared with the popular conventional

structure shown in Fig. 4(b) [10], the proposed latch has an

additional NMOS latch to ground path. The additional latch

helps for the comparator to turn on fast from the reset phase

by discharging the output node faster than the conventional

design owing to the reduced number of stack. This also

enhances the latching time constant. The latches in 2nd and 3rd

stages have the conventional structure shown in Fig. 4(b). This

is due to the relaxed latching time constant requirement in

them owing to the amplified signal via the 1st stage. Note that

the input pair structure is simplified with a single differential

pair while the real design for the 1st stage latches and the

interpolation latches in the 2nd stage have two differential pairs

for input and references.

(a) Proposed

(b) Conventional[10]

Fig. 4. Dynamic latches used in this design.

Fig. 3. Block diagram of the prototype flash ADC.

B. Latch Offset Calibration

The functionality of the proposed time-domain latch

interpolation technique relies on low offset of the 1st latch

array. Thus, the first stage latches are calibrated by the body

voltage control method similarly to several previously

reported designs as [11, 12]. Fig. 5 shows the block diagram

of the offset calibration scheme and the timing diagram. It

shows a single row of the three stages of latches and the

simplified schematic of the 1st stages input pair. During

calibration mode, the inputs of 1st stage latches are shorted to

their own reference levels. Depending on the 3rd stages output,

the body voltage is adjusted by proper switching to the resistor

string. When the 3rd stages output changes its polarity, the

control logic stops and the control word is stored in the

registers. In this design, nine levels of reference were used for

calibration. Note that the latches in the 2nd stage do not require

offset calibration owing to large gain of the 1st stage. When

the input difference between L1 and L2 is about 1mV (about

0.1 LSB of the present design), VL5 was guaranteed to have

more than 50mV in all process corners. Another design

consideration for the proposed interpolation scheme is the

mismatch in latching time constant between L1 and L2:

different latching time constant of L1 and L2 will alter the

interpolation behavior shown in Fig. 2. However, the MonteCarlo simulation showed that the 1 sigma value of the inputreferred offset by the time constant mismatch (after the offset

calibration) was 1.3mV (about 1/8 LSB), and it was turned out

to be not significant.

C. Clock Delay Circuit

As Fig. 2 illustrates, the time period for time-domain

interpolation is limited to t_int because the outputs of the 1st

stage latches eventually reach full digital levels (supply or

ground), and then no interpolation is possible. Thus, it is

important to set the time difference between CLK1 and CLK2

so that VL5 is maximized and the offset of L5 can be ignored.

In the design, the delay amount was set using inverters and

capacitor loads. From the circuit level simulations, we have

found that the interpolation function is robust when the time

delay between CLK1 and CLK2 lies in the range of 40 - 110ps.

For test purpose, a variable clock delay circuit shown in Fig. 6

was integrated.

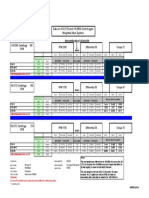

IV. Experimental Result

A prototype chip was implemented in a 90nm 1P9M

CMOS technology. The chip photo is shown in Fig. 7. The

ADC occupies 2.51mm2 of die area. The measured peak

DNL and INL are 0.6LSB and 0.55LSB, respectively after

calibration (Fig. 8). This proves that the proposed timedomain latch interpolation scheme along with the body

calibration works as expected. The FFT spectrum for low

frequency input (Fin = 50MHz) at 1GS/s sampling rate is

shown in Fig. 9. For measurement, the output data were

decimated by 1/16. The measured signal to noise and

distortion ratio (SNDR) and spurious free dynamic range

(SFDR) are 32.56dB and 43.53dB, respectively. The measured

SNDR and SFDR with respect to input frequency are shown in

Fig. 10. As the signal frequency increases, the performance

reduces and results showed that the input sampling network

had not enough bandwidth. The ADC core consumes 24mW at

1.2V supply. The ADC performance summary is presented in

Table I.

Fig. 7. Chip photo

Fig. 5. Calibration architecture and timing diagram

(a)

DNL

(b) INL

Fig. 8. Measured DNL and INL with and without calibration.

Fig. 6. Clock delay circuit & timing diagram.

flash ADCs. By utilizing the latching time difference between

two neighboring latches, interpolation function was

successfully implemented. A prototype 6 bit 1GS/s flash ADC

designed in 90nm CMOS proved the concept by measuring

peak DNL and INL to be 0.6LSB and 0.55LSB, respectively.

ACKNOWLEDGMENTS

Fig. 9. Measured FFT spectrum at 1GS/s with 50MHz input signal.

This work was supported by the IT R&D program of

MKE/KEIT [2009-S-025-01]. The CAD tools were supported

by IDEC of KAIST.

REFERENCES

SFDR

SNDR

Fig. 10. SNDR, SFDR vs. input frequencies at 1GS/s.

Table I. Performance Summary of Prototype ADC

Technology

90nm CMOS

Supply

1.2V

Resolution

6bit

Input Range (Differential)

0.6Vpp

Sampling Rate

0.4GS/s

1GS/s

Power Consumption

(excluding I/O, LVDS)

12mW

24mW

With Cal.

0.62/0.65LSB

0.6/0.55LSB

Without Cal.

2.12/4.03LSB

2.1/4.6LSB

SFDR

37.36dB@Nyquist

43.53dB@50MHz

SNDR

31.46dB@Nyquist

32.56dB@50MHz

ENOB

4.94b@Nyquist

5.17b@50MHz

FOM

0.97pJ/Conv-step

0.69pJ/Conv-step

DNL / INL

V. CONCLUSION

This paper proposed a time-domain latch interpolation

technique to reduce the number of dynamic comparators in

[1] R.E.J. van de Grift, I.W.J.M. Rutten, and M. van der Veen, An 8-bit video

ADC incorporating folding and interpolation techniques, IEEE J. Solid-State

Circuits, vol. 22, no.22, pp.944-953, Dec. 1987.

[2] K. Sushihara et al., A 6b 800MSample/s CMOS A/D Converter, IEEE

ISSCC Dig. Tech. Papers, pp. 428-429, Feb. 2000.

[3] K. Deguchi, N. Suwa, M. Ito, T. Kumamoto, and T. Miki, A 6bit 3.5GS/s

0.9V 98mW Flash ADC in 90nm CMOS, Dig. Symp. VLSI Circuits. pp.6465. June 2007.

[4] G. van der Plas S. Decoutere, and S. Donnay, A 0.16pJ/Conversion-Step

2.5mW 1.25GS/s 4b ADC in a 90nm Digital CMOS Process, IEEE ISSCC

Dig. Tech. Papers, pp. 566-567, Feb. 2006.

[5] B. Verbruggen, P. Wambacq, M. Kuijk, and G. Van der Plas, A 7.6 mW

1.75 GS/s 5b Flash A/D converter in 90nm digital CMOS, Dig. Symp. VLSI

Circuits, pp.14-15, June, 2008.

[6] H. Chung, A. Rylyakov, Z. T. Deniz, J. Bulzacchelli, G-Y. Wei, and D.

Friedman, A 7.5-GS/s 3.8-ENOB 52-mW flash ADC with clock duty cycle

control in 65nm CMOS, Dig. Symp. VLSI Circuits, 2009, p. 268269.

[7] J. Proesel, G. Keskin, J.-O. Plouchart, and L. Pileggi, An 8bit 1.5GS/s flash

ADC using post-manufacturing statistical selection, in Proc. IEEE CICC,

Sept. 2010.

[8] M. Choi, J. Lee, J. Lee, and H. Son. A 6-bit 5-GSample/s Nyquist A/D

Converter in 65nm CMOS. Dig. Symp. VLSI Circuits, pp. 16-17, June 2008.

[9] B. Razavi, Principles of Data Conversion System Design, New Work: IEEE

Press, 1995

[10] T. Kobayashi, K. Nogami, T. Shirotori, and Y. Fujimoto, A currentcontrolled latch sense amplifier and a static power-saving input buffer for

low-power architecture, IEEE J. Solid-State Circuits, vol. 28, pp. 523-527,

Apr. 1993.

[11] E. Alpman, H. Lakdawala, L.R. Carley, K. Soumyanath, A 1.1V 50mW

2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP Digital CMOS,

IEEE ISSCC Dig. Tech. Papers, pp. 65-77. Feb. 2009

[12] J. Yao, J. Liu, and H. Lee, Bulk Voltage Trimming Offset Calibration for

High-Speed Flash ADCs, IEEE Trans. Circuits Syst. II, vol. 57, pp. 101114,

Feb. 2010.

Potrebbero piacerti anche

- MSME-TECHNOLOGY CENTRE RECRUITMENTDocumento3 pagineMSME-TECHNOLOGY CENTRE RECRUITMENTSunil PandeyNessuna valutazione finora

- BSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Documento41 pagineBSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- PDIL Notice 12 08Documento12 paginePDIL Notice 12 08Manoj TyagiNessuna valutazione finora

- FACT Recruitment Notice 30 04 PDFDocumento17 pagineFACT Recruitment Notice 30 04 PDFSunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Documento8 pagineBSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Specialization - Test Paper - 2 - BSNL Je 2016Documento20 pagineBSNL Tta - Specialization - Test Paper - 2 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Documento41 pagineBSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- ECIL hiring Junior Technical Officer, ConsultantsDocumento7 pagineECIL hiring Junior Technical Officer, ConsultantsSandeep GoudNessuna valutazione finora

- HPCL GATE 2019 Advertisment PDFDocumento17 pagineHPCL GATE 2019 Advertisment PDFSunil PandeyNessuna valutazione finora

- BSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Documento8 pagineBSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE - Current Affairs - Test Paper - BSNL JE 2016Documento9 pagineBSNL TTA - JE - Current Affairs - Test Paper - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Documento8 pagineBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Documento9 pagineBSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Documento45 pagineBSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - Basic Engineering - Test Paper - BSNL Je 2016Documento21 pagineBSNL Tta - Je 2016 - Basic Engineering - Test Paper - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Documento45 pagineBSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta 2016 - GK & English - Test Paper - BSNL Je 2016Documento12 pagineBSNL Tta 2016 - GK & English - Test Paper - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Documento9 pagineBSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDocumento8 pagineBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyNessuna valutazione finora

- Network, Filters and Transmission Lines - BSNL JE 2016Documento8 pagineNetwork, Filters and Transmission Lines - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDocumento8 pagineBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - BSNL Je 2016Documento10 pagineBSNL Tta - Je 2016 - GK & Current Affairs - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDocumento8 pagineBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyNessuna valutazione finora

- BSNL TTA - JE 2016 - GK & Current Affairs - BSNL JE 2016 PDFDocumento10 pagineBSNL TTA - JE 2016 - GK & Current Affairs - BSNL JE 2016 PDFSunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Documento8 pagineBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Documento8 pagineBSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Documento8 pagineBSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Documento8 pagineBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyNessuna valutazione finora

- Electrical Measurements For GATE & Competitive Exams !Documento107 pagineElectrical Measurements For GATE & Competitive Exams !satishfactory82% (11)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- MPC-006 DDocumento14 pagineMPC-006 DRIYA SINGHNessuna valutazione finora

- Template EbcrDocumento7 pagineTemplate EbcrNoraNessuna valutazione finora

- Dimensional Analysis Similarity Lesson2 Dimensional Parameters HandoutDocumento11 pagineDimensional Analysis Similarity Lesson2 Dimensional Parameters HandoutRizqi RamadhanNessuna valutazione finora

- Introduction 3-12-86Documento13 pagineIntroduction 3-12-86Roshdy AbdelRassoulNessuna valutazione finora

- Function and Euqations - Quantitative Aptitude Questions MCQDocumento4 pagineFunction and Euqations - Quantitative Aptitude Questions MCQAnonymous v5QjDW2eHxNessuna valutazione finora

- Guidelines On Dissolution Profile Comparison: Udrun ReitagDocumento10 pagineGuidelines On Dissolution Profile Comparison: Udrun ReitagRaju GawadeNessuna valutazione finora

- SSX Diaphragm: Truextent® Replacement Diaphragms For JBL and RADIANDocumento2 pagineSSX Diaphragm: Truextent® Replacement Diaphragms For JBL and RADIANIvica IndjinNessuna valutazione finora

- Masturbation It Might Feel Good But ItsDocumento7 pagineMasturbation It Might Feel Good But ItsKshivam KhandelwalNessuna valutazione finora

- Sony HCD-GTX999 PDFDocumento86 pagineSony HCD-GTX999 PDFMarcosAlves100% (1)

- Overlord - Volume 01 - The Undead KingDocumento223 pagineOverlord - Volume 01 - The Undead KingPaulo FordheinzNessuna valutazione finora

- Kundalini Meditation & The Vagus Nerve - Eleven Minute MedsDocumento5 pagineKundalini Meditation & The Vagus Nerve - Eleven Minute Medstimsmith1081574100% (5)

- Ethics Module 2 - NotesDocumento1 paginaEthics Module 2 - Notesanon_137579236Nessuna valutazione finora

- Chapter 7 (Additional Notes) Thermodynamics Review (Power Plant Technology by M Wakil)Documento29 pagineChapter 7 (Additional Notes) Thermodynamics Review (Power Plant Technology by M Wakil)Aries SattiNessuna valutazione finora

- UPSC IFS Botany Syllabus: Paper - IDocumento3 pagineUPSC IFS Botany Syllabus: Paper - IVikram Singh ChauhanNessuna valutazione finora

- Ca2Documento8 pagineCa2ChandraNessuna valutazione finora

- Personality Types and Character TraitsDocumento5 paginePersonality Types and Character TraitspensleepeNessuna valutazione finora

- Computational Kinematics Assignment 2021Documento2 pagineComputational Kinematics Assignment 2021Simple FutureNessuna valutazione finora

- Vrio Analysis Slide Template 16x9 1Documento8 pagineVrio Analysis Slide Template 16x9 1Alt HrishiNessuna valutazione finora

- Is Revalida ExamDocumento11 pagineIs Revalida ExamRodriguez, Jhe-ann M.Nessuna valutazione finora

- IITG MA101 Endsem Question PaperDocumento12 pagineIITG MA101 Endsem Question PaperNarravula Harshavardhan100% (2)

- CBSE Worksheet-01 Class - VI Science (The Living Organisms and Their Surroundings)Documento3 pagineCBSE Worksheet-01 Class - VI Science (The Living Organisms and Their Surroundings)Ushma PunatarNessuna valutazione finora

- Beckman DxI 800 Prolactin Assay Superiority for Monomeric ProlactinDocumento5 pagineBeckman DxI 800 Prolactin Assay Superiority for Monomeric Prolactindoxy20Nessuna valutazione finora

- Astm C27Documento2 pagineAstm C27nee2790Nessuna valutazione finora

- HS-2172 Vs HS-5500 Test ComparisonDocumento1 paginaHS-2172 Vs HS-5500 Test ComparisonRicardo VillarNessuna valutazione finora

- Lect 17 Amp Freq RespDocumento22 pagineLect 17 Amp Freq RespBent777Nessuna valutazione finora

- Abb 60 PVS-TLDocumento4 pagineAbb 60 PVS-TLNelson Jesus Calva HernandezNessuna valutazione finora

- Palm Wine SpecificationDocumento10 paginePalm Wine SpecificationUday ChaudhariNessuna valutazione finora

- History: Ludwig Hunger: About Us: Home - Ludwig Hunger GMBHDocumento3 pagineHistory: Ludwig Hunger: About Us: Home - Ludwig Hunger GMBHPatrizio MassaroNessuna valutazione finora

- YOKOGAWADocumento16 pagineYOKOGAWADavide ContiNessuna valutazione finora

- NitrocelluloseDocumento7 pagineNitrocellulosejumpupdnbdjNessuna valutazione finora