Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

BUK556 Datasheet

Caricato da

zocanTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

BUK556 Datasheet

Caricato da

zocanCopyright:

Formati disponibili

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

GENERAL DESCRIPTION

N-channel enhancement mode logic

level field-effect power transistor in a

plastic envelope.

The device is intended for use in

automotive and general purpose

switching applications.

PINNING - TO220AB

PIN

QUICK REFERENCE DATA

SYMBOL

PARAMETER

VDS

ID

Ptot

Tj

RDS(ON)

Drain-source voltage

Drain current (DC)

Total power dissipation

Junction temperature

Drain-source on-state

resistance;

VGS = 5 V

PIN CONFIGURATION

DESCRIPTION

gate

drain

source

tab

BUK556-60H

MAX.

UNIT

60

60

150

175

22

V

A

W

C

m

SYMBOL

d

tab

drain

s

1 23

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL

PARAMETER

CONDITIONS

VDS

VDGR

VGS

ID

ID

IDM

Drain-source voltage

Drain-gate voltage

Gate-source voltage

Drain current (DC)

Drain current (DC)

Drain current (pulse peak

value)

Total power dissipation

Storage temperature

Junction Temperature

Ptot

Tstg

Tj

MIN.

MAX.

UNIT

RGS = 20 k

Tmb = 25 C

Tmb = 100 C

Tmb = 25 C

60

60

15

60

44

240

V

V

V

A

A

A

Tmb = 25 C

-

- 55

-

150

175

175

W

C

C

THERMAL RESISTANCES

SYMBOL

PARAMETER

Rth j-mb

Rth j-a

From junction to mounting base

From junction to ambient

October 1993

CONDITIONS

MIN.

TYP.

MAX.

UNIT

60

1.0

-

K/W

K/W

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

BUK556-60H

STATIC CHARACTERISTICS

Tj = 25 C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

V(BR)DSS

Drain-source breakdown

voltage

Gate threshold voltage

Zero gate voltage drain current

Zero gate voltage drain current

Gate source leakage current

Drain-source on-state

resistance

VGS(TO)

IDSS

IDSS

IGSS

RDS(ON)

MIN.

TYP.

MAX.

UNIT

VGS = 0 V; ID = 0.25 mA

60

VDS = VGS; ID = 1 mA

VDS = 60 V; VGS = 0 V;

VDS = 60 V; VGS = 0 V; Tj = 125 C

VGS = 15 V; VDS = 0 V

VGS = 5 V; ID = 25 A

1.0

-

1.5

1

0.1

10

18

2.0

10

1.0

100

22

V

A

mA

nA

m

MIN.

TYP.

MAX.

UNIT

DYNAMIC CHARACTERISTICS

Tj = 25 C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

gfs

Forward transconductance

VDS = 25 V; ID = 25 A

17

30

Ciss

Coss

Crss

Input capacitance

Output capacitance

Feedback capacitance

VGS = 0 V; VDS = 25 V; f = 1 MHz

2200

700

280

2800

1000

400

pF

pF

pF

td on

tr

td off

tf

Turn-on delay time

Turn-on rise time

Turn-off delay time

Turn-off fall time

VDD = 30 V; ID = 3 A;

VGS = 5 V; RGS = 50 ;

Rgen = 50

40

150

350

190

50

250

450

250

ns

ns

ns

ns

Ld

internal drain inductance

Measured from contact screw on

tab to centre of die

nH

Ld

internal drain inductance

Measured from drain lead 6 mm

from package to centre of die

nH

Ls

internal source inductance

Measured from source lead 6 mm

from package to source bond pad

12.5

nH

MIN.

TYP.

MAX.

UNIT

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25 C unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

IDR

60

IDRM

VSD

Continuous reverse drain

current

Pulsed reverse drain current

Diode forward voltage

IF = 50 A; VGS = 0 V

1.1

240

2.0

A

V

trr

Qrr

Reverse recovery time

Reverse recovery charge

IF = 50 A; -dIF/dt = 100 A/s;

VGS = -10 V; VR = 30 V

80

0.4

ns

C

MIN.

TYP.

MAX.

UNIT

150

mJ

AVALANCHE LIMITING VALUE

SYMBOL

PARAMETER

CONDITIONS

WDSS

Drain-source non-repetitive

unclamped inductive turn-off

energy

ID = 50 A; VDD 25 V;

VGS = 5 V; RGS = 50 ; Tmb = 25 C

October 1993

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

120

BUK556-60H

Normalised Power Derating

PD%

10

Zth j-mb / (K/W)

BUKx56-lv

110

100

90

D=

80

0.5

70

0.2

0.1

0.05

60

0.1

50

0.02

40

30

0.01

tp

PD

10

0

0

20

40

60

80 100

Tmb / C

120

140

160

ID / IDmax %

tp

T

t

0.001

180

1E-05

Fig.1. Normalised power dissipation.

PD% = 100PD/PD 25 C = f(Tmb)

120

D=

20

1E-03

t/s

1E-01

1E+01

Fig.4. Transient thermal impedance.

Zth j-mb = f(t); parameter D = tp/T

Normalised Current Derating

150

ID / A

10

8

BUK5y6-60A

7

6

VGS / V =

100

80

100

5

4.5

60

40

50

3.5

20

3

2.5

20

40

60

80 100

Tmb / C

120

140

160

180

BUK556-60H

ID / A

S/

)=

0.1

ID

6

VDS / V

10

RDS(ON) / Ohm

3

12

BUK5y6-60A

3.5

4.5

0.08

VD

tp = 10 us

ON

100

Fig.5. Typical output characteristics, Tj = 25 C.

ID = f(VDS); parameter VGS

Fig.2. Normalised continuous drain current.

ID% = 100ID/ID 25 C = f(Tmb); conditions: VGS 10 V

1000

S(

RD

10

0.06

100 us

1 ms

0.04

10 ms

100 ms

0.02

DC

7

VGS / V = 10

1

1

100

10

VDS / V

Fig.3. Safe operating area. Tmb = 25 C

ID & IDM = f(VDS); IDM single pulse; parameter tp

October 1993

20

40

60

80

ID / A

100

120

140

Fig.6. Typical on-state resistance, Tj = 25 C.

RDS(ON) = f(ID); parameter VGS

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

BUK556-60H

ID / A

150

VGS(TO) / V

BUK5y6-60A

max.

Tj / C = 25

150

100

typ.

min.

50

0

0

10

-60

-20

20

60

Tj / C

VGS / V

gfs / S

140

180

Fig.10. Gate threshold voltage.

VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Fig.7. Typical transfer characteristics.

ID = f(VGS) ; conditions: VDS = 25 V; parameter Tj

40

100

BUK5y6-60A

SUB-THRESHOLD CONDUCTION

ID / A

1E-01

35

1E-02

30

25

2%

1E-03

98 %

typ

20

1E-04

15

10

1E-05

5

1E-06

0

0

20

40

60

80

100

0.4

0.8

1.2

VGS / V

ID / A

Fig.8. Typical transconductance, Tj = 25 C.

gfs = f(ID); conditions: VDS = 15 V

2.0

1.6

2.4

Fig.11. Sub-threshold drain current.

ID = f(VGS); conditions: Tj = 25 C; VDS = VGS

Normalised RDS(ON) = f(Tj)

10000

C / pF

BUK5y6-60A

Ciss

1.5

1000

Coss

1.0

Crss

100

0.5

10

0

-60

-20

20

60

Tj / C

100

140

180

40

VDS / V

Fig.9. Normalised drain-source on-state resistance.

a = RDS(ON)/RDS(ON)25 C = f(Tj); ID = 25 A; VGS = 5 V

October 1993

20

Fig.12. Typical capacitances, Ciss, Coss, Crss.

C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

10

BUK556-60H

VGS / V

BUK5y6-60A

120

WDSS%

110

VDS / V =12

100

48

90

80

70

60

50

40

30

20

10

0

0

0

20

40

QG / nC

60

20

80

Fig.13. Typical turn-on gate-charge characteristics.

VGS = f(QG); conditions: ID = 50 A; parameter VDS

200

IF / A

40

80

100

120

Tmb / C

140

160

180

Fig.15. Normalised avalanche energy rating.

WDSS% = f(Tmb); conditions: ID = 50 A

BUK5y6-60A

VDD

150

Tj / C = 25

150

60

VDS

VGS

100

-ID/100

T.U.T.

0

50

RGS

R 01

shunt

0

0

0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8

VSDS / V

Fig.16. Avalanche energy test circuit.

WDSS = 0.5 LID2 BVDSS /(BVDSS VDD )

Fig.14. Typical reverse diode current.

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

October 1993

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

BUK556-60H

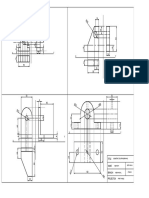

MECHANICAL DATA

Dimensions in mm

4,5

max

Net Mass: 2 g

10,3

max

1,3

3,7

2,8

5,9

min

15,8

max

3,0 max

not tinned

3,0

13,5

min

1,3

max 1 2 3

(2x)

0,9 max (3x)

2,54 2,54

0,6

2,4

Fig.17. TO220AB; pin 2 connected to mounting base.

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Refer to mounting instructions for TO220 envelopes.

3. Epoxy meets UL94 V0 at 1/8".

October 1993

Rev 1.000

Philips Semiconductors

Product Specification

PowerMOS transistor

Logic level FET

BUK556-60H

DEFINITIONS

Data sheet status

Objective specification

This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification

This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1996

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

October 1993

Rev 1.000

Potrebbero piacerti anche

- Fluke 77, 75, 73, 70, 23, 21 Series II UserDocumento37 pagineFluke 77, 75, 73, 70, 23, 21 Series II UserDoctor OldsNessuna valutazione finora

- Panasonic SLA HandbookDocumento73 paginePanasonic SLA HandbookzocanNessuna valutazione finora

- TL431ADocumento10 pagineTL431Ad_richard_dNessuna valutazione finora

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocumento13 pagineMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorszocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 26Documento5 paginePwde9502-D Carisma 99 Chassis 26zocanNessuna valutazione finora

- Project MenagementDocumento147 pagineProject MenagementzocanNessuna valutazione finora

- Feasibility Study TemplateDocumento8 pagineFeasibility Study TemplateAnis ZafirahNessuna valutazione finora

- Switching Power SupplyDocumento138 pagineSwitching Power SupplyStephen Dunifer95% (22)

- Norme - Decembar 2014Documento25 pagineNorme - Decembar 2014zocanNessuna valutazione finora

- MusicPal Manual Musicpal enDocumento120 pagineMusicPal Manual Musicpal enzocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 23Documento25 paginePwde9502-D Carisma 99 Chassis 23zocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 22Documento5 paginePwde9502-D Carisma 99 Chassis 22zocanNessuna valutazione finora

- ApendixDocumento18 pagineApendixzocanNessuna valutazione finora

- Engineer AdamDocumento11 pagineEngineer AdamzocanNessuna valutazione finora

- Feasability 2Documento8 pagineFeasability 2Layal90Nessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 17Documento26 paginePwde9502-D Carisma 99 Chassis 17zocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 36Documento3 paginePwde9502-D Carisma 99 Chassis 36zocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 21Documento4 paginePwde9502-D Carisma 99 Chassis 21zocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 13Documento117 paginePwde9502-D Carisma 99 Chassis 13zocanNessuna valutazione finora

- Phde9501-D Carisma 99 Electrical WiringDocumento325 paginePhde9501-D Carisma 99 Electrical WiringzocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 55Documento7 paginePwde9502-D Carisma 99 Chassis 55zocanNessuna valutazione finora

- Pwde9502-D Carisma 99 Chassis 52Documento31 paginePwde9502-D Carisma 99 Chassis 52zocanNessuna valutazione finora

- Mitshubishi ServisDocumento1 paginaMitshubishi ServiszocanNessuna valutazione finora

- Phde9501-B Carisma 98 Electrical Wiring (Except Gdi)Documento218 paginePhde9501-B Carisma 98 Electrical Wiring (Except Gdi)zocanNessuna valutazione finora

- Lisa 2 Ep Mootmised Teoorias Ja Praktikas - EnglDocumento95 pagineLisa 2 Ep Mootmised Teoorias Ja Praktikas - EnglzocanNessuna valutazione finora

- Harman-Kardon hk-610 SM (ET)Documento22 pagineHarman-Kardon hk-610 SM (ET)merat666Nessuna valutazione finora

- Phdr9501-A Carisma 96 97 Electrical WiringDocumento508 paginePhdr9501-A Carisma 96 97 Electrical WiringzocanNessuna valutazione finora

- MSB 95e54 003 - Carisma - 96 02 15Documento14 pagineMSB 95e54 003 - Carisma - 96 02 15zocanNessuna valutazione finora

- IntroArduinoBook PDFDocumento172 pagineIntroArduinoBook PDFAndrew TeohNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5783)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- L2001a Lab ManualDocumento13 pagineL2001a Lab ManualMuhammad Rais FawwaziNessuna valutazione finora

- Reply To RFI 004 - BIM Related QueriesDocumento7 pagineReply To RFI 004 - BIM Related QueriesSuresh DNessuna valutazione finora

- Archanadhaygude - 2yoe - SoftwaredeveloperDocumento2 pagineArchanadhaygude - 2yoe - SoftwaredeveloperPRESALES C2LBIZNessuna valutazione finora

- Errors While Importing Matplotlib:: General FAQ's of Week-3 (PDS)Documento5 pagineErrors While Importing Matplotlib:: General FAQ's of Week-3 (PDS)Ragunathan SmgNessuna valutazione finora

- AutopilotDocumento76 pagineAutopilotAnthony Steve LomilloNessuna valutazione finora

- Gartner Market Guide DDI 25042014Documento6 pagineGartner Market Guide DDI 25042014Mohamed Osama AbosreeNessuna valutazione finora

- PepsiCo GRCDocumento4 paginePepsiCo GRCessamsha3banNessuna valutazione finora

- Audiocodes Mediant Sbcs For Service ProvidersDocumento9 pagineAudiocodes Mediant Sbcs For Service ProvidersrAVINessuna valutazione finora

- Guia Modem Zyxel VMG862 3T50BDocumento4 pagineGuia Modem Zyxel VMG862 3T50BJosé AntonioNessuna valutazione finora

- N4 Xtend Training v3Documento3 pagineN4 Xtend Training v3Talha RiazNessuna valutazione finora

- How To Use KeygenDocumento1 paginaHow To Use KeygenearltonNessuna valutazione finora

- F6TesT EnglishDocumento270 pagineF6TesT EnglishHamylto PamoNessuna valutazione finora

- ISO ORTHO ModelDocumento1 paginaISO ORTHO Modelavishal ramNessuna valutazione finora

- Appid Yahoo Mail Neo&wssid EZ7 MR Zti M4 J&ymreqid Bec 69Documento10 pagineAppid Yahoo Mail Neo&wssid EZ7 MR Zti M4 J&ymreqid Bec 69Juliana R. B. AlmeidaNessuna valutazione finora

- Latent Variable Models for Density EstimationDocumento29 pagineLatent Variable Models for Density EstimationAboutNessuna valutazione finora

- User guide for FGV eClaims moduleDocumento42 pagineUser guide for FGV eClaims moduleSaipol AzmiNessuna valutazione finora

- UrbaWind, A Computational Fluid Dynamics Tool To Predict Wind Resource in Urban AreaDocumento9 pagineUrbaWind, A Computational Fluid Dynamics Tool To Predict Wind Resource in Urban AreaMeteodyn_UrbawindNessuna valutazione finora

- Serial Code Number Tinta L800Documento5 pagineSerial Code Number Tinta L800awawNessuna valutazione finora

- CCTVDocumento3 pagineCCTVJoan Cristy Cornista LastrillaNessuna valutazione finora

- ODWEK BasicsAndBeyondDocumento314 pagineODWEK BasicsAndBeyondcursocmodNessuna valutazione finora

- Computer Monitor: From Wikipedia, The Free EncyclopediaDocumento4 pagineComputer Monitor: From Wikipedia, The Free EncyclopediaSock SackNessuna valutazione finora

- Internshala TeardownDocumento12 pagineInternshala Teardownmuskansukhija18Nessuna valutazione finora

- Thing 1 Basic DocumentDocumento5 pagineThing 1 Basic Documentapi-354411812Nessuna valutazione finora

- Raytek 3i PlusDocumento4 pagineRaytek 3i PlusRahul BharadwajNessuna valutazione finora

- EEE-354: Telecommunication Systems EngineeringDocumento35 pagineEEE-354: Telecommunication Systems EngineeringBilal HabibNessuna valutazione finora

- CrashDocumento13 pagineCrashBabs SiclesNessuna valutazione finora

- Fire Control SystemDocumento40 pagineFire Control SystemwilliamNessuna valutazione finora

- Part of Bluetooth BookDocumento41 paginePart of Bluetooth Bookmeroka2000100% (1)

- Electronik PratikDocumento23 pagineElectronik PratikHoussam Bahri0% (1)

- Nrs Mod 5 Data Innovation ReportDocumento1 paginaNrs Mod 5 Data Innovation ReportBrahmananda ChakrabortyNessuna valutazione finora