Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Clamp

Caricato da

Gaetano GaetanoDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Clamp

Caricato da

Gaetano GaetanoCopyright:

Formati disponibili

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO.

1, JANUARY 1996

162

ization of an Active-Clamp Circuit to

ve Soft Switchi g in Flyback Converters

Robert Watson, StudentMember, IEEE, Fred C. Lee, Fellow, IEEE, and Guichao C. Hua

Abstract-Flyback derived topologies are attractive because of

their relative simplicity when compared with other topologies

used in low power applications. Incorporation of active-clamp

circuitry into the flyback topology serves to recycle transformer

leakage energy while minimizing switch voltage stress. The addition of the activef-clamp circuit also provides a mechanism for

achieving zero-voltage-switching(ZVS) of both the primary and

auxiliary switches. ZVS also limits the turn-off d i / d t of the output

rectifier, reducing rectifier switching losses, and switching noise

due to diode reverse recovery. This paper analyzes the behavior

of the ZVS active-clamp flyback operating with unidirectional

magnetizing current and presents design equations based on this

analysis. Experimental results are then given for a 500 W prototype circuit illustrating the soft-switching characteristics and

improved efficiency of the converter. Results from the application

of the active-clamp circuit as a low-loss turn-off snubber for

IGBT switches is also presented.

@vm

t

k

6

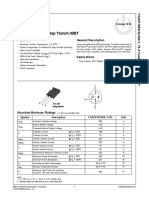

Fig. 1. Simplified schematic of the active-clamp flyback converter.

I. INTRODUCTION

HE flyback topology has long been attractive because

of its relative simplicity when compared with other

topologies used in low power (up to several hundred watts)

applications. The flyback transformer serves the dual purpose of providing energy storage as well as converter isolation,

theoretically minimizing the magnetic component count when

compared with, for example, the forward converter. A drawback to the use of the flyback is the relatively high voltage and

current stress suffered by its switching components. High peak

and RMS current stress is a particular problem for flybacks

when operating in discontinuous conduction mode (DCM) and

is in fact a primary detriment to increasing output power.

An addition, high turn-off voltage (caused by the parasitic

oscillation between the transformer leakage inductance and the

switch capacitance) seen by the primary switch traditionally

requires the use of an RCD clamp to limit the switch voltage

excursion. Unfortunately, in this scheme the energy stored in

the transformer leakage is dissipated in the clamp resistor,

resulting in a difficult design trade-off between clamping

action and clamp circuit power dissipation.

The limitations presented by the RCD clamp can be largely

overcome by replacing the passive clamp with an activeclamp circuit, as shown in Fig. 1. Active-clamp methods have

been explored in detail for forward converters [7], [XI. The

active-clamp circuit provides the benefits of recycling the

transformer leakage energy while minimizing turr-off voltage

Manuscript received June 15, 1994, revised July 12, 1995 This work was

supported by Zytec Corporation

The authors are with the Virginia Power Electronics Center, Bradley

Department of Electrical Engineenng, Virginia Polytechnic Institute and State

University, Blacksburg, VA 24061 USA

Publisher Item Identifier S 0885-8993(96)00603-5.

stress across the power switch. In addition, the active-clamp

circuit provides a means of achieving zero-voltage-switching

(ZVS) for the power switch and subsequent lowering of

the output rectifier di/dt. This results in decreased rectifier

switching loss and output switching noise. To achieve softswitching characteristics over a useful operating range, the

addition of a small resonant inductor in the active-clamp loop

is usually necessary (see Fig. 1).

The use of the active-clamp circuit to achieve soft switching

in flybacks operating with bidirectional magnetizing current is

well documented [ 11-[3]. By bidirectional magnetizing current

it is meant that the flyback transformer ripple current is

allowed to become negative (i.e., reverse direction relative

to magnetizing current flow defined in Fig. 1) for a portion

of each switching cycle. This is only possible in conjunction

with the operation of the active-clamp network. The (negative)

magnetizing current can then be used to discharge the primary

switch capacitance and achieve ZVS. However, for higher

output power operation, it is more desirable to minimize the

transformers ripple current content to reduce device current

stress [4], IS].This is directly analogous to CCM versus DCM

operation in conventional flyback converters, where, given

identical operating conditions, DCM op

greater device peak current stress and

CCM operation. However, ZVS can s

unidirectional magnetizing current by utilizi

stored in the resonant inductor [6]. The

resonant inductor also helps to softly com

of the output rectifier, resulting in reduced

rectifier switching losses. This would be a parti

in high output voltage applications where slower rectifiers are

more likely to be used.

0885-8993/96$05 .OO 0 1996 IEEE

WATSON et al.: ACTIVE-CLAMP CIRCUIT TO ACHIEVE SOFT SWITCHING IN FLYBACK CONVERTERS

163

0

0

Vm

0

0

0

T X T A

T4 T5

. ..

T5 -T6

-

T6- T7

Fig. 2. Active-clamp flyback topological states

This paper presents evaluation of a constant-frequency, softswitching, active-clamp flyback converter for dcldc conversion

applications. The basic principle of operation is analyzed and a

design procedure is developed. Experimental results are then

presented, which illustrate converter function and verify the

analysis presented.

11. ACTIVE-CLAMP

FLYBACK

CONVERTER

OVERVIEW

The incorporation of an active-clamp circuit into the basic

flyback topology is shown in Fig. 1. In the figure, the flyback transformer has been replaced with an equivalent circuit

model showing the magnetizing and leakage inductances ( L ,

represents the total transformer leakage inductance reflected to

the primary in addition to any external inductance). Switches

S1 and S2 are shown with their associated body diodes. C,

represents the parallel combination of the parasitic capacitance

of the two switches. It is this device capacitance resonating

with L, that enables ZVS for S1. With the active-clamp

circuit, the transistor turn-off voltage spike is clamped, the

transformer leakage energy is recycled, and zero-voltageswitching (ZVS) for both primary (Sl) and auxiliary ( S 2 )

switches becomes a possibility. These advantages come at the

expense of additional power stage components and increased

control circuit complexity (two switches as opposed to the

usual one switch).

Fig. 2 illustrates the topological states and Fig. 3 the key

waveforms for the active-clamp flyback converter. For this

description of circuit operation (and for the subsequent development of a design procedure in the next section), the

following assumptions are made:

ideal switching components,

the magnetizing current is always nonzero and positive

(positive direction as defined by Fig. I),

Fig. 3. Active-clamp flyback steady-state waveforms.

L, (includes the transformer leakage inductance) is much

less than the transformer magnetizing inductance, L ,

(typically 5% to 10% of L,),

sufficient energy is stored in L, to completely discharge

C, and turn on Sl's body diode, and

>> Toff.

The last assumption simply states that one-half the resonant

period formed by L, and Cclampis much longer than the

maximum off time of S1(T0~

E (1 - D)Ts).The sequence

of topological states is described below.

To-Tl: At TO,switch S1 is on, and the auxiliary switch,

S2, is off. The output rectifier, D1, is reversed biased as is the

antiparallel diode of 5'2. The magnetizing inductance (along

with the resonant inductance) is being linearly charged, just

as it would be during the inductor charging phase in "normal"

flyback operation.

T I - T ~ :S1 is turned off at T I . C, is charged by the

magnetizing current (which is also equal to the current through

the resonant inductor). C, is actually charged in a resonant

manner, but the charge time is very brief, leading to an

approximately linear charging characteristic.

Tz-T~:At T2, C, is charged (V& = I&,

Vc)to the

point where the antiparallel diode of S2 starts to conduct.

The clamp capacitor fixes the voltage across L, and the

transformer magnetizing inductance to V ,( S N G ) , forming

a voltage divider between the two inductances. Since Cclamp

is much larger than C,, nearly all of the magnetizing current

is diverted through the diode to charge the clamp capacitor.

Consequently, the voltage appearing across the magnetizing

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 1, JANUARY 1996

164

inductance, Vpri, decreases as V, increases, according to the

voltage divider action described by (1)

Vpri =

-v' L , L,+ L,'

T3-T4: At T3, Vpr; has decreased to the point where the

secondary transformer voltage is sufficient to forward bias

D1. The transformer primary voltage is then clamped by the

(very large) output capacitance to approximately NVo. L, and

Cclamp

begin to resonate. In order for S2 to achieve ZVS, the

device should be turned on before IcClamp

reverses direction.

T4-T5: The auxiliary switch, S2, is turned off at T4,

effectively removing Cclamp

from the circuit. A new resonant

network is formed between the resonant inductor and the

MOSFET parasitic capacitances. The transformer primary

voltage remains clamped at NVo as C, is discharged.

T5-T6: Assuming the energy stored in L, is greater than the

energy stored in C,, at T5CT will be sufficiently discharged to

allow Sl's body diode to start conducting. The voltage across

the resonant inductor becomes clamped at V,, NVo. This

also fixes the rate of decay of the output rectifier current to

For L,

>> L,, (2) simplifies to

diDl

- N

dt

-N

V,n

+ NVO

LT

(3)

It is during this interval that switch S1 can be turned on under

zero-voltage conditions.

T6-T7: S1 is on, and the secondary current is decreasing as

the resonant inductor current increases. At T7, the secondary

current decreases to zero (because the resonant inductor current has equaled the magnetizing current), and D1 reverse

biases, allowing the polarity to reverse on the transformer

primary. The magnetizing and resonant inductances begin to

linearly charge again, starting another switching cycle (T7 =

In addition to the S l / S 2 timing requirement. there must

also be sufficient energy stored in the resonant inductor to

completely discharge the switch capacitance. This requirement

is valid at time instant T4 (when S2 is turned off)

EL? 2 Ec,

I ~ ~ 2 t u off

r n

(5)

It should be noted that even if insufficient energy is stored in

L, to completely discharge the switch capacitance, meeting the

timing requirement called for in (4) guarantees switching with

the minimum possible voltage stress for the given operating

condition. Equation ( 5 ) can be used to develop a design

equation determining an appropriate resonant inductor value

that realizes ZVS at a desired operating point. This will be

detailed in the section concerned with the design of L,.

A. ZVS Active-Clamp Flyback Design Procedure

1 ) Select Flyback Transformer Inductance

of the active-clamp circuit does not significantly alter the

primary switch current waveform from that seen in non-activeclamp CCM flyback designs. Therefore, the usual methods of

determining the appropriate value of magnetizing inductance

can be used. Of course, the peak and RMS switch currents are

heavily influenced by the amount of allowed inductor ripple

current. This is usually expressed as some percentage of the

maximum average inductor current (occurring at m

load and minimum line) so as to limit switch currents.

2) Select Transfoimer Turns Ratio: The transformer turns

ratio is chosen to accommodate as low a voltage rating for the

switching devices as possible while still being able to realize

a reasonable range of duty cycles over the input line range.

Assuming that the active clamping provides for perfect voltage

clamping across the primary switch (i.e., no overshoot), then

the maximum off-state voltage appearing across S1 and S2

is given by

TO).

Note that the length of the time intervals TI to T3 and T4

to T7 have been greatly exaggerated in Fig. 3 in order to more The last part of the expression in (6) is the value of the

voltage developed across L,. Although an explicit value of

clearly show the transition periods.

the resonant inductor hasn't yet been determined, for the

purposes of estimating the maximum voltage stress on S1

111. SOFT-SWITCHING

FLYBACKDESIGNCONSIDERATIONS and S2 a value of L,/10 can be used as a conservative

For the purposes of ZVS of S1,there must be assurance that design guideline. Also, as long as L , >> L, the converter dut

the switch is turned on during the T5 to T6 time interval. If cycle behavior is approximately the same as for a non-act

not, the resonant inductor current reverses (becoming positive clamp flyback operating in CCM. With the addition of L,, the

again), recharging C,, and ZVS is lost (or at least partially effective duty cycle (as defined by the charge and discharge

lost). Therefore, the delay time between the turn off of S2 and cycle of the flyback inductor) is slightly less than switch S l ' s

the turn on of S1 is critical to ZVS operation. The optimum duty cycle (see Fig. 3)

value of this delay is one-quarter of the resonant period formed

by L, and C,

(4)

Strictly speaking, the value of C, is a function of applied

voltage (particularly at small drain-to-source voltages), but (4)

simplifies matters by assuming that it is not.

Equation (7) is approximate in that it assumes lossless switching. In this application A D M 5% of Dsl so for the purposes

of developing (6) and subsequent design equations it will be

assumed D = Deff = Dsl.

165

WATSON et al.:ACTIVE-CLAMP CIRCUIT TO ACHIEVE SOFT SWITCHING IN FLYBACK CONVERTERS

3) Design Resonant Inductor: After the value of L, has

been fixed, the resonant inductor can be designed. As mentioned previously, it is assumed its value will be a small

fraction of L,. For a given converter operating point and

value of C,, achieving ZVS requires that L, be of sufficient

size to completely discharge the switch capacitance. At time

instant T4, from (5)

IS1,peak

=I

ILm,peak

= IL,,peak 2

vCT

(8)

where the peak primary switch current is

(9)

The difficulty in solving (8) for L, is the fact that the resonant

capacitor voltage (V&) is a function of the value of L,.

However, in a practical design situation, the resonant inductor

voltage at T4 is relatively small (compared to

+ NVo) and

(8) can be solved for an approximate minimum value of L,

necessary to achieve ZVS

v,

51

,peak

be necessary to complicate the implementation of S2 by

defeating its slow body diode by placing a diode in series

with 52 and placing a fast recovery rectifier in parallel with

the S2-diode series combination. This will prevent conduction

of S2s body diode, necessary if a condition in the circuit ever

occurred where S2s body diode was conducting when S1 is

turned on. This could possibly occur, for example, during a

line or load transient. Of course, the possibility of ZVS for S 2

is lost using such a realization.

5) Select Clamp Capacitor: Choosing the value of clamp

capacitance is done based on the design of L,. The resonant

frequency formed by the clamp capacitor and the resonant

inductor should be sufficiently low so that there is not excessive resonant ringing across the power switch when the

switch is turned off. However, using too large a value of clamp

capacitance yields no improvement in clamping performance

at the expense of a larger (more costly and bulky) capacitor.

A good compromise for design purposes is to select the

capacitor value so that one-half of the resonant period formed

by the clamp capacitor and resonant inductance exceeds the

maximum off time of S1.Therefore

Cclamp

In applications requiring high output voltage, it may be more

desirable to specifically tailor the soft-switching characteristics

of the output rectifier than to necessarily realize ZVS of the

primary switch. In this case, (3) may be the more important

design criteria for the resonant inductor.

The RMS current carried by L, can be estimated from (11)

(1 - DHL)

,rr2L,F,2

The capacitor voltage rating has to exceed NVo by the amount

of voltage dropped across L,

The required ripple current rating for the capacitor is

JL,,RMS

1 DLL

Icclamp,EMS

max

I z t l a m p -/ F .

(11)

The expression for this current is complicated by the fact

that the resonant inductor carries both primary switch and

circulating clamp current.

4 ) Select Auxiliary Switch: For the purposes of estimating

the required current rating of S2, advantage is taken of the

assumption that the L, - Cclamp resonant period is much

longer than the off time of S1.Under this assumption, the

approximates a sawtooth

current through S2 (same as

waveform with endpoint currents equal to the peak current

through S1 (see Fig. 3). The MOSFET body diode conducts

clamp current for half the S2 on time with the MOSFET

itself conducting current for the remaining half of the cycle.

Therefore, the worst case maximum currents seen by both the

MOSFET and its body diode are approximately

and

where the peak primary switch current can be obtained from

(9). It should be noted that as a practical matter it may

(16)

Equation (16) was derived using the same simplifying assumption used to derive (12) and (13).

6) Choose Output Rectifier: The maximum theoretical reverse voltage seen by the output rectifier in the active-clamp

flyback is the same as for a standard flyback design. However,

the rectifier current is another matter. Due to the presence of

the clamp circuit, the secondary current is discontinuous in

shape even though the flyback inductor magnetizing current

is always positive and greater than zero. This is illustrated in

Fig. 3. The result is much higher peak secondary currents than

would normally be expected in a non-active-clamp flyback

operating in CCM

Ig?;eak

2pFX

Vo(1 - DLL)

The average rectifier current is just the load current. As was

pointed out previously, the addition of L, reduces the rate of

diode turn-off d i l d t . This improves rectifier switching losses

and converter noise levels (see Figs. 6-8).

7) Select Output Capacitor(s): The principal factor affecting the value of output capacitance is utilization of enough

capacitance to meet device ripple current ratings

E E E TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 1, JANUARY 1996

166

Efficiency (h)

Output Power (W)

Fig. 4. Efficiency comparison between RCD and active-clamp configmations. For RCD clamp, R = 4.7 K.Q, 10 W, and C = 2.2 pF.

Theoretically, the capacitance value would be selected based

on output voltage ripple specifications. However, in practice,

meeting the RMS current rating called for in (18) sets a lower

limit on an amount of capacitance that usually easily meets

any ripple voltage specification.

8) Design Flyback Transformer: Still constrained by the

assumption that L, << L,, the transformer design for the

active-clamp flyback is no different than that for a non-activeclamp CCM flyback, except the primary and secondary RMS

currents are somewhat different. The transformer secondary

and output rectifier RMS currents are equivalent, so

Fig. 5 . ZVS active-clamp flyback experimental waveforms. Top trace:

vgs,sl@ 15 V/div.; middle trace: I L , @ 5 A/div.; bottom trace: vds,S1

@ 100 V/div. Time scale is 1 ps/div.

0 --

--

Fig. 6. Output rectifier current waveforms @ 10 A/div. Toptrace.

N 2 pH. Time scale is 500 ns/div.

The transformer primary current is identical to the resonant L , = 7 p H ; bottom trace: L , =

inductor current, consequently its RMS value is given by (1 1).

Clamp circuit:

I v . EXPERIMENTAL

RESULTS

To experimentally characterize the soft-switching properties of the active-clamp flyback converter, a breadboard was

constructed to the specifications listed below:

input voltage: 100 VDC

output voltage: 48 VDC

* output power: 500 W maximum

switching frequency: 100 kHz

Using the design procedure discussed in the previous section

as a guide, the experimental converter was constructed using

0

0

the following components:

0

Transformer:

core: Toshiba PC40ETD49-Z

primary: 45T of 3 strands of 150/42 Litz wire

secondary: 15T of 5 strands of 150/42 Litz wire

L,: 215 pH, &ak (referred to primary): 2.3 pH

Resonant inductor:

core: MPP 55530

winding: 8T of 10 strands of AWG 26

L,: 7 pH (with no bias)

Cclamp:

2.2 pF, 250 V

S2: IRFF360

* 51: ESP360

* Output stage:

D1 : 2xBYV44-500

CO: 3 x 2200 pF, 100 V Aluminum electrolytic.

For the experimental circuit, ZVS was realized above

145 W. Fig. 4 compares experimental efficiencies using an

RCD clamp with no resonant inductor and the active-clamp

circuit with L, = 7 pH (all other circuit parameters are

identical). It can be seen that the active-clamp circuit yields

an improvement of at least -4% in power stage efficiency.

Maximum output power for the RCD clamped power stage

is about 250 W due to power dissipation limitations in the

clamp resistor.

Figs. 5 and 6 are experimental waveforms pertinent to illustrating the converters soft-switching characteristics. Fig. 5

displays S l s gate drive voltage, the resonant inductor current,

and Sls drain-to-source voltage. Operation is at Po = 300 W.

Fig. 6 compares the output rectifier current with and without

L, in the circuit. The operating point of the converter is

identical for both cases (Po = 300 W, ZVS with L,, hard

WATSON et al.: ACTIVE-CLAMP CIRCUIT TO ACHIEVE SOFT SWITCHING IN FLYBACK CONVERTERS

167

Efficiency ph)

IRGPC4OU

--c

IRGPC4OU. Cr = 3000 pF

m s o

.-..-.

IRFpcso~~m5o

-..-..

Output Power (W)

Fig. 9. Efficiency comparison using the active-clamp network with various

switch configurations. FS = 100 kHz.

Fig. 7. Output voltage noise, L , =

Experimental results comparing power stage efficiencies

using an IGBT with and without external capacitance is shown

in Fig. 9. With C, = 3000 pF, the efficiency is improved by

about 1% over most of the load range. Also, for comparison

purposes, efficiencies for a single and dual 600 V MOSFETs

are plotted. As can be seen, at PO= 400 W circuit efficiency

using a single IGBT is equal to the efficiency obtained using

two MOSFETs.

Lleak.

V. CONCLUSION

RES S W 3

kHZ

VBW 3 kHZ

SWP 1.0

sec

Fig. 8. Output voltage noise, L , = 7 pH.

switching without it). As can be seen from the figure, with

the resonant inductor the rectifier reverse recovery current

characteristic is substantially improved. Not only is switching

loss in the diode decreased, but the output voltage highfrequency (HF) noise is reduced. This is illustrated in Figs. 7

and 8, which show the output voltage noise spectrum with

and without L,. In particular, the noise levels in the frequency

range of about 2.5-3 MHz show a reduction of nearly 20 dB

between the two cases. Coincidentally, HF noise in the range

of about 2-5 MHz is typically very difficult to filter because

the frequency is somewhat low for effective use of ferrite beads

and is too high for standard capacitive bypassing.

Another attractive usage for the active-clamp circuit is

as a low-loss turn-off snubber when using an IGBT as the

primary switch device (51).IGBTs have superior conduction

characteristics compared to MOSFETs (of the same voltage

rating). The drawback to the use of IGBTs is that they

display excessive turn-off losses 3s their switching frequency

is increased. The severity of this problem can be reduced by

adding an external capacitor (C,) from the collector to the

emitter of the IGBT to slow down the rate of increase in

collector voltage as the device turns off. This allows time for

the device current to tail to zero without excessive device

voltage being present. Subsequently, before S1 is turned on,

the resonant inductor discharges C, so that its stored energy

is not dissipated in the IGBT at device turn on.

This paper has presented the analysis, design, and experimental results for a high-efficiency 500 W flyback dcldc

converter employing active-clamp circuitry. The incorporation

of the active-clamp circuit into the basic flyback topology

provides a mechanism for achieving ZVS for both the primary

and auxiliary switches and soft commutation of the output rectifier while operating with low ripple (unidirectional) current

in the flyback transformer. Low ripple current operation is

desirable as power levels of several hundred watts can realize

higher efficiencies than when compared with a non-activeclamp flyback operating in DCM or an active-clamp flyback

operating with high ripple currents.

APPENDIX

In this appendix are outlines of the derivations of the

equations that appear in the section of the paper describing

the design procedure [(6)-(19)]. Here we make the following

simplifying assumptions:

The clamp current is piecewise linear instead of quasisinusoidal.

Clamp capacitor voltage is constant (i.e., clamp capacitor

is assumed infinite in value).

The duration of the intervals Tl-T2 and T4-T6, shown

in Fig. 3, is short enough compared with the duration of

interval Tl-T6 to allow them to be neglected.

de^

= Dsl.

Equation (6): Fig. 10 shows the idealized clamp current

waveform and the simplified circuit topology during switch

51s off time. The switch voltage is given by

The peak switch current (which is equal to the peak magnetizing current and peak resonant inductor current) is determined

by applying the principal of power balance to the converter.

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 1, JANUARY 1996

168

the assumption of small duty cycle loss, VL?<< V,, NVo

during clamping portion of the switching cycle. Therefore, for

zvs of s1

-LriZ,

2l

2 5CrVz7

l@S2turn-off

1QS2 turn-off

(23)

For VC,.M V,, NVo (23) can be solved for Lr to yield (10).

Equation (11): The RMS current flowing in the resonant

inductor can be calculated with the aid of Figs. 3 and 11. If

we assume negligible duty cycle loss, the slope of the resonant

inductor current becomes infinite during the T 4 T 7 interval

shown in Fig. 3 (i.e., the duration of the T4-T7 interval

is zero). The RMS value of the current can then be more

easily approximated using two piecewise linear intervals over

a switching cycle

(b)

Fig. 10. (a) Idealized clamp capacitor current waveform. (b) Simplified

topological state S1 off, S2 on.

S1

s2

Lm

Integrating (24) yields an expression for the RMS current in

terms of the peak switch current. Equation (9) can then be

used to obtain (11).

Equations (12) and (13): Both of these equations can be

derived with the aid of Fig. 10. It is assumed the body diode

of 52 will conduct the positive portion of the clamp current

and the MOSFET will conduct the negative portion. With a

linear clamp current waveform and equal but opposite endpoint

values, this implies each part of S 2 will conduct for half of

the (1 - D)Ts interval. Therefore, the average body diode

current is

Lr

I S 2 body diode,avg E

Fig. 11. Idealized waveforms for computing effective duty cycle.

Under the assumptions stated above, the expression for the

peak switch current is the same as that obtained for a nonactive-clamp CCM flyback. This is simply the average inductor

current plus one-half of the peak-to-peak inductor ripple

current, and is given by (9). Substituting (9) into (20) results

in (6).

Equation (7): Referring to Fig. 11, the duration of the

interval ADTs is given by

ADT -

Lr

- V,,+NVo

(iL,,peak

+ iL,,valley). (21)

We now need an expression for the second factor in (21)

in terms of Ds1. Resorting to power balance and assuming

A D << Dsl yields

Substituting (22) into (21) yields the second part of the

expression given in (7).

Equations (8) and (10): Equation (8) follows directly from

(5). Equation (10) is complicated by the fact that the resonant

capacitor voltage is a function of the resonant inductor voltage,

which is given by the middle term in (20). However, under

The MOSFET

(4 d t

iCclamp

1-D

iSl, peak-

c ~ ~ eisn obtained

t

in a Similar m m ~ r

IS2, MOSFET,RMS E

@=Er---

- iSl,peak

/?*

i&,,,,

( t )d t

(26)

Equations (14)-(16): Equation (14) results from the resonance between L, and C c l a m p . We want half the resonant

period to be greater than S l s maximum off-time

Equation (27) can be solved for C c l a m p to yield (14). Once an

expression is found for the resonant inductor voltage during

the clamping cycle [middle term of (20)], the derivation of (15)

is straightforward.Equation (16) can be derived from Fig. 10

WATSON et al.: ACTIVE-CLAMP CIRCUIT TO ACHIEVE SOFT SWITCHING IN FLYBACK CONVERTERS

169

[SI C. Leu, G. Hua, and F. Lee, Comparison of forward topologies with

various reset schemes, in Proc. 9th Ann. VPEC Power Electron. Sem.,

1991, pp. 101-109.

<iD1> = Io

Fig. 12. Simplified output rectifier waveform.

Equations (17)-(19): Equations (17)-( 19) can be derived

with the aid of Fig. 12. As shown in the figure, the diode

current waveform has been approximated as piecewise linear.

This reflects the assumption that the clamp capacitor current

is linear during the clamping interval. Once again, if it is

assumed L, << L,, the rectifier turn-off current slope can

be approximated as infinite. The peak diode current can be

obtained from knowledge of the average rectifier current

Robert Watson (S93) was born in 1958 in Indianapolis, IN. He received the B.S.E.E. degree

in 1982 from Purdue University, West Lafayette,

Indiana and the M.S.E.E. degree in 1986 from

the University of Arizona in Tucson. Currently, he

is a Ph.D. candidate in electrical engineering at

Virginia Polytechnic Insbtute and State University

in Blacksburg.

Prior to joining the Virginia Power Electronics

Center (VPEC) at VPI&SU as a Research Assistant

in 1992, Mr. Watson split 10 years of industrial

employment between Hughes Aircraft Company and Bendix Engine Controls,

a division of Allied-Signal Corporation. Currently, he is a Research Associate at VPEC, specializing in dc and high-frequency ac distributed power

architectures, high-frequency power conversion, and power factor correction

applications.

Mr. Watson is a member of Phi Kappa Phi and was a Hughes Aircraft

Company Fellow in 1985 and 1986.

REFERENCES

Fred C. Lee (S72-M74-SM87-F90) received

the B.S. degree in electrical engineering from National Cheng Kung University in Taiwan in 1968,

and the M.S. and Ph.D. degrees from Duke University, Durham, NC in 1971 and 1974, respectively.

He holds the Lewis A. Hester Chair of Engineering at Virginia Tech, and was the James S. Tucker

Endowed Professor in the Bradley Department of

Electrical Engineenng. He is the founder and director of the Virginia Power Electronics Center

(VPEC), a Technology Development Center of the

Center for Innovative Technology (CIT). Under his leadership, VPEC has

become one of the largest university-based power electronics research centers

in the country. The Centers Industry Partnership Program has enrolled more

than 70 companies around the world. His research interests include highfrequency power conversion, distributed power systems, space power systems,

device characterization, and modeling and control of converters and design

optimization. During his career, he has published more than 100 referred

journal papers, more than 200 technical papers in national and intemational

conferences, and over 150 industry and government reports. He currently

holds 14 U.S. patents.

Dr. Lee is a recipient of the 1985 Ralph R. Teeter Educational Award of

the Society of Automotive Engineering, the 1989 William E. Newel1 Power

Electronics Award of the IEEE Power Electronics Society, the 1990 PCIM

Award for Leadership in Power Electronics Education, and the 1990 Virginia

Tech Alumni Award for Research Excellence. He is a Past President of the

IEEE Power Electronics Society.

[l] C. Henze, H. Martin, and D. Parsley, Zero-voltage switching in high

frequency power converters using pulse width modulation, in Proc. 3rd

Ann. Appl. Power Electron. Con$, 1988, pp. 33-40.

[2] H. Martin, Topology for miniature power supply with low voltage and

low ripple requirements, U.S. Patent 4618 919.

[3] K. Yoshida, T. Ishii, and N. Nagagata, Zero voltage switching approach

for flyback converter, in Proc. 14th lnt. Telecomm. Energy Con$, 1992,

pp. 324-329.

[4] W. Tang, E. Yang, and F. Lee, Loss comparison and subharmonic issue

on flyback power factor correction circuit, in Proc. 11th Annu. VPEC

Power Electron. Sem., 1993, pp. 125-131.

[51 R. Watson, G . Hua, and F. Lee, Characterization of an active clamp

flyback topology for power factor correction applications, in Proc. 9th

Ann. Appl. Power Electron. Con$, 1994, pp. 412418.

[6] K. Harada and H. Sakamoto, Switched snubber for high frequency

switching, in Proc. Power Electron. Spec. Conf, 1990, pp. 181-187.

[7] B. Carsten, Design techniques for transformer active reset circuits at

high frequency and power levels, in High Freq. Power Conversion

Con$ Proc., 1990, pp. 235-245.

Guichao C. Hua received the B.S. and M.S. degrees

in electrical engineering from Zhejiang University

in China in 1985 and 1988, respectively, and the

Ph.D. degree from Virginia Tech, Blacksburg, in

1994.

From 1988 to 1989, he was employed as a power

supply design engineer at Watt Power Supply Corp.

in China. He joined the Virginia Power Electronics

Center (VPEC) In 1989 and became a Research

Associate in 1991 and a Research Scientist in 1994.

He is currently with the Virginia Power Technologies in Blacksburg. He has published more than 40 papers and holds two

U.S. patents. His research interests include high-frequency power conversion,

new converterhnverter topologies, power-factor correction circuits, distributed

power systems, piezo-electric transformers, and UPS systems.

The output capacitor ripple current is equivalent to the output

rectifier RMS current with the DC portion of the current

removed. Therefore, two intervals of integration have to be

considered

Integrating (30) and using the result of (17) yields (18). The

transformer secondary is in series with the output rectifier, so

their RMS currents are identical. Since the dc component of

current is present, we have

Integrating (31) and using the result of (17) yields (19).

Potrebbero piacerti anche

- Fly-Back Mode 150wDocumento17 pagineFly-Back Mode 150wanon_4880132Nessuna valutazione finora

- An 7517Documento9 pagineAn 7517MallickarjunaNessuna valutazione finora

- ZVSDocumento28 pagineZVS12BACAUNessuna valutazione finora

- IEEE journal explores active-clamp circuits for soft switching in flyback convertersDocumento8 pagineIEEE journal explores active-clamp circuits for soft switching in flyback convertersharshithreddyNessuna valutazione finora

- Comparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsDocumento5 pagineComparison and Simulation of Full Bridge and LCL-T Buck DC-DC Converter SystemsKrishnaveni Subramani SNessuna valutazione finora

- High Power Factor Soft SwitchedDocumento7 pagineHigh Power Factor Soft SwitchedMohan KrishnaNessuna valutazione finora

- ZvsDocumento29 pagineZvsSandy RonaldoNessuna valutazione finora

- ARCP Converter Enables Soft Switching Without Increased Device RatingsDocumento8 pagineARCP Converter Enables Soft Switching Without Increased Device RatingsAjit JainNessuna valutazione finora

- Topic 3 LynchDocumento26 pagineTopic 3 Lynchsunil251Nessuna valutazione finora

- DC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnDocumento10 pagineDC-DC Converter: Four Switches V V 2, Capacitive Turn-Off Snubbing, ZV Turn-OnRomitan AlexandraNessuna valutazione finora

- An222a DDocumento16 pagineAn222a DMario Plinio CrivelliNessuna valutazione finora

- An Introduction to Switched Mode Power Supply TopologiesDocumento21 pagineAn Introduction to Switched Mode Power Supply Topologiesseahate100% (1)

- FairchildDocumento17 pagineFairchildshounakroyNessuna valutazione finora

- AN848 DynamicDocumento9 pagineAN848 DynamicAnonymous QakmLc3kTINessuna valutazione finora

- DRSSTCDocumento7 pagineDRSSTCGabriel Droguett Olea100% (1)

- A Novel Analysis of ZeroDocumento9 pagineA Novel Analysis of ZerodineshpeterNessuna valutazione finora

- 135264ijsetr6989 1453Documento8 pagine135264ijsetr6989 1453wasabikikkomanNessuna valutazione finora

- Novel zero-current switching PWM converters minimize lossesDocumento6 pagineNovel zero-current switching PWM converters minimize lossescarlos_eqnNessuna valutazione finora

- Effect of Source InductanceDocumento10 pagineEffect of Source Inductancemeeravali_snNessuna valutazione finora

- Design and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCDocumento13 pagineDesign and Application For PV Generation System Using A Soft-Switching Boost Converter With SARCIJERDNessuna valutazione finora

- Leakage Flux TransformerDocumento5 pagineLeakage Flux TransformerVishnu PillaiNessuna valutazione finora

- Buck Converter AnalysisDocumento4 pagineBuck Converter AnalysisJan Rafael EusebioNessuna valutazione finora

- A New ZVZCS Isolated Dual Series Resonant DC-DCDocumento9 pagineA New ZVZCS Isolated Dual Series Resonant DC-DCFelipe Martins GuimarãesNessuna valutazione finora

- Dire Dawa University: Institute of TechnologyDocumento49 pagineDire Dawa University: Institute of TechnologyAsed ZakirNessuna valutazione finora

- Slup205 Transformer and Inductor DesignDocumento29 pagineSlup205 Transformer and Inductor DesignmirscrNessuna valutazione finora

- A Novel ZCS-PWM Flyback Converter With A Simple ZCS-PWM Commutation CellDocumento9 pagineA Novel ZCS-PWM Flyback Converter With A Simple ZCS-PWM Commutation CellSHIVIKA BISARIANessuna valutazione finora

- CUK ConverterDocumento4 pagineCUK Converterranjitheee1292Nessuna valutazione finora

- Zero Voltage Switching Active Clamp Buck-BoostDocumento10 pagineZero Voltage Switching Active Clamp Buck-Boostranjitheee1292Nessuna valutazione finora

- Zero-Voltage and Zero-Current Switching FullDocumento8 pagineZero-Voltage and Zero-Current Switching FullFrank GonzalezNessuna valutazione finora

- PWM DC-DC: Two-Switch Forward Soft-Switching Power ConverterDocumento2 paginePWM DC-DC: Two-Switch Forward Soft-Switching Power ConverterSweatha SajeevNessuna valutazione finora

- PLC Based Load Sharing On Slide ShareDocumento28 paginePLC Based Load Sharing On Slide ShareHemu Bhai PatelNessuna valutazione finora

- Line Inductance EffectDocumento21 pagineLine Inductance EffectAkhilesh JindalNessuna valutazione finora

- One-Quadrant Switched-Mode Power Converters: R. PetrocelliDocumento26 pagineOne-Quadrant Switched-Mode Power Converters: R. PetrocelliClaudiu UdrescuNessuna valutazione finora

- Shunt Reactor Switching Transients at High Compensation LevelsDocumento14 pagineShunt Reactor Switching Transients at High Compensation LevelsJames Ernes Llacza Carmelo100% (1)

- A Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationDocumento8 pagineA Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationJie99Nessuna valutazione finora

- Bidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsDocumento5 pagineBidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsPaulo UchihaNessuna valutazione finora

- Introduction To Switched Mode Power Supplies.: Fig.3.0.1 Typical SMPS Block DiagramDocumento17 pagineIntroduction To Switched Mode Power Supplies.: Fig.3.0.1 Typical SMPS Block DiagramPhenias ManyashaNessuna valutazione finora

- Three-phase Fly-back AC/DC Converter Resonant SnubberDocumento5 pagineThree-phase Fly-back AC/DC Converter Resonant SnubberKarthik KumarNessuna valutazione finora

- Family of Soft-Switching PWMDocumento7 pagineFamily of Soft-Switching PWMMohan KrishnaNessuna valutazione finora

- Zero-Voltage Switching Technique in DC/DC Converters: Abstruct-ADocumento12 pagineZero-Voltage Switching Technique in DC/DC Converters: Abstruct-ARushikeshKatkarNessuna valutazione finora

- P. C. Sen - Principles of Electric Machines 2edDocumento634 pagineP. C. Sen - Principles of Electric Machines 2edwilliancsm100% (1)

- ZCS-PWM Converter For Reducing Switching Losses: Subi SDocumento7 pagineZCS-PWM Converter For Reducing Switching Losses: Subi SInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- J'15 - Analysis, Design and Realisation of A Zero-Current Transition Pulse-Width Modulation Interleaved Boost Power Factor Correction Converter With A Zero-Current Transition Auxiliary CircuitDocumento9 pagineJ'15 - Analysis, Design and Realisation of A Zero-Current Transition Pulse-Width Modulation Interleaved Boost Power Factor Correction Converter With A Zero-Current Transition Auxiliary Circuit閒雲野鶴Nessuna valutazione finora

- An Improved ZVT-ZCT PWM DC-DC Boost Converter With Increased EfficiencyDocumento8 pagineAn Improved ZVT-ZCT PWM DC-DC Boost Converter With Increased EfficiencyDeepak NayakNessuna valutazione finora

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingDocumento8 pagineTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclaveNessuna valutazione finora

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocumento9 pagineHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNessuna valutazione finora

- A Novel Aeronautical Static Inverter With High Frequency Pulse DC Link PDFDocumento8 pagineA Novel Aeronautical Static Inverter With High Frequency Pulse DC Link PDFqiwatingNessuna valutazione finora

- Analysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck ConverterDocumento12 pagineAnalysis, Design and Implementation of Zero-Current-Switching Resonant Converter DC-DC Buck Converterdaber_huny20Nessuna valutazione finora

- Zero Voltage Switching Resonant Power Devices by Bill AndrecakDocumento28 pagineZero Voltage Switching Resonant Power Devices by Bill AndrecakRekhamtrNessuna valutazione finora

- INTRODUCTIONDocumento11 pagineINTRODUCTIONsiddharthr954Nessuna valutazione finora

- 03 Diode Rectifier ProjectDocumento11 pagine03 Diode Rectifier ProjectManju NathNessuna valutazione finora

- IJEDRCP1402017Documento4 pagineIJEDRCP1402017anas maraabaNessuna valutazione finora

- Resonant Converter Power Supply Design for Arc WeldingDocumento5 pagineResonant Converter Power Supply Design for Arc Weldingshado2010Nessuna valutazione finora

- 1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - KheraluwalaDocumento8 pagine1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - Kheraluwalahafizabu123Nessuna valutazione finora

- An-9067 LCC Failure ModeDocumento12 pagineAn-9067 LCC Failure ModeRon HuangNessuna valutazione finora

- SSCB 1Documento5 pagineSSCB 1KARTHIK NNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsDa EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNessuna valutazione finora

- Working With Panels: Use The Buttons at The Lower Right of The Workspace To Access Any PanelDocumento8 pagineWorking With Panels: Use The Buttons at The Lower Right of The Workspace To Access Any PanelGaetano GaetanoNessuna valutazione finora

- Writing A Research ProposalDocumento5 pagineWriting A Research ProposalYousef Al HashemiNessuna valutazione finora

- PCS BOM SampleDocumento3 paginePCS BOM SampleGaetano GaetanoNessuna valutazione finora

- Communications CablesDocumento1 paginaCommunications CablesGaetano GaetanoNessuna valutazione finora

- Proposal TemplateDocumento15 pagineProposal TemplateFaaiz ShabbirNessuna valutazione finora

- PCS BOM SampleDocumento3 paginePCS BOM SampleGaetano GaetanoNessuna valutazione finora

- 125 Useful English PhrasesDocumento11 pagine125 Useful English PhrasesMohan PereraNessuna valutazione finora

- Book of Knowledge WEB en 1601Documento233 pagineBook of Knowledge WEB en 1601Gaetano GaetanoNessuna valutazione finora

- Thesis A Roc'hDocumento228 pagineThesis A Roc'hGaetano GaetanoNessuna valutazione finora

- 1997 Microthermal ImagingDocumento7 pagine1997 Microthermal ImagingGaetano GaetanoNessuna valutazione finora

- UserManual 703Documento733 pagineUserManual 703Gaetano GaetanoNessuna valutazione finora

- Digital Control Applications in Power Electronics Lesson1Documento47 pagineDigital Control Applications in Power Electronics Lesson1Ahmed58seribegawanNessuna valutazione finora

- PSIM User Manual V9.0.2Documento216 paginePSIM User Manual V9.0.2Khaled ChaibainouNessuna valutazione finora

- Understanding Common & Differential Mode G019Documento7 pagineUnderstanding Common & Differential Mode G019Praveen CkNessuna valutazione finora

- L-34 (DP) (Pe) ( (Ee) Nptel)Documento12 pagineL-34 (DP) (Pe) ( (Ee) Nptel)Abhi NáyNessuna valutazione finora

- Gen Equations TojmransfDocumento12 pagineGen Equations TojmransfGaetano GaetanoNessuna valutazione finora

- Inductors - MultilayerDocumento5 pagineInductors - MultilayerGaetano GaetanoNessuna valutazione finora

- Inductors - MultilayerDocumento5 pagineInductors - MultilayerGaetano GaetanoNessuna valutazione finora

- Power SystemDocumento14 paginePower SystemGaetano Gaetano100% (1)

- High Input Voltage, Off-Line Flyback Switching Power Supply Using FSC Igbt (Sgl5N150Uf)Documento9 pagineHigh Input Voltage, Off-Line Flyback Switching Power Supply Using FSC Igbt (Sgl5N150Uf)Pascu AurelNessuna valutazione finora

- High Current Pulse GeneratorDocumento12 pagineHigh Current Pulse GeneratorTranminhvmi TranNessuna valutazione finora

- PsimDocumento162 paginePsim10118015Nessuna valutazione finora

- Power Electronics Guide in 40 CharactersDocumento17 paginePower Electronics Guide in 40 CharactersAdnankhan BangashNessuna valutazione finora

- Power Electronics Lecture 4: The MOSFET and The IGBTDocumento16 paginePower Electronics Lecture 4: The MOSFET and The IGBTSolayman Salindato MasoNessuna valutazione finora

- Power Semiconductor Devices PosterDocumento1 paginaPower Semiconductor Devices PosterSai Pranahita KulithalaiNessuna valutazione finora

- FGH75T65SHD: 650 V, 75 A Field Stop Trench IGBTDocumento9 pagineFGH75T65SHD: 650 V, 75 A Field Stop Trench IGBTРоман АлександровичNessuna valutazione finora

- Problems Chptrs 19-30Documento54 pagineProblems Chptrs 19-30Pawan NarayanNessuna valutazione finora

- Ee2304 Power Electronics Lab ManualDocumento49 pagineEe2304 Power Electronics Lab ManualSree GaneshNessuna valutazione finora

- Surescan SR Power Converter: Fault Investigation ManualDocumento107 pagineSurescan SR Power Converter: Fault Investigation Manualfauzy syaeful100% (1)

- IGBT Testing - A Technical OverviewDocumento2 pagineIGBT Testing - A Technical OverviewGalco IndustrialNessuna valutazione finora

- SGP02N120 SGD02N120, SGI02N120: Fast IGBT in NPT-technologyDocumento14 pagineSGP02N120 SGD02N120, SGI02N120: Fast IGBT in NPT-technologypserednickiNessuna valutazione finora

- SEMIKRON Technical Explanation CAL DiodesDocumento15 pagineSEMIKRON Technical Explanation CAL DiodesHemchand ImmaneniNessuna valutazione finora

- Multiple Choice QuestionsDocumento39 pagineMultiple Choice QuestionsSunil Gadekar80% (20)

- AC To AC ConversionDocumento6 pagineAC To AC ConversionTaniyaNessuna valutazione finora

- 18 (Da Chaobo) FACTS Application in ChinaDocumento132 pagine18 (Da Chaobo) FACTS Application in ChinaAmany HamdyNessuna valutazione finora

- Power Losses Analysis of Two-Levels and Three-Levels PWM Inverter Handling Reactive PowerDocumento7 paginePower Losses Analysis of Two-Levels and Three-Levels PWM Inverter Handling Reactive Powertichtruong77Nessuna valutazione finora

- Irgb 4062 DPBFDocumento13 pagineIrgb 4062 DPBFCarlos OliveiraNessuna valutazione finora

- Learn Discrete ComponentsDocumento2 pagineLearn Discrete ComponentsamitcrathodNessuna valutazione finora

- Power Lab Manual 7th Sem 2011 - BGSDocumento109 paginePower Lab Manual 7th Sem 2011 - BGSSumanth Sathyanarayana100% (1)

- DRV MV Air Cooled Catalog PDFDocumento104 pagineDRV MV Air Cooled Catalog PDFLaurentiu Catalin100% (1)

- X - Active Clamping Circuit With Status Feedback For HV-IGBTDocumento5 pagineX - Active Clamping Circuit With Status Feedback For HV-IGBTOsman T.Nessuna valutazione finora

- Generation of PWM Using Verilog in FPGA 11Documento7 pagineGeneration of PWM Using Verilog in FPGA 11Rajani kant tiwariNessuna valutazione finora

- Users Manual UNITROL 1000-PM40 PDFDocumento19 pagineUsers Manual UNITROL 1000-PM40 PDFAlexandre100% (1)

- Igbt Cm200dy (New)Documento4 pagineIgbt Cm200dy (New)GamarJanuzajNessuna valutazione finora

- Behavior Switching Losses and Efficiency Enhancement PotentialsDocumento19 pagineBehavior Switching Losses and Efficiency Enhancement PotentialsCrm LabsNessuna valutazione finora

- Power Loss Calculation in IGBT ModulesDocumento16 paginePower Loss Calculation in IGBT Modulestichtruong77Nessuna valutazione finora

- Data Sheet 1SD536F2-5SNA0800N330100: Single-Channel SCALE Plug-and-Play IGBT DriverDocumento6 pagineData Sheet 1SD536F2-5SNA0800N330100: Single-Channel SCALE Plug-and-Play IGBT Driverashkan emamiNessuna valutazione finora

- Generation of PWM Using Verilog in FPGA PDFDocumento7 pagineGeneration of PWM Using Verilog in FPGA PDFRajani kant tiwariNessuna valutazione finora