Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

FPGA Based QDR-II+ SRAM Controller

Caricato da

IOSRjournalTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

FPGA Based QDR-II+ SRAM Controller

Caricato da

IOSRjournalCopyright:

Formati disponibili

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

Volume 5, Issue 6, Ver. I (Nov -Dec. 2015), PP 07-12

e-ISSN: 2319 4200, p-ISSN No. : 2319 4197

www.iosrjournals.org

FPGA based QDR-II+ SRAM Controller

Abhilash Chadhar

National Institute of Electronics and Information Technology Calicut, Kerala, India

Abstract: The hike in internet usage globally and the ascending number of its users have ensued to high

demands for high speed data communication systems enriched with faster processors and high speed interfaces

to peripheral components. With the advent to QDR SRAMs these requirements of this evolving system are

fulfilled. The QDR SRAM enables the system to work on four times the bandwidth when compared to other

SRAM architectures. For proper functioning of these SRAMs we introduce a design of QDR II+ controller

which serves the purpose of translating memory requests issued by the hardware to which the RAM has been

interfaced, into data and control signals for the SRAM while complying to the timing requirements imposed by

the memory configurations.

Keywords: FPGA, QDR II+ memory, IP core, SoC, Verilog

I.

Introduction

With the rapid increase in the processor speed, system designers have used better speed management

techniques such as use of interleaving, burst mode and other high speed memory systems for accessing memory.

For fulfilling the need of high speed data management SRAM serve as a most likely option [5]. There as some

concrete reasons that justifies the use of SRAM in a system. These include speed; cost of memory, volatility and

features. Even the fastest DRAMs require approximately six to ten processor clock cycles to access the first

data. This results in mismatch of speeds of the processor and the DRAM which in turn results in slower system

with improper resource management. In such cases SRAMs emerges to be a better option which can operate at

speeds of 550 MHz and even beyond. They even provide access times and cycle times equal to clock cycles

used by the microprocessors. Thus these ultra fast SRAMs prove as better and effective alternatives over its

other RAM variants. The density of SRAM is not as higher as DRAM because number of transistors required in

for one SRAM cell is large as compared to DRAM cell hence in todays scenario (in terms of chip density)

where 4-Gbits DRAMs are available the largest SRAMs are 144-Mbits [14]. DRAM cells need to be refreshed

for proper operation while SRAM cells need not be refreshed due to its volatile nature. Hence they are available

for reading and writing cent percent of the time.

II.

Architecture of the SRAM

QDR-II+ SRAM memory device offers two architecture variants [2], [11], [12]; those are 2 word burst

and 4-word burst. Only 4-word burst architecture is discussed here. 4- Word memory device architecture

comprises of 4 array of 51218 SRAM. Unlike DDR SRAM, this memory device has two data ports .Address

port is of 19-bits and Data ports of 72-bits. Control Signals

,

,

are available with this memory

device.

is active low and asserted

Fig. 1 the logic block diagram or the architectural view of QDR + SRAM. It has been taken from CYPRESS

CY7C1263v18 datasheet.[11]

DOI: 10.9790/4200-05610712

www.iosrjournals.org

7 | Page

FPGA based QDR-II+ SRAM Controller

when the read operation is required.

is an active low control signal and it is asserted when write

operation has to be performed.

is provided a 0 (Active Low) in order to write the data into memory and if

it will be 1 the data will not be written into memory at the target address.

, when it is given 0 then DLL

present inside the memory device will get off and start to perform like QDR-1 SRAM memory. K and

are

input clock signal and complement of one another. CQ and

are two echo clocks and synchronized with Input

Clock K and respectively.

The objective of this design is to implement a controller in FPGA which allows all the operations in

QDRII+ SRAM. The design also contains a test module which contains data generators in the form of LFSRs

(Linear feedback shift register), a comparator and an address counter.

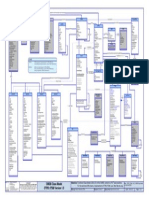

Fig. 2 The figure shows the hierarchy of the modules used in the program along with signals interacting with the

target device.

III.

Principle Of Operation

The design has been produced as per the standards of QDRII+ SRAMs which is provided in the table

1.1 Memory controller assigns the signals to QDRII+ SRAM based on the inputs from the system which are

memory requests. In our design the ALTMEMPHY IP core serves as the interface between the user logic and

the memory controller as well as between the memory controller and the QDR II+ SRAM [6],[12]. A

diagrammatic illustration of the top level scheme containing these interfaces has been clearly in the fig 1.2.

The principle behind the design is based on the timing characteristics of the SRAM device which gives

the information of the control, data path and acknowledgment signals. A FSM which appropriately changes the

states providing signals at required time acts as the heart of the controller. There are five states which properly

describe the working of the controller. The FSM is shown in fig 2 containing all those states with corresponding

inputs and outputs. The machine is a mealy model.

Initially the controller is at reset state, also it returns to reset state whenever reset is provided. At the

positive edge of the phy_clk it latches the write and read port select signals, these signals are active low. In our

design the controller is embedded with testbench which first writes to 100 locations and then reads them back in

order to compare whether the data is correctly written or not. Hence initially address counter is reset so that it

could start counting 100 addresses then the controller initiates writing when it senses wps_n as a low. It latches

the lower data word of D at the same instant. At the falling edge of the phy_clk the address is latched along with

upper data word on D. This completes the write cycle.

The quad data rate is achieved by operating two ports at dual data rate. This is the reason why

throughput is enhanced in QDR SRAMs. The controller asserts read and write control signals at different ports

hence the time required for bus turnaround is reduced because same bus is not used for write and read. This

results in increase of bandwidth in QDR SRAMs as compared to DDR SRAMs or ordinary SRAMs. Data flow

into the SRAM is through the write port and out of it is through the read port. These devices multiplex the

address inputs to minimize the number of address pins required.

When the controller is in write state it latches 18-bit word at every rising edge of phyclk, another 18-bit

word is latched at the negative edge of the clock. This process continues for one more cycle where a total of 72

bits are obtained, this makes the ports busy for two clock cycles hence the write operation cannot be accessed

two consecutive cycles. This is the reason why there is an intermediate state. When the address counter reaches

100 addresses it resets the address counter and lfsr. Now if rps_n is active it will start read operation else it will

wait at the intermediate state. In the read state 4 array accesses of 512x18 bits are performed in a burst of four

DOI: 10.9790/4200-056XXXXX

www.iosrjournals.org

8 | Page

FPGA based QDR-II+ SRAM Controller

subsequent 18 bit data words. On the following two falling edges of phy_clk after detection of rps_n active

leads to driving of lower 18 bit data on to corresponding Q, at the next subsequent rising edges of phy_clk the

data is driven out to Q until all four 18bit data words are given to Q.

The read access is similar to write operation contains four 18 bit words which take two cycles to read.

Hence read requests also cannot be made on 2 consecutive cycles. This is the reason why there is an

intermediate state. When the address counter reaches 100 addresses it resets the address counter and lfsr. Now if

rps_n is active it will start read operation else it will wait at the intermediate state. In the read state 4 array

accesses of 512x18 bits are performed in a burst of four subsequent 18 bit data words. On the following two

falling edges of phy_clk after detection of rps_n active leads to driving of lower 18 bit data on to corresponding

Q, at the next subsequent rising edges of phy_clk the data is driven out to Q until all four 18bit data words are

given to Q.

The read access is similar to write operation contains four 18 bit words which take two cycles to read.

Hence read requests also cannot be made on 2 consecutive cycles. After the completion of read operation it goes

to idle state from where it could again start writing as per the command issued.

IV.

Core I/O Diagram (Fig 4)

The core contains the following:

LFSRs (Linear Feedback Shift Registers)

Each one is of 18 bit. Total 8 LFSRs are used. Four are used to for generation of data to be written, rest of the

four are used for read comparison.

COMPARATOR

It is used to compare whether the read-back data is same as written data in the memory. It gives output pass or

fail based on comparison.

DOI: 10.9790/4200-056XXXXX

www.iosrjournals.org

9 | Page

FPGA based QDR-II+ SRAM Controller

Control logic (FSM)

Most essential part of the control that issues control signals based on the FSM. The FSM has 5 states: RESET,

READ, WRITE, INTERMEDIATE (state between read and write) and IDLE state

Address Counter

It gives 19 bit data output and counts up to 524287. It is used to generate address to which data is to be written

or from where it has to be read.

Most of the pins have been dealt with earlier. Remaining are: CTL_USR_MODE_RDY which is a high after the

resynchronization phase is over after this signal only the user data can be written or read from the RAM.

CTL_MEM_RDATA_VALID is assigned high when the controller is in read mode else it is in low condition.

Resource utilization:

Parameter

Combinational ALUTs

Memory ALUTs

Dedicated logic registers

Total registers

Total pins

Total block memory bits

DSP block 18-bit elements

Total PLLs

Total DLLs

Result

908 / 113,600 ( 1 % )

72 / 56,800 ( < 1 % )

4,041 / 113,600 ( 4 % )

4177

75 / 744 ( 10 % )

528,384 / 5,630,976 ( 9 % )

0 / 384 ( 0 % )

1 / 8 ( 13 % )

1 / 4 ( 25 % )

Power Analysis Result:

Parameter

Family

Device

Total Thermal Power Dissipation

Core Dynamic Thermal Power

Dissipation

Core

Static

Thermal

Power

Dissipation

I/O Thermal Power Dissipation

DOI: 10.9790/4200-056XXXXX

Result

Stratix III

EP3SL150F1152C2

1434.64 mW

107.57 mW

598.50 mW

728.58 mW

www.iosrjournals.org

10 | Page

FPGA based QDR-II+ SRAM Controller

V.

Hardware Test Results

Fig.6. The above signal Tap output illustrates read state of the controller where comparison is being performed

of the earlier written data into the the memory with currently read data through a comparator module which is a

part of the test-bench .Wherever the read data is same as LFSR data to be compared the pnf(pass and fail) signal

becomes high

Fig. 5. The signal Tap output shows that the controller is switching from write state to read state. The write port

select and read port select changing accordingly

DOI: 10.9790/4200-056XXXXX

www.iosrjournals.org

11 | Page

FPGA based QDR-II+ SRAM Controller

VI.

Potential Applictaions

It is used along with DSP processor memories, cache memories, routers, ATM switches, packet memories, lookup tables etc.

VII.

Conclusion And Future Work

As QDR II + SRAMs are playing a significant role in determining performance of the internet hence it

is very important to consider impact of a fast controller in present scenario. The design presented by us is a

simplistic model that serves the basic requirements of a memory controller. Hence it is incapable to detect if

sometimes the memory gives incorrect results. As our future plan, work could be done in improving the data

correction ability of the controller using various algorithms. These techniques will be useful in applications

where correct retrieval of data is very important like the space applications. Another area is that, present

controller is device specific. It could be made as a universal QDRII+ SRAM controller for all the devices or at

least the same family of devices.

References

[1].

[2].

[3].

[4].

[5].

[6].

[7].

[8].

[9].

[10].

[11].

[12].

[13].

[14].

[15].

[16].

[17].

[18].

[19].

[20].

Altera Corporation, AN 461: Design Guidelines for Implementing QDRII+ and QDRII SRAM Interfaces in Stratix III and Stratix IV

Devices. February 2010.

Altera Corporation, AN 326: Interfacing QDRII+ & QDRII with Stratix II, Stratix II GX, Stratix, & Stratix GX Devices.

Cypress Semiconductor Corporation.CY7C1302V25 9-Mb Pipelined SRAM with QDR Architecture. May 2008.

Steven M. Rubin, Computer Aids for VLSI Design, Addison-Wesley, 1987.

Jack Truong. (March 31st, 2005). Evolution of Network Memory. [Online]. Available: http://www.jedex.org/

Markus Ringhofer, Design and Implementation of a Memory Controller for Real-Time Applications, Institut fur Technische

Informatik Technische Universitat Graz

P Sundararajan. High Performance Computing Using FPGAs. Xilinx White Paper: FPGAs, 2010 - china.zylinks.com

M. Morris Mano, Digital Design, Prentice-Hall, 1984.

Granberg, Handbook of Digital Techniques for High-Speed Design.. Low price edition.Patparganj, Delhi,India. Pearson Education

India,ch 13 and ch 16.

Altera Corporation, AN 133: QDR SRAM Controller Reference Design. December 2000, ver. 1.0

Altera Corporation. AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices. May 2004, ver. 1.0

Altera Corporation. ALTERA External Memory PHY Interface (ALTMEMPHY) Mega function User Guide. January 2010

Simulating DRAM controllers for future system architecture exploration.

W. Wolf, A. Jerraya, and G. Martin, Multiprocessor system-on-chip (mpsoc) technology, Computer-Aided Design of Integrated

Circuits and Systems, IEEE Transactions on, vol. 27, no. 10, pp. 17011713, Oct. 2008.

M. W. Naouar, A. A. Naassani, E. Monmasson, and I. Slama-Belkhodja, FPGA-based predictive current for synchronous machine

speed drive, IEEE Trans. Power Electron., vol. 23, no. 4, pp. 21152126, July 2008.

Cypress Perform . 36-Mbit QDR II SRAM Four-Word Burst Architecture [Online].Available:http://www.cypress.com/?rID=47422

Cypress

Perform.

144-Mbit

QDR

II

SRAM

Two-Word

Burst

Architecture [Online].

Available:

http://www.cypress.com/?docID=48535

Cypress Semiconductor Corporation (Jayasree N / Pritesh M.), PLL Considerations in QDR -II/II+/DDR-II/II+SRAMs.

QDR Consortium. QDR Product Family [Online]. Available: http://www.qdrconsortium.org/qdr-product-family.htm

Anuj Chakrapani. QDR SRAM and RLDRAM: A Comparative Analysis. Network Systems: Design Line, Cypress Semiconductor

Corp, 2010.

DOI: 10.9790/4200-056XXXXX

www.iosrjournals.org

12 | Page

Potrebbero piacerti anche

- Socio-Ethical Impact of Turkish Dramas On Educated Females of Gujranwala-PakistanDocumento7 pagineSocio-Ethical Impact of Turkish Dramas On Educated Females of Gujranwala-PakistanInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- "I Am Not Gay Says A Gay Christian." A Qualitative Study On Beliefs and Prejudices of Christians Towards Homosexuality in ZimbabweDocumento5 pagine"I Am Not Gay Says A Gay Christian." A Qualitative Study On Beliefs and Prejudices of Christians Towards Homosexuality in ZimbabweInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Assessment of The Implementation of Federal Character in Nigeria.Documento5 pagineAssessment of The Implementation of Federal Character in Nigeria.International Organization of Scientific Research (IOSR)Nessuna valutazione finora

- An Evaluation of Lowell's Poem "The Quaker Graveyard in Nantucket" As A Pastoral ElegyDocumento14 pagineAn Evaluation of Lowell's Poem "The Quaker Graveyard in Nantucket" As A Pastoral ElegyInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- A Review of Rural Local Government System in Zimbabwe From 1980 To 2014Documento15 pagineA Review of Rural Local Government System in Zimbabwe From 1980 To 2014International Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Relationship Between Social Support and Self-Esteem of Adolescent GirlsDocumento5 pagineRelationship Between Social Support and Self-Esteem of Adolescent GirlsInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- A Proposed Framework On Working With Parents of Children With Special Needs in SingaporeDocumento7 pagineA Proposed Framework On Working With Parents of Children With Special Needs in SingaporeInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Attitude and Perceptions of University Students in Zimbabwe Towards HomosexualityDocumento5 pagineAttitude and Perceptions of University Students in Zimbabwe Towards HomosexualityInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- The Role of Extrovert and Introvert Personality in Second Language AcquisitionDocumento6 pagineThe Role of Extrovert and Introvert Personality in Second Language AcquisitionInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- The Impact of Technologies On Society: A ReviewDocumento5 pagineThe Impact of Technologies On Society: A ReviewInternational Organization of Scientific Research (IOSR)100% (1)

- Comparative Visual Analysis of Symbolic and Illegible Indus Valley Script With Other LanguagesDocumento7 pagineComparative Visual Analysis of Symbolic and Illegible Indus Valley Script With Other LanguagesInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Investigation of Unbelief and Faith in The Islam According To The Statement, Mr. Ahmed MoftizadehDocumento4 pagineInvestigation of Unbelief and Faith in The Islam According To The Statement, Mr. Ahmed MoftizadehInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Importance of Mass Media in Communicating Health Messages: An AnalysisDocumento6 pagineImportance of Mass Media in Communicating Health Messages: An AnalysisInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Edward Albee and His Mother Characters: An Analysis of Selected PlaysDocumento5 pagineEdward Albee and His Mother Characters: An Analysis of Selected PlaysInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Human Rights and Dalits: Different Strands in The DiscourseDocumento5 pagineHuman Rights and Dalits: Different Strands in The DiscourseInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- The Lute Against Doping in SportDocumento5 pagineThe Lute Against Doping in SportInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Beowulf: A Folktale and History of Anglo-Saxon Life and CivilizationDocumento3 pagineBeowulf: A Folktale and History of Anglo-Saxon Life and CivilizationInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Topic: Using Wiki To Improve Students' Academic Writing in English Collaboratively: A Case Study On Undergraduate Students in BangladeshDocumento7 pagineTopic: Using Wiki To Improve Students' Academic Writing in English Collaboratively: A Case Study On Undergraduate Students in BangladeshInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Role of Madarsa Education in Empowerment of Muslims in IndiaDocumento6 pagineRole of Madarsa Education in Empowerment of Muslims in IndiaInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Classical Malay's Anthropomorphemic Metaphors in Essay of Hikajat AbdullahDocumento9 pagineClassical Malay's Anthropomorphemic Metaphors in Essay of Hikajat AbdullahInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- An Exploration On The Relationship Among Learners' Autonomy, Language Learning Strategies and Big-Five Personality TraitsDocumento6 pagineAn Exploration On The Relationship Among Learners' Autonomy, Language Learning Strategies and Big-Five Personality TraitsInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Transforming People's Livelihoods Through Land Reform in A1 Resettlement Areas in Goromonzi District in ZimbabweDocumento9 pagineTransforming People's Livelihoods Through Land Reform in A1 Resettlement Areas in Goromonzi District in ZimbabweInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Kinesics, Haptics and Proxemics: Aspects of Non - Verbal CommunicationDocumento6 pagineKinesics, Haptics and Proxemics: Aspects of Non - Verbal CommunicationInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Women Empowerment Through Open and Distance Learning in ZimbabweDocumento8 pagineWomen Empowerment Through Open and Distance Learning in ZimbabweInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Motivational Factors Influencing Littering in Harare's Central Business District (CBD), ZimbabweDocumento8 pagineMotivational Factors Influencing Littering in Harare's Central Business District (CBD), ZimbabweInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Design Management, A Business Tools' Package of Corporate Organizations: Bangladesh ContextDocumento6 pagineDesign Management, A Business Tools' Package of Corporate Organizations: Bangladesh ContextInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Substance Use and Abuse Among Offenders Under Probation Supervision in Limuru Probation Station, KenyaDocumento11 pagineSubstance Use and Abuse Among Offenders Under Probation Supervision in Limuru Probation Station, KenyaInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Designing of Indo-Western Garments Influenced From Different Indian Classical Dance CostumesDocumento5 pagineDesigning of Indo-Western Garments Influenced From Different Indian Classical Dance CostumesIOSRjournalNessuna valutazione finora

- Micro Finance and Women - A Case Study of Villages Around Alibaug, District-Raigad, Maharashtra, IndiaDocumento3 pagineMicro Finance and Women - A Case Study of Villages Around Alibaug, District-Raigad, Maharashtra, IndiaInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- A Study On The Television Programmes Popularity Among Chennai Urban WomenDocumento7 pagineA Study On The Television Programmes Popularity Among Chennai Urban WomenInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Everything You Can Do in Power PointDocumento1 paginaEverything You Can Do in Power Pointbiotech181985Nessuna valutazione finora

- Offline Charts in The New MQL4 - MQL4 ArticlesDocumento11 pagineOffline Charts in The New MQL4 - MQL4 Articlestung tranNessuna valutazione finora

- Export Sibelius Score As PDFDocumento2 pagineExport Sibelius Score As PDFTim0% (1)

- WordPress Security GuideDocumento13 pagineWordPress Security GuideNeil TNessuna valutazione finora

- Sri Harsha Chayanam ResumeDocumento4 pagineSri Harsha Chayanam ResumeZakeer HussainNessuna valutazione finora

- ATOM Install Notes ReadmeDocumento2 pagineATOM Install Notes ReadmeRysul KabirNessuna valutazione finora

- Microsoft Official Course: Planning and Configuring Messaging Client ConnectivityDocumento39 pagineMicrosoft Official Course: Planning and Configuring Messaging Client ConnectivitySheriff deenNessuna valutazione finora

- Viraj Vilas Bankar ResumeDocumento1 paginaViraj Vilas Bankar ResumeRaviraj BankarNessuna valutazione finora

- Enhanced Mitigation Experience Toolkit 4.0: User GuideDocumento41 pagineEnhanced Mitigation Experience Toolkit 4.0: User Guidejegreen3Nessuna valutazione finora

- Unit IIDocumento21 pagineUnit IISH GamingNessuna valutazione finora

- 56667756423Documento2 pagine56667756423ArmandoAndreNessuna valutazione finora

- Otrs Itsm Datenmodell - DesbloqueadoDocumento1 paginaOtrs Itsm Datenmodell - DesbloqueadoLuis SamaniegoNessuna valutazione finora

- Micca Speck G2 User's Manual: Got A Question or Need Help?Documento28 pagineMicca Speck G2 User's Manual: Got A Question or Need Help?hhcorreavNessuna valutazione finora

- ChangelogDocumento26 pagineChangelogGhatNessuna valutazione finora

- Unité Learn The Benefits of APIs - Salesforce TrailheadDocumento6 pagineUnité Learn The Benefits of APIs - Salesforce TrailheadPascal JaramilloNessuna valutazione finora

- Cloud Computing - Lab 5Documento2 pagineCloud Computing - Lab 5Gigi BetonNessuna valutazione finora

- Welcome To Microsoft Teams: Chat-Based Collaboration PlatformDocumento23 pagineWelcome To Microsoft Teams: Chat-Based Collaboration PlatformMatta KongNessuna valutazione finora

- Project Srs Document: Submitted byDocumento7 pagineProject Srs Document: Submitted byAnshu GuptaNessuna valutazione finora

- Application BrokerDocumento27 pagineApplication BrokerRoberto Hernandez AmecaNessuna valutazione finora

- How To Add To Advanced Search Using Application DesignerDocumento10 pagineHow To Add To Advanced Search Using Application DesignerDenisse LeyvaNessuna valutazione finora

- List of Simtel.Net authorized mirror sitesDocumento2 pagineList of Simtel.Net authorized mirror sitestedozallennNessuna valutazione finora

- How To Completely Uninstall PostgreSQL - ObjectRocketDocumento8 pagineHow To Completely Uninstall PostgreSQL - ObjectRocketHenrique DevidéNessuna valutazione finora

- Basic Snort/MySQL Install on FreeBSD 4.4Documento7 pagineBasic Snort/MySQL Install on FreeBSD 4.4Rossana Ribeiro Moura VianaNessuna valutazione finora

- Starting Out With Programming Logic & Design - Chapter15 - GUI ApplicationsDocumento13 pagineStarting Out With Programming Logic & Design - Chapter15 - GUI ApplicationsAndrew CartsNessuna valutazione finora

- Berkeley Multimedia WorkshopDocumento7 pagineBerkeley Multimedia WorkshopVisual EditorsNessuna valutazione finora

- Song Name, Singer: Ningilona Paalapuntha Lyrics (From "Dorasaani"..Documento3 pagineSong Name, Singer: Ningilona Paalapuntha Lyrics (From "Dorasaani"..sarjuNessuna valutazione finora

- Zend - Practicetest.200 710.v2017!06!28.by - Elena.41qDocumento22 pagineZend - Practicetest.200 710.v2017!06!28.by - Elena.41qsergiolnsNessuna valutazione finora

- Documentation To Connect A Simple Web App To Wp-Rest ApiDocumento17 pagineDocumentation To Connect A Simple Web App To Wp-Rest ApiAdegoke BestmanNessuna valutazione finora

- ErrorDocumento4 pagineErrorlvzm1Nessuna valutazione finora

- Create A PivotTable To Analyze Worksheet Data - Microsoft Support2Documento4 pagineCreate A PivotTable To Analyze Worksheet Data - Microsoft Support2rajonirinaNessuna valutazione finora