Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Transconductor de Nauta

Caricato da

Diego AlejandroDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Transconductor de Nauta

Caricato da

Diego AlejandroCopyright:

Formati disponibili

2.1.

TRANSCONDUCTOR DE NAUTA

2.1.1. Fundamentos

Para la realizacin de filtros continuos de alta frecuencia MOS, se han

realizado muchas implementaciones usando integradores basados en

transconductores y capacidades para poder realizar integradores a alta

frecuencia. Y sin embargo se consiguen frecuencias de corte del orden de

del Megahercio. La propuesta que se describe a continuacin se basa en

un integrador implementado con

transconductor cargado con una

capacidad.

Uno de los principales problemas en filtros activos de alta frecuencia es el

error de fase en los integradores. Los factores de calidad Q de los polos y

ceros en el filtro son muy sensibles a la fase de los integradores en las

frecuencias de los polos y ceros. Para evitar eso se precisara una

ganancia DC lo suficientemente grande, mientras que las frecuencias de

los polos y ceros parsitos est por encima de de la frecuencia de corte de

los filtros para mantener las fase en -90. Esto implica una gran ganancia

DC y que los polos parsitos estn del orden de 100 veces por encima de

lo frecuencia de corte.

Se proponen dos tcnicas para conseguir esta combinacin de alta

ganancia DC y gran ancho de banda:

a. Si el elemento de transconductancia no tiene nodos internos, no

tendr polos ni ceros parsitos influenciando la funcin de transferencia.

b. Se puede incrementar la ganancia DC cargando al

transconductor con una resistencia negativa que compense la

resistencia de salida. Esto adems puede no necesitar un nodo

interno.

Una combinacin de estas dos tcnicas para implementar el

transconductor darn tericamente una ganancia DC y un ancho de banda

infinitos.

2.1.2.

Conversin V-I

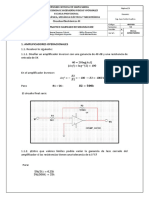

Segn el esquema del inversor tpico (a). Las intensidades de los

transistores de canal n y de canal p en saturacin son:

I dn =

I dp =

n

2

p

2

(V

(V

Vtn )

gsn

V pn )

gsp

con n =

con p =

nCoxWn

Ln

p CoxW p

Lp

Ilustracin 1: (a) Inversor simple.(b) Generacin de la tensin de

modo comn. (c) Versin balanceada. (d) Integrador de nauta

Entonces la intensidad de salida del inversor simple se puede escribir

como

I out = I dn I dp = a(Vin Vtn ) + bVin + c

2

con

a=

1

( n p )

2

b = p (Vdd Vtn + Vtp )

c=

1

p Vtn 2 (Vdd + Vtp )2

2

Suponiendo que todos los dispositivos funcionan en inversin fuerte y en

saturacin. Si n p , es decir, a 0 , la conversin V-I no ser linear,

apareciendo un trmino cuadrtico, que podra ser cancelado si se usa una

estructura balanceada.

La intensidad de salida ser nula cuando Vin = Vc , con:

Vc =

Vdd Vtn + Vtp

n

1+

p

+ Vtn

La figura 1(c) muestra la versin balanceada del circuito de la figura 1(a).

Los dos inversores son excitados con una tensin diferencial Vid centrada

en torno a la tensin de modo comn Vc . Las corrientes de salida I 01 e

I 02 pueden restarse para obtener la intensidad de salida I od :

1

1

I o1 = a Vc Vtn + Vid + bVc + Vid + c

2

2

2

1

1

I o 2 = aVc Vtn + Vid + b Vc Vid + c

2

2

2

2

1

1

I o1 I o 2 = a Vc Vtn + Vid Vc Vtn Vid + bVid

2

2

O tambin:

I o1 I o 2 = Vid (b + 2a (Vc Vtn )) = Vid ( p (Vdd Vc Vtp ) + n (Vc Vtn ))

Por lo tanto, se puede ver que la corriente de salida es lineal con la

tensin diferencial de entrada. Usando la expresin de Vc , la salida

quedara:

I od = I o1 I o 2 = Vid (Vdd Vtn + Vtp ) n p = Vid gm d

La transconductancia diferencial es lineal, incluso con inversores no

lineales. Para reducir las corrientes de salida de modo comn, n tiene

que ser muy parecida a p . Adems cabe destacar que gmd puede ser

sintonizada variando Vdd . El esquemtico completo de la propuesta es el

de la figura 1(d). Consiste en 6 inversores, con la misma alimentacin (por

ahora). La conversin V-I se lleva a cavo en los inversores 1 y 2, mientras

que el resto del circuito nos ayudar a controlar el modo comn.

2.1.3. Control del modo comn y mejora de la ganancia DC

El nivel del modo comn de las tensiones de salida Vo1 y Vo 2 se controla

con los inversores 3 a 6. Los inversores 4 y 5 funcionan como resistencias

entre los nodos de salida y el nivel de la tensin de nodo-comn Vc . Los

valores de esas resistencias son 1 gm4 y 1 gm5 respectivamente. Al

mismo tiempo los inversores 3 y 6 inyectan corrientes de valores

gm3 (Vc Vo1 ) y gm6 (Vc Vo 2 ) en ambas resistencias.

El resultado para el modo comn de las salidas es que el nodo Vo1

quedara cargado virtualmente con una resistencia de 1 ( gm5 + gm6 ) , y

que el Vo 2 es cargado con otra resistencia 1 ( gm3 + gm4 ) . Para seales

diferenciales de salida, el nodo Vo1 se carga con una resistencia de

1 ( gm5 gm6 ) y el Vo 2 con 1 ( gm4 gm3 ) . Si los cuatro inversores tienen

las mismas alimentaciones y estn perfectamente igualados, todas las

gms sern iguales. Por lo tanto el subcircuito formado por los inversores 3

a 6 forma una carga de resistividad baja para seales de modo comn y de

alta resistividad para seales diferenciales, consiguiendo controlar el modo

comn.

Nodo de Salida

Resistencia de modo

comn

Resistencia

Diferencial

Vo1

1 ( gm5 + gm6 )

1 ( gm5 gm6 )

Vo 2

1 ( gm3 + gm4 )

1 ( gm4 gm3 )

Tabla 1. Resistencias diferenciales y de modo comn vistes en los nodos de salida.

La ganancia DC de un inversor hecho con un transconductor como el

descrito puede ser incrementada cargando los inversores diferenciales 1 y

2 con una resistencia negativa. Eligiendo gm3 > gm4 , gm5 = gm4

y

gm3 = gm6 .

Esta

resistencia

negativa

de

valor

1 gm = 1 ( gm4 gm3 ) = 1 (gm5 gm6 ) se implementa fcilmente sin aadir

nodos extra al circuito. De este modo los inversores 4 y 5 pueden ser algo

menores que los inversores 3 y 6.

Para ser ms exacto en la respuesta, la ganancia DC puede ser

sintonizada usando una nueva tensin de alimentacin Vdd sobre los

inversores 4 y 5. De este modo, y si los transistores de estos inversores

estn suficientemente emparejados, la ganancia tericamente podra

hacerse infinita. En la realidad esa ganancia DC est limitada por el

desapareamiento. Se puede demostrar que la ganancia DC es igual al

valor recproco de del error relativo de la transconductancia debida al

desapareamiento. En conclusin se puede decir que eligiendo gm3 y gm6

mayores que gm4 y que gm5 , se conseguir un incremento significativo de

la ganancia DC sin afectar al ancho de banda.

Potrebbero piacerti anche

- Amplificadores DiscretosDocumento51 pagineAmplificadores DiscretosJalimRoye100% (1)

- Tema 2. Amplificadores de Varias Etapas y Amplificador DiferencialDocumento16 pagineTema 2. Amplificadores de Varias Etapas y Amplificador DiferencialXavier GualánNessuna valutazione finora

- Amplificadores de InstrumentaciónDocumento17 pagineAmplificadores de InstrumentaciónAlan DzipirisNessuna valutazione finora

- Amplificador DiferencialDocumento4 pagineAmplificador DiferencialDayber CruzNessuna valutazione finora

- Informe Final 1 Experiencia n0 1configuracion en CascadaDocumento15 pagineInforme Final 1 Experiencia n0 1configuracion en CascadaYOSVIN KEVIN GONZALES ANTICONANessuna valutazione finora

- Modulador 7Documento9 pagineModulador 7juanNessuna valutazione finora

- Rectificador Monofásico de Onda Completa ControladoDocumento14 pagineRectificador Monofásico de Onda Completa ControladoJose Alfredo MartinezNessuna valutazione finora

- Amplificador MultietapaDocumento8 pagineAmplificador MultietapaDiana Rodriguez ZavaletaNessuna valutazione finora

- Circuitos MultietapaDocumento12 pagineCircuitos MultietapaOsvaldo Meli0% (1)

- Rectificadores BifásicosDocumento11 pagineRectificadores BifásicosIsaac TellezNessuna valutazione finora

- Transistores JfetDocumento14 pagineTransistores JfetNeiraCariasDanielNessuna valutazione finora

- Final MagalyDocumento5 pagineFinal MagalyJuan A LópezNessuna valutazione finora

- Configuracion en CascadaDocumento13 pagineConfiguracion en CascadaJefferson YllaconzaNessuna valutazione finora

- Laboratorio 1 PDFDocumento24 pagineLaboratorio 1 PDFWaldir UmasiNessuna valutazione finora

- Rectificador A Diodos Con Linea Trifasica Conversor Ac A DC Grupo 6Documento24 pagineRectificador A Diodos Con Linea Trifasica Conversor Ac A DC Grupo 6David Ajhuacho Inca0% (1)

- Informe Final-Simetria ComplementariaDocumento11 pagineInforme Final-Simetria ComplementariaAngel LaurelNessuna valutazione finora

- Laboratorio N1 PDFDocumento4 pagineLaboratorio N1 PDFPool Ankori QuilcaNessuna valutazione finora

- Clase5 IDocumento20 pagineClase5 Irvh164Nessuna valutazione finora

- Examen de ElectrónicaDocumento3 pagineExamen de Electrónicastevennazare22100% (1)

- Op Amp 2Documento15 pagineOp Amp 2Carlos Enrique Salazar MuñozNessuna valutazione finora

- Graficas de TransistoresDocumento19 pagineGraficas de TransistoresnetbomNessuna valutazione finora

- Analisis en CascadaDocumento6 pagineAnalisis en CascadaHV RicardoNessuna valutazione finora

- Ecuación de Lagrange - Capitulo 16Documento12 pagineEcuación de Lagrange - Capitulo 16Juan Fabian MoralesNessuna valutazione finora

- Conexiones Con Varios TransistoresDocumento12 pagineConexiones Con Varios TransistoresRoberto Rocca JuárezNessuna valutazione finora

- Amplificadores OeracionalesDocumento6 pagineAmplificadores OeracionalesDaniel GiraldoNessuna valutazione finora

- Configuracion CascadaDocumento6 pagineConfiguracion CascadaOmar Minaya FerruzoNessuna valutazione finora

- Problemas Resueltos de Circuitos Electrnicos IIDocumento27 pagineProblemas Resueltos de Circuitos Electrnicos IIRicardoGonzales100% (1)

- Practica # 2 - Rectificador Monofasico de Onda Completa - Toma Central y Con Puente RectificadorDocumento13 paginePractica # 2 - Rectificador Monofasico de Onda Completa - Toma Central y Con Puente Rectificadormega235235Nessuna valutazione finora

- Amplificadores DiferencialesDocumento6 pagineAmplificadores DiferencialesAngel PaulNessuna valutazione finora

- INF. Final Lab 1 PDFDocumento11 pagineINF. Final Lab 1 PDFcarlos ramirezNessuna valutazione finora

- Problemas Resueltos Con OpampDocumento24 pagineProblemas Resueltos Con OpampLourdes AquinoNessuna valutazione finora

- Amp-Op Como Seguidor y Comparador de Voltaje PDFDocumento16 pagineAmp-Op Como Seguidor y Comparador de Voltaje PDFdavidcder90Nessuna valutazione finora

- Laboratorio 3.1Documento18 pagineLaboratorio 3.1ANGEL MAURICIO SARMIENTO ZARZOSANessuna valutazione finora

- Reporte de Práctica 9Documento13 pagineReporte de Práctica 9Ulises GarcíaNessuna valutazione finora

- Corriente en CascadaDocumento8 pagineCorriente en CascadaMarko Montalban MonteroNessuna valutazione finora

- Manual de Practicas - Amplificadores OperacionalesDocumento105 pagineManual de Practicas - Amplificadores OperacionalesLuis Armando Pulido García100% (2)

- Rectificadores MonofasicosDocumento5 pagineRectificadores Monofasicospaujose90Nessuna valutazione finora

- Reguladores y AmplificadoresDocumento10 pagineReguladores y AmplificadoresRonald Ayala ValeroNessuna valutazione finora

- Trabajo #4Documento4 pagineTrabajo #4JUAN ESTEBAN ACOSTA GAMBOANessuna valutazione finora

- La Configuración CascodeDocumento5 pagineLa Configuración CascodeJose LopezNessuna valutazione finora

- Procedimiento Práctico Multiplicadores de VoltajeDocumento4 pagineProcedimiento Práctico Multiplicadores de Voltajemac3132Nessuna valutazione finora

- Circuitos Electrónicos 2-Laboratorio AlvaDocumento9 pagineCircuitos Electrónicos 2-Laboratorio AlvaANGEN CSNessuna valutazione finora

- Amplificacion UV DCDocumento12 pagineAmplificacion UV DCRoberto CastilloNessuna valutazione finora

- Trabajo II FaseDocumento26 pagineTrabajo II FaseGabriel Llerena Quenaya100% (1)

- Nuevo Documento de Microsoft WordDocumento13 pagineNuevo Documento de Microsoft WordJesus Gallardo RamirezNessuna valutazione finora

- Ejemplo de Parcial - Electrónica Analógica I - Cátedra 2017 UNSAMDocumento7 pagineEjemplo de Parcial - Electrónica Analógica I - Cátedra 2017 UNSAMalio0oNessuna valutazione finora

- CS ElectronicaDocumento12 pagineCS ElectronicaMartin CazunNessuna valutazione finora

- Amplificador DiferencialDocumento28 pagineAmplificador DiferencialEsttyward Cuellar VenturaNessuna valutazione finora

- Tarea 2 Lab de Electrónica II Isaias Primera v28177287Documento12 pagineTarea 2 Lab de Electrónica II Isaias Primera v28177287Gabriel PrimeraNessuna valutazione finora

- Informe n8 IncompletoDocumento13 pagineInforme n8 IncompletoLidia Ayala CentenoNessuna valutazione finora

- Lab Amplificador DiferencialDocumento7 pagineLab Amplificador DiferencialArmando Alvarado YucraNessuna valutazione finora

- 2.modelos de Examen Resuelto Unidad IIIDocumento9 pagine2.modelos de Examen Resuelto Unidad IIIErick HernandezNessuna valutazione finora

- Reporte Electronica 05Documento12 pagineReporte Electronica 05davidcder90Nessuna valutazione finora

- Rectificador ControladoDocumento9 pagineRectificador Controladonelguarher100% (2)

- Laboratorio 3Documento13 pagineLaboratorio 3ANGEL MAURICIO SARMIENTO ZARZOSANessuna valutazione finora

- Amplificadores CascadaDocumento5 pagineAmplificadores CascadaJuan Sin Faceb100% (1)

- Armónicas en Sistemas Eléctricos IndustrialesDa EverandArmónicas en Sistemas Eléctricos IndustrialesValutazione: 4.5 su 5 stelle4.5/5 (12)

- Problemas resueltos de Hidráulica de CanalesDa EverandProblemas resueltos de Hidráulica de CanalesValutazione: 4.5 su 5 stelle4.5/5 (7)

- Diseño de Una Fuente de ReferenciaDocumento7 pagineDiseño de Una Fuente de ReferenciaDiego AlejandroNessuna valutazione finora

- Amplificador de InstrumentaciónDocumento10 pagineAmplificador de InstrumentaciónNixon CardonaNessuna valutazione finora

- Informe 3Documento2 pagineInforme 3Diego AlejandroNessuna valutazione finora

- Amplificador de InstrumentaciónDocumento10 pagineAmplificador de InstrumentaciónNixon CardonaNessuna valutazione finora

- Mini Proyecto ARquitecturaDocumento7 pagineMini Proyecto ARquitecturaDiego AlejandroNessuna valutazione finora

- Ejercicios MamiDocumento1 paginaEjercicios MamiDiego AlejandroNessuna valutazione finora

- Informe 5 Filtro Acoplamiento B1 06Documento2 pagineInforme 5 Filtro Acoplamiento B1 06Diego AlejandroNessuna valutazione finora

- Estefania Ricardo GamaDocumento1 paginaEstefania Ricardo GamaDiego AlejandroNessuna valutazione finora

- Maquinas Diagramas de ConexionDocumento1 paginaMaquinas Diagramas de ConexionDiego AlejandroNessuna valutazione finora

- Informe 5 Filtro Acoplamiento B1 06Documento2 pagineInforme 5 Filtro Acoplamiento B1 06Diego AlejandroNessuna valutazione finora

- Lab Motores InduccionDocumento4 pagineLab Motores InduccionDiego AlejandroNessuna valutazione finora

- Cartografia y Topografia Taller.Documento4 pagineCartografia y Topografia Taller.Diego AlejandroNessuna valutazione finora

- Informe 5 Filtro Acoplamiento B1 06Documento2 pagineInforme 5 Filtro Acoplamiento B1 06Diego AlejandroNessuna valutazione finora

- Informe 3Documento2 pagineInforme 3Diego AlejandroNessuna valutazione finora

- Goniometro InformeDocumento4 pagineGoniometro InformeDiego AlejandroNessuna valutazione finora

- ANEXOS Ecg InformeDocumento1 paginaANEXOS Ecg InformeDiego AlejandroNessuna valutazione finora

- Maquinas Diagramas de ConexionDocumento1 paginaMaquinas Diagramas de ConexionDiego AlejandroNessuna valutazione finora

- Amplificadores de PotenciaDocumento25 pagineAmplificadores de Potenciajochato2726Nessuna valutazione finora

- 4parametri BDDocumento23 pagine4parametri BDChristian MárquezNessuna valutazione finora

- Los Cuadros Electricos 2012Documento52 pagineLos Cuadros Electricos 2012Maria planellerNessuna valutazione finora

- WSCC 9 BusDocumento4 pagineWSCC 9 BusAgustín R. Marulanda G.Nessuna valutazione finora

- Lab #8 Impedancia Jhon FergusonDocumento8 pagineLab #8 Impedancia Jhon FergusonJhon FergusonNessuna valutazione finora

- El Lenguaje Ensamblador Del PIC16F84ADocumento57 pagineEl Lenguaje Ensamblador Del PIC16F84ALask HirakawaNessuna valutazione finora

- ApostilaTraduzida Espanhol....Documento48 pagineApostilaTraduzida Espanhol....natanael100% (1)

- Problemas Segundo ParcialDocumento15 pagineProblemas Segundo Parcialjossa juarezNessuna valutazione finora

- CT G2119eDocumento56 pagineCT G2119eanon_849693510Nessuna valutazione finora

- Cuestionario 1 Guia 4 MANTENIMIENTO.Documento14 pagineCuestionario 1 Guia 4 MANTENIMIENTO.javier hurtadoNessuna valutazione finora

- Instalaciones2 TSUDocumento17 pagineInstalaciones2 TSULuis Ernesto LealNessuna valutazione finora

- Despacho Economico FinalDocumento64 pagineDespacho Economico FinalDenis MelendezNessuna valutazione finora

- Componentes de Un Sistema FotovoltaicoDocumento2 pagineComponentes de Un Sistema Fotovoltaicojared sneider alvarez eustaquioNessuna valutazione finora

- Materiales SemiconductoresDocumento16 pagineMateriales SemiconductoresDiana AlboresNessuna valutazione finora

- ELECTROMOVILIDADDocumento16 pagineELECTROMOVILIDADFrancisco Martinez mendozaNessuna valutazione finora

- Formulas Cuk Pag 71Documento126 pagineFormulas Cuk Pag 71ezequiel becerraNessuna valutazione finora

- Proyecto Plantas y Subestaciones 2Documento7 pagineProyecto Plantas y Subestaciones 2misaelNessuna valutazione finora

- CFT 11236 201720 1Documento7 pagineCFT 11236 201720 1karen sanabriaNessuna valutazione finora

- EPF Riesgos Electricos Rev 02Documento19 pagineEPF Riesgos Electricos Rev 02Cristian SotoNessuna valutazione finora

- Manual iP5A EspanolDocumento101 pagineManual iP5A Espanolbyrs100% (1)

- Informe Instrumentación - Practica 3 PDFDocumento12 pagineInforme Instrumentación - Practica 3 PDFDanielNessuna valutazione finora

- Guía 6 Teoremas de CircuitosDocumento3 pagineGuía 6 Teoremas de CircuitosGuilleNessuna valutazione finora

- INTERRUPTOR SF6 Ó VacíoDocumento9 pagineINTERRUPTOR SF6 Ó VacíoRodrigo Venegas HidalgoNessuna valutazione finora

- Tarea N°4-2Documento4 pagineTarea N°4-2Carlos León PalominoNessuna valutazione finora

- TAREA Nº3 ElectronicaDocumento2 pagineTAREA Nº3 ElectronicaDilan CordovaNessuna valutazione finora

- Cne-Sumnistro Seccion 220Documento6 pagineCne-Sumnistro Seccion 220Walter E. Mendoza HumppireNessuna valutazione finora

- Tarea 01 Mmeqel2020-21Documento4 pagineTarea 01 Mmeqel2020-21Felipe Garcia.sanchezNessuna valutazione finora

- Lab 2.circuitosDocumento7 pagineLab 2.circuitosFRANCIS DAVID CABREJOS RAMOSNessuna valutazione finora

- Informe Balancin 1.0Documento43 pagineInforme Balancin 1.0Moises Cruz Mostacedo100% (1)

- Cuestionarios y Problemarios Etapa IiDocumento51 pagineCuestionarios y Problemarios Etapa Iicasandra contrerasNessuna valutazione finora

- Manual Usuario EspDocumento49 pagineManual Usuario EspJuanes1718Nessuna valutazione finora