Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

B 0623052213

Caricato da

sivakumarb92Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

B 0623052213

Caricato da

sivakumarb92Copyright:

Formati disponibili

International Journal of Recent Technology and Engineering (IJRTE)

ISSN: 2277-3878, Volume-2, Issue-2, May 2013

Design of Physical Coding Sublayer using

8B/10B Algorithm

N.Kiran Babu, P.S.Srinivas Babu

Abstract-In order to resolve the problem of base-line offset and

unbalanced code flow during the fiber data transmission, thesis

give a simple and practical solution 8B/10B encoder. This solution

taking a method which integrate checking scheme and logic

operation, through Verilog HDL description language, realize the

design of encoder. The proposed circuit is simulated in Xilinx and

Cadence. The results obtained in various tools are presented in this

paper.

Keywords Physical coding sub layer, 8B/10B algorithm,

Synchronization, Verilog HDL, Cadence Encounter.

I. INTRODUCTION

Due the quick development of communication of technology,

fiber communication is more and more popular for people, at

the same time; its higher transmission speed and bigger

capacity are required by people. But, high-speed fiber

transmission bring problem as base-line offset and

unbalanced code flow. So, based on such problems, we

design the 8B/10B encode, because its low transmission

mistake percent and DC compensation function, also with

checking mistake function during the transmission and

special function, it resolve the problem as base-line offset and

unbalanced code flow, but also was used in high-speed bus.

The PCS and the PMA are both contained within the physical

layer of the OSI reference model. The PCS and the Gigabit

Media Independent Interface (GMII) communicate with one

another via 8-bit parallel data lines and several control lines.

The PCS is responsible for encoding each octet passed down

from the GMII into ten bit code groups. The PCS is also

responsible for decoding ten bit code groups passed up from

the PMA into octets for use by the upper layers. The PCS also

controls the auto-negotiation process which allows two

separate gigabit devices to establish a link of which they are

both capable of using.

II. PCS FUNDAMENTALS

Figure 1. 8B/10B encoding relationship

It is important to ensure the DC balance of data flow during

the transmission process, also need to think about the

unbalance of DC data flow. As show in Table.2, for each 8B

data, after encoding, it will be transferred into one kind of

RD-&RD+. Encoder will decide the next 10B data based on

previous RD and ensure the DC data flow balance.

The original status of encoder is RD-, it will check the data

flow, if the quantity of number 1 and number 0 is the same,

the polarity of next 10B data will keep RD-, and otherwise, it

will turn to be RD+. If previous 10B polarity is RD+, and the

quantity of number 1 and number 0 of previous 10B data

keep same, the polarity of next 10B data will keep RD+.

2.2. Physical Coding Sublayer (PCS):

The PCS interface is the Gigabit Media Independent

Interface (GMII) which provides a uniform interface to the

Reconciliation sublayer for all 1000 Mb/s PHY

implementations (e.g., not only 1000BASE-X but also other

possible types of gigabit PHY entities). 1000BASE-X

provides services to the GMII in a manner analogous to how

100BASE-X provides services to the 100 Mb/s MII.

The 1000BASE-X PCS provides all services required by the

GMII, including:

a. Encoding (decoding) of GMII data octets to (from)

ten-bit code-groups (8B/10B) for communication with

the underlying PMA.

2.1 8B/10B CODING:

The PCS examines each incoming octet passed down by the

GMII and encodes it into a ten bit code group; this is referred

to as 8B/10B encoding. Many serial data transmission

standards utilize 8b/10b encoding to ensure sufficient data

transitions for clock recovery.

The principle of encoder is mapping transfer the input 8 bits

data into 10 bits data per the mapping principle, separate the 8

bits data into one group 3 bits data and another group 5bits

data, after encoding of the 8B/10B encoder, output one group

4 bits data and another group 6 bits data, to make a 10 bit

data. This coding scheme is used for high-speed serial data

transmission.

Manuscript received on May, 2013.

N.Kiran Babu, (VLSI Research Group, Department of Electronics &

Communication Engineering, KL University, Guntur,

Dr.P.S.Srinivas Babu, (VLSI Research Group, Department of

Electronics & Communication Engineering, KL University, Guntur

114

Figure 2. PCS Block Diagram

Design of Physical Coding Sublayer using 8B/10B Algorithm

b.

c.

Generating Carrier Sense and Collision Detect

indications for use by PHYs half-duplex clients.

Managing the Auto-Negotiation process, and informing

the management entity via the GMII when the PHY is

ready for use.

2.3. PMA (Physical Medium Attachment):

The PMA (shown in Figure2) serializes and de-serializes the

coded group between the PCS and PMD. This is

accomplished by recovery of the clock from the coded data

from PMD and multiplying by 10 of the parallel data rate.

The PMA also functions as recovering the clock from the

incoming data stream.

c) Otherwise, running disparity at the end of the sub-block is

the same as at the beginning of the sub block.

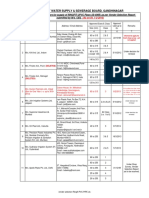

Table 4.2. Valid special code-groups

The /K28.5/ special code-group is chosen as the first

code-group of all ordered_sets which are signaled repeatedly

and for the purpose of allowing a receiver to synchronize to

the incoming bit stream (i.e., /C/ and /I/).

b. Carrier sense:

Carrier sense means that a transmitter uses feedback from a

receiver to determine whether another transmission is in

progress before trying to send. That is, it tries to detect the

presence of a carrier wave from another station before

attempting to transmit. If a carrier is sensed, the station waits

for the transmission in progress to finish before initiating its

own transmission.

The Carrier Sense process controls the GMII signal CRS:

Figure 3.PCS reference diagram

a. Running Disparity:

Running Disparity is a technique used in digital

communication in order to maintain a DC balance in digital

transmissions. For ex: if there are too many ones bunched

together in the data stream, then, Zeros are added to the data

and vice-versa.

What this does is that, in average, the numbers of ones are

equal to number of Zeros in a transmission stream. A DC

balanced signal is more immune to noise and easier to

recover at the end of the line.

Running disparity for the sub-blocks is calculated as follows:

a) Running disparity at the end of any sub-block is positive if

the sub-block contains more ones than zeros. It is also

positive at the end of the six-bit sub-block if the six-bit

sub-block is 000111, and it is positive at the end of the

four-bit sub-block if the four-bit sub-block is 0011;

b) Running disparity at the end of any sub-block is negative if

the sub-block contains more zeros than ones. It is also

negative at the end of the six-bit sub-block if the six-bit

sub-block is 111000, and it is negative at the end of the

four-bit sub-block if the four-bit sub-block is 1100.

Table 4.1: 8B/10B running disparity encoding examples

Figure 4-Carrier sense state diagram.

By using state diagram we can find the crs signal. If both

transmitter and receiver are occur at same time we can get the

crs signal as high, otherwise crs signal as low.

c. Synchronization:

The Synchronization process is responsible for determining

whether the underlying receive channel is ready for

operation. Failure of the underlying channel typically causes

the PMA client to suspend normal actions.

d. Auto-Negotiation:

The Auto-Negotiation process shall provide the means to

exchange configuration information between two devices

that share a link segment and to automatically configure both

devices to take maximum advantage of their abilities.

Auto negotiation is an Ethernet procedure by which two

connected devices choose common transmission parameters,

such as speed, duplex mode, and flow control. In this process,

the connected devices first share their capabilities regarding

these parameters and then choose the highest performance

transmission mode they both support. In the OSI model, auto

negotiation resides in the physical layer. For Ethernet over

twisted pair it is defined in clause 28 of IEEE 802.3.

Auto negotiation was originally defined as an optional

component in the fast Ethernet standard. It is backwards

compatible with 10BASE-T. The protocol was significantly

extended in the gigabit Ethernet standard, and is mandatory

for 1000BASE-T gigabit Ethernet over copper.

115

International Journal of Recent Technology and Engineering (IJRTE)

ISSN: 2277-3878, Volume-2, Issue-2, May 2013

Provide easy, plug-and-play upgrades from 10 Mbps,

100 Mbps, and 1000 Mbps as the network infrastructure

is upgraded.

Prevent network disruptions when connecting mixed

technologies such as 10BaseT, 100BaseTX, and

1000BaseT.

Accommodate future PHY (transceiver) solutions

Allow manual override of auto-negotiation

Support backward compatibility with 10BaseT

Provide a parallel detection function to recognize

10BaseT, 100BaseTX, and 100BaseT4 non-NWay

devices.

Defines the valid data code-groups (D code-groups) of the

8B/10B transmission code. Defines the valid special

code-groups (K code-groups) of the code. The tables are used

for both generating valid code-groups (encoding) and

checking the validity of received code-groups (decoding).

each octet entry has two columns that represent two (not

necessarily different) code-groups.

In this project, we used top-down methodology to complete

our design. We divide the whole PHY into small locks, and

these blocks can be further divided within themselves until

each block is manageable. For example, his hierarchy tree of

PCS is shown in figure 5.

Figure7Carrier sense.

The simulation results of decoder and SIPO is shown below

as Fig 8& 9.

Figure8--8B/10B decoder.

Figure 5. Hierarchy tree of the PCS

III. SIMULATION RESULTS

The simulation results shown are shown in fig5 and 6.Here

the outputs are we get the both encoding and decoding by

using 8B/10B coding algorithm. For transmitter side here we

use the encoder and carrier sense.

The simulation results of encoder and carrier sense is shown

below as Fig 6 & 7.

The following are the output waveforms in Xilinx:

Figure9--SIPO.

Figure6--8B/10B encoder.

Figure10final output waveform for PCS in Xilinx.

116

Design of Physical Coding Sublayer using 8B/10B Algorithm

N.Kiran babu was born on 26th Dec 1989 at Guntur,

india.He received his B.tech in Electronics &

Communication Engineerings from L.B.R.C.E,

mylavaram,AP, India and Pursuing M.Tech in VLSI at

K L University, Vijayawada, AP, India. His research

interests in, Digital VLSI Design and Low Power VLSI

Design.

The simulation results of PCS are shown below as Fig 11.by

using cadence Encounter and we get layout as Fig12.

The following are the output waveforms in Cadence:

Dr.P.S.Srinivas Babu did his M.Tech in 2004 and

PhD in 2009 both from College of Engineering,

Andhra University, and Visakhapatnam, India.

Later he completed one year Post Doctoral Research

with full financial support from National Research

Council, Italy during 2011-2012. His area of interest

includes Micro Electro Mechanical Systems

(MEMS) for Biological & RF applications, Nano

Electro Mechanical Systems (NEMS), Advanced Sensor System

Technologies. He is the author for several National and International

journal and conference publications. He visited Italy, Germany, Austria and

Slovenia to attend various Conferences/Workshops. Currently, he is

Professor of Electronics & Communication Engineering, K L University,

and Vaddeswaram, India.

Figure11-- Output waveform in cadence for PCS.

Layout for PCS by using Cadence Encounter:

Figure12layout in cadence for PCS

Power dissipation for layout in cadence 452.210W

IV. CONCLUSION

In this paper the design of 8B/10B encoder of PCS is part of

FPGA optical fiber communication, the demand of simple

program logic relation, clear level demarcate, fast speed is

put forward in The plan, which can be achieved by

simulation. This program can be used in need 8B/10B coding

of optical fiber coding remote data transmission system.

REFERENCES

[1]

[2]

[3]

IEEE standard P802.3z/o5. 2.1998.06

PCS design Spec$cation version. I, Rocket chips Inc. 1998.

Samir palnitkar, Verilog HDL: A Guide to Digital Design and

Synthesis, Sunsoft press, 1996.

[4] Verilog XL Reference Manual Ver. 2.2 cadence design systems,

1995.

[5] Spectre HDL Reference Manual Ver. 4.3.4 cadence design systems,

1995.

[6] VSC713.5 Preliminary Data Sheet, VITESSE Semiconductor

Corporation, 1997.

[7] Edward A. LEE, DIGITAL COMMUNICATION, kluwer Academic

Publishers, 1994.

[8] Simon Haykin, Communication Systems, John Willey & Sons, Inc,

1994.

[9] Andrew S. Tanenbaum, COMPUTER NETWORKS, Prentice-Hall,

Inc, 1996.

[10] Behzad Razavi, Design of monolithic Phase-Locked Loops and Clock

Recovery Circuits A Tutorial IEEE Press, 1994.

117

Potrebbero piacerti anche

- List of CPU ArchitecturesDocumento3 pagineList of CPU Architecturessivakumarb92Nessuna valutazione finora

- MIPSDocumento6 pagineMIPSsivakumarb92Nessuna valutazione finora

- 8b/10b Encoder Design: Xu Qiaoyu Liu HuijieDocumento3 pagine8b/10b Encoder Design: Xu Qiaoyu Liu Huijiesivakumarb92Nessuna valutazione finora

- Parallel 2Documento14 pagineParallel 2sivakumarb92Nessuna valutazione finora

- Chapter 12: Multiprocessor Architectures: Cache Coherence Problem and Cache Synchronization Solutions Part 1Documento31 pagineChapter 12: Multiprocessor Architectures: Cache Coherence Problem and Cache Synchronization Solutions Part 1sivakumarb92Nessuna valutazione finora

- An Implementation of Open Core Protocol For The On-Chip Bus: CH - Suryanarayana, M.Vinodh KumarDocumento4 pagineAn Implementation of Open Core Protocol For The On-Chip Bus: CH - Suryanarayana, M.Vinodh Kumarsivakumarb92Nessuna valutazione finora

- Data Hazards in ALU Instructions: Consider This SequenceDocumento14 pagineData Hazards in ALU Instructions: Consider This Sequencesivakumarb92Nessuna valutazione finora

- NVL-12.Constant Delay Logic StyleDocumento3 pagineNVL-12.Constant Delay Logic Stylesivakumarb92Nessuna valutazione finora

- NVL-14.Minimizing Energy of Integer Unit by Higher VoltageDocumento3 pagineNVL-14.Minimizing Energy of Integer Unit by Higher Voltagesivakumarb92Nessuna valutazione finora

- Data HazardsDocumento29 pagineData Hazardssivakumarb92Nessuna valutazione finora

- NVL-07.Thwarting Scan-Based Attacks On Secure-ICsDocumento3 pagineNVL-07.Thwarting Scan-Based Attacks On Secure-ICssivakumarb92Nessuna valutazione finora

- NVL 09.low Power Pulse Triggered Flip Flop DesignDocumento3 pagineNVL 09.low Power Pulse Triggered Flip Flop Designsivakumarb92Nessuna valutazione finora

- Fault Tolerant Systems: PrerequisitesDocumento14 pagineFault Tolerant Systems: Prerequisitessivakumarb92Nessuna valutazione finora

- Mips IsaDocumento32 pagineMips Isasivakumarb92Nessuna valutazione finora

- NVL-06.Carbon Nanotubes Blowing New Life Into NP DynamicDocumento3 pagineNVL-06.Carbon Nanotubes Blowing New Life Into NP Dynamicsivakumarb92Nessuna valutazione finora

- NVL-05.Area-Delay-Power Efficient Carry-Select AdderDocumento3 pagineNVL-05.Area-Delay-Power Efficient Carry-Select Addersivakumarb92Nessuna valutazione finora

- NVL-04.an Optimized Modified Booth Recoder For Efficient Design of The Add-Multiply OperatorDocumento4 pagineNVL-04.an Optimized Modified Booth Recoder For Efficient Design of The Add-Multiply Operatorsivakumarb92Nessuna valutazione finora

- A High-Speed, Energy-Efficient Two-Cycle Multiply-Accumulate (MAC) Architecture and Its Application To A Double-Throughput MAC UnitDocumento9 pagineA High-Speed, Energy-Efficient Two-Cycle Multiply-Accumulate (MAC) Architecture and Its Application To A Double-Throughput MAC Unitsivakumarb92Nessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Transmisor HarrisDocumento195 pagineTransmisor HarrisJose Juan Gutierrez Sanchez100% (1)

- Softening N Penetration Test BitumenDocumento11 pagineSoftening N Penetration Test BitumenEdwin LeonNessuna valutazione finora

- Parallel Port Programming (PART 1) With CDocumento13 pagineParallel Port Programming (PART 1) With ChertzoliNessuna valutazione finora

- Schematic Lenovo ThinkPad T410 NOZOMI-1Documento99 pagineSchematic Lenovo ThinkPad T410 NOZOMI-1borneocampNessuna valutazione finora

- Published Document Guidance On The Use of BS EN 13108, Bituminous Mixtures - Material SpecificationsDocumento8 paginePublished Document Guidance On The Use of BS EN 13108, Bituminous Mixtures - Material SpecificationsCristián JiménezNessuna valutazione finora

- Comfort and Performance Your Customers DemandDocumento18 pagineComfort and Performance Your Customers Demandgizex2013Nessuna valutazione finora

- SemDocumento31 pagineSemkaushik4208Nessuna valutazione finora

- ASTM F 412 - 01a Standard Terminology Relating To Plastic Piping Systems1Documento13 pagineASTM F 412 - 01a Standard Terminology Relating To Plastic Piping Systems1JORGE ARTURO TORIBIO HUERTANessuna valutazione finora

- ISO 9001:2015 Questions Answered: Suppliers CertificationDocumento3 pagineISO 9001:2015 Questions Answered: Suppliers CertificationCentauri Business Group Inc.100% (1)

- Vibration - Electrical or Mechanical - EASADocumento3 pagineVibration - Electrical or Mechanical - EASAGilbNessuna valutazione finora

- Valve Body PDFDocumento9 pagineValve Body PDFTimur TOT100% (2)

- Standardization of Naoh 1Documento3 pagineStandardization of Naoh 1api-309208977Nessuna valutazione finora

- PORTFOLIO: OFFICE WORK (20/06/2022-20/12/2022) Harleen KlairDocumento34 paginePORTFOLIO: OFFICE WORK (20/06/2022-20/12/2022) Harleen KlairHarleen KlairNessuna valutazione finora

- 20 Site SummaryDocumento2 pagine20 Site SummaryMuzammil WepukuluNessuna valutazione finora

- Concept of Circulation in A Free Vortex FlowDocumento55 pagineConcept of Circulation in A Free Vortex FlowAnil KumarNessuna valutazione finora

- BKLT DeaeratorDocumento24 pagineBKLT Deaeratormalikgaurav01Nessuna valutazione finora

- AB-522 Standard Pneumatic Test Procedure RequirementsDocumento16 pagineAB-522 Standard Pneumatic Test Procedure RequirementsShank HackerNessuna valutazione finora

- ITP InstrumentationDocumento9 pagineITP InstrumentationzhangyiliNessuna valutazione finora

- Eramus Bridge PDFDocumento10 pagineEramus Bridge PDFBabaO.Riley100% (1)

- Klübersynth UH1 14-151: Product InformationDocumento2 pagineKlübersynth UH1 14-151: Product InformationNathanael SuryantoroNessuna valutazione finora

- zx350lc 3 InglesDocumento6 paginezx350lc 3 InglesLuis Nahuelhuaique LemusNessuna valutazione finora

- Ism CodeDocumento9 pagineIsm CodePraneel KurhadeNessuna valutazione finora

- BD+ CD+ XD+ - tcm833-3534072Documento20 pagineBD+ CD+ XD+ - tcm833-3534072MisterMMNessuna valutazione finora

- Korantin PPDocumento4 pagineKorantin PPteddy garfieldNessuna valutazione finora

- Report On Automatic Phase Changer: Submitted ByDocumento32 pagineReport On Automatic Phase Changer: Submitted ByAndrea JohnsonNessuna valutazione finora

- Cache MemoryDocumento20 pagineCache MemoryKeshav Bharadwaj RNessuna valutazione finora

- BurnerDocumento4 pagineBurnerAhmed Mohamed KhalilNessuna valutazione finora

- Bs en 00378 3 2016Documento30 pagineBs en 00378 3 2016Darius VinNessuna valutazione finora

- U042en PDFDocumento12 pagineU042en PDFTatiya TatiyasoponNessuna valutazione finora

- GWSSB Vendor List 19.11.2013Documento18 pagineGWSSB Vendor List 19.11.2013sivesh_rathiNessuna valutazione finora