Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Interrupts: Interrupt Vector

Caricato da

anharDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Interrupts: Interrupt Vector

Caricato da

anharCopyright:

Formati disponibili

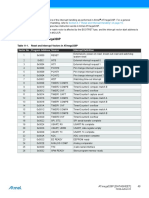

Interrupt Vector

No.Addr.

Source

1 0x0000 RESET

Interrupts

ATmega128

Interrupt Definition

External Pin, Power-on Reset, Brown-out Reset, and

Watchdog Reset

2 0x0002 INT0

External Interrupt Request 0

3 0x0004 INT1

External Interrupt Request 1

4 0x0006 INT2

External Interrupt Request 2

5 0x0008 INT3

External Interrupt Request 3

6 0x000A INT4

External Interrupt Request 4

7 0x000C INT5

External Interrupt Request 5

8 0x000E INT6

External Interrupt Request 6

9 0x0010 INT7

External Interrupt Request 7

10 0x0012 TIMER2 COMP Timer/Counter2 Compare Match

11 0x0014 TIMER2 OVF

Timer/Counter2 Overflow

12 0x0016 TIMER1 CAPT

Timer/Counter1 Capture Event

13 0x0018 TIMER1 COMPA Timer/Counter1 Compare Match A

14 0x001A TIMER1 COMPB Timer/Counter1 Compare Match B

15 0x001C TIMER1 OVF

Timer/Counter1 Overflow

16 0x001E TIMER0 COMP Timer/Counter0 Compare Match

MCU Control Register

Interrupt Vector

No. Addr.

17 0x0020

18 0x0022

19 0x0024

20 0x0026

21 0x0028

22 0x002A

23 0x002C

0 002C

24 0x002E

25 0x0030

26 0x0032

27 0x0034

28 0x0036

29 0x0038

30 0x003A

31 0x003C

32 0x003E

33 0x0040

34 0x0042

35 0x0044

Source

TIMER0 OVF

SPI, STC

USART0, RX

USART0, UDRE

USART0, TXC

ADC

EE READY

ANALOG COMP

TIMER1 COMPC

TIMER3 CAPT

TIMER3 COMPA

TIMER3 COMPB

TIMER3 COMPC

TIMER3 OVF

USART1, RX

USART1, UDRE

USART1, TXC

TWI

SPM_RDY

MCUCR 7

Interrupt Definition

Timer/Counter0 Overflow

Serial Transfer Complete

USART0, Rx Complete

USART0 Data Register Empty

USART0, Tx Complete

ADC Conversion Complete

EEPROM Ready

R d

Analog Comparator

Timer/Counter1 Compare Match C

Timer/Counter3 Capture Event

Timer/Counter3 Compare Match A

Timer/Counter3 Compare Match B

Timer/Counter3 Compare Match C

Timer/Counter3 Overflow

USART1, Rx Complete

USART1 Data Register Empty

USART1, Tx Complete

Two-wire Serial Interface

Store Program Memory Ready

SRE

SRW10

SE

SM1

SM0

SM2

IVSEL

IVCE

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

IVSEL Interrupt Vector Select

0 interrupt vector at start of program Flash

1 interrupt vector at start of Boot Loader section

IVCE Interrupt Vector Change Enable

after setting to 1, IVSEL may be changed within 4 clock

cycles

during that time, interrupts are disabled

INT0-3 - External Interrupts

Reset and Interrupt Vector

BOOTRST IVSEL

Reset address

Interrupt Vector address

fuse

MCUCR:1

$0000

$0002

$0000

Boot Reset address + $0002

Boot Reset address $0002

Boot Reset address Boot Reset address + $0002

EICRA

ISC31

ISC30

ISC21

ISC20

ISC11

ISC10

ISC01

ISC00

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

ISC11-ISC10 Interrupt Sense Control 1

00 low level

01 reserved

10 falling edge async

11 rising edge async

Level/edge event

BOOTSZ1 BOOTSZ0 Boot Reset address

fuse

fuse

$FE00

$FC00

$F800

$F000

asynchronous regardless on the clock

can wake up also from other than just Idle sleep mode

level detected at the end of instruction execution

Multiplex PD0-PD3

INT4-7 - External Interrupts

EICRB

External Interrupt Mask Register

EIMSK

ISC71

ISC70

ISC61

ISC60

ISC51

ISC50

ISC41

ISC40

INT7

INT6

INT5

INT4

INT3

INT2

INT1

INT0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

ISC11-ISC10 Interrupt Sense Control 1

00 low level

01 any change

INT0-7 External Interrupt Request Enable

10 falling edge

11 rising edge

0 disabled

1 enabled

Level event

asynchronous regardless on the clock

can wake up also from other than just Idle sleep mode

level detected at the end of instruction execution

If the conditions are met, the interrupt is called

even when the pin is set to output

Edge/toggle event

may be used as software interrupt

depends on the clock, pulse must be longer than 1 clock

Multiplex PE4-PE7

External Interrupt Flag Register

EIFR

INTF7

INTF6

INTF5

INTF4

INTF3

INTF2

INTF1

INTF0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

INT0-7 External Interrupt Flag

0 clear

1 interr

interrupt

pt triggered

set when edge/logic change causes INT0-7

jump on the specified location

zeroed after the routine is finished (or manually)

Level interrupt always clear

Potrebbero piacerti anche

- 4 Experiment 4 Interrupt and I/O InterfacingDocumento17 pagine4 Experiment 4 Interrupt and I/O InterfacingSuhas NipaneNessuna valutazione finora

- Government Engineering College, GandhinagarDocumento8 pagineGovernment Engineering College, GandhinagarDhrumil ManiyarNessuna valutazione finora

- 7sj642 Settings 180912 TrialDocumento13 pagine7sj642 Settings 180912 TrialkelsimpsNessuna valutazione finora

- Avr Atmega128 Interrupts Cheat-SheetDocumento14 pagineAvr Atmega128 Interrupts Cheat-SheetNick TarasNessuna valutazione finora

- Using External Interrupts For MegaAVR DevicesDocumento12 pagineUsing External Interrupts For MegaAVR DevicesJhon ZumaetaNessuna valutazione finora

- Advanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. PDocumento46 pagineAdvanced Microprocessors: Session - 24 Prof. Venkataramaiah. P. Pvishu212167% (3)

- Embedded Systems - Lec 4 - InterruptsDocumento29 pagineEmbedded Systems - Lec 4 - InterruptsIslam Abd ElhadlyNessuna valutazione finora

- Section 8. 70055cDocumento20 pagineSection 8. 70055cjpjenifferNessuna valutazione finora

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocumento1 paginaInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNessuna valutazione finora

- Avr Tutorials - Com AVR Microcontroller InterruptsDocumento4 pagineAvr Tutorials - Com AVR Microcontroller InterruptsMohamed AshrafNessuna valutazione finora

- Module - III (A&B)Documento80 pagineModule - III (A&B)PamusainagaharshavardhanNessuna valutazione finora

- Topic 11 - ATMega32 Interrupt in C (ISMAIL - FKEUTM 2018)Documento60 pagineTopic 11 - ATMega32 Interrupt in C (ISMAIL - FKEUTM 2018)Aya AmirNessuna valutazione finora

- 8051 Interrupts and Interfacing Applications: Module - 5Documento26 pagine8051 Interrupts and Interfacing Applications: Module - 5Pate VishnuNessuna valutazione finora

- PIC24FJ64GA002 Interrupt VectorsDocumento10 paginePIC24FJ64GA002 Interrupt Vectorsocelot_and_allNessuna valutazione finora

- InterruptsDocumento34 pagineInterruptsJaney24100% (1)

- PLCBeginnerguide110 177Documento68 paginePLCBeginnerguide110 177Jun CiaoNessuna valutazione finora

- IC BA5979S DatasheetDocumento11 pagineIC BA5979S Datasheetnaupas007Nessuna valutazione finora

- 8 Reset PDFDocumento20 pagine8 Reset PDFnicolas8702Nessuna valutazione finora

- F 818Documento9 pagineF 818Eric YangNessuna valutazione finora

- 6809 ProgDocumento201 pagine6809 ProgAntonio SabaNessuna valutazione finora

- Management: Centre de Formation TechniqueDocumento20 pagineManagement: Centre de Formation TechniqueRoger Anibal ZamoraNessuna valutazione finora

- Ch10 AVR Interrupt ProgrammingDocumento23 pagineCh10 AVR Interrupt ProgrammingWarforce Rox100% (1)

- InterruptDocumento22 pagineInterrupthefawoj62Nessuna valutazione finora

- Ch11 AVR Serial Port ProgrammingDocumento25 pagineCh11 AVR Serial Port ProgrammingSimple knowledgeNessuna valutazione finora

- "Clock Systems and Their Distribution" On Page 24: MCU Control Register - McucrDocumento5 pagine"Clock Systems and Their Distribution" On Page 24: MCU Control Register - McucrAlejo CifuentesNessuna valutazione finora

- Korg DW-8000 Service ManualDocumento47 pagineKorg DW-8000 Service ManualMatthew DavidsonNessuna valutazione finora

- Print - ContentsDocumento5 paginePrint - ContentsPhan Văn TúNessuna valutazione finora

- PIC18F4550: PLL Prescaler Selection BitsDocumento6 paginePIC18F4550: PLL Prescaler Selection BitsFrancisco Javier García GarcíaNessuna valutazione finora

- AVR2 AppendixF FuseBitsDocumento6 pagineAVR2 AppendixF FuseBitsabdullahNessuna valutazione finora

- Lecture 7 - AVR Interrupt ProgrammingDocumento26 pagineLecture 7 - AVR Interrupt Programmingmminhdoan2203Nessuna valutazione finora

- S7-200 Quick Reference Information: Special Memory BitsDocumento6 pagineS7-200 Quick Reference Information: Special Memory BitsDjNIAZINessuna valutazione finora

- Pin No. Pin Name Description Alternate FunctionDocumento7 paginePin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- Integrated Circuit Systems, IncDocumento11 pagineIntegrated Circuit Systems, Incroger marqNessuna valutazione finora

- Programable Elements I InterruptsDocumento17 pagineProgramable Elements I InterruptsOliver Ochoa GarciaNessuna valutazione finora

- Timer, AdcDocumento16 pagineTimer, Adchefawoj62Nessuna valutazione finora

- Lecture 7Documento48 pagineLecture 7tecleador1Nessuna valutazione finora

- Imprimir Datasheet 1Documento14 pagineImprimir Datasheet 1Randy Siancas VelezNessuna valutazione finora

- LB1847Documento17 pagineLB1847serlabtriesteNessuna valutazione finora

- Kenwood Kdc-Mp408u Mp438u x492 Mp5039u Mp5539u W5041ua W5041ug W5141uay W5141ugy W5541u W5641uy Et 169Documento48 pagineKenwood Kdc-Mp408u Mp438u x492 Mp5039u Mp5539u W5041ua W5041ug W5141uay W5141ugy W5541u W5641uy Et 169mrdevil83100% (1)

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocumento8 pagineCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- Exp 12) Prbs Generator and Shift RegisterDocumento5 pagineExp 12) Prbs Generator and Shift RegisterMani BharathiNessuna valutazione finora

- iNTRODUCTION TO MICROCONTROLLERSDocumento72 pagineiNTRODUCTION TO MICROCONTROLLERSAlok SrivastavNessuna valutazione finora

- Sesion 4Documento5 pagineSesion 4gaosrock1234Nessuna valutazione finora

- LV76213 3C PDFDocumento6 pagineLV76213 3C PDFjdrsant100% (1)

- Bush 1433Documento5 pagineBush 1433Daniel AvecillaNessuna valutazione finora

- MT Datasheet CroppedDocumento107 pagineMT Datasheet Croppedbasar.metin2Nessuna valutazione finora

- Ee3954 Fall13 08 InterruptsDocumento44 pagineEe3954 Fall13 08 InterruptsHeart StopperNessuna valutazione finora

- 10 ATmega328P InterruptsDocumento17 pagine10 ATmega328P InterruptsJarfoNessuna valutazione finora

- 05 AVR Timer-Counter AVRDocumento95 pagine05 AVR Timer-Counter AVRPriscillaNessuna valutazione finora

- 4 - InterruptsDocumento38 pagine4 - Interruptskomailhaiderz123Nessuna valutazione finora

- UBC104 Embedded Systems: Review: Introduction To MicrocontrollersDocumento72 pagineUBC104 Embedded Systems: Review: Introduction To MicrocontrollersAlok SrivastavNessuna valutazione finora

- Pin No. Pin Name Description Alternate FunctionDocumento6 paginePin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- 8051 InterruptsDocumento20 pagine8051 InterruptsAliNessuna valutazione finora

- VCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocumento8 pagineVCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNessuna valutazione finora

- I 3 CDocumento3 pagineI 3 CKiran AlladaNessuna valutazione finora

- DatashetDocumento11 pagineDatashetRoberto VegaNessuna valutazione finora

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocumento8 pagineCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNessuna valutazione finora

- BigData - Sem 4 - Elective 1 - Module 2 - PPTDocumento29 pagineBigData - Sem 4 - Elective 1 - Module 2 - PPThitaarnavNessuna valutazione finora

- Abap Project Demo On Wednesday 11.30 Am: BASICS (1 Day)Documento2 pagineAbap Project Demo On Wednesday 11.30 Am: BASICS (1 Day)anup kumarNessuna valutazione finora

- Aix-Configure SNMP On AixDocumento2 pagineAix-Configure SNMP On AixAntonio A. BonitaNessuna valutazione finora

- DEH Installation GuideDocumento184 pagineDEH Installation GuideTHAMARAI SELVANNessuna valutazione finora

- Cos1512 101 2012 3 B Nostudy GuideDocumento92 pagineCos1512 101 2012 3 B Nostudy GuideLina Slabbert-van Der WaltNessuna valutazione finora

- Pix To ASADocumento24 paginePix To ASAembadingaNessuna valutazione finora

- 32-Bit Vedic MultiplierDocumento9 pagine32-Bit Vedic MultiplierNawaz ShariffNessuna valutazione finora

- Des 1d11orgDocumento30 pagineDes 1d11orgΘεοδόσιος ΚαλίκαςNessuna valutazione finora

- XST User Guide For Virtex-6, Spartan-6, and 7 Series DevicesDocumento485 pagineXST User Guide For Virtex-6, Spartan-6, and 7 Series DevicesRicardo NicolaldeNessuna valutazione finora

- Basis 3 Years ExpDocumento4 pagineBasis 3 Years ExpSurya NandaNessuna valutazione finora

- Cs101 Quiz1 PrelimDocumento6 pagineCs101 Quiz1 PrelimDevina GraciaNessuna valutazione finora

- HARAR HEALTH SCIENCE COLLEGE Exit ExamDocumento45 pagineHARAR HEALTH SCIENCE COLLEGE Exit Examsuraasefa5Nessuna valutazione finora

- Tcil-It Fee It Dated Aug 2011Documento5 pagineTcil-It Fee It Dated Aug 2011Anonymous qnE08HcNessuna valutazione finora

- B2. Introduction To Big Data With Spark and Hadoop - CourseraDocumento12 pagineB2. Introduction To Big Data With Spark and Hadoop - CourseraHafiszanNessuna valutazione finora

- ProfiledataDocumento47 pagineProfiledataMr.KneZZzNessuna valutazione finora

- ADF Best PracticesDocumento50 pagineADF Best PracticesAkhil RangarajuNessuna valutazione finora

- Minitab 16Documento8 pagineMinitab 16VitalyNessuna valutazione finora

- Ricoh Aficio MP2500SP BrochureDocumento6 pagineRicoh Aficio MP2500SP BrochureAnonymous WD109UakyNessuna valutazione finora

- Microprocessor - 8086 OverviewDocumento2 pagineMicroprocessor - 8086 OverviewVipul MistryNessuna valutazione finora

- A Hands-On Introduction To Insecure DeserializationDocumento18 pagineA Hands-On Introduction To Insecure DeserializationasdffNessuna valutazione finora

- MVI69 AFC DatasheetDocumento3 pagineMVI69 AFC Datasheet김윤식Nessuna valutazione finora

- Cohesity Pure Solution BriefDocumento2 pagineCohesity Pure Solution Briefhank100% (1)

- Eeproms 24CXXDocumento18 pagineEeproms 24CXXAlberto YepezNessuna valutazione finora

- Oracle: Oracle Database Administration IIDocumento6 pagineOracle: Oracle Database Administration IInew_raja100% (1)

- Anaconda InstallationDocumento9 pagineAnaconda InstallationanmolNessuna valutazione finora

- 1 s2.0 S0167404817301578 MainDocumento14 pagine1 s2.0 S0167404817301578 Mainricksant2003Nessuna valutazione finora

- APACS ArchitectureDocumento12 pagineAPACS Architecturesina20795Nessuna valutazione finora

- Citrix Secure Remote WorkDocumento21 pagineCitrix Secure Remote WorkCharlie LopezNessuna valutazione finora

- A Panda3D Hello World Tutorial 1Documento33 pagineA Panda3D Hello World Tutorial 1Eduardo PerdomoNessuna valutazione finora

- (DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFDocumento30 pagine(DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFsamuelNessuna valutazione finora