Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Power Optimization of IO Ports Using Clock Gating Technique

Caricato da

Editor IJRITCCCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Power Optimization of IO Ports Using Clock Gating Technique

Caricato da

Editor IJRITCCCopyright:

Formati disponibili

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 2 Issue: 6

ISSN: 2321-8169

1761 1763

_______________________________________________________________________________________________

Power Optimization of I/O Ports Using Clock Gating Technique

Kirti

Surendra Waghmare

Dept. of E &TC Engineering

G.H. Raisoni college of Engg. & Management

Pune, India

kirti435@gmail.com

Dept. of Electronics Engineering

G.H. Raisoni college of Engg. & Management

Pune, India

Surendra.waghmare@raisoni.net

Abstract This paper deals with the one of the application of clock gating techniques. As we all know that today power and switching speed

optimization are the major areas on which vlsi designers are more concern about. Clock Gating Technique is one of the solutions to this major

problem. So, here we are doing a kind of experiment on the applications of CGT e.g.UART and ADC. On the basis of this experiment we can have

some clear views regarding efficiency of this technique. This paper provides the concept of reducing power consumption in IDLE state and

enhances switching speed when the functional block is in running state. This modified instruction level clock gating reduces dynamic power by

19-25%.

Keywords- CGT, ACG, DCG, Clock , UART, ADC etc

__________________________________________________*****_________________________________________________

I.

INTRODUCTION

Clock Gating Technique(CGT) is a well known method which

can be used to reduce power dissipation while designing any

VLSI circuit. Now a days, power consumption and switching

speed are the areas for which vlsi designers are more

concerned about. CGT is one of the technique which can

optimize the power by 19-25% and can enhance the switching

speed as well [3]. As we have two types of CGT: (i)DCG &

(ii)ACG. To use Deterministic Clock Gating we should be

perfect in system architecture designing, and should have the

knowledge of pipelining. Whereas Adaptive Clock Gating

first analyzes IP model which can be modeled as a finite state

machine [3]. Here we are achieving the goal through ACG

technique.

II. EXISTING ADC SYSTEM

In todays era everything is digitalized to make our lives easy

and comfortable. Every single thing has been changed its state

to be digital. As we know that there are so many drawbacks of

analog signals , so , to overcome all these problems we switch

over digital signal. To convert analog signal into digital form

we require Analog to Digital Converter i.e. ADC. Here we will

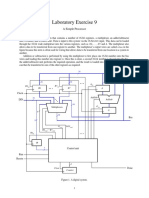

discuss the existing ADC system. As shown in fig. (1) ADC

has different functional blocks in it. These functional blocks

are as follows:

A comparator.

A Multiplexer.

A successive approximation register.

An output latch buffer.

A sample and hold circuit (optional).

First of all we provide N-bit input signals to the Multiplexer,

so , that it avoids congession to the inputs channels of ADC.

Since multiplexer is nothing but a type of digital switch which

produces only one output signal regardless of no. of inputs

present. This output signal of multiplexer is given as one of

the inputs to the comparator. Second input of comparator is the

signal provided by the register tree. Register tree is nothing but

the voltage divider circuit which is use to produce equivalent

analog value i.e. Vref. Now the comparator will compare these

two inputs available to it .

Fig. (1). Block Diagram of ADC

If ( Vref > output of Mux ) :

Then, Vout = 1i.e. digital value of MSB.

If ( Vref < Output of Mux ) :

Then , Vout = 0 i.e. Digital value of MSB.

The output of the comparator is given to S.A.R unit to perform

binary search for all bits available in SAR. The final digital

codes available in SAR is the digitalized representation of

analog signal. In this ways it produces digital signal out of

analog inputs.

DRAWBACKS:

ADC has comparator which is nothing but one of the

application of Operational Amplifier (Op-Amp). As

we know that op-amp consumes more power to

compare Vref and output of Mux. It leads to more

power dissipation.

For comparator three major constraints are to be

consider:

(i)

Comparator Trimming.

1761

IJRITCC | June 2014, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 2 Issue: 6

ISSN: 2321-8169

1761 1763

_______________________________________________________________________________________________

(ii)

Correction of Digital Output Data.

(iii)

Selection of Optimal Set of Comparator.

The points mentioned above are the reasons behind

this experiment of power reduction of ADC by using

Clock Gating Technique.

II.

PROPOSED CLOCK GATING ARCHITECTURE

Modified instruction level Adaptive Clock Gating is the only

method which can optimize dynamic power which deals with

power consumption and switching activity. So, we use this

technique to analyze IP model of FSM. For FSM there are five

states: Idle, ready, Run, Wait and End. Usually we provide

clock signal to each and every states of FSM to make a

transition from one state to another. When an IP core finishes

its work and enters to the idle state and stays there until system

bus makes a request. Whenever any state of FSM enters the

IDLE state ACG is being considered as shown in Fig. 2[3].

For output the control signals are generated in running staes,

and combined with thw main FSM clock signal using

modigfied instruction level clock gating. When not needed

clock signal is diaabled. When output is active high,

instructional ACG disables the IP clock otherwise, the clock

is enabled. It reduces dynamic power consumption by 1520%[1][3].

Some of the instructions dont need this SIO operation but

need PORT operation, such as IN SIO, OUT SIO instruction.

By seeing this fig 3 We have a view that a power control

logic is being used in different states of the FSM of PORT I/O

functional block design flow. The control logic decide clock

period for every instruction, and according to that the state of

the clock to every component will be decide , whether it will

be active mode or non active mode. This CGT efficiently

reduces switching activity of the clock and register operation

in the design flow of functional block. Some functional block

enters in the IDLE state, which causes more reduction in the

clock power consumption. Hence, the idea behind our

proposed clock gating technique is to reduce switching speed

of a functional block when they enter in IDLE state, and the

power consumed by a functional block in running state as

well.

The basic block diagram of a sample PORT I/O functional

block is shown Fig.3 All operations need synchronization with

the system clock, and both the edge of clock should be used.

When Input of SIO MUX = 1, that means , PORT blocks are

not being used but SIO block is being used. We adopt clock

gating technique to the clock of PORT block. When the PORT

blocks are in running state the clock becomes disable. Hence ,

it is easy to reduce power dissipation of the unused blocks.

Fig. (2) Standard Design Flow

Fig. (2) ACG Principle for Low Power Design

A. APPICATION OF CLOCK GATING TECHNIQUE

Now a days Dynamic power management (DPM) has become

very popular in low power vlsi design area. The concept of

DPM is to minimize switching speed as much as possible, by

using clock gating technique . Instruction level clock gating

technique is being used to control the clock of Mux, SAR,

Register tree. The basic procedure is shown in Fig. 3.

B.

CLOCK GATED ADC ARCHITECTURE

The method of calibration is responsible to select an optimal

set of comparators for this particular design and the reason

behind this is the low power consumption of this method. The

comparators are disabled by clock gating method to reduce

the power consumption. Out of all clock gating here we use

NAND gate as a local clock driver for all comparators as

shown in Fig. 3.

Where,

PORT I/O = I/O port operation,

ID = instruction decode operation,

IF = instruction fetch operation,

SIO = UART operation means transmission and reception

Port

1762

IJRITCC | June 2014, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 2 Issue: 6

ISSN: 2321-8169

1761 1763

_______________________________________________________________________________________________

value is read inside by SC, OE and EOC, and 8 bit

parallel data sequence mentioned in link above, and

then clock is topped again. This will result into power

saving.

:

V. CONCLUSION AND FUTURE WORK

Here we have used clock gating techniques (ACG) in

functional block designing of ADC. As it is mentioned above

the drawbacks of existing ADC, so we are proposing the

ACG, which is more efficient and easy for low power VLSI

design for sequential as well as combinational circuits. It can

also enhance switching speed along with reduction in power

consumption by using same technique. We can reduce area as

well, if we want to.

ACKNOWLEDGMENT

Fig. (3) Clock Gated Comparator

The NAND-gate is chosen to emphasize the rising edge of the

clock at minimal clock load. When clock is disabled, the

comparators will be go on the latching state i.e. in waiting

state so that there will not be any effect of changes in the input

signal or will not dissipate power due to switching. latched

output has only two states either high i.e. 1 or low i.e. 0.

The enable signal is also used to reset the output signal in the

subsequent latch to prevent the disabled comparator from

biasing the final output. A serial-to-parallel-interface (SPI) is

being used to program the enable signal register through an

prt which is externally connect to it . It also leads to less power

dissipation.

Vref to the comparators are generated by a voltage divider

circuit known as resistor ladder. It also causes power

dissipation , but the amount is very low so we can neglect it .

IV. METHODOLOGY

FPGA board runs at 4-35Mhz and ADC runs at typical

frequency of 650Khz.

Using counter and clock divider we will divide main

FPGA clock to get desired frequency. That frequency

controller through AND gate will be sent out from

FPGA on a port pin and given to ADC0808 IC.

There will be a gating variable bit declared inside

VHDL code. This bit and generated 650Khz

frequency will be giben to AND gate. If that bit is

high clock will be fed to ADC otherwise no clock.

Now when program needs some external analog value

to be read, it will activate the clock for ADC, ADS

I would like to express my special thanks of gratitude to

my guide Mr. Surendra Waghmare , HOD Vijay Kumar Joshi,

as well as our Principal Dr. D. D. Shah who gave me the

golden opportunity to do this wonderful project on the topic

Power Optimization of I/O Ports using Clock Gating

Techniques , which also helped me in doing a lot of Research

and i came to know about so many new things I am really

thankful

to

them.

Secondly i would also like to thank my parents and friends

who helped me a lot in finalizing this project within the

limited time frame.

REFERENCES

[1]

[2]

[3]

[4]

[5]

Jagritkathuria, M. Ayoubkhan, Arti Noor, A Review of

Clock Gating Technique , IJECE, ISSN: 2230-7672, Vol.1, Issue-2, Aug-2011.

Q. Wu, M. Pedram, and X. Wu, Clock gating and its

application to low power design of sequential circuits

IEEE Transactions on Circuits and Systems I, Vol.- 47, pp.

415-420, 2000.

Hyeon-Mi Yang, Sea-Ho Kim, Keun-Sik Park, Hi-Seok

Kim, Low Power Input/Output Port Design Using Clock

Gating TechniqOue ISSN: 1790-5117, ISBN: 978-960474-162-5.

Upwinderkaur , Rajesh Mehra, Low Power CMOS

Counter using Clock Gated Flip-Flop, IJEAT, ISSN:22498958, Vol-2, Issue-4, April-2013.

John F. Wakerly Digital Design Principles and Practices,

Prentice Hall, 2005.

WEBSITES:

[6]

[7]

[8]

[9]

[10]

www.springerlink.com

www.opencore.org.

www.freebsd.org

www.wikipedia.com

www.national.com

1763

IJRITCC | June 2014, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

Potrebbero piacerti anche

- Importance of Similarity Measures in Effective Web Information RetrievalDocumento5 pagineImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCNessuna valutazione finora

- A Review of 2D &3D Image Steganography TechniquesDocumento5 pagineA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNessuna valutazione finora

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocumento5 pagineDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCNessuna valutazione finora

- Channel Estimation Techniques Over MIMO-OFDM SystemDocumento4 pagineChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNessuna valutazione finora

- A Study of Focused Web Crawling TechniquesDocumento4 pagineA Study of Focused Web Crawling TechniquesEditor IJRITCCNessuna valutazione finora

- Prediction of Crop Yield Using LS-SVMDocumento3 paginePrediction of Crop Yield Using LS-SVMEditor IJRITCCNessuna valutazione finora

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocumento3 paginePredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaNessuna valutazione finora

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocumento5 pagineHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaNessuna valutazione finora

- Itimer: Count On Your TimeDocumento4 pagineItimer: Count On Your Timerahul sharmaNessuna valutazione finora

- 45 1530697786 - 04-07-2018 PDFDocumento5 pagine45 1530697786 - 04-07-2018 PDFrahul sharmaNessuna valutazione finora

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineDocumento4 paginePaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCNessuna valutazione finora

- 44 1530697679 - 04-07-2018 PDFDocumento3 pagine44 1530697679 - 04-07-2018 PDFrahul sharmaNessuna valutazione finora

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocumento3 pagineSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaNessuna valutazione finora

- 41 1530347319 - 30-06-2018 PDFDocumento9 pagine41 1530347319 - 30-06-2018 PDFrahul sharmaNessuna valutazione finora

- 49 1530872658 - 06-07-2018 PDFDocumento6 pagine49 1530872658 - 06-07-2018 PDFrahul sharmaNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Differential PairDocumento6 pagineDifferential PairAjay Kumar MattupalliNessuna valutazione finora

- Smart Relay - Zelio Logic SR2 - SR3 - SR2B201JDDocumento6 pagineSmart Relay - Zelio Logic SR2 - SR3 - SR2B201JDWilfredo GarciaNessuna valutazione finora

- MPMC QB ANS 3 0 (Both QB)Documento65 pagineMPMC QB ANS 3 0 (Both QB)Gangadhar JenaNessuna valutazione finora

- Questions On Asynchronous & Synchronous Counters With Solutions (1987 2014)Documento11 pagineQuestions On Asynchronous & Synchronous Counters With Solutions (1987 2014)DHRUV CHAUHANNessuna valutazione finora

- Pin Configuration of 8085Documento3 paginePin Configuration of 8085sarthakNessuna valutazione finora

- RKD & BRK User's ManualDocumento16 pagineRKD & BRK User's ManualRithwik SathyanNessuna valutazione finora

- MC14536B Programmable Timer: PDIP-16 P Suffix CASE 648Documento16 pagineMC14536B Programmable Timer: PDIP-16 P Suffix CASE 648djorjuelaNessuna valutazione finora

- Flip FlopDocumento29 pagineFlip FlopAndleeb juttiNessuna valutazione finora

- Pulse Width ReductionDocumento8 paginePulse Width Reductiongudala praveenNessuna valutazione finora

- MC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648Documento12 pagineMC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648suriantoNessuna valutazione finora

- Laboratory Exercise 9: A Simple ProcessorDocumento8 pagineLaboratory Exercise 9: A Simple ProcessorhxchNessuna valutazione finora

- 18CS33Documento41 pagine18CS33Yawar ShakeelNessuna valutazione finora

- Ed2 Assignment - 7segmentDocumento7 pagineEd2 Assignment - 7segmentdinNessuna valutazione finora

- Presentation - Hartley - Diff PairsDocumento40 paginePresentation - Hartley - Diff Pairsjagadees21Nessuna valutazione finora

- Demystifying Resets Synchronous Asynchronous and Other Design Considerations Part 2Documento9 pagineDemystifying Resets Synchronous Asynchronous and Other Design Considerations Part 2alexNessuna valutazione finora

- P89LPC912/913/914: 1. General DescriptionDocumento63 pagineP89LPC912/913/914: 1. General Descriptionashish gautamNessuna valutazione finora

- Fixing Setup and Hold Violation - Static Timing Analysis (STA) Basic (Part 6c) - VLSI ConceptsDocumento7 pagineFixing Setup and Hold Violation - Static Timing Analysis (STA) Basic (Part 6c) - VLSI ConceptsIlaiyaveni IyanduraiNessuna valutazione finora

- Lecture 8 CTS PDFDocumento40 pagineLecture 8 CTS PDFmayurNessuna valutazione finora

- ICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesDocumento16 pagineICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesStefano Romeu ZeplinNessuna valutazione finora

- MC 33370Documento24 pagineMC 33370Abdel HadiNessuna valutazione finora

- First Reset Signal On Laptop MotherboardDocumento2 pagineFirst Reset Signal On Laptop Motherboardangelito alarasNessuna valutazione finora

- 3900 Series Base Station Technical Description (06) (PDF) - enDocumento502 pagine3900 Series Base Station Technical Description (06) (PDF) - enklajdiNessuna valutazione finora

- 8086 Final ProjectDocumento30 pagine8086 Final ProjecttiggafputuhsNessuna valutazione finora

- QuesbkDocumento6 pagineQuesbkNivithaNessuna valutazione finora

- A Linear High Voltage Charge Pump For MEMS Applications inDocumento4 pagineA Linear High Voltage Charge Pump For MEMS Applications insolidmasteryNessuna valutazione finora

- Digital Electronics - 2 Marks With Answers PDFDocumento40 pagineDigital Electronics - 2 Marks With Answers PDFMANJU C S100% (22)

- 64Kx32 3.3V Synchronous SRAM Pipelined Outputs Burst Counter, Single Cycle DeselectDocumento19 pagine64Kx32 3.3V Synchronous SRAM Pipelined Outputs Burst Counter, Single Cycle DeselectAnonymous T9HtUYccYANessuna valutazione finora

- Keyboard InterfaceDocumento12 pagineKeyboard InterfaceCruise_IceNessuna valutazione finora

- Unit 5 - Electronic Measurement & Instrumentation - WWW - Rgpvnotes.inDocumento12 pagineUnit 5 - Electronic Measurement & Instrumentation - WWW - Rgpvnotes.inRahul kumar singhNessuna valutazione finora

- Berry B Brey Part IDocumento49 pagineBerry B Brey Part Ikalpesh_chandakNessuna valutazione finora