Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Assignment 1

Caricato da

Saqib ZafarCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Assignment 1

Caricato da

Saqib ZafarCopyright:

Formati disponibili

IEC

Fall 2015

Assignment #1

Topics: Differential Pairs, Active Loads, Small Signal Analysis

Due Date: Sept. 30, 2015

Problem 1: (Section 7.1) For the differential amplifier specified in problem

7.1 of Sedra and Smith, assume G2 has been grounded (0 V) and vG1 has

been adjusted to yield iD1 = 0.11 mA and iD2 = 0.09 mA.

(a) What are the corresponding values of vGS1, vGS2, vS , and vid? [vGS1 =

0.97 V, vGS2 = 0.94 V, vS = -0.94 V, vid = 0.03 V ]

(b) What is the differential voltage gain (vD2 vD1/vid)? [3.33 ]

Problem 2: (Section 7.1) Sedra and Smith: Chapter 7, problem 7.8. [VGS =

0.99 V, gm = 1.06 mA/V, vid = 0.27 V, Ibias = 800 A]

Problem 3: (Section 7.2) We would like to design an NMOS differential

amplifier that operates with a differential input voltage as high as vid =

0.2 V. To keep the gain characteristics reasonably linear, we need the

value under the square root in Equation (7.23) of Sedra and Smith to be

no smaller than 0.9. Finally, assume that nCox = 100 A/V2 and a gm of

3 mA/V is required.

(a) What overdrive voltage (VOV ) is required for the transistors? [0.316 V ]

(b) What current (I) should the pair be biased with? [0.95 mA]

(c) What W/L ratio should the transistors be sized with? [95 ]

(d) What differential gain results for RD = 5 k, neglecting channel length

modulation? [15 ]

(e) What is the differential output voltage corresponding to the maximum

differential input voltage? [3 V ]

Problem 4: (Section 7.2) Consider the differential pair shown in Fig. 7.4 of

Sedra and Smith, where vid is a small signal sine wave. The pair is biased

with I = 300

A, and nCox = 100 A/V2. A design error has resulted in a sizing mismatch

between the transistors, with (W/L)1 = 10 and (W/L)2 = 20. You may neglect

channel length modulation.

(a) What are the steady state bias currents for each transistor, ID1 and ID2?

[ID1 = 100 A, ID2 = 200 A]

(b) What is VOV for the two transistors? [0.447 V ]

(c) What is the differential gain (Ad) assuming RD = 5 k? [6.71 ]

Problem 5: (Section 7.2) Sedra and Smith: Chapter 7, problem

7.15. (a) Answer: [|Ad| = 3.85, |Acm| = 0.05, CMRR = 37.7 dB

]

(b) Answer: [|Ad| = 7.7, |Acm| = 0.0005, CMRR = 83.7 dB ]

Problem 6: (Section 7.4) An NMOS differential pair operating at a bias current

I = 100 A uses transistors with n = 100 A/V2, W/L = 20, and Vt = 0.8 V.

kt

(a) How much input offset voltage is introduced if RD/RD = 5%? [5.57 mV ]

(b) How much input offset voltage is introduced if (W/L)/(W/L) =

5%? [5.57 mV ]

(c) How much input offset voltage is introduced if Vt = 5 mV? [5 mV ]

(d) What is the worst case input offset voltage if all three effects are present?

[16.14 mV ]

Problem 7: (Section 6.5) Consider the common source amplifier of Fig. 6.18(a)

2

in the text, where ktn =

p = 250 A/V , |Vt| = 0.6 V, and |VA| = 10 V.

2.5kt

(a) What is the required IREF to obtain an output resistance of 100 k? [0.05

mA]

(b) Find (W/L)1 to obtain a gain of -40 V/V with IREF as specified above.

[6.4 ]

(c) If Q2 and Q3 must have the same overdrive voltages as Q1, find their W/L

ratios. [16 ]

Problem 8:

[gm1 gm2 r2 /4]

(Section 6.5) Sedra and Smith: Chapter 6, problem 6.61.

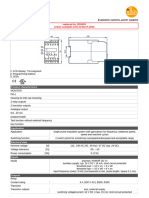

Problem 9: (Section 6.5) Consider the amplifier in Fig. 1. The power

supply voltage is VDD = 5 V; for NMOS devices nCox = 100 A/V2, for

PMOS devices pCox = 50 A/V2, |Vt| = 1 V for all devices, and the sizing

of the transistors is as follows: (W/L)1 = 8m/2m, (W/L)2 = 4m/2m,

and (W/L)3

= 4m/2m. You may ignore channel length modulation for M2 and M3, but

you must consider it for M1 with VA t = 15 V/m.

(a) What is the small signal input resistance, rin? [1620

(b) What is the small signal output resistance, rout? [1480

]

]

(c) What is the small signal voltage gain, vout/vsig ? [-1.24 V/V

Potrebbero piacerti anche

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Brushless DC Electric MotorDocumento8 pagineBrushless DC Electric MotorAngel VelasquezNessuna valutazione finora

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- TL431 Design Tips2 PDFDocumento10 pagineTL431 Design Tips2 PDF3degreesNessuna valutazione finora

- SENB8604-02 Systems Operation GlossaryDocumento41 pagineSENB8604-02 Systems Operation GlossaryChristian BedoyaNessuna valutazione finora

- Investigatory Project On LDRDocumento16 pagineInvestigatory Project On LDRHarsh81% (26)

- Nano ChemistryDocumento15 pagineNano ChemistryJani Basha100% (1)

- Automatic Voltage Regulator Using PIDDocumento1 paginaAutomatic Voltage Regulator Using PIDSaqib ZafarNessuna valutazione finora

- 09IPST042Documento6 pagine09IPST042Saqib ZafarNessuna valutazione finora

- Power System Protection Presentation ScheduleDocumento1 paginaPower System Protection Presentation ScheduleSaqib ZafarNessuna valutazione finora

- Lecture6 UC1 Slides PDFDocumento18 pagineLecture6 UC1 Slides PDFSaqib ZafarNessuna valutazione finora

- PoetryDocumento1 paginaPoetrySaqib ZafarNessuna valutazione finora

- Registers and CountersDocumento21 pagineRegisters and CountersSaqib ZafarNessuna valutazione finora

- Assignment - 3 - Power System Analysis and DesignDocumento2 pagineAssignment - 3 - Power System Analysis and DesignSaqib ZafarNessuna valutazione finora

- Poetry 2Documento1 paginaPoetry 2Saqib ZafarNessuna valutazione finora

- PoetryDocumento1 paginaPoetrySaqib ZafarNessuna valutazione finora

- Lab Report: Engr. Wasim Iqbal Submitted byDocumento7 pagineLab Report: Engr. Wasim Iqbal Submitted byسید کاظمیNessuna valutazione finora

- 2040 Pojacalo Za ZvucniciDocumento16 pagine2040 Pojacalo Za ZvucniciMile SareskiNessuna valutazione finora

- Current ElectricityDocumento28 pagineCurrent ElectricityTEK AYERNessuna valutazione finora

- How To Repair CFL BulbDocumento7 pagineHow To Repair CFL Bulbhernandezacevedo_jNessuna valutazione finora

- DD2003Documento3 pagineDD2003Carlos Eduardo SiqueiraNessuna valutazione finora

- Mitsubishi v500 VFD IB NA 0600135E-A FR-V560 Instruction Manaul-DetailedDocumento243 pagineMitsubishi v500 VFD IB NA 0600135E-A FR-V560 Instruction Manaul-DetailedMROstop.comNessuna valutazione finora

- 1.2V TO 37V VOLTAGE REGULATOR WITH 1.5A OUTPUTDocumento11 pagine1.2V TO 37V VOLTAGE REGULATOR WITH 1.5A OUTPUTchzelNessuna valutazione finora

- Ecd Lab Manual Lab 1Documento4 pagineEcd Lab Manual Lab 1Huma MalikNessuna valutazione finora

- Power Electronics Lab Manual for VII Semester B.E. – ECEDocumento28 paginePower Electronics Lab Manual for VII Semester B.E. – ECEManjunath KalkutagiNessuna valutazione finora

- Signs of DNA Origami Self AssemblyDocumento14 pagineSigns of DNA Origami Self AssemblytrashbinfoodieNessuna valutazione finora

- Gemini Sound X-2 Service ManualDocumento24 pagineGemini Sound X-2 Service Manualbizzinifra5522Nessuna valutazione finora

- 74HC73Documento19 pagine74HC73S. ChavesNessuna valutazione finora

- Electric Trains and Japanese Technology: Breakthrough in Japanese Railways 4Documento9 pagineElectric Trains and Japanese Technology: Breakthrough in Japanese Railways 4Aee TrDNessuna valutazione finora

- 74HC HCT4066 NXPDocumento27 pagine74HC HCT4066 NXPprpabst8514Nessuna valutazione finora

- Commutation Techniques 1Documento19 pagineCommutation Techniques 1mekdi kikNessuna valutazione finora

- Manson Ep-925 Modifications: EP-925 and PALSTAR PS-30MDocumento6 pagineManson Ep-925 Modifications: EP-925 and PALSTAR PS-30MLaurentiu IacobNessuna valutazione finora

- 900 Series Installation v5-1 (English)Documento44 pagine900 Series Installation v5-1 (English)Katneza Katman MohlalaNessuna valutazione finora

- SN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionDocumento19 pagineSN54F32, SN74F32 Quadruple 2-Input Positive-Or Gates: DescriptionAlfonso BlancoNessuna valutazione finora

- ECE320 Chapter 3 PDFDocumento23 pagineECE320 Chapter 3 PDFAhsan NisarNessuna valutazione finora

- Describing Function and Application: InductanceDocumento2 pagineDescribing Function and Application: InductanceAbdulloh KhoironyNessuna valutazione finora

- Bzt52c2v4 Series g1804Documento7 pagineBzt52c2v4 Series g1804Zlatko Mrki HrncicNessuna valutazione finora

- Silicon N-Channel Power MOSFET CS4145 A8H Technical SpecificationsDocumento10 pagineSilicon N-Channel Power MOSFET CS4145 A8H Technical SpecificationsHidayat KhanNessuna valutazione finora

- Moc3051-M, Moc3052-MDocumento10 pagineMoc3051-M, Moc3052-MIvanNessuna valutazione finora

- клон Sunking - ver.3Documento7 pagineклон Sunking - ver.3popovolegNessuna valutazione finora

- 1989 Van Stryland n2Documento3 pagine1989 Van Stryland n2Ra SoNessuna valutazione finora