Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Ee177 Supplement 7

Caricato da

stephen_562001Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Ee177 Supplement 7

Caricato da

stephen_562001Copyright:

Formati disponibili

9/16/2015

Shift Register

SequentialLogic/Circuits:

ShiftRegister

Sequential Logic Circuits

Combinational

outputs

Combinational

logic

Memory

outputs

Memory

elements

Inputs

Sequential circuit = Combinational logic + Memory Elements

Basic shift register function

Serial in/Serial out shift registers (SISO)

Serial in/Parallel out shift registers (SIPO)

Parallel in/Serial out shift registers (PISO)

Parallel in/Parallel out shift registers

(PIPO)

Bidirectional shift registers

Shift register applications

Registers

A register is a memory device that can be used to

store more than one-bit information

A register is usually realized as several flip-flops

with common control signals that control the

movement of data to and from the registers

.

Current State of A sequential Circuit:

Value stored in memory elements (value of state variables).

State transition:

A change in the stored values in memory elements thus changing

the sequential circuit from one state to another state.

9/16/2015

Shift Registers

Registers

An n-bit register is a collection of n D flip-flops with a

common clock used to store n related bits.

Example:

74LS175 4-bit register

74LS175

1D

D

CLR

2D

D

CLR

3D

CLK

/CLR

D

CLR

4D

D

CLR

Multi-bit register that moves stored data bits left/right ( 1

bit

position

per clock

Shift

Left iscycle)

towards MSB

/1Q

Q3 Q2 Q1 Q0

Q3 Q2 Q1 Q0

1Q

CLK

CLR

LSI

1 LSI

2Q

/2Q

1D

3Q

2D

/3Q

4Q

/4Q

3D

4D

1Q

1Q

2Q

2Q

3Q

3Q

4Q

4Q

Shift Right (or Shift Up) is towards MSB

RSI

Q3 Q2 Q1 Q0

Q3 Q2 Q1 Q0

RSI

74LS175

Basic Shift Register Functions

consist of an arrangement of flip-flops

important in applications involving storage and

transfer of data (data movement) in digital system

used for storing and shifting data (1s and 0s)

entered into it from an external source and

possesses no characteristic internal sequence of

states.

D flip-flops are use to store and move data

The flip-flop as a storage element

When a 1 is on D, Q

becomes a 1 at

triggering edge of CLK

or remains a 1 if already

in the SET state

When a 0 is on D, Q

becomes a 0 at

triggering edge of CLK or

remains a 0 if already in

the RESET state

9/16/2015

Basic data movement in shift registers

(Four bits are used for illustration. The bits move in the

direction of the arrows.)

Serial In, Serial Out Shift Registers

(SISO)

Serial In

Clock

Serial In, Serial Out Shift Registers

(SISO)

SO

For a n-bit SRG:

Serial Out = Serial In delayed

by n clock period

CLK

Serial In / Serial Out Shift Registers

(SISO)

Serial In /Parallel Out Shift Registers

(SIPO)

Parallel In / Serial Out Shift Registers

(PISO)

Parallel In / Parallel Out Shift Registers

(PIPO)

SRG n

>

SI

CLK

Types of Shift Registers

Serial Out

4-bit shift register example:

Serial in: 1 0 1 1 0 0 1 1 1 0

Serial out: - - - - 1 0 1 1 0 0

Clock:

CLK

9/16/2015

Serial In, Serial Out Shift Registers

(SISO)

Serial In, Parallel Out Shift registers

(SIPO)

Serial In

Clock

CLK

1Q

2Q

>

SI

SRG n

1Q

2Q

SO

nQ

Serial to Parallel Converter

CLK

nQ

Example: 4-bit shift register

serin: 1 0 1 1 0 0 1 1 1 0

1Q: - 1 0 1 1 0 0 1 1 1

2Q: - - 1 0 1 1 0 0 1 1

3Q: - - - 1 0 1 1 0 0 1

4Q: - - - - 1 0 1 1 0 0

clock:

CLK

9/16/2015

Serial In, Parallel Out Shift registers

(SIPO)

Example:

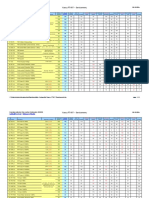

Thestatesof4bitregister(SRG4)forthedatainputandclocks

waveforms.

Data bits entered serially (right-most bit first)

Difference from SISO is the way data bits are taken out of the register in

parallel.

Assume the register initially contains all 1s

Output of each stage is available

Parallel In, Serial Out Shift Registers

(PISO)

4-bit parallel in/serial out shift register (PISO)

CLOCK

LOAD/SHIFT

Serial in

1D

1Q

CLK

S

2D

2Q

CLK

Parallel to Serial

Converter

Load/Shift=1

D i Qi

Load/Shift=0

Qi Qi+1

ND

S

L

NQ

Serial out

CLK

9/16/2015

Parallel In, Parallel Out Shift Register

(PIPO)

Parallel In, Parallel Out Shift Register (PIPO)

CLOCK

LOAD/SHIFT

Serial In

1D

2Q

NQ

CLK

ND

General Purpose:

Makes any kind of

(left) shift register

1Q

CLK

S

2D

D

CLK

Bi-directional Shift Registers

Immediately following simultaneous entry of all data

bits, it appears on parallel output.

Bi-directional Universal Shift Registers

11

Datacanbeshiftedleft

Datacanbeshiftedright

Aparallelloadmaybepossible

74HC194isanbidirectionaluniversalshiftregister

Modes:

Hold

Load

Shift Right

Shift Left

10

9

7

6

5

4

3

2

CLK

CLR

S1

S0

LIN

D

C

B

A

RIN

74x194

QD

QC

QB

QA

12

13

14

15

4-bit Bi-directional Universal (4-bit) PIPO

Function

Hold

Shift right/up

Shift left/down

Load

Mode

S1 S0

0

0

0

1

1

0

1

1

QA*

QA

RIN

QB

A

Next state

QB* QC*

QB QC

QA QB

QC QD

B

C

QD*

QD

QC

LIN

D

9/16/2015

Four-bit Johnson counters

Five-bit Johnson counters

Serial output

connected back

to serial input

The complement

of the output (Q)

is fedback into

1st FF.

A 10-bit ring counter

Shift Register Applications

State Registers

Shift registers are often used as the state register in a sequential

device. Usually, the next state is determined by shifting right and

inserting a primary input or output into the next position (i.e. a

finite memory machine)

Very effective for sequence detectors

Serial Interconnection of Systems

keep interconnection cost low with serial interconnect

Assume initial

state:

1010000000

Bit Serial Operations

Bit serial operations can be performed quickly through device

iteration

Iteration (a purely combinational approach) is expensive (in terms

of # of transistors, chip area, power, etc).

A sequential approach allows the reuse of combinational

functional units throughout the multi-cycle operation

9/16/2015

Shift Register Applications Example:

Serial Interconnection of Systems

CTL

CLK

CLOCK

Transmitter

Control

Circuits

Parallel

Data from

A-to-D

converter

n

Shift Register Applications Example:

8-Bit Serial Adder

Control

/SYNC

>

Circuits

Serial DATA

One bit

x6

x5

y7

y6

y5

x0

...

Sequential Implementation of:

Z[7..0] = X[7..0] + Y[7..0]

Receiver

>

Parallelto-serial

converter

x7

Parallel

Data to

D-to-A

converter

Serial-toparallel

converter

n

y0

...

Cin A

FA

Cout

CLK

CLR

B

S

>

CLEAR_C

z7

z6

z5

...

...

0

z0

Shift Register Applications Example:

The shift register as a time-delay device

Shift Register Applications Example:

Simplified logic diagram of a serial-to-parallel converter

Potrebbero piacerti anche

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- CH 2: Basic MOS Device PhysicsDocumento20 pagineCH 2: Basic MOS Device PhysicsMuhammad FaizanNessuna valutazione finora

- Amf25nt PDFDocumento88 pagineAmf25nt PDFBùi Tấn DũngNessuna valutazione finora

- Cross Box Manual R 10Documento16 pagineCross Box Manual R 10ZalNessuna valutazione finora

- TTL Logic Gates: Laboratory 1Documento3 pagineTTL Logic Gates: Laboratory 1stephen_562001Nessuna valutazione finora

- Ee177 Supplement 4Documento7 pagineEe177 Supplement 4stephen_562001Nessuna valutazione finora

- Ee177 Supplement 3Documento14 pagineEe177 Supplement 3stephen_562001Nessuna valutazione finora

- Ee177 Supplement 2Documento10 pagineEe177 Supplement 2stephen_562001Nessuna valutazione finora

- Introduction To Digital Logic: Number & CodesDocumento14 pagineIntroduction To Digital Logic: Number & Codesstephen_562001Nessuna valutazione finora

- Emt113 - CH5 - Amir RazifDocumento17 pagineEmt113 - CH5 - Amir Razifstephen_562001Nessuna valutazione finora

- Microprocessor ProjectDocumento13 pagineMicroprocessor ProjectshipliNessuna valutazione finora

- Mitsubishi F700 VFD Manual-Applied-Japanese DomesticDocumento303 pagineMitsubishi F700 VFD Manual-Applied-Japanese DomesticMROstop.comNessuna valutazione finora

- Panasonic HDTV TH 42px80uDocumento116 paginePanasonic HDTV TH 42px80uSergio Alexander Pérez ChotoNessuna valutazione finora

- 3BSCB - Decoder and EncoderDocumento11 pagine3BSCB - Decoder and EncoderSunil RajNessuna valutazione finora

- Eeng350 03 PDFDocumento40 pagineEeng350 03 PDFHasan JomaaNessuna valutazione finora

- Study of Micro Wave Components-1Documento6 pagineStudy of Micro Wave Components-1narasimhaNessuna valutazione finora

- MDVR X5 SerieDocumento4 pagineMDVR X5 SerieTTB VisionNessuna valutazione finora

- Complete Analysis of Erbium-Doped Fiber Amplifiers: Technical PaperDocumento15 pagineComplete Analysis of Erbium-Doped Fiber Amplifiers: Technical Paperhanhnguyen2003Nessuna valutazione finora

- SE DS Fronius IG Plus Advanced US ENDocumento2 pagineSE DS Fronius IG Plus Advanced US ENAndreas ENessuna valutazione finora

- Power Quality Lesson PlanDocumento2 paginePower Quality Lesson PlanAnonymous HyOfbJ6Nessuna valutazione finora

- Hfe Pioneer pdr-555rw ServiceDocumento72 pagineHfe Pioneer pdr-555rw ServiceYannisNessuna valutazione finora

- CE223 - Signal Processing: Module Supervisor: Dr. Eirina Bourtsoulatze Eb20668@essex - Ac.ukDocumento18 pagineCE223 - Signal Processing: Module Supervisor: Dr. Eirina Bourtsoulatze Eb20668@essex - Ac.ukHyper - XNessuna valutazione finora

- P521 Commissioning & Test SheetDocumento28 pagineP521 Commissioning & Test SheetDHARMENDRANessuna valutazione finora

- Fpga Viva QuestionDocumento4 pagineFpga Viva QuestionManila MathurNessuna valutazione finora

- Project Report IR Remote TesterDocumento7 pagineProject Report IR Remote TesterNarendar Kumar Oad100% (1)

- 2016 - Programming in Arduino PDFDocumento34 pagine2016 - Programming in Arduino PDFMihai Bogdan100% (1)

- 12 Iostat Examples For Solaris Performance TroubleshootingDocumento5 pagine12 Iostat Examples For Solaris Performance Troubleshootingshekhar785424Nessuna valutazione finora

- AVerTV USB2.0 Plus (M036)Documento1 paginaAVerTV USB2.0 Plus (M036)min2bal4uNessuna valutazione finora

- 2SC9012 PromaxJohntonDocumento3 pagine2SC9012 PromaxJohntonsenel1020% (1)

- Introduction To Introduction To 8085 8085: MicroprocessorDocumento12 pagineIntroduction To Introduction To 8085 8085: MicroprocessorunchalliNessuna valutazione finora

- FT-817 Softw Adjustment Menu Tabela Com Valores DefaultDocumento6 pagineFT-817 Softw Adjustment Menu Tabela Com Valores DefaultDaniel CoslovskyNessuna valutazione finora

- File ListDocumento15 pagineFile ListLllNessuna valutazione finora

- 1.adc DacDocumento35 pagine1.adc DacGopinathan MNessuna valutazione finora

- Detectomat Katalog 2011Documento226 pagineDetectomat Katalog 2011Milica LolićNessuna valutazione finora

- Pages From Cdfi Phase Final Report-3 2Documento9 paginePages From Cdfi Phase Final Report-3 2api-261836656Nessuna valutazione finora

- Transistors Ucp ADocumento16 pagineTransistors Ucp Azaryabimran222Nessuna valutazione finora

- DHI-NVR2104HS-P-S2: Lite MPDocumento3 pagineDHI-NVR2104HS-P-S2: Lite MPLuis Daniel Asbun FriasNessuna valutazione finora