Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Power Good Signal

Caricato da

Olivier OuinaCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Power Good Signal

Caricato da

Olivier OuinaCopyright:

Formati disponibili

US 20130257511A1

(19) United States

(12) Patent Application Publication (10) Pub. N0.: US 2013/0257511 A1

CHEN et a].

(54)

(43) Pub. Date:

POWER GOOD SIGNAL GENERATING

CIRCUIT

Oct. 3, 2013

Publication Classi?cation

(51)

(71) ApplicantszCHUN-SHENG CHEN, Tu-Cheng

(TW); HUA ZOU, Wuhan City (CN)

Int. Cl.

H03K 17/042

(52) U5, Ci,

UsPc

(2006.01)

........................................................ ..

327/377

(72) Inventors: CHUN-SHENG CHEN, Tu-Cheng

(TW); HUA ZOU, Wuhan City (CN)

(57)

ABSTRACT

(21) App1.N0.: 13/656,545

(22)

(30)

Filed;

Oct 19, 2012

A circuit includes ?rst to ?fth resistors and ?rst to third

electronic sWitches. The circuit allows a signal from a ?rst

Foreign Application Priority Data

Mar. 27, 2012

terminal of the second electronic sWitch to change from a loW

level to a high level gradually, and to change from a high level

(CN) ....................... .. 2012100839012

to a loW level abruptly.

+3V_DUAL

O

+ 5V S B

O

+5V SB

3 R1

2 Ra

Re 2

R4

D1

'4

-_o PWRIIIK

R5

'

R3

Q1 |/

|\

E R 8 -- C1

K Q8

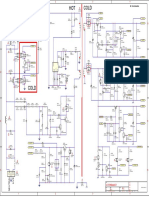

Patent Application Publication

Oct. 3,2013

US 2013/0257511 A1

+3V_DUAL

+5VSB

+5VSB

0

2R1

<

D1

R4

:4

-_<> PWRIIIK

R5

NV

R3

R63

91K

2R2 E R8 -: C1

KGB

Oct. 3, 2013

US 2013/0257511A1

POWER GOOD SIGNAL GENERATING

CIRCUIT

BACKGROUND

of the transistor Q3 is grounded. A collector of the transistor

Q3 is connected to the cathode of the diode D1 through the

resistor R8.

[0012] When an external poWer supply is connected to the

motherboard, a voltage received by the standby poWer termi

[0001] 1. Technical Field

[0002] The present disclosure relates to a signal generating

circuit.

[0003] 2. Description of Related Art

[0004] In motherboards, the period of time Within Which

signals change needs to be specially designed. For example, a

voltage received by the standby poWer terminal +5 VSB is

less than 4.3 volts, according to the resistances of the resistors

R1, R2, and R3, a voltage at the base of the transistor Q1 is

less than a turn-on voltage of the transistor Q1 (Which is equal

to 0.65 volts) such that the transistor Q1 is turned off. The

poWer good signal needs to be changed from a loW level to a

high level gradually, and changed from a high level to a loW

transistor Q2 outputs a loW level signal, namely the signal

level rapidly. It is costly to design and manufacture circuitry

to achieve these Working parameters.

BRIEF DESCRIPTION OF THE DRAWING

[0005] Many aspects of the embodiments can be better

understood With reference to the folloWing draWing. The

components in the draWings are not necessarily draWn to

scale, the emphasis instead being placed upon clearly illus

trating the principles of the present embodiments.

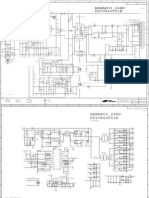

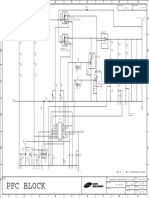

[0006] The FIGURE is a circuit diagram of an exemplary

embodiment of a signal generating circuit.

DETAILED DESCRIPTION

[0007] The disclosure, including the accompanying draW

ing, is illustrated by Way of examples and not by Way of

limitation. It should be noted that references to an or one

embodiment in this disclosure are not necessarily to the same

embodiment, and such references mean at least one.

[0008] Referring to the FIGURE, an exemplary embodi

ment of the signal generating circuit is illustrated, the signal

generating circuit outputs a poWer good signal PWROK. The

signal generating circuit is set on a motherboard. The signal

generating circuit processes a signal to be output as a

nal +5 VSB is increased from 0 volt to 5 volts. When the

transistors Q2 and Q3 are turned on. The collector of the

PWROK is at a loW level.

[0013]

When the voltage received by the standby poWer

terminal +5 VSB is 4.7 volts, the voltage at the base of the

transistor Q1 is 0.65 volts. The transistor Q1 is turned on, and

the transistors Q2 and Q3 are turned off. The collector of the

transistor Q2 outputs a high level signal, that is to say the

signal PWROK is then at a high level and has become the

poWer good signal.

[0014] When the voltage received by the standby poWer

terminal +5 VSB is stable, namely the voltage received by the

standby poWer terminal +5 VSB is 4.7 volts to 5 volts, the

poWer good signal PWROK is maintained at a high level.

[0015] When the external poWer supply is disconnected

from the motherboard, the voltage received by the standby

poWer terminal +5 VSB is decreased from 5 volts to 0 volts.

As long as the voltage received by the standby poWer terminal

+5 VSB is greater than 4.7 volts, the poWer good signal

PWROK is maintained at a high level. When the voltage being

received by the standby poWer terminal +5 VSB is less than

4.7 volts, the base ofthe transistor Q1 is less than 0.65 volts,

such that the transistor Q1 is turned off. At this time, the

collector of the transistor Q1 is at a high level. The transistor

Q3 is turned on. The transistor Q2 is turned on, such that the

collector of the transistor Q2 is at a loW level. In other Words,

a loW level) rapidly.

the high level signal indicating PWROK drops instantly to a

loW level signal.

[0016] From the above description, When the voltage

received by the standby poWer terminal +5 VSB is increased

[0009]

to at least 4.7 volts from 0 volts, the poWer good signal

PWROK signal developing gradually from a loW level to a

high level, and to output a reverse signal (from a high level to

The signal generating circuit includes resistors

R1-R8, a capacitor C1, a diode D1, and transistors Q1-Q3. A

PWROK changes over a period of time from a loW level to a

standby poWer terminal +5 VSB on the motherboard is

high level. When the voltage received by the standby poWer

grounded through the resistors R1 and R2 connected in series.

A node betWeen the resistors R1 and R2 is grounded through

the resistor R3 and the capacitor C1 connected in series. A

terminal +5 VSB is reduced to at least 4.7 volts from 5 volts,

cathode of the diode D1 is connected to the node betWeen the

resistors R1 and R2. An anode of the diode D1 is connected to

a node betWeen the resistor R3 and the capacitor C1. The

resistors R1 and R2 make up a voltage divider circuit.

[0010] Abase of the transistor Q1 is connected to the node

betWeen the resistor R3 and the capacitor C1. An emitter of

the transistor Q1 is grounded. A collector of the transistor Q1

is connected to the standby poWer terminal +5 VSB through

the resistor R4. The collector of the transistor Q1 is further

the poWer good signal PWROK changes suddenly from a high

level to a loW level signal. In other Words, the PWROK signal

can be changed from a loW level to a high level sloWly, and

changed from a high level to a loW level rapidly.

[0017]

In the embodiment, the transistors Q1-Q3 function

as electronic sWitches.

[0018] The foregoing description of the exemplary

embodiments of the disclosure has been presented only for

the purposes of illustration and description and is not

intended to be exhaustive or to limit the disclosure to the

precise forms disclosed. Many modi?cations and variations

connected to a base of the transistor Q2 through the resistor

R5. An emitter of the transistor Q2 is grounded. A collector of

the transistor Q2 is connected to a dual poWer terminal +3V_

DUAL on the motherboard through the resistor R6. The col

lector of the transistor Q2 outputs a signal PWROK as a

With various modi?cations as are suited to the particular use

poWer good signal.

contemplated. Alternative embodiments Will become appar

[0011] A base of the transistor Q3 is connected to the col

lector of the transistor Q1 through the resistor R7. An emitter

disclosure pertains Without departing from its spirit and

are possible. The embodiments Were chosen and described in

order to explain the principles of the disclosure and their

practical application so as to enable others of ordinary skill in

the art to utiliZe the disclosure and various embodiments and

ent to those of ordinary skills in the art to Which the present

Oct. 3, 2013

US 2013/0257511Al

scope. Accordingly, the scope of the present disclosure is

de?ned by the appended claims rather than by the foregoing

description and the exemplary embodiments described

therein.

What is claimed is:

1. A circuit to generate a signal, the circuit comprising:

?rst to ?fth resistors, Wherein a ?rst terminal of the ?rst

resistor is connected to a ?rst poWer terminal, a second

terminal of the ?rst resistor is grounded through the

second resistor; and

?rst to third electronic sWitches, Wherein a control terminal

of the ?rst electronic sWitch is connected to a node

betWeen the ?rst and second resistors, a ?rst terminal of

the ?rst electronic sWitch is connected to the ?rst poWer

terminal through the third resistor, a second terminal of

the ?rst electronic sWitch is grounded, the ?rst terminal

of the ?rst electronic sWitch is further connected to con

trol terminals of the second and third electronic

sWitches, a ?rst terminal of the second electronic sWitch

is connected to a second poWer terminal through the

fourth resistor, the ?rst terminal of the second electronic

sWitch further outputs the signal, a second terminal of

the second electronic sWitch is grounded, a ?rst terminal

of the third electronic sWitch is connected to a node

betWeen the ?rst and second resistors through the ?fth

resistor, a second terminal of the third electronic sWitch

is grounded.

2. The circuit of claim 1, further comprising a sixth resistor

and a capacitor, Wherein the sixth resistor is connected to the

node betWeen the ?rst and second resistors and the control

terminal of the ?rst electronic sWitch, a ?rst terminal of the

capacitor is connected to the control terminal of the ?rst

electronic sWitch, a second terminal of the capacitor is

grounded.

3. The circuit of claim 2, further comprising a diode,

Wherein an anode of the diode is connected to the control

terminal of the ?rst electronic sWitch, a cathode of the diode

is connected to the node betWeen the ?rst and second resis

tors.

4. The circuit of claim 1, further comprising a seventh

resistor, Wherein a ?rst terminal of the seventh resistor is

connected to the ?rst terminal of the ?rst electronic sWitch, a

second terminal of the seventh resistor is connected to the

control terminal of the second electronic sWitch.

5. The circuit of claim 1, further comprising an eighth

resistor, Wherein a ?rst terminal of the eighth resistor is con

nected to the ?rst terminal of the ?rst electronic sWitch, a

second terminal of the eighth resistor is connected to the

control terminal of the third electronic sWitch.

6. The circuit of claim 1, Wherein the ?rst poWer terminal is

a standby poWer, the second poWer terminal is a dual poWer,

the signal output from the ?rst terminal of the second elec

tronic sWitch is a poWer good signal.

7. The circuit of claim 1, Wherein each of the ?rst to third

electronic sWitches is a transistor, the control terminal of each

electronic sWitch is a base of the transistor, the ?rst terminal

of each electronic sWitch is a collector of the transistor, the

second terminal of each electronic sWitch is an emitter of the

transistor.

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDa EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsValutazione: 3 su 5 stelle3/5 (2)

- Aec Mini Project 7 1 1Documento8 pagineAec Mini Project 7 1 1Surendra MalluNessuna valutazione finora

- Linear Wave Shaping: Department of Electronics and Communication EngineeringDocumento0 pagineLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaNessuna valutazione finora

- Sweep GeneratorDocumento9 pagineSweep GeneratorHaridas C SNessuna valutazione finora

- Optimise vintage radio performance with an inexpensive wobbulator unitDocumento8 pagineOptimise vintage radio performance with an inexpensive wobbulator unitNestor Alberto Escala0% (2)

- NE555 Astable MultivibratorDocumento6 pagineNE555 Astable Multivibratorbhanuka2009Nessuna valutazione finora

- AB89Documento12 pagineAB89Sourabh SharmaNessuna valutazione finora

- Mit Aec Labmanula 10esl37Documento45 pagineMit Aec Labmanula 10esl37anon_70724250Nessuna valutazione finora

- Eleg. 2111 Laboratory 6 "Q" Factor and Transient Response of An RLC Series CircuitDocumento9 pagineEleg. 2111 Laboratory 6 "Q" Factor and Transient Response of An RLC Series Circuitpra_zara2637Nessuna valutazione finora

- Oscillator NotesDocumento11 pagineOscillator NotesHarsh SinghNessuna valutazione finora

- The Transistor Astable Multi VibratorDocumento6 pagineThe Transistor Astable Multi VibratorTavleen KaurNessuna valutazione finora

- Astable MultivibratorDocumento38 pagineAstable MultivibratorSherry Sher0% (1)

- United States Patent (10) Patent No.: US 8,520,412 B2Documento25 pagineUnited States Patent (10) Patent No.: US 8,520,412 B2david19775891Nessuna valutazione finora

- Expt 5 - Wein Bridge Oscillator (2020)Documento3 pagineExpt 5 - Wein Bridge Oscillator (2020)samarthNessuna valutazione finora

- Multivibrator Manual PDFDocumento73 pagineMultivibrator Manual PDFAvijitRoyNessuna valutazione finora

- N. Bacalso Avenue, Cebu City: Cebu Institute of Technology - UniversityDocumento15 pagineN. Bacalso Avenue, Cebu City: Cebu Institute of Technology - UniversityTreyes RobertNessuna valutazione finora

- Self Oscillating Flyback ConverterDocumento7 pagineSelf Oscillating Flyback ConverterNaren DranNessuna valutazione finora

- PDC Lab Updated 1Documento63 paginePDC Lab Updated 1deepa reddyNessuna valutazione finora

- Astable MultivibratorDocumento146 pagineAstable Multivibratorsantovaron123Nessuna valutazione finora

- Development of The Carioca Front-End Chip For The LHCB Muon DetectorDocumento11 pagineDevelopment of The Carioca Front-End Chip For The LHCB Muon DetectorAmir SultanNessuna valutazione finora

- Astable CircuitsDocumento9 pagineAstable CircuitsRavindranath ShrivastavaNessuna valutazione finora

- Selman Kasim Bağirici 2008514046 Signal GeneratorsDocumento40 pagineSelman Kasim Bağirici 2008514046 Signal GeneratorsSelman BağırıcıNessuna valutazione finora

- A Simple Square Rooting Circuit Based On Operational Amplifiers (Opamps)Documento3 pagineA Simple Square Rooting Circuit Based On Operational Amplifiers (Opamps)Harendra Kumar100% (1)

- Application of IC 555Documento6 pagineApplication of IC 555ManojkumarNessuna valutazione finora

- PDC Lab ManualDocumento33 paginePDC Lab ManualBhanu SriNessuna valutazione finora

- Electronics Circuits DesignDocumento9 pagineElectronics Circuits DesignDhayala Sundaram KandanNessuna valutazione finora

- Experiment 1Documento7 pagineExperiment 1Clement RajNessuna valutazione finora

- EDC Lab ManualDocumento48 pagineEDC Lab ManualDishan D Shah100% (1)

- World University of Bangladesh: Experiment 6: Study of A Wein Bridge Oscillator CircuitDocumento2 pagineWorld University of Bangladesh: Experiment 6: Study of A Wein Bridge Oscillator CircuitshajibNessuna valutazione finora

- MultivibratorsDocumento14 pagineMultivibratorsMuhammadSajidNessuna valutazione finora

- ESD Lab Manual PDFDocumento67 pagineESD Lab Manual PDFAnonymous mg0FcO1xjNessuna valutazione finora

- Chapter Three System Driver 3.1 MOSFET Control CircuitDocumento11 pagineChapter Three System Driver 3.1 MOSFET Control CircuitAlhussain EmbarkNessuna valutazione finora

- PEL Lab ManualDocumento127 paginePEL Lab Manualmksamy2021Nessuna valutazione finora

- ECEN4618: Experiment #1 Timing Circuits With The 555 TimerDocumento9 pagineECEN4618: Experiment #1 Timing Circuits With The 555 TimerMashgol KarimNessuna valutazione finora

- DC Lab ManualDocumento43 pagineDC Lab ManualSowmya KharviNessuna valutazione finora

- Power Electronics Lab (Part-1)Documento98 paginePower Electronics Lab (Part-1)Muhammad zohaibNessuna valutazione finora

- Astable MultivibratorDocumento4 pagineAstable MultivibratorDa100% (1)

- PDC Lab ManualDocumento46 paginePDC Lab ManualKumar Goud.K90% (10)

- Silicon Controlled Rectifier ExplainedDocumento10 pagineSilicon Controlled Rectifier ExplainedJenny MaristelaNessuna valutazione finora

- Analogue Electronics Lab ReportDocumento8 pagineAnalogue Electronics Lab ReportKing EverestNessuna valutazione finora

- Measure and Design a RC Phase Shift OscillatorDocumento4 pagineMeasure and Design a RC Phase Shift OscillatorNA NANessuna valutazione finora

- Prototipo de Encendido ElectronicoDocumento4 paginePrototipo de Encendido ElectronicoEmernelsonNessuna valutazione finora

- Function GeneratorDocumento78 pagineFunction GeneratorVishali Chowdary100% (1)

- BSME diode waveform shapingDocumento9 pagineBSME diode waveform shapingJoshua G. BasasNessuna valutazione finora

- What Are Astable Multi-Vibrator, Its Wave Form, Saturated Point, Cutoff Point and Application? Astable MultivibratorDocumento7 pagineWhat Are Astable Multi-Vibrator, Its Wave Form, Saturated Point, Cutoff Point and Application? Astable MultivibratorwilliamNessuna valutazione finora

- Build 555 Monostable MultivibratorsDocumento6 pagineBuild 555 Monostable MultivibratorsPriyanshu KumawatNessuna valutazione finora

- IC 555 ProjectsDocumento14 pagineIC 555 ProjectsParth Lad100% (1)

- Currents Through Inductances, Capacitances and ResistancesDocumento14 pagineCurrents Through Inductances, Capacitances and ResistancesZulu LoveNessuna valutazione finora

- EEE 54 DP2 DocumentationDocumento5 pagineEEE 54 DP2 DocumentationDarl John MendozaNessuna valutazione finora

- Visit Electronics Club for 555 Timer GuideDocumento13 pagineVisit Electronics Club for 555 Timer GuideMehar GuptaNessuna valutazione finora

- Single transistor circuit converts 12V DC to 230V ACDocumento7 pagineSingle transistor circuit converts 12V DC to 230V ACyr48Nessuna valutazione finora

- 4 OscillatorsDocumento12 pagine4 OscillatorsTeshale AlemieNessuna valutazione finora

- Pee Lab ManualDocumento77 paginePee Lab ManualRajendraTuraka100% (1)

- Oscillator CircuitsDocumento19 pagineOscillator Circuits21-08523Nessuna valutazione finora

- Project Report: Water Level IndicatorDocumento14 pagineProject Report: Water Level IndicatorMayank BansalNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Farm AnimalDocumento20 pagineFarm AnimalOlivier OuinaNessuna valutazione finora

- How To Solve Ramdomly No Power ShutdownDocumento2 pagineHow To Solve Ramdomly No Power ShutdownOlivier OuinaNessuna valutazione finora

- Fonte Samsung LN32B350F1Documento2 pagineFonte Samsung LN32B350F1atomo33100% (3)

- BN44 00277a PDFDocumento5 pagineBN44 00277a PDFOlivier OuinaNessuna valutazione finora

- Evidence of Success: A Better Backyard Broiler For Rural IndiaDocumento3 pagineEvidence of Success: A Better Backyard Broiler For Rural IndiaOlivier OuinaNessuna valutazione finora

- Document revision and sheet numberDocumento5 pagineDocument revision and sheet numberrponce161276100% (1)

- Common Diseases & Ailments of TurkeysDocumento18 pagineCommon Diseases & Ailments of TurkeysOlivier OuinaNessuna valutazione finora

- READ HIGHLIGHTED CHANGES IN TOXOPLASMOSIS TESTDocumento10 pagineREAD HIGHLIGHTED CHANGES IN TOXOPLASMOSIS TESTOlivier OuinaNessuna valutazione finora

- Calcul Odds Ratio in RDocumento14 pagineCalcul Odds Ratio in ROlivier OuinaNessuna valutazione finora

- BN44 00273B PDFDocumento3 pagineBN44 00273B PDFHamza Abbasi AbbasiNessuna valutazione finora

- Data Sheet: Beyond Innovation Technology Co., LTDDocumento6 pagineData Sheet: Beyond Innovation Technology Co., LTDOlivier OuinaNessuna valutazione finora

- BN44 00155aDocumento2 pagineBN44 00155aCaptain444100% (1)

- Samsung Power Board Circuit BN44-00273D PDFDocumento3 pagineSamsung Power Board Circuit BN44-00273D PDFJejeNessuna valutazione finora

- BN44 00273B PDFDocumento3 pagineBN44 00273B PDFHamza Abbasi AbbasiNessuna valutazione finora

- China TV Tda11105Documento1 paginaChina TV Tda11105eu1992ro100% (1)

- Computer - Hardware - Diagnosing & Fixing Motherboard FaultsDocumento4 pagineComputer - Hardware - Diagnosing & Fixing Motherboard Faultsscribdraza786Nessuna valutazione finora

- Computer - Hardware - Diagnosing & Fixing Motherboard FaultsDocumento4 pagineComputer - Hardware - Diagnosing & Fixing Motherboard Faultsscribdraza786Nessuna valutazione finora

- BN44 00273B PDFDocumento3 pagineBN44 00273B PDFHamza Abbasi AbbasiNessuna valutazione finora

- Op To IsolatorsDocumento14 pagineOp To IsolatorsOlivier OuinaNessuna valutazione finora

- Toshiba 40XF550U LCD200917 - TB Service BulletinDocumento1 paginaToshiba 40XF550U LCD200917 - TB Service BulletinOlivier OuinaNessuna valutazione finora

- 02 Inkjet PrinterDocumento12 pagine02 Inkjet PrinterOlivier OuinaNessuna valutazione finora

- Laptop Power SequencingDocumento14 pagineLaptop Power SequencingOlivier Ouina100% (2)

- Multimeter Operation ManualDocumento4 pagineMultimeter Operation ManualOlivier OuinaNessuna valutazione finora

- 09 - LEDs Power SuppliesDocumento1 pagina09 - LEDs Power SuppliesOlivier OuinaNessuna valutazione finora

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocumento28 pagineBias Power Supply For TV and Monitor TFT LCD Panels: Featuresmitesh12123Nessuna valutazione finora

- A Detailed Look Into Psus: Switching Regulator Topologies Used in Contemporary PsusDocumento3 pagineA Detailed Look Into Psus: Switching Regulator Topologies Used in Contemporary PsusOlivier OuinaNessuna valutazione finora

- A Detailed Look Into Psus: Switching Regulator Topologies Used in Contemporary PsusDocumento3 pagineA Detailed Look Into Psus: Switching Regulator Topologies Used in Contemporary PsusOlivier OuinaNessuna valutazione finora

- Csail: Identification and Authentication of Integrated CircuitsDocumento26 pagineCsail: Identification and Authentication of Integrated CircuitsOlivier OuinaNessuna valutazione finora

- Snteng 6Documento3 pagineSnteng 6ashkanr65Nessuna valutazione finora

- DTC U0028 - 87 (Advanced Keyless Entry and Push Button Start System)Documento2 pagineDTC U0028 - 87 (Advanced Keyless Entry and Push Button Start System)Yousef ShishaniNessuna valutazione finora

- SK 19517Documento2 pagineSK 19517Carey C Jones100% (1)

- Strand Century Lighting 2669-2660 12x12-Inch Lekolite Ellipsoidal Spotlight Spec Sheet 6-77Documento2 pagineStrand Century Lighting 2669-2660 12x12-Inch Lekolite Ellipsoidal Spotlight Spec Sheet 6-77Alan MastersNessuna valutazione finora

- Inami Slitlamp ManualDocumento17 pagineInami Slitlamp ManualmonicaNessuna valutazione finora

- Cummins: Fault Code: 298 PID: P223 SPN: 1084 FMI: 4Documento4 pagineCummins: Fault Code: 298 PID: P223 SPN: 1084 FMI: 4Enrrique LaraNessuna valutazione finora

- WEG Indústrias S.A.: Performance Curves Related To SpeedDocumento1 paginaWEG Indústrias S.A.: Performance Curves Related To SpeedidontlikeebooksNessuna valutazione finora

- DEWA - List of Civil Standard DrawingsDocumento14 pagineDEWA - List of Civil Standard Drawingsraviaggrawalla8727Nessuna valutazione finora

- Electrical Engineer Seeking Challenging RoleDocumento3 pagineElectrical Engineer Seeking Challenging RoleHeidi RamosNessuna valutazione finora

- Toyota Camry Body ElectricalDocumento10 pagineToyota Camry Body ElectricalJohn100% (49)

- EATSDocumento10 pagineEATSrsivanandNessuna valutazione finora

- Product Selection Guide: Cable AccessoriesDocumento44 pagineProduct Selection Guide: Cable Accessoriesricardo139Nessuna valutazione finora

- Service T Service T Service T Service T Service Training Raining Raining Raining RainingDocumento18 pagineService T Service T Service T Service T Service Training Raining Raining Raining RainingMohammed Yassine GarrebNessuna valutazione finora

- Red 47 Bom+Doc v1.2Documento7 pagineRed 47 Bom+Doc v1.2mrgreengenesNessuna valutazione finora

- Device Status Number Suffix Code Latest Release Latest NumberDocumento36 pagineDevice Status Number Suffix Code Latest Release Latest NumberGracia SediNessuna valutazione finora

- P&F Catalogue Proximity SensorDocumento1 paginaP&F Catalogue Proximity SensorAnshuman MitraNessuna valutazione finora

- Earth-Fault and Short-Circuit Indicator Type: Elektro-MechanikDocumento5 pagineEarth-Fault and Short-Circuit Indicator Type: Elektro-MechanikkotiniNessuna valutazione finora

- Parts Manual: 872238 B40D 6X6 ADT MK VI - A840D60 B35D 6X6 ADT MK VI - A835D60 B35D 6X6 WDB Adt MK Vi - A836D60Documento864 pagineParts Manual: 872238 B40D 6X6 ADT MK VI - A840D60 B35D 6X6 ADT MK VI - A835D60 B35D 6X6 WDB Adt MK Vi - A836D60Biswajit DasNessuna valutazione finora

- SM 89Documento36 pagineSM 89Camilo RamosNessuna valutazione finora

- Fuse and Types of Fuses - Constructio, Operation & ApplicationsDocumento9 pagineFuse and Types of Fuses - Constructio, Operation & ApplicationsKhaled RabeaNessuna valutazione finora

- 62 Low Voltage TransformersDocumento36 pagine62 Low Voltage TransformersBob Mitzel NavarreteNessuna valutazione finora

- Engine Speed AdjustmentDocumento1 paginaEngine Speed Adjustmentsixin93551Nessuna valutazione finora

- Water Pump Commissioning ChecklistDocumento2 pagineWater Pump Commissioning ChecklistUcok RapuiNessuna valutazione finora

- Metric: Dwgb001 Dwg. Tol. and InterpDocumento26 pagineMetric: Dwgb001 Dwg. Tol. and InterpAndré MariaNessuna valutazione finora

- Cable Current Carrying Capacities PDFDocumento3 pagineCable Current Carrying Capacities PDFSanoj Deepak PNessuna valutazione finora

- Connecting an engine control moduleDocumento1 paginaConnecting an engine control moduleOmar Hernández100% (1)

- Thomelec - Ke-Fkr4 ENGDocumento1 paginaThomelec - Ke-Fkr4 ENGGabriel DelfinoNessuna valutazione finora

- SPECIFICATIONS FOR BUILDING FOUNDATIONSDocumento2 pagineSPECIFICATIONS FOR BUILDING FOUNDATIONSvijjikewlguy7116Nessuna valutazione finora

- ECU Pinout AWP Vs AZGDocumento8 pagineECU Pinout AWP Vs AZGB-ertNessuna valutazione finora

- Beacon BomDocumento7 pagineBeacon BomAnkurNessuna valutazione finora

- CCTV Maintenance Checklist Log ReportDocumento5 pagineCCTV Maintenance Checklist Log Reportali ahmedNessuna valutazione finora