Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Manchester Encoding

Caricato da

MANIKANDANCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Manchester Encoding

Caricato da

MANIKANDANCopyright:

Formati disponibili

International Journal of Electrical, Electronics and Data Communication, ISSN (p): 2320-2084,

Volume-1, Issue-2, April-2013

VHDL IMPLEMENTATION OF MANCHESTER ENCODER AND

DECODER

SUCHITRA SURESH

P G Scholar, Musaliar College of Engineering and Technology, Pathanamthitta

Email: suchitraponnu@gmail.com

Abstract: An implementation of Manchester coding is being described in this paper. Manchester coding technique is a

digital coding technique in which all the bits of the binary data are arranged in a particular sequence. The Intersil HD-15530

is a high performance CMOS device intended to service the requirements of MlL-STD-1553 and similar Manchester II

encoded, time division multiplexed serial data protocols. This LSI chip is divided into two sections, an Encoder and a

Decoder. These sections operate completely independent of each other, except for the Master Reset functions. This circuit

meets many of the requirements of MIL-STD- 1553. The Encoder produces the sync pulse and the parity bit as well as the

encoding of the data bits. The Decoder recognizes the sync pulse and identifies it as well as decoding the data bits and

checking parity. This integrated circuit is fully guaranteed to support the 1MHz data rate of MlL-STD-1553 over both

temperature and voltage. It interfaces with CMOS, TTL or N channel support circuitry. The HD-15530 can also be used in

many party line digital data communications applications, such as an environmental control system driven from a single

twisted pair cable of fiber optic cable throughout the building. The functions of the encoder section of the MED include a

microprocessor interface, parallel to serial conversion, frame generation, and NRZ to Manchester encoding. This circuitry

can run very fast since it does not require a high-frequency clock. The frame format used is similar to that of a UART. The

Manchester decoder limits the maximum frequency of operation of the MED, since it uses a high-frequency clock. The

receiver circuitry is more complex, since clock recovery and center sampling is done. Additional receiver functions are

frame detection, decoding of Manchester to NRZ, serial to parallel conversion, and a microprocessor interface.

Keywords: Manchester coding, Encoder, Decoder, NRZ, Moores law, UART, clock frequency

I.

INTRODUCTION

II.

Manchester coding technique is a digital coding

technique in which all the bits of the binary data are

arranged in a particular sequence. Here a bit 1 is

represented by transmitting a high voltage for half

duration of the input signal and for the next halftime

period an inverted signal will be send. When

transmitting 0 in Manchester format, for the first

half cycle a low voltage will send, and for the next

half cycle a high voltage is send. The advantage of

Manchester coding is that, when sending a data

having continuous high signals or continuous low

signal (e.g.: 11110000), it is difficult to calculate the

number of 1 S and Os in the data. Because there is no

transition from low to high or high to low for a

particular time period (Here it is 4 x T, T is the time

duration for a single pulse). The detection is possible

only by calculating the time duration of the signal.

But when we code this signal in Manchester format

there will always be a transition from high to low or

low to high for each bit. Thus for a receiver it is

easier to detect the data in Manchester format and

also the probability for occurrence of an error is very

low in Manchester format and it is a universally

accepted digital encoding technique.

MANCHESTER ENCODER AND

DECODER

Manchester coding technique is a digital coding

technique in which all the bits of the binary data are

arranged in a particular sequence. Here a bit 1 is

represented by transmitting a high voltage for half

duration of the input signal and for the next halftime

period an inverted signal of the original signal (i.e.,

0 ) will send. When transmitting 0 in Manchester

format, for the first half cycle a low voltage will send

, and for the next half cycle a high voltage will send.

The advantage of Manchester coding is that, when

sending a data having continuous high signals or

continuous low signal (e.g.: 11110000), it is difficult

to calculate the number of is and Os in the data.

Because there is no transition from low to high or

high to low for a particular time period (Here it is 4 x

T, T is the time duration for a single pulse). The

detection is possible only by calculating the time

duration of the signal. But when we code this signal

in Manchester format there will always be a transition

from high to low or low to high for each bit. Thus for

a receiver it is easier to detect the data in Manchester

format and also the probability for occurrence of an

error is very low in Manchester format and it is a

universally accepted digital coding technique.

In this paper a Manchester encoding and decoding

operations are achieved by VHDL coding technique.

All the codes are written with reference to HD15530,

Fig 1 Manchester coding format

VHDL Implementation of Manchester Encoder and Decoder

43

International Journal of Electrical, Electronics and Data Communication, ISSN (p): 2320-2084,

Volume-1, Issue-2, April-2013

CMOS Manchester encoder and decoder IC.

HD15530 IC contains a Manchester encoder and

decoder blocks.

III.

HD15530 CMOS MANCHESTER

ENCODER AND DECODER

The Intersil HD- 15530 is a high performance

CMOS device intended to service the requirements

ofMlL-STD-1 553 and similar Manchester II

encoded; time division multiplexed serial data

protocols. This LSI chip is divided into two sections,

an Encoder and a Decoder. These sections operate

completely independent of each other, except for the

Master Reset functions. This circuit meets many of

the requirements of MIL-STD- 1553.

The Encoder produces the sync pulse and the parity

bit as well as the encoding of the data bits. The

Decoder recognizes the sync pulse and identifies it as

well as decoding the data bits and checking parity.

This integrated circuit is fully guaranteed to support

the I MBits data rate ofMlL-STD1553 over both

temperature and voltage. It interfaces with CMOS,

TTL or N channel support circuitry, and uses a

standard 5V supply.

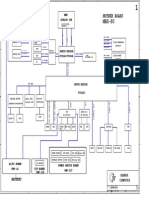

Fig 3 Decoder Block Diagram

IV.

ENCODER OPERATION

The Encoder requires a single clock with a

frequency of twice the desired data rate applied at the

SEND CLOCK input. An auxiliary divide by six

counters is provided on chip which can be utilized to

produce the SEND CLOCK by dividing the

DECODER CLOCK.

The HD-15530 can also be used in many party line

digital data communications applications, such as an

environmental control system driven from a single

twisted pair cable of fiber optic cable throughout the

building.

.

The Encoders cycle begins when ENCODER

ENABLE is high during a falling edge of ENCODER

SHIFT CLOCK. This cycle lasts for one word length

or twenty ENCODER SHIFT CLOCK periods. At the

next low-to-high transition of the ENCODER SHIFT

CLOCK, a high SYNC SELECT input actuates

command sync or a low will produce data sync for

the word. When the Encoder is ready to accept data,

the SEND DATA output will go high and remain

high for sixteen ENCODER SHIFT CLOCK periods.

During these sixteen periods the data should be

clocked into the SERIAL DATA input with every

high-to-low transition of the ENCODER SHIFT

CLOCK so it can be sampled on the low to- high

transition. After the sync and Manchester II coded

data are transmitted through the BIPOLAR ONE and

BIPOLAR ZERO outputs, the Encoder adds on an

additional bit which is the parity for that word.

If ENCODER ENABLE is held high continuously,

consecutive words will be encoded without an

interframe gap. ENCODER ENABLE must go low

by time as shown to prevent a consecutive word from

being encoded.

At any time a low on OUTPUT INHIBIT input

will force both bipolar outputs to a high state but will

not affect the Encoder in any other way. To abort the

Encoder transmission a positive pulse must be

applied at MASTER RESET.

Fig 2 Encoder Block Diagram

VHDL Implementation of Manchester Encoder and Decoder

44

International Journal of Electrical, Electronics and Data Communication, ISSN (p): 2320-2084,

Anytime after or during this pulse, a low-to-high

transition on SEND CLOCK clears the internal

counters and initializes the Encoder for a new word.

Volume-1, Issue-2, April-2013

The decoded data available at SERIAL DATA

OBT is in NRZ. After all sixteen decoded bits have

been transmitted the data is checked for odd parity. A

high on VALID WORD output indicates a successful

reception of a word without any Manchester or parity

errors. At this time the Decoder is looking for a new

sync character to start another output sequence.

VALID WORD will go low approximately 20

DECODER SHIFT CLOCK periods after it goes high

if not reset low sooner by a valid sync and two valid

Manchester bits as shown.

At any time in the above sequence a high input on

DECODER RESET during a low-to- high transition

of DECODER SHIFT CLOCK will abort

transmission and initialize the Decoder to start

looking for a new sync character.

Fig 4 Encoder timing waveform

V.

DECODER OPERATION

The Decoder requires a single clock with a

frequency of 12 times the desired data rate applied at

the DECODER CLOCK input. The Manchester II

coded data can be presented to the Decoder in one of

two ways.

The BIPOLAR ONE and BIPOLAR ZERO inputs

will accept data from a comparator sensed

transformer coupled bus as specified in Military Spec

1553. The UNIPOLAR DATA input can only accept

non-inverted Manchester II coded data. (E.g. from

BIPOLAR ONE OUT of an Encoder through an

inverter to Unipolar Data Input).

The Decoder is free running and continuously

monitors its data input lines for a valid sync character

and two valid Manchester data bits to start an output

cycle. When a valid sync is recognized, the type of

sync is indicated on COMMAND/DATA SYNC

output. If the sync character was command sync, this

output will go high and remain high for sixteen

DECODER SHIFT CLOCK periods, otherwise it will

remain low. The TAKE DATA output will go high

and remain high while the Decoder is transmitting the

decoded data through SERIAL DATA OUT.

Fig 5 Decoder timing waveform

VI.

O V E RV I EW O F

P R O G R AM M I N G AN D

S I M U LA T IO N

This system was realized in VHDL language using

MODEL SIM Software.

VHDL Implementation of Manchester Encoder and Decoder

45

International Journal of Electrical, Electronics and Data Communication, ISSN (p): 2320-2084,

Volume-1, Issue-2, April-2013

A digital system can be represented at different

levels of abstraction. This keeps the description and

design of complex systems manageable.

The highest level of abstraction is the behavioral

level that describes a system in terms of what it does

(or how it behaves) rather than in terms of its

components and interconnection between them.

A behavioral description specifies the relationship

between the input and output signals. The structural

level, on the other hand, describes a system as a

collection of gates and components that are

interconnected to perform a desired function.

A structural description could be compared to a

schematic of interconnected logic gates. It is a

representation that is usually closer to the physical

realization of a system. VHDL allows one to describe

a digital system at the structural or the behavioral

level. The behavioral level can be further divided into

two kinds of styles: Data flow and Algorithmic. The

dataflow representation describes how data moves

through the system. This is typically done in terms of

data flow between registers (Register Transfer level).

The data flow model makes use of concurrent

statements that are executed in parallel as soon as

data arrives at the input. On the other hand, sequential

statements are executed in the sequence that they are

specified. VHDL allows both concurrent and

sequential signal assignments that will determine the

manner in which they are executed.

VHDL uses reserved keywords that cannot be used

as signal names or identifiers. Keywords and userdefined identifiers are case insensitive. Lines with

comments start with two adjacent hyphens (--) and

will be ignored by the compiler. VHDL also ignores

line breaks and extra spaces.

VHDL is a strongly typed language which implies

that one has always to declare the type of every object

that can have a value, such as signals, constants and

variables.

Once an entity is modelled it needs to be validated

by a VHDL system. Once the sample circuit is

completed design is to be simulated to verify that it

actually does what it is intended to do. Test benches

apply some sequence of inputs to the circuit being

tested (the unit under test, or UUT) so that its

operation can be observed in simulation.

A test bench must consist of a component

declaration corresponding to the UUT, and a

description of input stimulus being applied to the

UUT. Thus the test bench can be defined as virtual

environment which is used to verify the correctness

or soundness of the hardware model.

ModelSim is a verification and simulation tool for

VHDL, Verilog, System Verilog, and mixed language

designs. Mentor Graphics was the first to combine

single kernel simulator (SKS) technology with a

unified debug environment for Verilog, VHDL, and

System C.

Fig 6 Digital System as VHDL entity

VHDL is an acronym for VHSIC Hardware

Description Language (VHSIC is an acronym for

Very High Speed Integrated Circuits). It is a

hardware description language that can be used to

model a digital system. The other widely used

hardware description language is Verilog. Both are

powerful languages that allow you to describe and

simulate complex digital systems. A third HDL

language is ABEL (Advanced Boolean Equation

Language) which was specifically designed for

Programmable Logic Devices (PLD). ABEL is less

powerful than the other two languages and is less

popular in industry. Although these languages look

similar as conventional programming languages,

there are some important differences. A hardware

description language is inherently parallel, i.e.

commands, which correspond to logic gates, are

executed (computed) in parallel, as soon as a new

input arrives.

A HDL program mimics the behavior of a

physical, usually digital, system. It also allows

incorporation of timing specifications (gate delays) as

well as to describe a system as an interconnection of

different components. A hardware description of this

digital system is called an entity. An entity X when

used in another entity becomes a component for the

entity Y. Therefore a component is also an entity,

depending on the level at which we are trying to

model.

VHDL Implementation of Manchester Encoder and Decoder

46

International Journal of Electrical, Electronics and Data Communication, ISSN (p): 2320-2084,

Volume-1, Issue-2, April-2013

The combination of industry-leading, native SKS

performance with the best integrated debug and

analysis environment make ModelSim the simulator

of choice for both ASIC and FPGA design. The best

standards and platform support in the industry make it

easy to adopt in the majority of process and tool

flows.

The design was thoroughly simulated to test all the

instructions in VHDL simulator software. As the

coding system has high accuracy, the system gives

more accuracy and efficiency in data sending. This

coding system is a universally accepted digital coding

system. Also it provides more security for data

transmission.

In ModelSim, all designs are compiled into a

library. You typically start a new simulation in

ModelSim by creating a working library called

"work". "Work" is the library name used by the

compiler as the default destination for compiled

design units. After creating the working library, you

compile your design units into it.

REFERENCES

[1]

[2]

The ModelSim library format is compatible across

all supported platforms. You can simulate your

design on any platform without having to recompile

your design. With the design compiled, you load the

simulator with your design by invoking the simulator

on a top-level module (Verilog) or a configuration or

entity/architecture pair (VHDL).

[3]

[4]

Assuming the design loads successfully, the

simulation time is set to zero, and you enter a run

command to begin simulation. If you dont get the

results you expect, you can use ModelSims robust

debugging environment to track down the cause of

the problem.

[5]

[6]

The Wave window allows you to view the results

of your simulation as HDL waveforms and their

values. The Wave window is divided into a number

of window panes. All window panes in the Wave

window can be resized by clicking and dragging the

bar between any two panes.

[7]

[8]

If you close the Wave window, any configurations

you made to the window (e.g., signals added, cursors

set, etc.) are discarded. However, you can use Save

Format command to capture the current Wave

window display and signal preferences to a DO file.

You open the DO file later to recreate the Wave

window as it appeared when the file was created.

[9]

[10]

[11]

[12]

[13]

C O N CL U S IO N

Shi Jingzhuo; Xu Yingxi; Shi Jing, Manchester

encoder and decoder based on CPLD, IEEE International

Conference on Industrial Technology, 2008(ICIT 2008),

Page(s): 1 - 3, 2008.

Yu-Cherng Hung; Min-Ming Kuo; Chiou-Kou Tung; ShaoHui Shieh, High-Speed CMOS

Chip Design

for Manchester and Miller Encoder , Fifth International

Conference on Intelligent Information Hiding and

Multimedia Signal Processing, 2009(IIH-MSP '09)

Digital

Object

Identifier: 10.1109/IIH-MSP.2009.62 ,

Page(s): 538 541, 2009.

Al-Sammak,

A.J.,

Encoder circuit

for

inverse

differential Manchester

code

operating

at

any

frequency, Electronics Letters , Vol 38 , Issue: 12,

Page(s): 567 568, 2002

Jifeng Li; Minggang Chai, Design of 1553B avionics bus

interface chip based on FPGA, Proceedings 2011

International Conference on Electronics, Communications

and Control (ICECC), Page(s): 3642 3645, 2011.

Markarian, G.; Honary, B.; King, D.; Kissaka, M.,

Integrated circuit design and implementation for a new

optimum Manchester decoder, IEEE

Global

Telecommunications

Conference

(GLOBECOM

'95), Volume: 2, 1995.

Sauter, T.; Kero, N., Majority Manchester decoding for

active redundant data transmission, Proceedings IEEE

Symposium

on Computers

and

Communications,

Page(s): 78 82, 1995.

El-Medany,

W.M.,

FPGA

implementation

of

RDR Manchester and D-Manchester CODEC design for

Wireless Transceiver ,Radio Science Conference (NRSC

2008)Page(s):1-5, 2008.

Jimenez, J.; Martin, J.L.; Astarloa, A.; Zuloaga, A.,

Manchester decoding algorithm for multifunction vehicle

bus , 2004 IEEE International Conference on Industrial

Technology (IEEE ICIT '04), Volume. 2, Page(s): 769

774, 2004.

Technical papers from VSSC Library

www.aldec.com

www.ashenden.com.au

Xilinx, Manchester Encoder-Decoder for Xilinx CPLDs

XAPP339

(v1.3)

2002.

[Online].

Available:

http://www.xilinx.com/support/documentation/application_

notes/xapp339.pdf

http://www.ee.iitm.ac.in/~balajis/EE5000/MC_TDM.pdf

The paper VHDL Implementation of Advanced

Manchester Encoder and Decoder presented here

gives an easy and less expensive way to implement

Manchester coding system. First the different

components that constitute the coder have been

designed with required inputs, outputs & control

signals. The interface between the designed

components has been formulated. This was then

realized in VHDL language using MODEL SIM

Software.

VHDL Implementation of Manchester Encoder and Decoder

47

Potrebbero piacerti anche

- Decoder Hoping CodeDocumento18 pagineDecoder Hoping CodeEletrotec ErasmoNessuna valutazione finora

- Esab Caddy Tig-2200i Ac-Dc 718-xxx To 843-xxxDocumento64 pagineEsab Caddy Tig-2200i Ac-Dc 718-xxx To 843-xxxhitano12100% (1)

- Advantages and Disadvantages of DBMSDocumento7 pagineAdvantages and Disadvantages of DBMSBavani Marimuthu50% (2)

- Microcontroller Basics and ProgrammingDocumento92 pagineMicrocontroller Basics and ProgrammingVishal Gudla NagrajNessuna valutazione finora

- ManualDocumento53 pagineManualShrey Grover100% (1)

- Z3 2 4Documento104 pagineZ3 2 4Vu Duc Hoan100% (1)

- VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique For Wireless Sensor NetworkDocumento7 pagineVLSI Architecture of FM0/Manchester Encoding Using SOLS Technique For Wireless Sensor NetworkDon RajuNessuna valutazione finora

- Features Description: CMOS Manchester Encoder-DecoderDocumento14 pagineFeatures Description: CMOS Manchester Encoder-DecoderKaty KimberlynNessuna valutazione finora

- I S Bus Specification: 1.0 2.0 Basic Serial Bus RequirementsDocumento7 pagineI S Bus Specification: 1.0 2.0 Basic Serial Bus RequirementseballiriNessuna valutazione finora

- Manchester Data Encoding For Radio CommunicationsDocumento5 pagineManchester Data Encoding For Radio Communicationsjmarcos.whoscallNessuna valutazione finora

- Manchester Encoding Using RS232Documento4 pagineManchester Encoding Using RS232Izhar Rosli100% (1)

- 1.4 KNR2103 - Week 9 - Day 1 - PDF PDFDocumento21 pagine1.4 KNR2103 - Week 9 - Day 1 - PDF PDFسلمان اوڠNessuna valutazione finora

- 1.4 KNR2103 - Week 9 - Day 1 - PDF PDFDocumento21 pagine1.4 KNR2103 - Week 9 - Day 1 - PDF PDFسلمان اوڠNessuna valutazione finora

- High-Speed CMOS Chip Design For Manchester and Miller EncoderDocumento7 pagineHigh-Speed CMOS Chip Design For Manchester and Miller EncoderAishwarya a nairNessuna valutazione finora

- Interactive Voice Response SystemDocumento17 pagineInteractive Voice Response SystemSowjanya ModalavalasaNessuna valutazione finora

- 21EC10028 Exp 01Documento8 pagine21EC10028 Exp 01Tejaswini ANessuna valutazione finora

- Build A Program Remote Control IR Transmitter Using HT6221Documento4 pagineBuild A Program Remote Control IR Transmitter Using HT6221malhiavtarsinghNessuna valutazione finora

- Build A Program Remote Control IR Transmitter Using HT6221Documento2 pagineBuild A Program Remote Control IR Transmitter Using HT6221rudraNessuna valutazione finora

- Surya - First PhasereportDocumento10 pagineSurya - First PhasereportSuribabuIppiliNessuna valutazione finora

- Research Inventy: International Journal of Engineering and ScienceDocumento7 pagineResearch Inventy: International Journal of Engineering and ScienceresearchinventyNessuna valutazione finora

- Manchester Encoding Using RS232Documento7 pagineManchester Encoding Using RS232cleiserpirapora2422Nessuna valutazione finora

- Humidity and Temperature: About DHT11 SensorDocumento4 pagineHumidity and Temperature: About DHT11 SensorminiecateNessuna valutazione finora

- LGEC002 Door Lock System Using RFDocumento8 pagineLGEC002 Door Lock System Using RFShivani MehrotraNessuna valutazione finora

- EE 3206, Exp 05Documento5 pagineEE 3206, Exp 05Tahsin Zaman TalhaNessuna valutazione finora

- Assignment No:: Subject: Name: Rollno.Documento25 pagineAssignment No:: Subject: Name: Rollno.Sharad Patil DholeNessuna valutazione finora

- EnDat 2.2Documento20 pagineEnDat 2.2Tushar Kanti BiswasNessuna valutazione finora

- Wireless Equipment Timeout ControlDocumento5 pagineWireless Equipment Timeout ControlAnand BhaskarNessuna valutazione finora

- Circuit Diagram Wireless TransmitterDocumento17 pagineCircuit Diagram Wireless Transmitterumaiya1990100% (2)

- RS-232 (Serial Communication) and MAX-232Documento35 pagineRS-232 (Serial Communication) and MAX-232Azam Rafique100% (2)

- Introduction To Spread Spectrum CommunicationsDocumento20 pagineIntroduction To Spread Spectrum CommunicationsSriramNessuna valutazione finora

- Low Power & Area Efficient Layout Analysis of Cmos EncoderDocumento5 pagineLow Power & Area Efficient Layout Analysis of Cmos EncoderSamiksha GautamNessuna valutazione finora

- Data and Computer Communications: Chapter 5 - Signal Encoding TechniquesDocumento49 pagineData and Computer Communications: Chapter 5 - Signal Encoding TechniquesSaurav SenNessuna valutazione finora

- Delta Modulation For Voice Transmission: Application Note January 1997 AN607.1Documento6 pagineDelta Modulation For Voice Transmission: Application Note January 1997 AN607.1Mac AnciadoNessuna valutazione finora

- Encoder and Decoder: A Project By:Priyanka Basak 3Rd Year, 6th Sem Roll:32Documento13 pagineEncoder and Decoder: A Project By:Priyanka Basak 3Rd Year, 6th Sem Roll:32Indranil GangulyNessuna valutazione finora

- Remote Controlled Digital Audio Processor - Full Project AvailableDocumento3 pagineRemote Controlled Digital Audio Processor - Full Project AvailableK Raja SekarNessuna valutazione finora

- Project Final Report IIDocumento50 pagineProject Final Report IIRemigild PeterNessuna valutazione finora

- Time Synchronizing Signal by GPS SatellitesDocumento10 pagineTime Synchronizing Signal by GPS SatellitesAisha Sultan ZNessuna valutazione finora

- Polar Biphase Line EncodingDocumento12 paginePolar Biphase Line EncodingGerald KapinguraNessuna valutazione finora

- Paper On AC LoadDocumento4 paginePaper On AC LoadDidarul AlamNessuna valutazione finora

- Rfid Interface TO 8051: Deepak GuptaDocumento4 pagineRfid Interface TO 8051: Deepak Guptamohitdaya14Nessuna valutazione finora

- DHTDocumento9 pagineDHTNoman Jabbar100% (2)

- IR Sensor Based Distance Measurement SystemDocumento5 pagineIR Sensor Based Distance Measurement SystemRajkeen ChamanshaikhNessuna valutazione finora

- 8251 Material PDFDocumento31 pagine8251 Material PDFskarthikpriyaNessuna valutazione finora

- RF Id Attendence MemoryDocumento128 pagineRF Id Attendence Memoryakhilesh thapliyalNessuna valutazione finora

- Combinational CircuitsDocumento5 pagineCombinational CircuitsRafena17Nessuna valutazione finora

- HCTL 2017Documento12 pagineHCTL 2017ivancho1070Nessuna valutazione finora

- ECR MachineDocumento37 pagineECR Machineapi-3721578100% (1)

- RF and GSM Based Wireless Power Theft MonitoringDocumento27 pagineRF and GSM Based Wireless Power Theft MonitoringDebashishParida50% (2)

- WarField Land Rover That Alerts On Sensing Panted Land MinesDocumento32 pagineWarField Land Rover That Alerts On Sensing Panted Land MinesPavan KPNessuna valutazione finora

- Agenda: Introduction To Telecom Network Introduction To Digital SPC SwitchDocumento73 pagineAgenda: Introduction To Telecom Network Introduction To Digital SPC Switcha_krivushaNessuna valutazione finora

- Convolution EncoderDocumento7 pagineConvolution EncoderJeevith PaulNessuna valutazione finora

- Combinational Circuits: 4 To 2 EncoderDocumento5 pagineCombinational Circuits: 4 To 2 EncoderRafena MustaphaNessuna valutazione finora

- Code Division Multiple AccessDocumento8 pagineCode Division Multiple AccessDwarak ChaluvadiNessuna valutazione finora

- Heart Beat MoniteringDocumento5 pagineHeart Beat MoniteringmadhavMIETNessuna valutazione finora

- DS1603Documento8 pagineDS1603jnax101Nessuna valutazione finora

- Topic 1.basic Data CommDocumento42 pagineTopic 1.basic Data CommAIMAN DANIAL BIN SULONGNessuna valutazione finora

- EPMA-Hyperion 11.2.8 New FeaturesDocumento5 pagineEPMA-Hyperion 11.2.8 New FeaturesNawab ShariefNessuna valutazione finora

- Laboratory 2 BEEDocumento11 pagineLaboratory 2 BEE22-03844Nessuna valutazione finora

- Bachelor Thesis: Oslo and Akershus University College of Applied SciencesDocumento155 pagineBachelor Thesis: Oslo and Akershus University College of Applied SciencesexcalidorNessuna valutazione finora

- Notes For ICT IGCSE Chapter 1 - 3Documento15 pagineNotes For ICT IGCSE Chapter 1 - 3Gentle FeatherNessuna valutazione finora

- What Are Batch Processing System and Real Time Processing System and The Difference Between ThemDocumento6 pagineWhat Are Batch Processing System and Real Time Processing System and The Difference Between ThemfikaduNessuna valutazione finora

- Network Design (Rancid)Documento11 pagineNetwork Design (Rancid)pianksatriacementoNessuna valutazione finora

- Sai Vidya Institute of Technology: Course: 15ec663 - Digital System Design Using VerilogDocumento27 pagineSai Vidya Institute of Technology: Course: 15ec663 - Digital System Design Using VerilogShivaprasad B KNessuna valutazione finora

- Easy Data Exchange Via Festo Easyip: Festo Ag & Co - KGDocumento11 pagineEasy Data Exchange Via Festo Easyip: Festo Ag & Co - KGFFlipooxNessuna valutazione finora

- 2SJ162Documento7 pagine2SJ162Bryan WahyuNessuna valutazione finora

- Integration InterfacesDocumento170 pagineIntegration Interfacesjlopez_303Nessuna valutazione finora

- Sony-Ne5-Mb-3e Sony SCHEMATICDocumento31 pagineSony-Ne5-Mb-3e Sony SCHEMATICvideosonNessuna valutazione finora

- Wanguard Console (HugeCloud - Console)Documento1 paginaWanguard Console (HugeCloud - Console)Paulo Maciel de SouzaNessuna valutazione finora

- Thesis SheetsDocumento12 pagineThesis Sheetselsa n. calvezNessuna valutazione finora

- DTHUB API Automation CourseDocumento13 pagineDTHUB API Automation CourseHarry HarryNessuna valutazione finora

- Power Electronics Spring 2023 19022023 110358pmDocumento3 paginePower Electronics Spring 2023 19022023 110358pmAHSAN HAMEEDNessuna valutazione finora

- Main NicoleArambuloDocumento1 paginaMain NicoleArambuloChristianettm86Nessuna valutazione finora

- Cap-Max-System-Server Ds Ap 0516 PDFDocumento2 pagineCap-Max-System-Server Ds Ap 0516 PDFBao Quoc MaiNessuna valutazione finora

- 29F64G08CBAAA Micron PDFDocumento159 pagine29F64G08CBAAA Micron PDFMarcelo TrassiNessuna valutazione finora

- Sct4 System Tailoring Vol.1Documento630 pagineSct4 System Tailoring Vol.1Rajiv Kumar TiwaryNessuna valutazione finora

- DSP and Multicore ProcessorsDocumento12 pagineDSP and Multicore Processorsvvsulakhe6337Nessuna valutazione finora

- PM6750 Patient Monitor Module Manual PDFDocumento8 paginePM6750 Patient Monitor Module Manual PDFJuan DuasoNessuna valutazione finora

- Artemis TrainingDocumento5 pagineArtemis TrainingAgellos KoursarisNessuna valutazione finora

- DSAH00464830Documento23 pagineDSAH00464830asousa534Nessuna valutazione finora

- Module 4: Physical Layer: Introduction To Networks v7.0 (ITN)Documento42 pagineModule 4: Physical Layer: Introduction To Networks v7.0 (ITN)Nguyễn Thị Thùy LinhNessuna valutazione finora

- ID-DPDP Scheme For Storing Authorized Distributed Data in CloudDocumento36 pagineID-DPDP Scheme For Storing Authorized Distributed Data in Cloudmailtoogiri_99636507Nessuna valutazione finora

- CATV Products BrochureDocumento56 pagineCATV Products BrochurePhilip SaundersNessuna valutazione finora

- Module-Week 5Documento2 pagineModule-Week 5Maria Christina ManzanoNessuna valutazione finora

- Subject: Java Programming Track: TVL/ICT/Computer Programming Grade: 11Documento4 pagineSubject: Java Programming Track: TVL/ICT/Computer Programming Grade: 11Rodito Jr VillanuevaNessuna valutazione finora