Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

ELE290 CIRCUIT ANALYSIS

Caricato da

Zyne Mohd JohariDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

ELE290 CIRCUIT ANALYSIS

Caricato da

Zyne Mohd JohariCopyright:

Formati disponibili

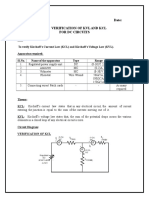

BASIC ELECTRICAL ENGINEERING

ELE290

1.0 CIRCUIT ANALYSIS

This topic will cover two methods of circuit analysis which are:a) Kirchoffs Current Law (KCL)

b) Kirchoffs Voltage law (KVL)

1.0.1) Kirchoffs Current Law (KCL)

Kirchoffs current law states that the algebraic sum of the current at a node/junction in a

network at any instant of time is zero. KCL may be expressed mathematically as:n

i

j 1

Where ij represents current in the jth element and n is the number of elements connected to

the node k. This means that the algebraic sum of the currents meeting at a junction is zero. If

the current s entering the node are taken as positive, the currents leaving the node are

negatives, or vice versa. The KCL maybe thought of to be a consequence of the conservation

of electric charge- charge cannot be created nor destroyed but must be conserved.

i1

i2

i5

i3

i4

Figure 1 Application of KCL

KCL equation for Fig. 1 above can be expressed as:-

i1 i2 i3 i4 i5 0

By rearranging the equation, the equation for node k can be rewritten as:-

i3 i4 i1 i2 i5

With KCL, it is obvious that elements in series carry the same current value.

i1 i 2

I1

I2

I3

i 2 i3

BASIC ELECTRICAL ENGINEERING

ELE290

1.0.2) Kirchoffs Voltage Law (KVL)

Kirchoffs voltage law states that at any instant of time the sum of voltages in a closed circuit

equals to zero. KVL may be expressed mathematically as:n

v

j 1

Where vj represents the individual voltage in the jth element around the closed circuit having

n elements.

If the voltage drop from the positive polarity to the negative polarity is assigned as positive

sign, then the voltage rise from the negative polarity to the positive polarity is assumed as

negative, or vice-versa.

KVL is a consequences of the fact that no energy is lost or created in an electric circuit. It is

our choice whether to apply KVL clock-wise or anti clock-wise. As we go round the loop, it is

also our choice to add the voltage drops ( and subtract voltage rise) or add the voltage rise

(and subtracts voltage drop). Both methods are correct.

However, usually going clock-wise is chosen and voltage drop in elements is set as negative

values; meaning that any voltage drop in the closed circuit is subtracted.

+V1-

10 V

+V2-

KVL direction 5 V

-V3+

Figure 2 Application of KVL

By applying KVL onto the closed loop in Fig. 2, the equation below is obtained:-

10V V1 V2 5V V3 0

By rearranging the equation, the equation for the closed circuit can be rewritten as:-

5V V1 V2 V3

With KVL, it is obvious that elements in parallel connection have the same voltage drop

across them.

BASIC ELECTRICAL ENGINEERING

ELE290

+

V1

-

+

V2

-

+

V3

-

V1 V2

V 2 V3

1.1) Series and Parallel connection:1.1.1) Series Connection

For impedances that is connected in series, addition of the impedances can be calculated

by adding each of the impedance.

R1

R2

R3

RTOTAL R1 R2 R3

1.1.2) Parallel Connection

For impedances that is connected in parallel, addition of the impedances must be

calculated by using parallel concept from right to left part of the circuit. Normal addition

cannot be used.

R1

1

RTOTAL

1

RTOTAL

RTOTAL

R2

1

1

R1 R2

R1 R2

R1 R2

RR

1 2

R1 R2

BASIC ELECTRICAL ENGINEERING

ELE290

1.2) Current Divider Rule

When a current has to be divided among various resistors connected in parallel, the current is

divided by using the current divider rule:-

IT

I1

R1

I2

R2

I T I1 I 2

I1

R2

IT

R1 R2

I2

R1

IT

R1 R2

1.3) Voltage Divider Rule

When a voltage has to be divided among various resistors connected in series, the voltage is

divided by using the voltage divider rule:-

+ V1R1

+

V

-

R2

V V1 V2

V1

R1

V

R1 R2

V2

R2

V

R1 R2

+

V2

-

BASIC ELECTRICAL ENGINEERING

ELE290

Tutorials

1. Determine the following values

I2

10

10V

10

+ VR1 I1

a.

I1

10V

3

5

1

+

VR1

-

b.

20

15

I1

20V

24

I2

100

c.

2.2k

10k

5V

d.

+

I1 VR1

-

50k

I2

4.7k

12k

1k

+

VR1

-

Potrebbero piacerti anche

- 1.0 Circuit Analysis: Basic Electrical Engineering ELE290Documento5 pagine1.0 Circuit Analysis: Basic Electrical Engineering ELE290MohdFirdausNessuna valutazione finora

- World University of Bangladesh Department of Electrical & Electronic Engineering (EEE)Documento5 pagineWorld University of Bangladesh Department of Electrical & Electronic Engineering (EEE)NickNessuna valutazione finora

- M.M. Engineering College - Mullana: Laboratory Manual Practical Experiment Instruction SheetDocumento3 pagineM.M. Engineering College - Mullana: Laboratory Manual Practical Experiment Instruction Sheetvj4249Nessuna valutazione finora

- Electronics Study Material For MSCDocumento23 pagineElectronics Study Material For MSCiswaleha100% (1)

- 18Ees101J-Basic Electrical & Electronics Engineering: Unit 1Documento57 pagine18Ees101J-Basic Electrical & Electronics Engineering: Unit 1Mohammed JavidhNessuna valutazione finora

- Verification of KVL and KCLDocumento3 pagineVerification of KVL and KCLVarun Vadluri80% (5)

- Ec2155 Lab ManualDocumento32 pagineEc2155 Lab ManualSuresh Ponnusamy50% (2)

- Devre Teori̇si̇ I Hafta 2Documento28 pagineDevre Teori̇si̇ I Hafta 2halilibrahimmutlu4268Nessuna valutazione finora

- Eee 03Documento6 pagineEee 03Sayeed MohammedNessuna valutazione finora

- Bee Lab ManualDocumento40 pagineBee Lab ManualDk gamingNessuna valutazione finora

- Verify KVL KCL DC CircuitsDocumento3 pagineVerify KVL KCL DC Circuitssakshi rainaNessuna valutazione finora

- KVL, KCL, Thevenin's Theorem and Norton's TheoremDocumento9 pagineKVL, KCL, Thevenin's Theorem and Norton's TheoremHenok BelaynehNessuna valutazione finora

- Verifying KVL and KCL Circuit Laws (39Documento8 pagineVerifying KVL and KCL Circuit Laws (39TOP 5 GHOSTNessuna valutazione finora

- DC Lab - Exp - 2Documento6 pagineDC Lab - Exp - 2THE LEARNER GAMINGNessuna valutazione finora

- Beee Practical 2 Unit 1Documento4 pagineBeee Practical 2 Unit 1Shivam HansNessuna valutazione finora

- Ee 211Documento37 pagineEe 211Muhammad OsamaNessuna valutazione finora

- Module 3Documento5 pagineModule 3Christine MalibiranNessuna valutazione finora

- Lec - Kirchoff LawsDocumento32 pagineLec - Kirchoff Lawszaheerduaa27Nessuna valutazione finora

- EEE Experiment 1Documento8 pagineEEE Experiment 1SavioNessuna valutazione finora

- Verification of Kirchhoff's Voltage Law (KVL) .: EXPT. No. 02Documento3 pagineVerification of Kirchhoff's Voltage Law (KVL) .: EXPT. No. 02Butterfly mahfuzNessuna valutazione finora

- DC Lab Exp 2 Student Manual (Fall 22-23)Documento6 pagineDC Lab Exp 2 Student Manual (Fall 22-23)Ratul kumarNessuna valutazione finora

- Me 005Documento25 pagineMe 005Pratheesh S KumarNessuna valutazione finora

- Expt. No. 2Documento5 pagineExpt. No. 2shindevedant60Nessuna valutazione finora

- Verification of KCL and KVLDocumento3 pagineVerification of KCL and KVLCOLD FIRENessuna valutazione finora

- BH Khan Introduction To Sustainable EnergyDocumento40 pagineBH Khan Introduction To Sustainable EnergyTushar GuptaNessuna valutazione finora

- Chap2 Beta1313 Part IDocumento85 pagineChap2 Beta1313 Part ISimson DianNessuna valutazione finora

- Advantage of Kirchhoff Law in Electrical CircuitDocumento4 pagineAdvantage of Kirchhoff Law in Electrical Circuitsubha ambepitiyaNessuna valutazione finora

- GNITS Basic Electrical Engineering Lab ManualDocumento62 pagineGNITS Basic Electrical Engineering Lab Manualkuthurupandu5363Nessuna valutazione finora

- 01-4B Basic Circuit IllustDocumento5 pagine01-4B Basic Circuit Illustsbec54Nessuna valutazione finora

- (EE-111) Lab File For 2nd Semester: Institute of Engineering and TechonologyDocumento22 pagine(EE-111) Lab File For 2nd Semester: Institute of Engineering and TechonologyDEVIL WISHER YTNessuna valutazione finora

- EXP 2 KCL and KVLDocumento3 pagineEXP 2 KCL and KVLbattlestrokerNessuna valutazione finora

- DC-Lab Report 02Documento10 pagineDC-Lab Report 02Shahriar Ahsan JohaNessuna valutazione finora

- Files 2-Chapters Chapter 6 Electrical and Electromechanical Systems 2Documento19 pagineFiles 2-Chapters Chapter 6 Electrical and Electromechanical Systems 2Naveen KrishnaNessuna valutazione finora

- Lecture-02 KCL-KVL - Series Parallel Circuits - Nodes - Loops - BranchesDocumento26 pagineLecture-02 KCL-KVL - Series Parallel Circuits - Nodes - Loops - BranchesMohsin RazaNessuna valutazione finora

- Bee Lab ManualDocumento43 pagineBee Lab ManualShivansh SahuNessuna valutazione finora

- Pee Lab ManualDocumento77 paginePee Lab ManualRajendraTuraka100% (1)

- Beee 1.2Documento3 pagineBeee 1.2Rahul surya BobbiliNessuna valutazione finora

- Verify Kirchhoff's Laws Using DC CircuitsDocumento30 pagineVerify Kirchhoff's Laws Using DC CircuitsJigar SoniNessuna valutazione finora

- Title:-: Name: Muhammad Faheem Zia Reg No. # UW-19-ME-BSC-053Documento3 pagineTitle:-: Name: Muhammad Faheem Zia Reg No. # UW-19-ME-BSC-053muhammad faheem ziaNessuna valutazione finora

- DC Circuit Analysis FundamentalsDocumento16 pagineDC Circuit Analysis Fundamentalsyacob sozoNessuna valutazione finora

- Current DivisionDocumento62 pagineCurrent DivisioneyobNessuna valutazione finora

- FEE Lec 1Documento25 pagineFEE Lec 1SanthoshNessuna valutazione finora

- Pertemuan 3 - Hukum KirchoffDocumento15 paginePertemuan 3 - Hukum KirchoffDede KurniawanNessuna valutazione finora

- Pertemuan 3 - Hukum KirchoffDocumento15 paginePertemuan 3 - Hukum KirchoffDede KurniawanNessuna valutazione finora

- Mesh AnalysisDocumento61 pagineMesh AnalysisKasani Tirumala tejaNessuna valutazione finora

- Kirchoff's LawDocumento13 pagineKirchoff's LawAditya Pratap Singh Sengar50% (4)

- Module 3 Kirchhoff's Laws and Wye - Delta TransformationsDocumento33 pagineModule 3 Kirchhoff's Laws and Wye - Delta Transformationssuga lin0% (1)

- Circuit Variables: Potential V Elevation HDocumento12 pagineCircuit Variables: Potential V Elevation HIshank Singh ThandiNessuna valutazione finora

- Discuss Test 1 - Review: - Kirchoff's Rules For Circuits - Resistors in Series & ParallelDocumento33 pagineDiscuss Test 1 - Review: - Kirchoff's Rules For Circuits - Resistors in Series & ParallelSandeep KumarNessuna valutazione finora

- Fund - Circuit Chap TwoDocumento29 pagineFund - Circuit Chap TwoERMIAS AmanuelNessuna valutazione finora

- Practical TemplateDocumento8 paginePractical TemplatezwavhudiNessuna valutazione finora

- EEE207Electrics and Electronics-Chapter 2Documento21 pagineEEE207Electrics and Electronics-Chapter 2tyoudalpenaNessuna valutazione finora

- Kirchhoff's LawsDocumento3 pagineKirchhoff's Lawsabhioptimus00Nessuna valutazione finora

- DC Lab - Exp - 2 - Student - Manual (Spring 22-23)Documento5 pagineDC Lab - Exp - 2 - Student - Manual (Spring 22-23)Bahesty Monfared AkashNessuna valutazione finora

- Design of Igbt Based LLC Resonant InverterDocumento7 pagineDesign of Igbt Based LLC Resonant InverterdhruvNessuna valutazione finora

- CH1 - Circuit Variables PDFDocumento25 pagineCH1 - Circuit Variables PDFahmed ahmedNessuna valutazione finora

- EEEDocumento15 pagineEEEMITALI DUBEY 22BCE10350Nessuna valutazione finora

- Cdlab Manual 2023-2024Documento71 pagineCdlab Manual 2023-2024sivabavatharniiNessuna valutazione finora

- 1 Circuit Theory - MZMDocumento47 pagine1 Circuit Theory - MZMSyahmi AkmalNessuna valutazione finora

- EE 251: Basic Electrical Engineering: Spring 2021 - Section: DA Week 8Documento52 pagineEE 251: Basic Electrical Engineering: Spring 2021 - Section: DA Week 8Omar AbubakerNessuna valutazione finora

- Probsolall PDFDocumento51 pagineProbsolall PDFnicole deleonNessuna valutazione finora

- Lecture 8 - Kirchhoffs Voltage Law and Mesh AnalysisDocumento8 pagineLecture 8 - Kirchhoffs Voltage Law and Mesh AnalysisTushar SharmaNessuna valutazione finora

- Limitations of Ohm's Law, KCL & KVLDocumento2 pagineLimitations of Ohm's Law, KCL & KVLAhsan Sial AhsanNessuna valutazione finora

- Elements of Electrical Engineering EEB 1113 (3 Credits) : EEE Department Manipal International University, NilaiDocumento37 pagineElements of Electrical Engineering EEB 1113 (3 Credits) : EEE Department Manipal International University, NilaiSanjith KaurNessuna valutazione finora

- EEE3100 Lab 3 PDFDocumento4 pagineEEE3100 Lab 3 PDFPutri SaidatinaNessuna valutazione finora

- 1.3 Kirchhoff's Laws: Learning OutcomesDocumento19 pagine1.3 Kirchhoff's Laws: Learning OutcomesAzri Nova100% (1)

- Unit1 KCV PDFDocumento110 pagineUnit1 KCV PDFsanjanaNessuna valutazione finora

- EME 207 Electrical Circuits Loop CurrentsDocumento17 pagineEME 207 Electrical Circuits Loop Currentsمحمد الحديNessuna valutazione finora

- Ultimate Electronics: Practical Circuit Design and Analysis: Table of ContentsDocumento3 pagineUltimate Electronics: Practical Circuit Design and Analysis: Table of ContentsPaulAlmond CitoCamba RegalaNessuna valutazione finora

- Linear Circuit ThoeryDocumento41 pagineLinear Circuit Thoeryanon_848374899Nessuna valutazione finora

- Parallel Circuit PDFDocumento32 pagineParallel Circuit PDFSarsalejo MarsthinieNessuna valutazione finora

- Circuits: Asst. Prof. Dr. Gülnihal MuratoğluDocumento24 pagineCircuits: Asst. Prof. Dr. Gülnihal MuratoğluKarim SharafNessuna valutazione finora

- Chapter2 L4&5 TL PerformanceDocumento22 pagineChapter2 L4&5 TL Performancecharleskinyua222Nessuna valutazione finora

- A Report Submitted To The Department of Electrical and Computer Engineering, College of Engineering University of DuhokDocumento18 pagineA Report Submitted To The Department of Electrical and Computer Engineering, College of Engineering University of DuhokBryar HusenNessuna valutazione finora

- Shroff S.R. Rotary Institute of Chemical TechnologyDocumento10 pagineShroff S.R. Rotary Institute of Chemical TechnologyUTSAV PANKAJ PATELNessuna valutazione finora

- DC Circuit Analysis: Ohm's Law and Kirchhoff's LawsDocumento9 pagineDC Circuit Analysis: Ohm's Law and Kirchhoff's LawsKandi PrintNessuna valutazione finora

- Udayagiri, SPSR Nellore Dist. (A.P) - 524 226: Title of The Subject: Comprehensive Viva-Voce-IIIDocumento12 pagineUdayagiri, SPSR Nellore Dist. (A.P) - 524 226: Title of The Subject: Comprehensive Viva-Voce-IIIsiddam maheshNessuna valutazione finora

- ELEN 20044 IM Fundamentals of Electrical Circuits EditedDocumento78 pagineELEN 20044 IM Fundamentals of Electrical Circuits EditedChelsiemea VargasNessuna valutazione finora

- LabReport Total PDFDocumento42 pagineLabReport Total PDFKhông Có TênNessuna valutazione finora

- Alternating Current Circuits and Electromagnetic Waves ExplainedDocumento32 pagineAlternating Current Circuits and Electromagnetic Waves ExplainedKristineNessuna valutazione finora

- Current Electricity Target Publications Jee Main Physics IIDocumento40 pagineCurrent Electricity Target Publications Jee Main Physics IIsanits591100% (3)

- Basic Feedback Control in Bio Medicine 2009Documento222 pagineBasic Feedback Control in Bio Medicine 2009j2ch5en100% (1)

- Eca 3Documento35 pagineEca 3Ahmed SohailNessuna valutazione finora

- ch2 Raymond Winton Intermediate CircuitsDocumento34 paginech2 Raymond Winton Intermediate CircuitsTyler AnthonyNessuna valutazione finora

- Applications of First Order Differential Equations Discussion Part I PDFDocumento22 pagineApplications of First Order Differential Equations Discussion Part I PDFErika Dawn Luciano AmbrayNessuna valutazione finora

- EEN01a-L EXPERIMENT NO.4 - Online (ME)Documento14 pagineEEN01a-L EXPERIMENT NO.4 - Online (ME)Elizabeth De GalaNessuna valutazione finora

- M.Abdullah FA19 BEE 110 ECA 2 LAb REPORT 4Documento8 pagineM.Abdullah FA19 BEE 110 ECA 2 LAb REPORT 4Atyia JavedNessuna valutazione finora

- Ohm's Law and Kirchhoff's Voltage Law Verification (39Documento4 pagineOhm's Law and Kirchhoff's Voltage Law Verification (39Saleh Ahmed SifatNessuna valutazione finora

- EE251 Note 10 - Computer Solution of Shunt FaultsDocumento66 pagineEE251 Note 10 - Computer Solution of Shunt Faults0dz012Nessuna valutazione finora