Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Principio Da Localidade e Memoria Cache

Caricato da

Anderson AugustoTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Principio Da Localidade e Memoria Cache

Caricato da

Anderson AugustoCopyright:

Formati disponibili

Memria Cache

Princpio da Localidade

Apenas uma parte relativamente pequena do

espao de endereamento dos programas

acessada em um instante qualquer

Localidade Temporal

Um item referenciado tende a ser referenciado

novamente dentro de um espao de tempo curto

Localidade Espacial

Se um item referenciado, itens cujos endereos

sejam prximos ao dele tendem a ser logo

referenciados

Localidade em Programas

Localidade temporal:

Em funo de sua estrutura, as instrues e dados

da maioria dos programas tendem a ser acessados

de maneira repetitiva

Localidade espacial:

As instrues so acessadas quase sempre de

maneira seqencial

Elementos de arrays ou registros

Nveis de Memria - 01

Dados sempre copiados entre nveis de memria

adjacentes

Anlise focada apenas em dois nveis, um superior

e um inferior

Bloco:

Unidade mnima de informao trocada entre

nveis

Nveis de Memria - 02

Processador

Dados transferidos

Taxa/Razo de Acertos

Mede desempenho da Hierarquia

Acerto:

Informao solicitada pelo processador encontra-se no

nvel superior

Taxa de acerto: frao de acessos com acerto

Falta:

Informao solicitada pelo processador no se

encontrada no nvel superior

Nvel inferior acessado em busca do bloco.

Taxa de faltas = (1 taxa de acerto)

Tempo de Acerto e Penalidade por Faltas

Determinam a eficincia da implementao de

uma hierarquia de memria

Tempo de acerto tempo para acesso ao nvel

superior, incluindo o tempo para determinar o

acerto ou falta

Penalidade por falta tempo para a substituio

dos blocos mais o tempo de envio da informao

ao processador

Tempo de acerto <<< penalidade por falta

Memria Cache

Originalmente, nvel da hierarquia de memria

situado entre o processador e a memria

principal

Termo estendido para qualquer memria

gerenciada de modo a tirar vantagem da

localidade de acesso

Caractersticas - 01

Diminui o gargalo existente entre processador e

memria principal

Diferena de velocidade

5 a 10 vezes mais rpidas que a memria

principal

Ligada diretamente MP

10

Caractersticas - 02

Tecnologia semelhante da CPU e, em

conseqncia, possui tempos de acesso

compatveis com a mesma, resultando numa

considervel reduo da espera da CPU para

receber dados e instrues da cache

11

Nveis De Cache - 01

L1 Level 1 (nvel 1)

Dentro do processador

Mesma velocidade do processador

L2 Level 2 (nvel 2)

Dentro do invlucro, fora do chip

Metade da velocidade do processador

L3 Level 3 (nvel 3)

Cache externa, situada na placa me

12

Nveis De Cache - 02

Invlucro do processador

Processador

Cache L2

Cache L1

Memria

principal

13

Diviso da Cache L1

A cache L1 geralmente dividida em cache de

dados e cache de instrues: processamento

mais rpido

processador

dados

instrues

Cache L1

14

Localidade

Devido ao princpio da localidade, interessante

que a memria cache armazene o pedao do

programa que executado repetidas vezes,

deixando o restante do programa que no est

sendo utilizado na memria principal

15

Utilizao da Cache - 01

Sempre que o processador vai buscar uma nova

instruo (ou dado), ele acessa a memria cache:

Se a instruo estiver na cache (acerto ou hit), ela

transferida em alta velocidade para o processador

Se a instruo no estiver na cache (falta ou miss), a

execuo do programa interrompida e a instruo

desejada transferida da MP para a MC

16

Utilizao da Cache - 02

No feita a transferncia somente da instruo,

mas sim de um bloco que, segundo o princpio

da localidade, contm instrues que sero

usadas em seguida

17

controlador

de cache

Processador

Memria

principal

Cache

Palavra

(instruo

ou dado)

Bloco

de palavras

18

Elementos de Projetos de uma

Cache

Funo de mapeamento MP/MC

Algoritmos de substituio de dados na cache

Polticas de escrita

19

Funo de Mapeamento

A funo de mapeamento indica quais blocos da

MP esto presentes na cache e onde eles esto

localizados na cache

A MC e MP esto divididas em blocos de x

palavras

A MC pode conter m blocos (linhas)

A MP pode conter b blocos

20

MP

Bloco 0

.

.

.

Byte 0

Byte 1

Byte 63

Bloco 1

.

.

.

Byte 0

Byte 1

Byte 63

.

.

.

Bloco

226 -1

.

.

.

Byte 0

Byte 1

Byte 63

Diviso da MP de 4G bytes

em blocos de 64 bytes ento

tem-se 226 blocos de 64 bytes

21

MC

Byte 63

...

Byte 1

Byte 0

Linha 0

Byte 63

...

Byte 1

Byte 0

Linha 1

Byte 63

...

.

.

.

Byte 1

Byte 0

Linha 2

Byte 63

Tag ou

rtulo

...

Byte 1

Byte 0

Linha 1023

Diviso da MC de 64K bytes em

linhas de 64 bytes ento tem-se

1024 linhas de 64 bytes

22

Mapeamento Direto - 01

Cada bloco da MP tem uma linha de cache

previamente definida para ser armazenado

Muitos blocos iro ser destinados a uma mesma

linha

23

B0

.

.

.

Byte 0

Byte 1

tag

Byte 63

B1

.

.

.

Byte 0

Byte 1

Byte 63

...

Byte 1 Byte 0

Linha 0

Byte 63

...

Byte 1 Byte 0

Linha 1

Byte 63

...

.

.

.

Byte 1 Byte 0

Linha 2

...

Byte 1 Byte 0 Linha 1023

Byte 63

.

.

.

26

-1

.

.

.

Bloco 1023

Byte 0

Byte 1

Byte 63

Byte 63

24

Mapeamento Direto - 02

Cada linha da MC dever acomodar 216 blocos ou

65536 blocos (um de cada vez)

O campo tag serve para identificar qual bloco a

linha est armazenando no momento

25

Mapeamento Direto - 03

Cada endereo de MP pode ser dividido nos

seguintes elementos:

32 bits

Nmero do bloco

Nmero da linha

na linha

16 bits

216= 64K blocos

10 bits

210= 1024 linhas

Nmero do byte

6 bits

26= 64 bytes

26

Mapeamento Direto - 04

Exemplo:

O processador manda para a MC o seguinte

endereo:

00000000000001000000011001001000

4

25

27

00000000000001000000011001001000

25

Byte 63

...

Byte 1

Byte 0

Linha 0

Byte 63

...

Byte 1

Byte 0

Linha 1

Byte 63

...

Byte 1

Byte 0

Linha 2

Byte 1

Byte 0

Byte 63

Byte 63

Tag ou

rtulo

Byte 8

...

Byte 1

Byte 0

Linha 25

Linha 1023

28

Mapeamento Direto - 05

Se o campo tag do endereo for igual ao campo

tag da linha da cache, o contedo do byte

solicitado enviado para o processador

29

Mapeamento Direto - 06

Se os campos tag forem diferentes, isso significa

que o bloco desejado no se encontra na cache e,

portanto, deve ser transferido da MP para a

linha 25, substituindo o atual bloco para, em

seguida, a palavra (o byte) requerida ser

transferida para o processador pelo barramento

de dados

30

Mapeamento Direto - 08

A tcnica de mapeamento direto simples e de

baixo custo

Desvantagem: fixao da localizao para os

blocos

Imagine se durante a execuo de um programa um

dado cdigo fizer referncias repetidas a palavras

situadas em blocos alocados na mesma linha, ento

haver necessidade de sucessivas idas MP para

substituio de blocos (muitas faltas) e queda no

desempenho do sistema

31

Mapeamento Associativo - 01

Os blocos no tm uma linha fixada previamente

para seu armazenamento

O bloco armazenado em uma linha que

selecionada de acordo com o algoritmo de

substituio de cache

32

B0

.

.

.

Byte 0

Byte 1

Byte 63

B1

.

.

.

Byte 0

Byte 1

tag

Byte 63

...

Byte 1 Byte 0

Linha 0

Byte 63

...

Byte 1 Byte 0

Linha 1

Byte 63

...

.

.

.

Byte 1 Byte 0

Linha 2

...

Byte 1 Byte 0 Linha 1023

Byte 63

.

.

.

26

-1

.

.

.

Byte 63

Byte 0

Byte 1

Byte 63

33

Mapeamento Associativo - 02

Cada linha da MC pode acomodar um dos 226

blocos da memria principal

O campo tag tem agora 26 bits de tamanho

34

Mapeamento Associativo - 03

Cada endereo de MP dividido nos

seguintes elementos:

32 bits

Nmero do bloco

Nmero do byte

26 bits

226 blocos

6 bits

26 bytes

35

Mapeamento Associativo - 04

Quando o processador realiza um acesso

memria, o campo bloco do endereo

comparado com todos os 1024 tags da cache

para verificar se o bloco est ou no presente

36

Mapeamento Associativo - 05

Se o bloco estiver presente, o byte transferido

para a CPU seno o endereo do bloco usado

para buscar na memria principal o bloco

ausente

37

Mapeamento Associativo - 06

Desvantagem: teste do campo bloco do endereo

de memria com todos os tags da cache

38

Mapeamento Associativo por

Conjunto de N Posies - 01

Esquema intermedirio entre o direto e o

totalmente associativo

Nmero fixo de posies onde um bloco pode ser

armazenado na cache

Cache associativa de n posies:

n posies possveis para cada bloco

Cache com conjuntos de n posies

Blocos mapeados diretamente em um conjunto e

colocado em qualquer elemento do conjunto

39

Bits de Validade

Quando o processador inicializado, a cache

est vazia e os rtulos no tm significado

Bits de validade so adicionados cache para

identificar se um bloco tem informaes vlidas

Bit igual a zero -> Informao invlida

40

Tratamento de Faltas 01

Atividades do controle principal:

Parar o processador

Congelar o contedo dos registradores

Um controle separado trata as faltas:

Busca a informao necessria na memria

Atualiza a informao na cache

Execuo retomada no ciclo gerador da falta

41

Tratamento de Faltas 02

1. Enviar memria o valor original de PC

2. Comandar uma leitura da unidade de memria e

esperar o resultado

3. Escrever o resultado da leitura na entrada da

cache, seu rtulo e bit de validade

4. Reiniciar a execuo da instruo no passo 1

42

Parada em Uso

Tcnica para reduo do nmero de ciclos

parados pela falta no acesso cache

Baseia-se no processamento de outras instrues

durante o tratamento de faltas

Na falta produzidas pelo acesso a dados novas

instrues que no dependem do dado podem ser

executadas

No ajuda para faltas no acesso a instrues

Geralmente, no mostra ganhos expressivos pela

dependncia do dado sendo acessado

43

Algoritmos De

Substituio De Cache - 01

Qual bloco atualmente armazenado na cache

deve ser retirado para dar lugar a um novo bloco

que est sendo transferido?

LRU (Least Recently Used): O controlador de cache

escolhe o bloco que est h mais tempo sem ser

utilizado pela CPU

FIFO (First in first out): O controlador de cache

escolhe o bloco que est armazenado h mais tempo

na cache, independentemente de estar sendo usado ou

no com freqncia pela CPU

44

Algoritmos De

Substituio De Cache - 02

LFU (Least Frenquently Used): o controlador de

cache escolhe o bloco que tem tido menos acessos

(menos referncias) por parte da CPU

Escolha aleatria

45

Polticas de Escrita pela Memria

Cache - 01

Quando o processador realiza uma operao de

escrita, esta acorre imediatamente na cache

A memria cache uma memria intermediria

logo necessrio que a MP seja atualizada para

que o sistema mantenha sua correo e

integridade

46

Antes da execuo

da instruo X = Y + Z

Memria Principal

Cache

Processador

X=1

Y=7

Z=2

X=Y+Z

X=1

Y=7

Z=2

X=Y+Z

X=Y+Z

Bloco 4

Bloco 4

47

Depois da execuo

da instruo X = Y + Z

Memria Principal

Cache

Processador

X=1

Y=7

Z=2

X=Y+Z

X=9

Y=7

Z=2

X=Y+Z

X=Y+Z

Bloco 4

Bloco 4

48

Processador

Processador

Processador

X=Y+Z

Cache

X=1

Cache

X=1

cache

X=9

X=9

MP

X=9

X=1

X=9

49

Polticas de Escrita pela Memria

Cache - 02

O bloco 4 (o valor de X) precisa ser atualizado na

memria

Quando?

Depende da poltica de escrita

50

Write Through - 01

Cada escrita em uma palavra da cache acarreta

em uma escrita na palavra correspondente na

MP, assegurando validade permanente e igual ao

contedo de ambas as memrias

Caso haja outras CPUs, estas alteraro tambm

suas caches

51

Write Through - 02

Simples, mas no favorece o desempenho

Qualquer escrita faz com que a informao seja

escrita tambm na memria principal

Aumento do nmero de ciclos de clock

Buffer de escrita:

Armazena o dado enquanto este aguarda sua escrita na

memria

Reduz o problema das escritas na mem. principal

Buffer cheio Processador parado em escritas

52

Write Through - 03

Faltas de escrita:

Processador simplesmente atualiza a memria

principal, como antes

No ocorrem leituras da memria principal

durante a escrita pelo processador

53

Write Back

Quando ocorre uma escrita, o novo

valor escrito apenas no bloco da cache

O bloco s ser escrito na memria

principal quando ele precisar ser

substitudo na cache

Pode melhorar muito o desempenho,

porm mais complexo que o writethrough

54

Tamanho do Bloco 01

Relaciona-se com a explorao da localidade

espacial e desempenho

Em geral, a taxa de faltas cai com o aumento

do tamanho do bloco

55

Tamanho do Bloco 02

Taxa de faltas pode crescer se o bloco

representar uma frao considervel do tamanho

da cache

Pequeno nmero de blocos -> Alta competio

Blocos retirados da cache sem muita explorao

Potrebbero piacerti anche

- Oc Aula 05Documento28 pagineOc Aula 05Raphael QuintanilhaNessuna valutazione finora

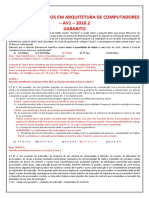

- Gabarito Top Av Arq MM Prova Av1 2018 2Documento5 pagineGabarito Top Av Arq MM Prova Av1 2018 2Alexandre Melo100% (1)

- AMD Athlon 64 X2Documento5 pagineAMD Athlon 64 X2César GomesNessuna valutazione finora

- Exercicio 6Documento2 pagineExercicio 6PhiberdjNessuna valutazione finora

- Arquitetura MARIE Capítulo 4Documento65 pagineArquitetura MARIE Capítulo 4Diego Villegas VillacrecesNessuna valutazione finora

- Organização de Computadores - Gabarito AD1 2006.1Documento8 pagineOrganização de Computadores - Gabarito AD1 2006.1Mauricio RodriguesNessuna valutazione finora

- Computador Função e InterconexõesDocumento2 pagineComputador Função e InterconexõesManoel VictorNessuna valutazione finora

- Aula Microcontroladores 2 RegistradoresDocumento35 pagineAula Microcontroladores 2 RegistradoresLendione BatistaNessuna valutazione finora

- Modos Endereçamento MIPSDocumento19 pagineModos Endereçamento MIPSMatheusNessuna valutazione finora

- Aula 05Documento20 pagineAula 05Xavier JoaquimNessuna valutazione finora

- AP1 - 2013-2 - Gabarito - Organização de ComputadoresDocumento4 pagineAP1 - 2013-2 - Gabarito - Organização de ComputadoresJoeme AlvesNessuna valutazione finora

- Exercícios sobre Gerenciamento de MemóriaDocumento8 pagineExercícios sobre Gerenciamento de MemóriaJonathan MouraNessuna valutazione finora

- Endereçamento de Memórias e Lógica de SeleçãoDocumento12 pagineEndereçamento de Memórias e Lógica de SeleçãoAntonio Celso VieiraNessuna valutazione finora

- QuestionarioDocumento2 pagineQuestionarioapi-3763143100% (1)

- Aula 13 Processamento de Dados Na UcpDocumento20 pagineAula 13 Processamento de Dados Na UcpErmerson MoraesNessuna valutazione finora

- Gerencia de Memorias CacheDocumento59 pagineGerencia de Memorias CacheFabiano Andrade100% (1)

- Apresentação Sobre Memória de Um ComputadorDocumento33 pagineApresentação Sobre Memória de Um ComputadorMarco Antonio Maues Jr.Nessuna valutazione finora

- ACSO Cap5 Conceitos 2020 2021 v3Documento74 pagineACSO Cap5 Conceitos 2020 2021 v3MitchocenceNessuna valutazione finora

- Micros 03Documento14 pagineMicros 03fpreisNessuna valutazione finora

- Arquitetura de Computadores - Lista de ExercíciosDocumento14 pagineArquitetura de Computadores - Lista de ExercíciosalexNessuna valutazione finora

- Aula 13Documento61 pagineAula 13Igor LimaNessuna valutazione finora

- Curso_de_Tecnologia_em_Sistemas_de_CompuDocumento8 pagineCurso_de_Tecnologia_em_Sistemas_de_CompuHugo RossiNessuna valutazione finora

- ExercDocumento2 pagineExercjorgeNessuna valutazione finora

- MemoriaDocumento70 pagineMemoriaLorena AmaralNessuna valutazione finora

- Estrutura e Função Do ProcessadorDocumento32 pagineEstrutura e Função Do ProcessadorrodrigolosinaNessuna valutazione finora

- Cap 4 Caminho de Dados e ControleDocumento62 pagineCap 4 Caminho de Dados e ControleIgor GledsonNessuna valutazione finora

- Hierarquia de memórias em sistemas de computaçãoDocumento7 pagineHierarquia de memórias em sistemas de computaçãoVinícius OliveiraNessuna valutazione finora

- Estrutura e Função Do ProcessadorDocumento36 pagineEstrutura e Função Do ProcessadorRamon Pierre TomazNessuna valutazione finora

- Lista prova 1 memória cacheDocumento6 pagineLista prova 1 memória cacheWeslley RodrigoNessuna valutazione finora

- Cache ExerciciosDocumento3 pagineCache ExerciciospatyvirgilioNessuna valutazione finora

- Funções da UCP e componentes de uma CPUDocumento4 pagineFunções da UCP e componentes de uma CPUNatalFonseca0% (2)

- Organização de Computadores - Simulado - Aula8Documento5 pagineOrganização de Computadores - Simulado - Aula8ddrum21Nessuna valutazione finora

- Arquitetura e Organização de Computadores: Componentes Básicos de Um ComputadorDocumento66 pagineArquitetura e Organização de Computadores: Componentes Básicos de Um ComputadorNick DiasNessuna valutazione finora

- AP1 - 2019-1 - Gabarito - Organização de ComputadoresDocumento6 pagineAP1 - 2019-1 - Gabarito - Organização de ComputadoresJoeme AlvesNessuna valutazione finora

- Arquitetura de Computadores PDFDocumento64 pagineArquitetura de Computadores PDFronaldo17433Nessuna valutazione finora

- Exercicios Arquitetura e Sistemas de ComputadoresDocumento4 pagineExercicios Arquitetura e Sistemas de ComputadoresA Carlos GarciaNessuna valutazione finora

- Organização de Computadores - Respostas da 3a Lista de ExercíciosDocumento12 pagineOrganização de Computadores - Respostas da 3a Lista de ExercíciosPatrick LaraNessuna valutazione finora

- Microprocessadores e Computadores PessoaisDocumento3 pagineMicroprocessadores e Computadores PessoaisAntonio milton MugabeNessuna valutazione finora

- Tipos de barramento e placa mãeDocumento8 pagineTipos de barramento e placa mãeNathan roucheNessuna valutazione finora

- UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁDocumento5 pagineUNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁRodolfo FerreiraNessuna valutazione finora

- Arquitetura de Compuradores - Lista 4 PDFDocumento10 pagineArquitetura de Compuradores - Lista 4 PDFSamuel LeonhardtNessuna valutazione finora

- SDAC-Arquitetura de MicroprocessadoresDocumento17 pagineSDAC-Arquitetura de MicroprocessadoresapinheiroNessuna valutazione finora

- Detalhamento dos blocos de CPU e PeriféricosDocumento4 pagineDetalhamento dos blocos de CPU e PeriféricosJúnior MoreiraNessuna valutazione finora

- Tema 2 - Componentes de HardwareDocumento9 pagineTema 2 - Componentes de HardwareRenan “Ribas” RibeiroNessuna valutazione finora

- 1a ListaExerciciosDocumento4 pagine1a ListaExerciciosRilner Azevedo de MucioNessuna valutazione finora

- Lista 1 Sel415Documento3 pagineLista 1 Sel415raulpmicenaNessuna valutazione finora

- Memória e Desempenho em Sistemas DigitaisDocumento2 pagineMemória e Desempenho em Sistemas DigitaisClarissa Conta pra ndsNessuna valutazione finora

- Ap1 - Questões 11,12,13,14,21,22,25e26Documento4 pagineAp1 - Questões 11,12,13,14,21,22,25e26Thiago Francisco Paes AlvesNessuna valutazione finora

- Prova 1 - ARQUITETURA DE COMPUTADORES III - Ciência Da Computação - PUCDocumento9 pagineProva 1 - ARQUITETURA DE COMPUTADORES III - Ciência Da Computação - PUCVítor Cabral Rodrigues PiresNessuna valutazione finora

- Lista 3 - Marcone Gabriel Da SilvaDocumento6 pagineLista 3 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVANessuna valutazione finora

- SO Gerência MemóriaDocumento37 pagineSO Gerência MemóriaElvio MalveziNessuna valutazione finora

- Funções de instruções, estados de execução e técnicas de interrupçãoDocumento2 pagineFunções de instruções, estados de execução e técnicas de interrupçãoHERMIL GLAUBER MARGALHO DAX REISNessuna valutazione finora

- Microprocessadores e sua estruturaDocumento61 pagineMicroprocessadores e sua estruturaKiko Liko100% (1)

- Microcontrolador 01 PDFDocumento21 pagineMicrocontrolador 01 PDFlidiomar10Nessuna valutazione finora

- Microprocess AdoresDocumento59 pagineMicroprocess AdoresRicardo GomesNessuna valutazione finora

- Document 1Documento7 pagineDocument 1Renata OliveiraNessuna valutazione finora

- Componentes de HardwareDocumento19 pagineComponentes de Hardwarehenriquetg002Nessuna valutazione finora

- Calibração de termistor para medição de temperaturaDocumento8 pagineCalibração de termistor para medição de temperaturasilvio de LimaNessuna valutazione finora

- Apostila LispDocumento53 pagineApostila LispHigashi MonteiroNessuna valutazione finora

- Newton 1a Lei MovimentoDocumento3 pagineNewton 1a Lei MovimentoBUBUNessuna valutazione finora

- Uma Teoria Do Pensar (2022)Documento8 pagineUma Teoria Do Pensar (2022)André BizziNessuna valutazione finora

- Raciocínio lógico enigmasDocumento5 pagineRaciocínio lógico enigmasDyl FerreiroNessuna valutazione finora

- Análise da Regressão MúltiplaDocumento31 pagineAnálise da Regressão Múltiplaluizmario15Nessuna valutazione finora

- Terapia narrativa e relação terapeuticaDocumento9 pagineTerapia narrativa e relação terapeuticaSilneiNessuna valutazione finora

- Flexão Pura e SimplesDocumento28 pagineFlexão Pura e SimplesrsainttNessuna valutazione finora

- Fichas Trabalho ComplementarDocumento66 pagineFichas Trabalho ComplementarAnabela CorreiaNessuna valutazione finora

- Dilatação Térmica LinearDocumento10 pagineDilatação Térmica LinearHebert FerrazNessuna valutazione finora

- Teorema de Tales Divisão de SegmentosDocumento13 pagineTeorema de Tales Divisão de SegmentosKamilla Borges AlmeidaNessuna valutazione finora

- Aula 5 - Química XDocumento24 pagineAula 5 - Química XGuilhermeNessuna valutazione finora

- Derek Parfit - Identidade PessoalDocumento18 pagineDerek Parfit - Identidade PessoalRaoul MarianNessuna valutazione finora

- Normas de TCC Fatec Zona LesteDocumento30 pagineNormas de TCC Fatec Zona Lesteausto01Nessuna valutazione finora

- Relação Euler QuadriláterosDocumento6 pagineRelação Euler QuadriláterosalexNessuna valutazione finora

- Práticas de gestão em agência bancáriaDocumento58 paginePráticas de gestão em agência bancáriaMorenah MacielNessuna valutazione finora

- 4 Lista de Exercícios Elementos Mecanica Clássica - MUVDocumento3 pagine4 Lista de Exercícios Elementos Mecanica Clássica - MUVJorge PINTO GRANDENessuna valutazione finora

- Perfis de concentração em reações de transferência de massaDocumento8 paginePerfis de concentração em reações de transferência de massaEdilton NunesNessuna valutazione finora

- Cronograma de Estudos EsaDocumento22 pagineCronograma de Estudos EsaMONITUTORNessuna valutazione finora

- Karl PopperDocumento2 pagineKarl PopperSara NetoNessuna valutazione finora

- Implementação de funções lógicas com multiplexadorDocumento17 pagineImplementação de funções lógicas com multiplexadorKelvin TanguneNessuna valutazione finora

- Provas Matem Tica ANTIGO 20211 APX3xlsx APs - vqvrlf6p9869gnf11062021Documento1 paginaProvas Matem Tica ANTIGO 20211 APX3xlsx APs - vqvrlf6p9869gnf11062021Jakson de almeidaNessuna valutazione finora

- Critérios divisibilidade e números primosDocumento5 pagineCritérios divisibilidade e números primosOtávioNessuna valutazione finora

- Relatório experimental valida lei de Boyle-MariotteDocumento14 pagineRelatório experimental valida lei de Boyle-MariotteVinícius SilvaNessuna valutazione finora

- Fichamento - Implementação de Políticas PúblicasDocumento2 pagineFichamento - Implementação de Políticas PúblicasMarco AndradeNessuna valutazione finora

- Processo FundiçãoDocumento15 pagineProcesso FundiçãowagnercpcNessuna valutazione finora

- Fundamentos Robótica MecatrônicaDocumento10 pagineFundamentos Robótica MecatrônicaFelipe Viveiros da RochaNessuna valutazione finora

- Dist AmostralDocumento13 pagineDist AmostralAbguellXerindaDinisNessuna valutazione finora

- Soluções (Curvas de SolubilidadeDocumento38 pagineSoluções (Curvas de SolubilidadeGleisonNessuna valutazione finora

- Aula-1-Espaços Vetoriais-1Documento37 pagineAula-1-Espaços Vetoriais-1Gabriel UrbanoNessuna valutazione finora