Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Sect 4

Caricato da

Sry SantosDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Sect 4

Caricato da

Sry SantosCopyright:

Formati disponibili

Section 4: Rectifier Operation & Control

Chapter 1 - Rectifier Operating Principles

1.1 Introduction .............................................................................................. 4-1

1.2 SCR principles .......................................................................................... 4-1

1.2.1 Internal semiconductor structure .................................................. 4-2

1.2.2 SCR triggering mechanisms ........................................................ 4-3

1.2.3 SCR Turn-on characteristics ........................................................ 4-6

1.2.4 SCR Turn-off mechanisms .......................................................... 4-7

1.2.5 SCR turn-off characteristics ......................................................... 4-8

1.3 SCR Ratings ............................................................................................. 4-9

1.4 Phase control techniques ........................................................................ 4-11

1.4.1 Basic phase-control principles ................................................... 4-11

1.4.2 3-phase controlled rectifier ........................................................ 4-13

1.5 Rectifier construction ............................................................................. 4-14

1.6 Rectifier control system .......................................................................... 4-17

1.6.1 Control system overview ........................................................... 4-17

1.6.2 Charge mode selection ............................................................... 4-19

1.6.3 Input supply fault detection. ...................................................... 4-19

1.6.4 Input current limit ...................................................................... 4-19

1.6.5 Battery current limit ................................................................... 4-19

1.6.6 Battery temperature compensation ............................................ 4-19

1.6.7 Controlled start/stop ................................................................... 4-20

1.6.8 DC overvoltage and undervoltage fault detection ..................... 4-20

1.6.9 Battery Circuit Breaker .............................................................. 4-20

Chapter 2 - Rectifier Logic Board

2.1 Chapter overview ................................................................................... 4-21

2.2 General description ................................................................................. 4-21

2.2.1 Circuit board functions .............................................................. 4-21

2.2.2 Input/Output connections ........................................................... 4-21

2.2.3 Block diagram description ......................................................... 4-23

2.3 Detailed circuit description .................................................................... 4-26

2.3.1 Introduction ................................................................................ 4-26

2.3.2 Reference voltage generator ...................................................... 4-26

2.3.3 Battery temperature compensation ............................................ 4-27

2.3.4 Volts error amplifier .................................................................. 4-27

Battery current limit ......................................................... 4-29

Input current limit ............................................................ 4-29

Start/Stop control ............................................................. 4-30

2.3.5 Drive pulse generator ................................................................. 4-31

Analogue timing control circuit ....................................... 4-31

Digital signal processing .................................................. 4-33

S-4.FM5 - Issue 2 Dated 21/08/97

SECTION 4 - Rectifier Operation & Control

7200 Series UPS Service Manual

2.3.6 Start/Stop logic .......................................................................... 4-35

Input mains phase rotation error ...................................... 4-35

Input mains undervoltage ................................................. 4-35

ON/OFF control from UPS Logic Board ......................... 4-36

Control power supply failure detection ............................ 4-36

2.3.7 Control power supplies .............................................................. 4-36

2.4 Summary Information ............................................................................ 4-37

Chapter 3 - Rectifier Gate Drive Interface Board (4542040W)

3.1 Introduction ............................................................................................ 4-39

3.2 Rectifier SCR gate drive requirements ................................................... 4-39

3.3 Gate drive circuit .................................................................................... 4-40

Chapter 4 - Rectifier Snubber Board (4540043B)

4.1 Snubber requirements and characteristics .............................................. 4-41

4.2 Snubber board ......................................................................................... 4-42

ii

S-4.FM5 - Issue 2 Dated 21/08/97

Section 4:

Chapter 1 - Rectifier Operating Principles

1.1

Introduction

The 7200 series UPS employs a fully controlled, 3-phase SCR bridge rectifier to

provide a regulated DC busbar suitable for charging the UPS batteries and present

the inverter with a stable input voltage. This chapter describes the principles of

operation of an SCR device and its use in a phase-controlled rectifier circuit.

1.2

SCR principles

The Thyristor, or Silicon Controlled Rectifier (SCR), is a three-terminal device

which was first introduced to the power electronics industry in 1957. It is essentially a solid-state switch which is normally triggered from its non-conducting

state (OFF condition) to its conducting state (ON condition) by a pulse applied between its gate and cathode terminals. In general, in its ON-state the SCR acts as a

unidirectional conducting device and blocks current flow in the reverse direction

(cathode-to-anode). In its OFF-state, it blocks current flow in both directions.

Figure 4-1: SCR principles (summary)

SCR Three Terminal Device

ANODE

An SCR is a three-terminal device which

can be considered to act as an

electronically controlled switch.

CATHODE

GATE

SCR Switch Analogy

SCR ON

current flow anode-cathode

That is, when an SCR is turned ON

(conducting) the forward voltage

drop between its Anode and

Cathode is small and can be

considered to be short-circuit for all

practical purposes.

ANODE

CATHODE

SCR OFF

no current flow

ANODE

CATHODE

s4-c1.fm5 - Issue 2 Dated 21/08/97

Alternatively, in its non-conducting

(OFF) state the SCR presents a

very high Anode/Cathode impedance and can be considered to be

open circuit like an open switch.

4-1

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

1.2.1

7200 Series UPS Service Manual

Internal semiconductor structure

The SCR structure comprises four alternate P and N type semiconductor layers. Figure 4-2 shows how these layers can be split to form a pair of interconnected P-N-P and N-P-N transistors; annotated T1 and T2 in the diagram.

Figure 4-2: SCR Regenerative transistor analogy

Anode

P1

N1

Gate

Gate

P2

N2

Anode

Gate

IA

Anode

P1

N1

P2

N2

N1

P2

T1

T2 (NPN)

T1 (PNP)

Anode

I2

I1

Gate

T2

Ig

Cathode

Cathode

Cathode

Cathode

With reference to the transistor model above, the two transistors are connected in

a regenerative manner i.e. ignoring the gate current (Ig), T2s collector current

(I2) is drawn through T1 emitter-base junction (turning T1 on) and T1s collector

current (I1) flows through T2 base-emitter junction (turning T2 on). This can be

expressed mathematically as I2 = 2 x I1 (where 2 is the current gain of T2)

and I1 = 1 x I2 (where 1 is the current gain of T1).

Regeneration occurs when the sum of the current gain of both transistors (T1 and

T2), also described as the loop gain of the two transistors, is greater than unity;

at which point the transistors try to turn ON each other harder and harder until

both devices rapidly reach full saturation. This equates to the SCR being in its

conduction state, whereby the voltage drop across the device is approximately

1.0V and its anode current is determined only by the external voltage and load impedance.

As with a normal transistor, the current gain T1 and T2 varies proportionally

with emitter current, and in the absence of any gate signal the only current initially

flowing through the transistors is a leakage current comparable to with the reverse

current of a diode. Under these conditions the value of the current gain associated

with each emitter falls to a very low figure, and the device is designed such that

the loop gain is made less than unity, and the transistors remain non-conducting

i.e. this is equivalent to the SCRs non-conducting forward blocking state. Indeed, the fact that the two emitter-base pairs need be designed only for an average

value of of 0.5, to produce the effective unity loop gain necessary to make conduction self-sustaining, makes it possible to use relatively thick base layers, and

hence obtain a much greater voltage blocking capability than in a practicable transistor.

In summary, the SCR can be triggered from its non-conducting to conducting

state by increasing the circulating current through T1 and T2 to the point where

the loop gain rise above unity. This may be accomplished by several means, some

of which are undesirable, as described below.

4-2

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

1.2.2

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

SCR triggering mechanisms

Breakover voltage

Figure 4-3: SCR static characteristic with zero gate current

IA

Forward

Conducting

Holding

Current

Reverse

VAK

Avalanche

Breakdown

Forward

Blocking

Breakover

Voltage

Reverse

Figure 4-3 illustrates the static characteristics for the SCR anode current (IA) and

anode-cathode voltage (VAK) with zero gate current. This shows that in the reverse

direction the SCR characteristic is similar to that of a normal diode, in that very

little current flows as the reverse voltage increases until the reverse avalanche

breakdown point is reached, where-upon the current rapidly increase.

In the forward blocking region, increasing the forward voltage does not tend to

increase the leakage current until the point is reached where avalanche multiplication begins to take place. Past this breakover voltage point, the leakage current

increases quite rapidly until the total current through the device is sufficient to

raise the internal loop gain 1 whereupon the SCR switches to its conduction

state provided the anode current remains in excess of a minimum current known

as the holding current. When the anode current falls below the holding current

the loop gain falls below unity and the device will revert to its forward blocking

(non-conducting) state.

Albeit not necessarily destructive, this means of triggering the SCR is undesirable

(especially in phase-control applications) and usually avoided by employing a

device whose forward breakover voltage and peak inverse voltage ratings are well

outside the available circuit voltage. Additionally, external components may be

used to prevent spurious voltage spikes inadvertently triggering the device by this

means.

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-3

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

Gate triggering

Figure 4-4: Effects of gate current on triggering

IA

Forward

Conducting

Ig2 > Ig1 > Ig0

Holding

Current

Ig2

Ig1 Ig0

Reverse

Avalanche

Breakdown

Blocking

VAK

Forward

Reverse

The usual method employed to trigger the SCR from the blocking to the conducting state, is to inject sufficient current into the gate terminal (T2 base) to increase the current in the main circuit by the modest amount required to raise the

loop gain to greater than unity. That is, the injected gate current (Ig) leads to an

increase in I2 which in turn leads to an increase in I1, which further increases I2....

and so on, until both transistors are saturated.

Figure 4-4 shows that for increasing magnitudes of gate current, the region of

characteristics between breakover current and holding current is narrowed and the

effective forward breakover voltage is reduced. For sufficiently high gate currents

the entire forward blocking region is removed and the V-I characteristics are essentially identical to those of a P-N rectifier.

This is a very advantageous mode of operation, since it is possible to use a device

with a forward breakover voltage much higher than any voltage likely to be encountered in the circuit, and use only a moderate amount of trigger power to start

the high-conduction state.

Once the gate has been used to trigger the device into conduction it loses control

and can be removed without affecting the external circuits operation i.e. once

the SCR is conducting, the anode current is determined solely by the external circuits voltage and impedance, and the only method of turning the device off is to

reduce this to below the SCRs holding-current level. To minimise internal losses

and heating effects, it is usual therefore not to apply the gate current for much

longer than is necessary to assure the device turns on; for this reason the gate

signal normally takes the form of a current pulse of sufficient amplitude and duration to ensure this condition is satisfied.

4-4

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Figure 4-5: Gate drive parameters spread

Maximum

gate current

allowed

Gate Voltage (V)

12

Maximum

gate voltage

allowed

SAFE

OPERATING

AREA

Maximum

gate power

dissipation

(V x I)

Minimum

gate voltage

allowed

Minimum

gate current

allowed

0.5

1.0

1.5

Gate Current (A)

2.0

As can be seen from Figure 4-5, the spread of gate voltage versus gate current can

be quite wide for different load variations. The gate circuitry must therefore be

able to accommodate this variation and also allow for different sizes of SCR. Typical design values are for 6V and 1A pulses for 10sec.

dV/dt triggering

As with all semiconductor devices, there are internal capacitive effects between

the various P and N layers, and between the electrodes. In the case of the SCR

these effects can turn-on the device inadvertently if the rate of change of voltage

applied to it are sufficient to raise the current flow to a level which raises the internal loop gain above unity:

i.e.the current flowing through the capacitor = CdV/dt and has the same effect

as injecting a gate current if allowed to increase to the appropriate level.

As with the breakover-voltage triggering mechanism described above, this

method of turning on the device is not generally used as it is uncontrollable and

is normally prevented by connecting additional components (known as snubbers)

across the device to limit the rate of such voltage changes (see paragraph 4.1 on

page 4-41).

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-5

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

1.2.3

7200 Series UPS Service Manual

SCR Turn-on characteristics

Figure 4-6: SCR turn-on characteristics

VAK x IA

Power

Dissipation

t

VAK

90%

Voltage across

SCRs

10%

t

IA

90%

Anode

Current

10%

0

td

t

tr

ton

Gate

Current

0

10%

As described previously, two basic conditions must be satisfied in order to turn

on an SCR. First, the device must be forward-biased i.e. its anode must be positive with respect to its cathode; second, a suitable current pulse must be injected

into its gate terminal. When both these conditions are satisfied, the device will

turn ON and an anode-cathode current will flow through the device depending on

external circuit parameters.

In detail, the turning-on of an SCR in response to a gate trigger signal may be considered to take place in three phases. First, a delay occurs before any kind of significant response is apparent. Secondly, under the direct influence of the gate

current, conduction is established in a small area adjacent to the gate. Finally, the

conducting area spreads with a fairly constant velocity, no longer influenced by

the gate, until the whole area is conducting.

Corresponding to the increase in conducting area, the resistance of the cell falls

from the near-infinite blocking value, rapidly to a relatively high value while

conduction is concentrated in the gate region, and then relatively to a the steady

state value. The instantaneous voltage drop thus follows a waveform such as that

illustrated in Figure 4-6, resulting in an instantaneous power dissipation:

w = VAK x IA .

4-6

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Conventionally, as shown in Figure 4-6, the total switching time is divided into

the delay time (td) and the rise time (tr); these periods are arbitrarily delimited, for

the purpose of measurement, at the instants when the voltage across the SCR falls

to 90% and 10% of the initial blocking voltage. The rise-time (tr) is defined as the

time required for the anode voltage to drop from 90% to 10% of its forward blocking value. The rise of current as voltage across the SCR falls is determined largely

by the external circuit. In a purely resistive circuit the current will rise in the same

manner as the voltage falls; hence the term rise time. It is important that the instantaneous current-voltage product during the turn on interval does not exceed

the device dissipation capability. For this reason, the rate of rise of anode current

(di/dt) must be limited. The delay time (td) is reduced as the gate current is increased; however there are other considerations that affect the chosen gate signal,

as described later (see paragraph 3.2 on page 4-39).

1.2.4

SCR Turn-off mechanisms

To turn an SCR OFF its anode-cathode current must be reduced below the holding current value, which is usually very small. This can be achieved by interrupting the current flow externally, by opening an switch for example, or by some

means reverse biasing the anode-cathode potential i.e. making its anode negative with respect to the cathode.

The processes of turning off an SCR by reversing its anode-cathode voltage is

known as commutation; and can broadly be divided into two forms described

as either natural or forced commutation.

Figure 4-7: SCR Turn-off mechanism

A

Anode

IA

Anode

P1 +

N1

Gate

Gate

P2 +

N2

J1

J2

J3

Cathode

Cathode

Referring to Figure 4-7, when an SCR is conducting, each its three semiconductor

junctions (J1-J3) are forward-biased and the two base regions (N1 & P2) are

heavily saturated with holes and electrons (stored charge).

When the SCR is commutated by the application of a reverse anode-cathode voltage, the holes and electrons in the vicinity of the two end junctions (J1 & J3) will

diffuse to the junctions and result in a reverse current in the external circuit. The

voltage across the SCR will remain at about 0.7V as long as an appreciable reverse current flows. After the holes and electrons in the vicinity of J1 and J3 have

been removed, the reverse current will cease; the junctions J1 and J3 will assume

a blocking state and the voltage across the SCR will then increase to a value determined by the external circuit. However, recovery of the device is not complete,

since a high concentration of holes and electrons still exists in the vicinity of the

centre junction (J2). This concentration decreases by the process of recombination in a manner which is largely independent of the external bias conditions.

After the hole and electron concentration at J2 has decreased to a low value, J2

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-7

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

will regain its blocking state and a forward voltage may then be reapplied to the

SCR without turning it back on. The time that elapses after the cessation of forward current flow and before forward voltage may safely be applied is called the

SCR turn-off time (toff), and can typically range from 3sec to 50sec depending on the design and construction of the particular device.

1.2.5

SCR turn-off characteristics

Figure 4-8: SCR turn-off characteristics

Anode-Cathode

Current

trr

0

tfb

toff

Voltage across 0

SCRs

t1

t2

t3

t5

t4

t6

t9

t7

t10

t8

Figure 4-8 illustrates graphically the (some-what idealised) effects on the SCR

voltage and current of the turn-off mechanism described above. The total turn-off

time (toff) is the total time between the anode current falling to zero (t3) and the

device being capable of supporting a forward voltage (t8). This is shown to comprise two components. First the reverse recovery time (trr) (t3 to t6) followed by

the forward blocking time (tfb) (t6 to t8). These intervals are not constant, but are

a affected by several, mainly external, parameters.

For example the turn-off time will increase with:

An increase in junction temperature.

An increase in forward current amplitude (t1 to t2).

An increase in the rate of decay of forward current (t2 to t3).

A decrease in peak reverse current (t4).

A decrease in reverse voltage (t5 to t7).

An increase in the rate of reapplication of forward blocking voltage (t8 to

t9).

An increase in forward blocking voltage (t9 to t10).

An increase in external gate impedance.

A more positive gate bias voltage.

Natural versus forced commutation

As its title suggests, natural commutation takes place automatically when the

voltage across the SCR reverses as part of the external circuit function this is the

case in the phase-controller application, as the device is fed with the input a.c.

4-8

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

mains supply and is naturally reverse-biased on every negative half-cycle. As

this happens at 50Hz, the reverse voltage is maintained across the SCR for several

tens of milli-seconds and presents no commutation timing problems.

Forced commutation is used when the SCR is fed from a DC source, such as in

an inverter application. Under such circumstances the reverse voltage must be

generated by a dedicated commutation circuit which must present a reverse voltage pulse of sufficient magnitude and duration to ensure the device has time to

fully turn off under all rated load conditions. (Note: in the 7200 series UPS the

inverter section is transistor based so this does not apply).

1.3

SCR Ratings

Junction temperatures

Power losses in an SCR produces thermal energy (heat) which must be conducted

away from the junction region. Heat dissipation is achieved by mounting the SCR

on a suitable heatsink the heat developed within the device then flows via the

device case and heatsink to the ambient air, and can be dispersed by fan extraction

if necessary.

The maximum operating junction temperatures are typically 125C - 150C.

Heat losses are a function of:

ON-state conduction losses

A product of the voltage drop across the device (about 1.5V) and the

amount of current flowing through it. This can be as high as 500W.

OFF-state losses

These losses are due to leakage current and are therefore very small.

Switching losses

The heat generated during turn-on and turn-off is a function of the voltage

across the device and the current flowing through the device at the time of

switching. These losses can be very large but exist for a very short duration only, as illustrated in the characteristic curves shown previously.

An upper temperature limit must be imposed to restrict mechanical failure and

prevent excessive temperatures to internal joints and leads (which may interfere

within the device package). When such a temperature limit is imposed (e.g.

125C) it will have a direct affect on the device rated current capability.

Current ratings

Several rated current conditions can be stipulated in the device specification; and

thermal breakdown is likely if any one of these values are exceeded.

Average current rating (IAV)

This is the maximum average ON-state current the device may conduct

continuously.

RMS Current rating (IRMS)

This is the maximum RMS ON-state current the device may conduct continuously i.e. this is the steady-state operating current.

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-9

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

Peak Current rating (IPK)

This is the repetitive surge current the device may conduct at a specified

short pulse-width.

It rating (It)

This is the maximum forward non-repetitive surge current (i.e. Overload

current) capability, and is usually specified for one half cycle of 50Hz

operation.

Voltage ratings

Maximum Forward Voltage (VFBO)

This is the maximum forward voltage that can be applied across the device

(anode-to-cathode) without the device being forced to turn on.

There is always a small anode-to-cathode leakage current when a voltage

is applied to the device, and if the voltage is increased to the critical VFBO

the SCR will switch rapidly into full conduction. This is not dangerous to

the device itself, but may cause a short circuit within the rectifier if other

SCRs are already conducting when this false triggering occurs.

Maximum reverse voltage (VRBO)

This is the maximum reverse voltage that can be applied across the device

(cathode-to-anode) without the device being forced into reverse breakdown. If VRBO is exceeded it will lead to destructive breakdown, and the

SCR will not recover (thats blown it!).

Maximum rate-of-change (dv/dt)

A very high rate of increase of forward (anode-to-cathode) cathode dv/dt

can turn on the SCR, even though there is no gate signal and VFBO is not

exceeded (see page 4-5).

4-10

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

1.4

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Phase control techniques

Phase control of the power rectifier is made possible by the fact that it contains

SCRs (Silicon Controlled Rectifiers - also called Thyristors), rather than straightforward power diodes.

1.4.1

Basic phase-control principles

Figure 4-9 shows a single SCR connected in a simple AC circuit and can be used

to illustrate the basic principles of phase control techniques.

Note: although a half wave rectifier circuit is shown, this circuit has no practical

use in the 7200 equipment but is used only to simplify explanation.

Figure 4-9: Simple half-wave rectifier circuit

Vin ( peak )

Vdc ( mean ) = ---------------------------------------2

Vin(peak)

Vdc(mean)

Input

AC

RL

Max Output

SCR gate permanently

turned ON

Mean

DC

Input

AC

RL

0V

Min. Output

SCR gate permanently

turned OFF

The top diagram shows the situation where the SCR receives a permanent gate

drive signal i.e. the gate is permanently positive with respect to the cathode. In

this condition the SCR passes current during the whole of the input AC waveform

positive half-cycles but blocks the negative half-cycles, as the anode-cathode are

reverse biased during the reverse periods i.e. the SCR is said to be naturally

commutated at the end of each positive half-cycle. This results in a half-wave

rectified voltage being developed across the load resistor, and the SCR can be

seen to be acting in the same manner as a normal rectifier diode. Note that in this

example the mean (d.c.) load voltage is approximately 0.45 times the input peak

voltage, and is shown as a dotted line superimposed on the output waveform.

In the lower diagram the SCR gate drive voltage is removed altogether and under

these circumstances the SCR is permanently turned off during both the positive

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-11

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

and negative half-cycles of the input voltage waveform. In this case the mean

(d.c.) load voltage will of course be zero.

The two conditions described above illustrate how the maximum and minimum load voltages are obtained. The description on the following page shows

how phase control techniques may be used to vary the mean load voltage to any

point between these two extremes.

Figure 4-10: Simple controlled rectifier; showing 45 and 90 output waveforms

SCR conducts only during the shaded

period of the input positive half-cycle

Vdc(max)

Vdc(mean)

Input

AC

RL

0

90

180

270

360

0V

Output waveform at 45 delay

Vdc(mean) is slightly less than the maximum

available dc voltage Vdc(max)

Gate ON

SCR turned ON by gate pulse

Vdc(max)

Vdc(mean)

Input

AC

0

90

180

Gate ON

270

360

RL

0V

Output waveform at 90 delay

Vmean is even less than that achieved

at 45 delay

The examples on the previous page showed that the mean voltage, Vdc(mean),

produced by the simple half-wave rectifier circuit is at a maximum when the SCR

is turned on throughout the whole of its positive (forward biased) half cycle, and

at a minimum when the SCR gate is totally devoid of a drive signal.

When used in a phase-controlled circuit, the mean voltage, Vdc(mean), is varied

between these two extremes by applying the gate drive signal at a variable point

in its forward biased half-cycle as illustrated in Figure 4-10. In the top diagram

the SCR gate is triggered when the input waveform is 45 into its positive half

cycle. The SCR therefore conducts during the period between 45 and 180 only

i.e. it is not turned on between 0 and 45, and is turned off by natural commutation at 180. As shown in the top waveform diagram, under these circumstances

the mean dc voltage Vdc(mean) is slightly less than maximum Vdc(max).

In the lower diagram the SCR gate trigger is delayed by a further 45, to a total of

90, which leads to a corresponding fall in mean output voltage, as shown.

This is the basic principle of a phase-controlled rectifier i.e. controlling the

mean DC voltage between its maximum and minimum limits by controlling the

variable phase delay between the point at which the SCR becomes forward biased

and the application of its gate drive signal.

4-12

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

The terms phase forward and phase back are used in power engineering

fields to describe the action of advancing or retarding the gate drive signal respectively e.g. phasing forward the rectifier implies that the SCR is turned on earlier in its forward conduction cycle and more energy is therefore allowed through

the rectifier, leading to an increased mean DC voltage.

1.4.2

3-phase controlled rectifier

The 7200 series UPS uses a three-phase controlled bridge rectifier, as shown in

Figure 4-11. The circuit is similar to a standard diode bridge rectifier but comprises 6 SCRs in place of the more usual diodes, and each SCR is phase controlled in

the manner described on the previous pages.

Figure 4-11: Basic three-phase bridge rectifier circuit

R+

Shaded area shows R+

SCR forward biased

period

0

Return path period:

S+

T+

90

30

first via S- SCR

then via T- SCR

R+

S+

T+

R (load)

R+

150

S current

T current

Each SCR controls the rectifier conduction during one half cycle period of an

input cycle. Taking the R phase as an example, the top SCR (R+) controls the R

phase positive half cycle, and the lower SCR (R) controls the negative half cycle.

Looking at the R phase positive half cycle (R+) in detail, the three-phase waveform diagram shows that this device is forward-biased only for a 120 period between 30 and 150 of the incoming R phase waveform. This is true of all six

SCRs and means that the bridge output voltage can be controlled over its full

range by controlling the individual SCR conduction angles between 30 and 150.

In practice all six SCRs are controlled such that their conduction phase angles are

identical, therefore the rectifier load current is shared equally between all three

phases.

Note: in the practical 7200 circuit, the load comprises the DC Busbar filter

(smoothing) capacitors, the batteries (when the battery circuit breaker is closed)

and the power inverter section. The rectifier SCRs are thus controlled at the phase

angle necessary to maintain the DC Bus voltage at the required battery charge

voltage while at the same time passing the power demanded by the inverter to

enable it to produce its correct output voltage over a wide load range.

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-13

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

1.5

7200 Series UPS Service Manual

Rectifier construction

The rectifier power components and the static switch power components are assembled on the same heatsink , as illustrated below.

Figure 4-12: Power rectifier construction

Connections to snubber boards

and gate drivers

RECTIFIER 3-Ph

MAINS FEED

STATIC BYPASS

MAINS FEED

Bypass SCRs

Connections to snubber board

and gate driver

Input current CTs

Rectifier SCRs

RECTIFIER OUTPUT

DC Busbar

Gate Driver (trigger)

board

4-14

Snubber board

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Figure 4-13: Rectifier assembly wiring details

Yellow

Red

Yellow

Red

X4

2 1

Yellow

Red

X3

2 1

Yellow

Red

X2

2 1

Yellow

Red

X1

2 1

1 4

2 1

X8

Black

T8

X5

2 1

Black

V6

K2

3

X3

White

Yellow

Red

X6

2 1

G2

Black

G1

K1

X7

G2

4542040W

G1

K1

Black

K2

Black

3

X2

4540043B

V5

White

G2

T7

V4

G1

K1

57

58

59

+

s4-c1.fm5 - Issue 2 Dated 21/08/97

1 4

Black

K2

3

X1

White

From Interface PCB

45900540 (X18)

4-15

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

Depending on the module rating, the rectifier SCRs can take the form of Twinpak or individual devices. As their name suggests, Twinpak devices contain

two SCRs in a single moulded package (See Figure 4-14). As shown, the anode

of one device is internally connected to the cathode of the other, and brought out

to a power connection along with the remaining free anode and cathode. This then

forms a convenient package for the phase controlled rectifier application, with the

a.c. input connected to the common power connection and the DC Bus positive

and negative connections made to the appropriate anode and cathode, as shown.

Separate gate connections are provided, with connection G1 being internally connected to the (+) SCR and G2 to the () SCR.

Where single devices are used, their anode, cathode and gate connections are individually identified.

The gate drive signals take the form of a high frequency modulated waveform 2

which is produced by the Rectifier Logic Board and present whenever the particular SCR is due to be turned on. The gate signal is not required once the device is

turned on, in practice it is applied only for a short burst which avoids excessive

wear on the SCR gate material (see paragraph 3.2 on page 4-39).

The Rectifier Logic Board gate drive signals are connected via ribbon cables to

the Driver Interface Board which contains snubber components designed to

ensure clean rectifier SCR switching, and is mounted on the rectifier assembly

itself. This board applies the drive signals to the SCR gate/cathode via twisted pair

cables note that an auxiliary cathode connection is often provided on the SCR

device for connecting to the negative end of the gate drive cables.

Figure 4-14: Twinpak SCR internal details

AC Input

+VE DC BUS

VE DC BUS

+VE SCR Gate (G1)

4-16

VE SCR Gate (G2)

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

1.6

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Rectifier control system

Figure 4-15: Rectifier control system

Input

Fuses

Rectifier Assembly

Phase

Controlled

Rectifier

Rectifier Logic Board

UPS Logic Board

DC Bus Neg

+

-

Battery

Breaker

Battery

Drive

Interface Bd.

DC Bus Pos

TO INVERTER

SECTION

Battery current sense

Input current sense

Input voltage sense

Input

Choke

Operator Logic Board

DC Busbar

filter capacitors

DC Bus voltage sense

Input mains

Input

Isolator

Alarm Interface Board

(I/O Option)

Remote Alarms

Operator Control

Panel

High Voltage

Interface Board

ON GENERATOR

External Control Options

1.6.1

Control system overview

Figure 4-15 shows the control boards associated with the rectifier control together

with their major control signals.

The Rectifier Logic Board is central to the rectifier control system and is the board

ultimately responsible for generating the rectifier SCR gate drive signals at appropriate phase angles to effect the phase-control techniques described earlier in this

chapter. At its heart is a complex, analogue voltage regulation circuit which uses

the input voltage, input current, DC bus voltage and battery current sense signals

within a series of closed-control loops.

The control system offers the following features, each of which is functionally described in the remainder of this chapter:

charge mode selection i.e. automatic and manually controlled switching

between float and boost charge modes (where applicable).

adjustable input current limit and battery current limit functions.

individually adjustable float, boost, and manual voltage reference levels.

battery temperature compensation which reduces the DC bus voltage progressively if the battery cabinet temperature rises above 25C.

input supply fault detection.

DC overvoltage and undervoltage fault detection.

controlled start/stop features.

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-17

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

1.6.1.1

7200 Series UPS Service Manual

Analogue control signals

Input mains voltage sense

The 3-phase input mains voltage is attenuated on the High Voltage Interface

Board and three line-line proportional sense signals are passed to the Rectifier

Logic Board where they provide zero-crossing reference signals for the phasecontrol timing circuits and are also monitored by input undervoltage and input

phase sequence fault detection circuits.

Input current sense

The rectifier input current is detected by CTs fitted to the power rectifier assembly. The signals produced by these CTs are rectified on the High Voltage Interface

Board and a single input current sense signal, proportional to the total input current, is connected to the input current limit circuit on the Rectifier Logic Board

via the UPS Logic Board.

Note: the sensitivity of this signal is selected by jumpers on the High Voltage Interface Board.

DC Bus (battery) voltage sense

The DC busbar voltage is a function of the rectifier output when the rectifier is

operative, and a function of the battery voltage when the rectifier is inoperative

and the batteries are discharging. This voltage is attenuated on the High Voltage

Interface Board and a proportional DC voltage sense signal is passed to the Rectifier Logic Board where it provides a feedback input to the rectifier voltage regulation control loop.

Battery current sense

Battery current is sensed by a Hall-effect DCCT connected in the battery positive line. The signal produced by the CT is rectified on the High Voltage Interface

Board and a current-proportional signal is connected to the battery current limit

circuit on the Rectifier Logic Board via the UPS Logic Board. The sense signal is

polarity-sensitive i.e. a positive signal indicates a charging current, and vice

versa.

Note: the sensitivity of this signal is selected by jumpers on the High Voltage Interface Board.

1.6.1.2

Digital control signals

Various digital signals are passed between the UPS Logic Board and all the other

boards connect to it. These can broadly be categorised as:

alarm data generated on the Rectifier Logic Board and UPS Logic Board

which are passed to the Operator Control Panel via the Operator Logic

Board also to the Alarms Interface Board (for remote indication) where

fitted.

rectifier metering data generated on the UPS Logic Board and passed to

the Operator Control Panel e.g. input voltage, battery volts current

metering.

control data entered at the Operator Control Panel which is stored by the

UPS Logic Board e.g. boost charge parameters, DC voltage monitor

threshold parameters; manual selection of Rectifier ON/OFF status and

immediate Boost Charge mode.

external control options e.g. remote stop, emergency shutdown, on-generator input current limit.

4-18

s4-c1.fm5 - Issue 2 Dated 21/08/97

7200 Series UPS Service Manual

1.6.2

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

Charge mode selection

Although the float, boost, and manual charge operating voltage levels are individually adjustable by potentiometers on the Rectifier Logic Board, the selected

mode of operation is determined by digital command signals generated by the

UPS Logic Board and applied to the Rectifier Logic Board control logic (See paragraph 2.3.2).

The automatic boost mode parameters (boost voltage level and duration, and

changeover threshold) are entered via the Operator Control Panel and stored in the

UPS Logic Board micro system. Changeover from float charge to either boost or

manual charge modes can also be initiated manually from the Operator Control

Panel at any time.

1.6.3

Input supply fault detection.

The input voltage sense signal is applied to undervoltage and phase sequence

fault detection circuits on the Rectifier Logic Board which shut down the rectifier

and provide error signals to the UPS Logic Board under fault conditions (See paragraph 2.3.6). On the Rectifier Logic Board, led H9 indicates an input undervoltage error and H8 a phase sequence error.

1.6.4

Input current limit

On the Rectifier Logic Board, if the input current sense signal exceeds the current

limit threshold (adjustable between 100%-130%) it phases-back the rectifier, and

reduces the DC busbar voltage to a level which maintains the input current at its

set limit level (See paragraph 2.3.4.2); it also sends an input overload signal to

the UPS Logic Board which initiates an alarm on the Operator Control Panel.

Note: if required, the input current limit level can be automatically reduced by

25% when the UPS is operating on a stand-by generator. This facility is enabled

from the Operator Control Panel and initiated by auxiliary contacts of the On

Generator contactor which are connected to the UPS Logic Board via the External Alarms Board.

Led H6 illuminates on the Rectifier Logic Board when the input current limit circuit is active.

1.6.5

Battery current limit

A battery current limit circuit on the Rectifier Logic Board operates in a similar

manner to the input current limit circuit described above, and phases-back the

rectifier to reduce the DC busbar voltage if the battery charge current exceeds a

predefined current limit threshold (See paragraph 2.3.4.1). It also sends a battery current limit status signal to the UPS Logic Board where it is used by the

software controlled automatic boost charge changeover function.

Led H5 illuminates on the Rectifier Logic Board when the input current limit circuit is active.

1.6.6

Battery temperature compensation

This is an optional control input to the Rectifier Logic Board which progressively

reduces the DC busbar voltage as the battery cabinet temperature rises above

25C and is included to prevent reduced battery life due to the effects of overheating. The temperature is monitored by a thermistor located in the battery cabinet

which produces a temperature-variable signal on the High Voltage Interface

s4-c1.fm5 - Issue 2 Dated 21/08/97

4-19

SECTION 4 - Rectifier Operation & Control

CHAPTER 1 - Rectifier Operating Principles

7200 Series UPS Service Manual

Board which is then passed to the Rectifier Logic Board via the UPS Logic Board

(See paragraph 1.6.6).

1.6.7

Controlled start/stop

The Rectifier Logic Board contains a start/stop control circuit which effectively

turns ON/OFF the rectifier SCR drive signals. This circuit is affected by several

circuits on the Rectifier Logic Board itself (e.g. input undervoltage or phase rotation error) and also by a start/stop signal produced on the UPS Logic Board in response to various monitored system-wide control signals (See paragraph 2.3.6).

1.6.8

DC overvoltage and undervoltage fault detection

The UPS Logic Board uses DC voltage sense signal to detect various critical DC

busbar voltage levels. DC Over/Under voltage conditions instigate a rectifier

shutdown and trip the battery circuit breaker. Other conditions produce a warning

alarm only; such as the Low Voltage which warn the operator of an impending

DC undervoltage (and therefore battery trip) condition.

Note: the operating threshold of these conditions are programmable via the Operator Control Panel.

1.6.9

Battery Circuit Breaker

The battery circuit breaker is manually closed but can be electrically tripped by

the UPS Logic Board. The circuit breaker cannot be initially closed until the DC

bus voltage rises above the DC Undervoltage trip level. Once closed, it will be

tripped by the UPS Logic Board if:

the DC bus voltage rises to the DC Overvoltage level.

the DC bus voltage falls below the DC Undervoltage level (i.e. with the

mains failed and the batteries discharged to their trip level).

the emergency stop circuit is activated.

4-20

s4-c1.fm5 - Issue 2 Dated 21/08/97

Section 4:

Chapter 2 - Rectifier Logic Board

2.1

Chapter overview

This chapter contains a circuit description of the Rectifier Logic Board used

across the whole 7200 Series UPS model range, and should be read in conjunction

with circuit diagram SE-4520074-A (4 pages). Signal annotations shown on the

circuit diagrams are shown in italics in the following text e.g. [IREC>.

2.2

2.2.1

General description

Circuit board functions

The board is responsible for providing the drive signals for the rectifier SCRs at

the appropriate phase angle necessary to produce the required DC Bus (battery

charging) voltage. In so doing, the board monitors the following UPS parameters

via the High Voltage Interface Board and UPS Logic Board (See Figure 4-15):

Input voltage for SCR synchronisation and mains failure detection.

Input current for SCR current protection.

DC Bus (battery) voltage closed-loop voltage regulation.

Battery current for battery protection.

Battery temperature for battery protection.

System control signals from the UPS Logic Board microcontroller (Run/

Stop; Charge mode selection; On Generator; Current limit selection;

soft-start to reduce dc bus capacitors inrush current on start-up).

As part of its control function, the Rectifier Logic Board detects several abnormal

operating conditions and provides the UPS Logic Board control system with the

following error status signals:

2.2.2

Rectifier overload.

Input supply phase rotation error.

Input supply undervoltage.

Rectifier On/Off.

Control power supply failure.

Input/Output connections

The Rectifier Logic Board has four connectors, described below:

X1 Output SCR gate drive signals to Rectifier Driver Interface Board

4542040-W

X2 System control signals to/from the UPS Logic Board 4550007-H

(See Table 4-1).

X3 Control power supplies input from AC-DC Power Supply Board

4503030-M.

X4 Interface to second rectifier control circuit in a 12-pulse rectifier system (optional facility not used in standard module).

s4-c2.fm5 - Issue 3 Dated 09/11/98

4-21

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

7200 Series UPS Service Manual

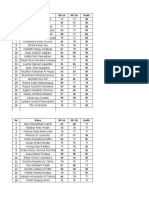

Table 4-1: Connector X2 pinout details

PIN

I/O

1-4

I/O

0V ground reference for digital electronics

5-8

+12V power supply to UPSLB

9-12

-12V power supply to UPSLB

13-14

I/O

Common ground reference for analogue sense inputs

15

VREC_AC Input mains voltage sense signal phases U-W (approx. 15Vp-p)

16

VREC_BA Input mains voltage sense signal phases V-U (approx. 15Vp-p)

17

VREC_CB Input mains voltage sense signal phases W-V (approx. 15Vp-p)

18

IB Battery current sense signal

19

20

Function

Not in use

I

21-23

IREC Rectifier input current sense signal (6 pulses/cycle)

Not in use

24

IREC_T Used in parallel systems only (not available)

25

VB DC Bus (battery) voltage feedback 3Vdc @ 432Vbus

26

T_BAT Battery cabinet temperature sensor 2.98Vdc @ 25C

27

IDC_1 Not used in standard model (12 pulse rectifier option only)

28

IDC_2 Not used in standard model (12 pulse rectifier option only)

29

DB Used in parallel systems only (used for input current sharing control)

30

DB_0 Used in parallel systems only (used for input current sharing control)

31

Not in use

32

OVL_REC Signals rectifier overload error status to UPSLB (Overload = 1)

33

BLK_REC Signals rectifier OFF/ON status to UPSLB (OFF = 1 and ON = 0)

34

SEQ Signals input mains phase sequence error status to UPSLB (Error = 1)

35

IN_LOW Signals low input volts error status to UPSLB (Low Volts = 1)

36

ON-REC Rectifier Run/Stop selection from UPSLB micro (RUN = 1 and STOP = 0)

37

STAT Reduced current limit selection (On generator = 1)

38

REC_A Charge mode selection from UPSLB micro

39

REC_B Charge mode selection from UPSLB micro

40

4-22

Not in use

s4-c2.fm5 - Issue 3 Dated 09/11/98

7200 Series UPS Service Manual

2.2.3

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

Block diagram description

The following illustration shows the Rectifier Logic Board at its most basic functional block diagram level each of the blocks shown is described in more detail

in the remainder of this chapter.

Figure 4-16: Rectifier Logic Board basic block diagram

Mains volts sense

(3-phase) sync signal

Batt I sense

Bus Volts F/B

Volts

Error

Amplifier

DC Control

voltage

DC Reference

voltage

Batt temp sense

Charge Mode

Selection

(UPSLB)

Reference

Voltage

Generator

Bi-directional

Control

(UPSLB)

AC-DC Supply

Start/

Stop

Logic

Rectifier

SCR

Drive

Pulses

Start/Stop

control line

Input I sense

Drive

Pulse

Generator

Fault

Detection

Logic

Power

Supply

Phase control principles

The board regulates the DC busbar (battery charging) voltage using standard

phase controlled techniques i.e. by controlling the point at which each rectifier

SCR is turned on during its forward biased period. This is achieved by detecting

the point at which each SCR becomes forward biased and then applying a variable

time delay between this point and the production of its gate drive pulses. Maximum DC busbar voltage is obtained when the delay is very short, whereupon the

SCRs are allowed to conduct for the whole of their forward biased period. Consequently, as the time delay is increased the SCRs conduct for a shorter period

leading to a reduced DC busbar voltage (See paragraph 1.4).

Drive pulse generator

This block has two major responsibilities. First, it contains a timing circuit which,

in conjunction with the DC control voltage signal, controls the timing of the

SCR drive pulses relative to the mains voltage sense signals (i.e. it uses the mains

sense signals to synchronise each SCRs timing to the relevant forward biased

period of the incoming supply); second, it contains a signal conditioning circuit

which processes the resulting drive pulses to provide a modulated drive waveform.

The DC control voltage directly controls the adopted SCR drive signals time

delay and therefore also the DC busbar voltage i.e. increasing the DC control

voltage reduces the time delay and results in a greater DC busbar voltage.

s4-c2.fm5 - Issue 3 Dated 09/11/98

4-23

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

7200 Series UPS Service Manual

Reference voltage generator

The reference voltage generator provides the volts error amplifier with its DC

reference voltage input. This is seen as a voltage demand signal by the voltage

error amplifier in that it represents the DC busbar target voltage.

The reference voltage generator can produce one of four DC reference voltage

levels equating to float charge, boost charge, manual charge, or test; as requested

by the processor on the UPS Logic Board. Note that although the charge mode is

selected by the UPS Logic Board, the respective DC reference voltage for each

mode is individually adjustable by potentiometers on the Rectifier Logic Board

itself.

An analogue signal proportional to the battery temperature is also applied to the

reference voltage generator and can be used to reduce the DC reference voltage by 1.5Vdc/C as the battery temperature rises between 25C and 35C.

The test mode is used for fault-finding only and allows the DC busbar voltage to

be manually adjusted within the range 0V to 650Vdc.

Volts error amplifier

In the block diagram the primary output of the voltage error amplifier is annotated DC control voltage. This is the signal which directly controls the DC

busbar voltage via the time delay circuit in the drive pulse generator see above.

The magnitude of the DC control voltage is determined by a comparator within

the volts error amplifier which compares the DC busbar voltage feedback signal

with the DC reference voltage produced by the reference voltage generator

block. This basically forms a closed-loop control system, in that the error amplifier constantly modifies the DC control voltage in such a way as to make the rectifier phase-forward or phase-back (as required) to maintain equilibrium between

the DC reference and DC bus feedback signal voltages.

The volts error amplifier also monitors the input current and battery current

sense signals and reduces the DC control voltage if either of these signals reaches a preset current limit threshold. Such an event reduces the DC busbar voltage

to maintain the particular current at its limiting value.

Start/Stop Logic

The start/stop command signal produced by this circuit block is controlled by a

signal produced on the UPS Logic Board in response to its system control logic,

and affects both the volts error amplifier and drive pulse generator blocks.

When the signal is in its stop mode it totally inhibits the drive pulse generators

outputs, effectively closing down the rectifier, and also clamps the DC control

voltage to zero by inhibiting the volts error amplifier output thus demanding

zero DC busbar voltage. When the start/stop signal enters its start mode it immediately releases the inhibit on the drive pulse generator block, enabling the

output drive pulses to be produced; however, the clamp on the volts error amplifier is lifted gradually such that the DC reference voltage is allowed to rise to

its operational level at a controlled rate.

The combined effects of these two operations ensure the power rectifier is stopped

and started in a controlled manner providing an input current walk-in on startup to prevent undesirable input current surges damaging the power components.

This soft-start-controlled walk-in takes approximately 5 seconds to charge the dc

capacitor tray.

4-24

s4-c2.fm5 - Issue 3 Dated 09/11/98

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

The fault detection block output is also connected to the start/stop control line

and has the same effects as the start/stop control signal applied from the UPS

Logic Board. It also applies an input to the start/stop logic block which passes a

fault status signal back to the UPS Logic Board in response to certain detected

fault events hence the start/stop line between the UPS Logic Board and Rectifier

Logic board is shown as bi-directional in the block diagram.

Fault detection logic

This block detects several abnormal/fault conditions on the Rectifier Logic Board

and, depending on the condition will:

provide on-board led indication.

send a fault signal to UPS Logic Board (via the Start/Stop Logic block).

apply a stop condition to the start/stop control line.

Following is a list of the monitored conditions see paragraph 2.3.4.3 for a full

circuit description.

Table 4-2: Monitored faults

Stop

Line?

Signals to

UPSLB

Indication

Battery current limit

No

CHG

H5

Input current limit

No

OVL

H6

Input mains undervoltage

Yes

IN_LOW

BLK_REC

H9

Input mains phase sequence error

Yes

SEQ

BLK_REC

H8

Control power supply monitor

Yes

BLK_REC

H7

Condition

Control power supplies

The Rectifier Logic Board requires regulated 12Vdc supplies for its operation.

These are obtained from the AC-DC Power Supply Board and will be present

whenever the UPS input mains supply (or static bypass supply in a split-bypass

system) is live. An on-board, three-terminal +5V regulator (N14) is driven from

the +12V supply to provide a regulated +5V supply voltage rail.

In the event of a mains failure the AC-DC Power Supply Board will become inactive and the 12V rails are provided by the DC-DC Power Supply Board via the

UPS Logic Board provided the batteries remain connected to the DC busbar (see

section 3 of this manual for details of the control power supplies).

s4-c2.fm5 - Issue 3 Dated 09/11/98

4-25

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

2.3

7200 Series UPS Service Manual

Detailed circuit description

2.3.1

Introduction

The Rectifier Logic Board circuit diagram (SE-4520074-A) comprises 4 sheets.

With reference to the block diagram description in Figure 4-16, the drawings can

broadly be described as follows:

Sheet 1 contains a signal map showing the interconnection of the signals

passing between the other three sheets.

Sheet 2 contains the:

reference voltage generator circuit

battery temperature compensation circuit

volts error amp circuit

battery current limit circuit

input current limit circuit

soft-start control amplifier

Sheet 3 contains the timing portion of the drive pulse generator circuit

together with the mains undervoltage (-15%) detection circuit

Sheet 4 contains the:

signal conditioning portion of the drive pulse generator circuit

start/stop logic and fault detection circuits

control power supplies and its power failure detection circuit

2.3.2

Reference voltage generator

(refer to diagram sheet 2)

This circuit is responsible for providing the volts error amplifier with a DC reference voltage which acts as a voltage demand signal, informing the volts error

amplifier of the desired DC busbar (battery charging) voltage.

Four reference voltages are available: Test, Boost, Float, and Manual, which are

individually set by R19, R20, R21, R22 respectively. These resistors are connected in independent resistor chains which are fed from a stable +5V supply produced by a voltage regulator circuit comprising N6, R23 and R24. If the regulator

is working correctly its Vref input (junction R23/R24) will be at 2.5V.

A multiplexer i.c. (D1) is used to select one of the four reference voltages under

the control of the microprocessor on the UPS Logic Board (REC_A and REC_B

signals). The four pot wiper voltages at the multiplexers inputs 1X thru 4X are

connected to its X output according to the table below:

Table 4-3: Logic table for Q1 (4052)

Mode

REC_A

REC_B

Output X =

Output Y =

Manual

X1

Y1 (H4 Yellow)

Float

X2

Y2 (H3 Green)

Boost

X3

Y3 (H2 Green)

Test

X4

Y4 (H1 Yellow)

Notice that the multiplexers Y channel provides on-board led indication of the

selected charger mode by switching the return path for leds H1-H4.

4-26

s4-c2.fm5 - Issue 3 Dated 09/11/98

7200 Series UPS Service Manual

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

As shown on sheet 4, the [REC_A/B> signals are obtained directly from the UPS

Logic Board via connector X2-38 and X2-39: however, these can be overridden

by links connected to X9 positions 1 & 2. This is a test facility, and enables the

bench/commissioning engineer to select any one of the four charger modes while

undertaking the board set-up procedures. X9 links 1 and 2 must be open during

normal UPS operation.

The selected reference voltage from Q1 (X) (pin13), which can be monitored at

test-point X8-6, is inverted by N4a and applied to the volts error amplifier (N4b)

via R43 (22k) this is the point annotated DC reference voltage in Figure 4-16,

and is approximately 3.0Vdc when the dc bus is at 432Vdc. As the signal is inverted by N4a, the DC reference voltage is always of a negative polarity i.e.

the demanded DC bus voltage increases as the signal goes more negative. As a

guide, this (linear) signal has a sensitivity of around -7.24mV/V(bus demand).

2.3.3

Battery temperature compensation

Note: this is an optional feature which is normally disabled in a standard module

A temperature sense signal, proportional to the battery cabinet temperature, is

connected via terminal X2-26 and jumper X5 (pins 2-3) to amplifier N2c, where

it is differentially summed with a variable voltage set by R121. The output from

N2c is then summed with the reference voltage generator output (See paragraph

2.3.2) at N4a inverting input (test point X8-5).

The affected of the temperature sense signal is to reduce the DC reference voltage by approximately 1.5Vdc per C as the battery temperature increases above

25C. This is done to prevent the batteries from being overcharged and so prolongs battery life.

That is, the temperature signal has no affect until it overcomes the threshold set

by R121, whereupon it progressively reduces the DC busbar voltage as the temperature increases.

The circuit is calibrated by connecting jumper X5 to position (1-2) and adjusting

R121 to obtain 2.98V at test point X5-1 (equates to 25C).

Note: this must be undertaken before the various charge levels are set.

If the facility is not required, leave jumper X5 in position (1-2). This connects the

reference voltage from R121 to both N2c inputs, where they self cancel.

2.3.4

Volts error amplifier

The earlier block diagram description states that the volts error amplifier produces the DC control voltage which ultimately controls the DC busbar voltage.

In practice the volts error amplifier circuit comprises two amplifiers (circuit diagram sheet 2); N4b (which is the true error amplifier) and N3a (which is a unity

gain buffer amplifier). The output signal, analogous to the DC control voltage

signal in the block diagram, is annotated [MOD>.

N3a has five diode-coupled signals connected to its non-inverting input (pin 3)

obtained from:

a fixed dc biasing circuit

the error amplifier (N4b) output via V5

the input current limit detector (N1d) via V3

the battery current limit detector (N1a) via V4

a soft-start signal from the start/stop logic circuit (N4d) via V6

Each of these inputs can affect N3as [MOD> output, as described in detail below.

s4-c2.fm5 - Issue 3 Dated 09/11/98

4-27

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

7200 Series UPS Service Manual

Fixed bias

A fixed bias voltage of approximately +10.5Vdc is applied to N3a pin 3 by the

circuit comprising V1, R60, R55 and R63.

In the absence of all other inputs to N3a the magnitude of this signal would drive

N3a output [MOD>) to +10.5V which is sufficient to cause the drive pulse generator circuit to turn on the rectifier SCRs with minimum delay producing maximum DC busbar voltage. In practice, the inputs to N3a pin 3 from the voltage

error amplifier and current limit circuits therefore control the rectifier by pulling

down, or clamping, the voltage established by the fixed bias circuit: thereby reducing the SCRs conduction to an angle which produces the desired DC busbar

voltage. Such clamping action is achieved by these circuits via their respective

coupling diodes (V3-V6).

Under normal operating conditions the current limit circuits are inactive and

diodes V3 and V4 are reversed biased and have no affect on N3a. The DC control

voltage ([MOD>) is therefore usually controlled by the output from the voltage

error amplifier (N4b) alone.

Error amplifier (N4b)

N4b compares the DC reference voltage produced by Q1/N4a (See paragraph

2.3.2) with a DC busbar voltage feedback signal (approximately 3.0V at

432Vbus) which is connected to X2-25 and fed to the error amplifier via buffer

N2a and R42 (22k).

Note that the DC reference voltage signal has a positive polarity due to the noninverting action of N2a (monitored at X8-1) while the DC reference voltage produced at N4a pin 1 has a negative polarity. The error amp (N4b) therefore compares the magnitude of these two signals differentially.

Error amplifier regulation circuit action

If the DC busbar falls below its required voltage the DC busbar feedback signal

will be lower in amplitude than the DC reference voltage and the voltage error

amplifier output will ramp in a positive direction, lifting the clamp (by V5) on

N3a non-inverting input. This allows the DC control voltage ([MOD>) to increase so raising the DC Busbar voltage. This action will take place until the

DC busbar feedback signal increases to a level equal to the DC reference voltage at which point the output from N4b output will remain constant and cease

demanding an increase in DC busbar voltage.

If the DC busbar rises above the required voltage the circuit will respond with the

opposite polarity i.e. if the DC busbar feedback signal is higher than the DC

reference voltage then N4b output will decrease and further clamp the input to

N31 with a resulting reduction in the DC control voltage ([MOD>).

Due to the presence of C28 in its feedback path, the volts error amplifier (N4b)

integrates any amplitude difference between its DC busbar feedback (+) and

DC reference voltage (-) input signals, and so affects the rectifiers regulation

speed of response. The circuit response can be selected by jumper X6 which

should be positioned (1-2) in modules rated at 60kVA and below (faster response), and (2-3) in modules rated at 80kVA and above.

4-28

s4-c2.fm5 - Issue 3 Dated 09/11/98

7200 Series UPS Service Manual

2.3.4.1

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

Battery current limit

Battery current sense signal

Battery current is measured by a Hall-effect dc current sensor which produces a

dc voltage proportional to the battery current. This voltage is calibrated on the

High Voltage Interface Board (see paragraph 2.3.22 on page 7-11) and then

passes through the UPS Logic Board to enter the Rectifier Logic Board at X2-18

where it is buffered by N1c. The resulting sense signal appears as a positive voltage at test point X8-2.

Battery current limit circuit operation

From test point X8-2 the battery current sense signal is connected to a level detector circuit (N1a) whose output pin 1 changes from logic high to low if the battery current exceeds the level set by R18. When this occurs it clamps the input to

the volts error summing amplifier (N3a), via V4, reducing the DC control voltage ([MOD>) which in turn reduces the DC busbar voltage thereby reducing the

battery charge current. The reference voltage set by R18 can be monitored at test

point X8-8 and can be in the range 0V to -5V. This range is determined by a 5V

regulator circuit, based on N5, connected between the 0V and -12V power rails.

If the regulator circuit is operating correctly the junction of R12 and R13 will be

held at -2.5V. R18 is normally adjusted to obtain 0.1Vdc per amp of required current limit at X8-8 for the 30kVA, 40kVA and 60kVA models respectively.

This circuit is dynamic in its operation i.e. as the DC busbar voltage reduces so

too does the battery charge current. Ultimately, the circuit operation reduces the

DC busbar voltage to a level which sustains the battery charge current at the level

set by R18.

In practice the battery current limit circuit is only likely to become active when

the UPS input mains supply returns from a prolonged outage: whereupon the

heavily discharged batteries are certain to demand a high initial recharge current.

Under these circumstances the DC busbar voltage is initially restricted but will

gradually increase to its nominal value while maintaining the battery current at its

set limit level as the batteries regain their charge.

Battery current limit indication

Led H5 illuminates when the battery current limit circuit is active. The indication

circuit operates by detecting whether or not V4 is turned on. When V4 is conducting, the input to N3 pin 6 via R56 is approximately -0.6V with respect to the signal

applied via R57 to pin 5. These conditions force N3 pin 7 to switch high which

illuminates H5 and produce a logic high [CHG> signal, which is connected to the

UPS Logic Board, via X2-23, to inform it of the battery current limit status.

2.3.4.2

Input current limit

Input current sense signal

The UPS input current is sensed by current transformers (CTs) fitted to the rectifier assembly input R and T lines. The CTs outputs are rectified and normalised

on the High Voltage Interface Board (see paragraph 2.3.18 on page 7-10) and the

resulting dc voltage, which is proportional to the input current, is connected via

the UPS Logic Board to the Rectifier Logic Board X2-20. From here the sense

signal is buffered by N1b and can be measured as a positive voltage at test point

X8-3.

s4-c2.fm5 - Issue 3 Dated 09/11/98

4-29

SECTION 4 - Rectifier Operation & Control

CHAPTER 2 - Rectifier Logic Board

7200 Series UPS Service Manual

Input current limit circuit operation

From test point X8-3 the input current sense signal is connected to a level detector

circuit (N1d) whose output pin 14 changes from logic high to low if the input current exceeds the level set by R17. When this occurs it clamps the input to the

volts error summing amplifier (N3a), via V3, reducing the DC control voltage

([MOD>) which in turn reduces the DC busbar voltage thereby reducing the input

current. The reference voltage set by R17 can be monitored at test point X8-7 and

can be in the range -0.5V to -5V. This range is determined by a 5V regulator circuit, based on N5, as described above for the battery current limit circuit. In practice R17 is adjusted to obtain 0.8Vdc at test point X8-7 in a 30kVA model; this is

increased to 1.2Vdc for 40kVA and 1.6Vdc for 60kVA models.

This circuit is dynamic in its operation i.e. as the DC busbar voltage reduces so