Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Proyecto VHDL Mediante GAL22V10D (Control de Motor y Leds)

Caricato da

Doming de la CruzDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Proyecto VHDL Mediante GAL22V10D (Control de Motor y Leds)

Caricato da

Doming de la CruzCopyright:

Formati disponibili

UNIVERSIDAD

DEL CALLAO

NACIONAL

FACULTAD DE INGENIERIA ELCTRICA Y

ELECTRNICA

ESCUELA PROFECIONAL DE INGENIERIA

ELECTRNICA

ASIGNATURA:

computadoras

Arquitectura de

Laboratorio -92G

CODIGO

12132203

76

12132100

12

SEMESTRE ACADEMICO: 2014-B

TEMA:

PROYECTO VHDL

PROFESOR:

Cucho Mendoza Zenn

APELLIDOS/NOM

BRES

DE

LA

CRUZ

CASTRO

DOMINGO CESAR

HERRERA ESCATE

HAROLD ANDRE

PREVIO(

6)

P_LAB(

8)

SUST(

4)

TAREAS(

2)

NOT

A

Proyecto de VHDL por medio del GAL 22V10D

I.

Introduccin:

GAL (Generic Array Logic), en espaol Arreglo Lgico Genrico, son un

tipo de circuito integrado, de marca registrada por Lattice

Semiconductor, que ha sido diseados con el propsito de sustituir a

la mayora de las PAL, manteniendo la compatibilidad de sus

terminales.

Utiliza una matriz de memoria EEPROM en lugar por lo que se puede

programar varias veces.

Un GAL en su forma bsica es un PLD con una matriz AND

reprogramable, una matriz OR fija y una lgica de salida programable

mediante una macrocelda. Esta estructura permite implementar

cualquier funcin lgica como suma de productos con un nmero de

trminos definido. En los PLDs no reprogramables la sntesis de las

ecuaciones lgicas se realiza mediante quema de fusibles en cada

punto de interseccin de los pines de entrada con las compuertas. En

el caso de un GAL es bsicamente la misma idea pero en vez de estar

formada por una red de conductores ordenados en filas y columnas

en las que en cada punto de interseccin hay un fusible, el fusible se

reemplaza por una celda CMOS elctricamente borrable (EECMOS).

Mediante la programacin se activa o desactiva cada celda EECMOS y

se puede aplicar cualquier combinacin de variables de entrada, o sus

complementos, a una compuerta AND para generar cualquier

operacin producto que se desee. Una celda activada conecta su

correspondiente interseccin de fila y columna, y una celda

desactivada desconecta la interseccin. Las celdas se pueden borrar y

reprogramar elctricamente.

II.

Objetivos:

-

Programar en lenguaje VHDL y controlar un circuito externo.

Usar GAL22v10d para controlar un circuito por medio del lenguaje

VHDL.

Controlar un motor y leds por medio del lenguaje VHDL y la

interfaz de Proteus Isis.

III.

Funcionamiento:

La manera en la que opera nuestro proyecto es la siguiente:

Tenemos 3 pulsadores, uno para el sentido Horario, uno para el

sentido Antihorario y uno ms que es el pulsador para detener el giro,

llamado tambin stop.

Para esto tenemos nuestra programacin hecha previamente en el

VHDL, la cual ser mostrada en breve, el programa ejecutable (.jed) la

cual adquirimos usando el programa ispleverclasic siguiendo una

serie de pasos mostrados a continuacin, es as que el GAL22V10D

puede controlar a los dems dispositivos segn nuestra

programacin. Para resumir esta parte, usando nuestra programacin

en VHDL controlamos varios dispositivos mediante un solo integrado,

GAL22V10D.

Siguiendo con el proceso, el GAL22V10D permite aprovechar las

ventajas del motor para hacerlo girar, ya sea en sentido horario o

antihorario dependiendo del pulsador que activemos mientras dura el

proceso o detenerlo si es deseado, mediante el pulsador de stop.

Se agregaron una serie de leds, como demostracin del sentido en el

cual va el motor, esto es simplemente esttico, pero permite

visualizar de una mejor manera el giro del motor DC.

IV.

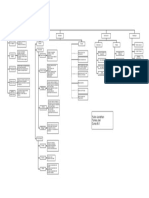

Diagrama de flujo:

Proyecto VHDL con

motor y leds

Cargamos la programacin

en .jed en el GAL22V10D

Apretamos cualquiera de

los pulsadores para el giro

del motor

Antihorario

Horario

V.

El motor gira en sentido

horario y los leds se

encienden indicando el

sentido de giro

Programacin en VHDL:

El motor gira en sentido

antihorario y los leds se

encienden indicando el

sentido de giro

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity motorled is

port( P: in std_logic_vector(2 downto 0);

S: out std_logic_vector(1 downto 0);

P1: in std_logic_VECTOR(2 DOWNTO 0);

C: out std_logic_vector(2 downto 0);

V: out std_logic_vector(2 downto 0)

end motorled ;

architecture motorled of motorled is

signal B: std_logic_vector (1 downto 0);

begin

------------DECLARANDO SIGNAL B------------with P select

);

B <= "01" when "011",

"10" when "101",

"11" when "110",

"00" when others;

------------VALORES DE GIRO DEL MOTOR-------process(B)

begin

if B="01" then S <= "10" ;

end if;

if B="10" then S <= "01" ;

end if;

if B="11" then S <= "00" ;

end if;

if B="00" then S <= "00" ;

end if;

end process;

-----------------PARTE DE LOS LEDS-----------------------with P select

C <= "101" when "011",

"110" when "101",

"100" when others;

----------PARTE DE VELOCIDAD

with P1 select

V <= "001" when "011",

"010" when "101",

"100" when others;

end motorled;

En imgenes:

USANDO EL ISPLEVER CLASSIC:

Para comvertir nuestro archivo a formato .jed para que lo podramos abrir en

proteus seguiremos los siguiente pasos:

Crear archivo en la carpeta donde se encuentrra el proyecto en VHDL:

Seleccionar el GAL 22V10D para su uso en el ISIS:

Abrir el archivo VHDL creado con la programacin a usar:

Una ves creado compilar el trabajo de la siguiente forma:

Realizar el mapa de fusibles de la siguiente manera:

Una ves seguido los pasos abrimos y observamos la asignacin de PINES en

el CHIP REPORT

VI. Simulacin en Proteus:

VII. Observaciones y Conclusiones:

Nuestro programa tiene un diseo agradable a la vista el cual

permite escoger un sentido de giro para un motor y asimismo

detenerlo si es deseado, todo por medio de pulsadores que sirven

como selectores mediante la ejecucin de nuestra programacin.

Concluimos del laboratorio que usando VHDL y Proteus podemos

simular circuitos como PLD con una programacin la cual es mas

til que hacerlo de la manera clsica con solo compuertas e

integrados ya que suplantamos todo ello por una programacin la

cual controla el proceso del circuito dndonos la ventaje de

portabilidad y menos gasto para el proyecto.

Es posible desarrollar un programa en lenguaje VHDL en Quartus II

y simularlo en Proteus, sin embargo no es suficiente estos 2

programas para desarrollarlo.

El GAL utilizado 22V10 es muy til y verstil, pues podemos

declarar variables de entradas y salidas a preferencia y gusto del

usuario.

Es mucho ms prctico que el PPI pues se requieren menos

componentes y es ms sencilla la declaracin de puertos.

Durante el desarrollo de ste programa tuvimos inconvenientes

como el uso de un programa extra para crear el archivo .jed que

sirviera de base para nuestro proyecto en Proteus.

Se us el ispLever Classic 1.8 con el cual pudimos hacer uso de

nuestra programacin dentro del 22V10.

Trabajamos bajo el mismo concepto de nuestro proyecto PPI, es

decir, logramos hacer el mismo trabajo, pero sta vez empleando

lo aprendido en la 2da parte del semestre.

Potrebbero piacerti anche

- Latches y Mult - UNLaMDocumento27 pagineLatches y Mult - UNLaManon_729877093Nessuna valutazione finora

- Touch Con PICDocumento8 pagineTouch Con PICLucho AngelNessuna valutazione finora

- Torno G71 DesbasteDocumento5 pagineTorno G71 DesbasteLima Garcia JuanNessuna valutazione finora

- Proyecto Tacometro 2.Documento109 pagineProyecto Tacometro 2.Carlos RiveraNessuna valutazione finora

- Sumador RestadorDocumento4 pagineSumador RestadorMiguel Angel Lucas SorianoNessuna valutazione finora

- Tema 6 Teclado Digital DecimalDocumento4 pagineTema 6 Teclado Digital Decimal2mercedesNessuna valutazione finora

- Practica 1 DSMDocumento6 paginePractica 1 DSMLuis Eduardo AndradeNessuna valutazione finora

- Voltímetro USB NeoTeoDocumento18 pagineVoltímetro USB NeoTeovevi5860Nessuna valutazione finora

- td3 PDFDocumento226 paginetd3 PDFTecnicasdigitales3 UtnNessuna valutazione finora

- MicrocontroladorDocumento5 pagineMicrocontroladorprofe321Nessuna valutazione finora

- Contador Rapidos s7 200Documento37 pagineContador Rapidos s7 200Elvis Torres QuispeNessuna valutazione finora

- 2.2 Fibra - PEN CLEANING (One Click)Documento15 pagine2.2 Fibra - PEN CLEANING (One Click)provenser electricNessuna valutazione finora

- Final 1Documento3 pagineFinal 1Esmeralda Quispe LeónNessuna valutazione finora

- Dokumen - Tips - Tipos de Arranques de Motores y EsquemasDocumento21 pagineDokumen - Tips - Tipos de Arranques de Motores y EsquemasOsvaldo Leonardo LetowskiNessuna valutazione finora

- Ci MM74C922Documento9 pagineCi MM74C922JOSE FRANCIA ZORRILLANessuna valutazione finora

- Programacion en CUPLDocumento11 pagineProgramacion en CUPLapi-2752733683% (6)

- Códigos VHDLDocumento3 pagineCódigos VHDLFrida Sofía Andrade SierraNessuna valutazione finora

- Multiplexor BCD/HEXDocumento7 pagineMultiplexor BCD/HEXJavier GzalNessuna valutazione finora

- Practica3 Auto IncreibleDocumento4 paginePractica3 Auto Increibleroberto hidalgoNessuna valutazione finora

- Informe de Proyecto FinalDocumento6 pagineInforme de Proyecto FinalByron P. Villarreal100% (1)

- Manual de Prácticas Pic 16f688Documento15 pagineManual de Prácticas Pic 16f688txusmaster_hackNessuna valutazione finora

- Funcionamiento LCD para FPGADocumento4 pagineFuncionamiento LCD para FPGAMichael ßermeoNessuna valutazione finora

- Microcontroladores IntroduccionDocumento29 pagineMicrocontroladores IntroduccionDeysi Leonela100% (1)

- 3 Progra Del Microcontrolador en Ensamblador (3) (2792)Documento32 pagine3 Progra Del Microcontrolador en Ensamblador (3) (2792)Alfredo Pacheco ZapataNessuna valutazione finora

- PulsosDocumento14 paginePulsosGordo XploNessuna valutazione finora

- Linea de Producción CosimirDocumento15 pagineLinea de Producción CosimirIngGuillermoVenturaNessuna valutazione finora

- Semáforo Con Un PIC16F628Documento3 pagineSemáforo Con Un PIC16F628Saul RamirezNessuna valutazione finora

- Informe-Practica de Digitales (Codificadores BDC)Documento7 pagineInforme-Practica de Digitales (Codificadores BDC)IvanGomezGNessuna valutazione finora

- Generador de Ondas Cuadradas para ArduinoDocumento2 pagineGenerador de Ondas Cuadradas para ArduinoPierDonneeNessuna valutazione finora

- Tutorial de CircuitMaker 6Documento7 pagineTutorial de CircuitMaker 6Jesus Revollo VargasNessuna valutazione finora

- Primera y Segunda Derivada en LabviewDocumento7 paginePrimera y Segunda Derivada en LabviewLuis SanchezNessuna valutazione finora

- 4 Compilar Con MplabX en Lenguaje C Usando XC16 y Simular en Proteus 8.5Documento22 pagine4 Compilar Con MplabX en Lenguaje C Usando XC16 y Simular en Proteus 8.5ronaldvNessuna valutazione finora

- VHDL y FpgaDocumento33 pagineVHDL y FpgaSting Marquez VargasNessuna valutazione finora

- Practica6 Organización y Arquitectura de ComputadorasDocumento17 paginePractica6 Organización y Arquitectura de ComputadorasEduardo RojasNessuna valutazione finora

- Sustentacion Compensador Adelanto-Atraso g1Documento17 pagineSustentacion Compensador Adelanto-Atraso g1Carlos LópezNessuna valutazione finora

- Práctica 4 Electrónica Analógica SujetadoresDocumento7 paginePráctica 4 Electrónica Analógica SujetadoresSalva CervantesNessuna valutazione finora

- Lab de Electronica 4Documento7 pagineLab de Electronica 4Gnzlz KarlaNessuna valutazione finora

- Digitales 4Documento37 pagineDigitales 4Alissa DimasNessuna valutazione finora

- 1 - Especificaciones MódulosDocumento13 pagine1 - Especificaciones MódulosElmer RchNessuna valutazione finora

- Practica 2 Lab DSMDocumento12 paginePractica 2 Lab DSMAlex ToledoNessuna valutazione finora

- Semaforo DigitalDocumento4 pagineSemaforo Digitalithan alvarezNessuna valutazione finora

- Diagrama de BounceDocumento13 pagineDiagrama de BounceDaniel Alcazar HernandazNessuna valutazione finora

- Practicas Ep2 2018 AviDocumento15 paginePracticas Ep2 2018 AviSindel Parra GomoraNessuna valutazione finora

- Proyecto de Programables Control de TemperaturaDocumento49 pagineProyecto de Programables Control de TemperaturaCarlos ArriazaNessuna valutazione finora

- Informe Final 4 - Ci 74ls194Documento8 pagineInforme Final 4 - Ci 74ls194edsonygisellaNessuna valutazione finora

- Motor GiroDocumento3 pagineMotor GiroJoha BermudezNessuna valutazione finora

- Practica 2 DSMDocumento6 paginePractica 2 DSMLuis Eduardo AndradeNessuna valutazione finora

- LABORATORIO 05 - 2 Contadores AsincronosDocumento5 pagineLABORATORIO 05 - 2 Contadores AsincronosDarwin YoverdNessuna valutazione finora

- Conversor Analogo Digital 0804Documento8 pagineConversor Analogo Digital 0804Luis Fernando Merma DurandNessuna valutazione finora

- SIRIUS Arrancadores DirectosDocumento8 pagineSIRIUS Arrancadores DirectosChapo GuzmanNessuna valutazione finora

- Arduino y Matlab (Funcion de Transferencia) (Reparado)Documento4 pagineArduino y Matlab (Funcion de Transferencia) (Reparado)Alejandro mora lopezNessuna valutazione finora

- El KlystronDocumento7 pagineEl KlystronJose Gutierrez0% (2)

- Practica 7 Transistor-BJT-OsciladorDocumento10 paginePractica 7 Transistor-BJT-OsciladorRaul bandalaNessuna valutazione finora

- Informe Programador Pic Usb 1Documento21 pagineInforme Programador Pic Usb 1JalexanderhgNessuna valutazione finora

- Multiplicador de Voltaje LabDocumento8 pagineMultiplicador de Voltaje LabCarlos Sarmiento MelgarejoNessuna valutazione finora

- Reductor de Frecuencia PDFDocumento8 pagineReductor de Frecuencia PDFAlejandro AlvarezNessuna valutazione finora

- S1D02Documento8 pagineS1D02jochato2726Nessuna valutazione finora

- Semaforo Digital - JPRRDocumento18 pagineSemaforo Digital - JPRRjeanNessuna valutazione finora

- Trabajo Del Curso - TR1Documento8 pagineTrabajo Del Curso - TR1Piero PinedNessuna valutazione finora

- Informe 1Documento14 pagineInforme 1Pato BautistaNessuna valutazione finora

- Practica de Control DigitalDocumento22 paginePractica de Control Digitalg10382776Nessuna valutazione finora

- Criterios de Oscilacion FirmeDocumento3 pagineCriterios de Oscilacion FirmeDoming de la Cruz0% (1)

- Tarea AcademicaDocumento8 pagineTarea AcademicaDoming de la CruzNessuna valutazione finora

- Proyecto PPI Mediante Emu8086 (Control de Motor y Leds)Documento14 pagineProyecto PPI Mediante Emu8086 (Control de Motor y Leds)Doming de la Cruz100% (1)

- Informe Final de Circuitos Electrónicos IIDocumento5 pagineInforme Final de Circuitos Electrónicos IIDoming de la CruzNessuna valutazione finora

- Medidor de PulsoDocumento7 pagineMedidor de PulsoDoming de la CruzNessuna valutazione finora

- FET Laboratorio N 4Documento4 pagineFET Laboratorio N 4Doming de la CruzNessuna valutazione finora

- Aplicaciones de Diodo TunelDocumento1 paginaAplicaciones de Diodo TunelDoming de la CruzNessuna valutazione finora

- Fanuc Basico PDFDocumento218 pagineFanuc Basico PDFPrudencio Lopez LopezNessuna valutazione finora

- Tema 1. - PunterosDocumento33 pagineTema 1. - Punterosgerar2005Nessuna valutazione finora

- Habilidades Digitales y OfimáticaDocumento127 pagineHabilidades Digitales y OfimáticaTatiana López AlvearNessuna valutazione finora

- Regla CoddDocumento2 pagineRegla CoddTsubasa HebiNessuna valutazione finora

- Practica 1 y 2 HTML BasicoDocumento3 paginePractica 1 y 2 HTML BasicoMartin Uziel Franco ArteagaNessuna valutazione finora

- Fundamentos en La Implementación de Componentes FrontDocumento3 pagineFundamentos en La Implementación de Componentes FrontJohana moralesNessuna valutazione finora

- Tipos de Memorias PDFDocumento18 pagineTipos de Memorias PDFRafael MonzonNessuna valutazione finora

- Conecccion PLC Dvp10sx-11r de Deltal EthernetDocumento4 pagineConecccion PLC Dvp10sx-11r de Deltal EthernetRicardo DiazNessuna valutazione finora

- CRONOGRAMA DIGITACIôNDocumento16 pagineCRONOGRAMA DIGITACIôNKiara2525100% (1)

- Antologia Informatica 2022 PDFDocumento140 pagineAntologia Informatica 2022 PDFYoung Dance ProjectNessuna valutazione finora

- 2.4 Perifericos InternosDocumento18 pagine2.4 Perifericos Internosomarale_borre0% (1)

- Tema 5 - Diseño de ClasesDocumento94 pagineTema 5 - Diseño de ClasesGana CoinsNessuna valutazione finora

- InformáticaDocumento173 pagineInformáticafreddy joseNessuna valutazione finora

- Examen Final Del Capítulo 1Documento8 pagineExamen Final Del Capítulo 1sofimachNessuna valutazione finora

- Netbeans y Diagrama de FlujoDocumento9 pagineNetbeans y Diagrama de FlujoRonald Salinas soriaNessuna valutazione finora

- Valeria Becerra Sistema de ArchivosDocumento18 pagineValeria Becerra Sistema de ArchivosAlexa BecerraNessuna valutazione finora

- Práctica #6. Introducción A Los Autómatas ProgramablesDocumento19 paginePráctica #6. Introducción A Los Autómatas ProgramablesDaniel David Mantilla QuinteroNessuna valutazione finora

- Formato F-5 (Solicitd PC) 2020Documento1 paginaFormato F-5 (Solicitd PC) 2020MauricioD.MéndezNessuna valutazione finora

- Arquitectura Cliente-ServidorDocumento3 pagineArquitectura Cliente-ServidorAlejandro AcostaNessuna valutazione finora

- Leccion 6Documento3 pagineLeccion 6Sergio SanchezNessuna valutazione finora

- 1940 Primeras ComputadorasDocumento2 pagine1940 Primeras ComputadorasMiguel Enrique Junior Zavaleta RojasNessuna valutazione finora

- Fundamentos de Las Redes y ComunicacionesDocumento31 pagineFundamentos de Las Redes y ComunicacionesConejillo de indias100% (1)

- GET Leer Datos de Una CPU RemotaDocumento6 pagineGET Leer Datos de Una CPU RemotaHenry Wladimir Cóndor SinchiguanoNessuna valutazione finora

- Herramientas de Hirens BootDocumento28 pagineHerramientas de Hirens BootLeonardo Llanos PradaNessuna valutazione finora

- 4 Fundamentos de AplicacionesDocumento77 pagine4 Fundamentos de AplicacionesJesus MovilesNessuna valutazione finora

- Zape EdtDocumento1 paginaZape EdtMaycol Alexander Piza MenendezNessuna valutazione finora

- 8 - Representación de Números Con Signo y Formato Estándar - IEEEDocumento12 pagine8 - Representación de Números Con Signo y Formato Estándar - IEEEant003Nessuna valutazione finora

- EVALUACIÓN CONTINUA 2 - RedesDocumento2 pagineEVALUACIÓN CONTINUA 2 - RedesAlexis RuestasNessuna valutazione finora

- Actividad 7 - Edison ChiluizaDocumento11 pagineActividad 7 - Edison Chiluizajoselyn tigreNessuna valutazione finora

- Pantalla de Fallos SP4000 PDFDocumento1 paginaPantalla de Fallos SP4000 PDFJoAn RoYuNessuna valutazione finora