Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Review Review Technology Technology: Advancements Advancements

Caricato da

Fatih KarabacakDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Review Review Technology Technology: Advancements Advancements

Caricato da

Fatih KarabacakCopyright:

Formati disponibili

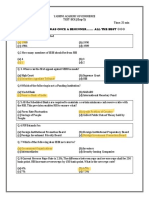

CENG 5534 : Advanced Digital System Design

Review

Technology

Design Methodology:

Top--down approach: Specs., constraints, Behavioral, RTL, Structural

Top

Tradeoffs: HW/SW, Comb./Seq., ...

HDL Constructs:

Entity: entity declaration, architecture body

VHDL data: identifiers, objects, classes, types

Statements: PROCESS, assignment, IFIF-THENTHEN-ELSE, WAIT, LOOP

Synthesis,

y

,

Portability, compatibility, implementation,

Chip density and performance

Microprocessors improving in performance between 1.5 and 2

Learning

Simulation:

, costs

times per year

Styles of description:

Advancements

Cycle, timing,

Today:: Combinational Logic (concurrent and sequential statements)

Today

Paradigms, general algorithms

Technologies, specific algorithms, applications

Technology changes, principles remain

Specific Objectives

1.

Outline

Combinational Logic - Concurrent Statements

Write functionally correct and well

well--documented VHDL

synthesis,

y

, of anyy

code,, intended for either simulation or synthesis

combinational or sequential logic design.

2.

Define and use the three major styles of writing VHDL

code ((structural

structural,, dataflow,

dataflow, and behavioral).

behavioral).

3

3.

Write VHDL code that can be implemented efficiently in

a given technology device.

Boolean Equations

Logical and Relational Operators

With--SelectWith

Select-When, WhenWhen-Else

Component Instantiations

Combinational Logic - Sequential Statements

If--ThenIf

Then-Else, Case

Case--When

FIFO Example

3

Combinational Logic

CENG 5534 : Advanced Digital System Design

Combinational and Sequential Logic

In

L o gic

In

L o gic

Combinational and Sequential Logic

Out

Out

C ir c u i t

Both implemented with concurrent / sequential statements

C i r c u it

State

( a ) C o m b i n a ti o n a l

O u t p u t = f( I n )

Combinational Logic

Outputs are functions of current

inputs only

No memory

Example: gates, multiplexers,

multiplexers,

decoders,, ALUs

decoders

Concurrent statements in architecture, outside processes;

( b ) S e q u en tial

Dataflow

and Structural styles

O u t p u t = f (I n , P r e v io u s I n )

Sequential Logic

O t t are ffunctions

ti

off currentt and

d

Outputs

past inputs

Uses memory (flip(flip-flops, RAM, ROM)

Example: state machines,

machines, counters,

counters,

shift registers

registers,, FIFOs

Sequential statements inside processes;

Behavioral

style

Combinational Logic - Concurrent

Statements

Combinational Logic Technology

Static

Conventional CMOS

Ratioed Logic

Transmission Gate

Concurrent Statements

Boolean Equations

Logical

g

and Relational Operators

p

Dynamic

Domino

np--CMOS

np

With

With-SelectSelect-When

When,

,

When

When-Else

Component Instantiations

Boolean Equations

Use in both concurrent and sequential signal assignments <=

Use in sequential variable assignments :=

Cumbersome for array

y operations

p

Often good for simplesimple-toto-complex scalar operations

Examples:

asignal <= bsig OR csig

csig;

;

avariable := bvar AND cvar

cvar;

;

7

Combinational Logic

CENG 5534 : Advanced Digital System Design

Logical Operators

With--Select

With

Select--When Statement

AND, OR, XOR, NAND, NOR, XNOR, NOT

Also called a selected signal assignment statement

std_ulogic, and their 1D

For types: bit, boolean, std_logic, std_ulogic,

Concurrent statement

arrays

Similar to a sequential CASE statement

NOT has higher precedence; others have equal, lower precedence

Select one of several values to drive an output signal

Parentheses usually required for multilevel equations

Examples:

Selection based on all possible values of a selector expression

Syntax:

z <= a AND b AND c OR d NAND e OR NOT f;

Eq i alent

Equivalent:

z <= ((((a AND b) AND c) OR d) NAND e) OR (NOT f);

Not equivalent, but usual algebraic meaning:

z <= (a AND b AND c) OR (d NAND e) OR (NOT f);

WITH selector_expression

selector expression

out_signal <=

value1

value2

...

value9

SELECT

WHEN choice1

choice1,

,

WHEN choice2

choice2,

,

WHEN choice9

choice9;

;

With--Select

With

Select--When Statement

With--Select

With

Select--When Statement

Selector expression

-- 2-toto-1 multiplexer

WITH addsub SELECT

opcode <= add WHEN 0,

sub WHEN 1;

Signal name, or expression with signal names

Choices

Match type of selector

Set of choices must be mutually exclusive and all inclusive

Number, string, expression, choice1 | choice2, OTHERS

Values

Anything normally legal on right side of concurrent signal assignment

Statement synthesizes to an NN-bit M-to

to--1 multiplexer

Values are data inputs

Selector and choices form select input codes

Out_signal is the data output

11

Combinational Logic

WITH(a AND b) SELECT

WITH(a

out <=

1011 WHEN 00 | 01,

11-11

--

WHEN 1Z,

x OR y WHEN 11,

0000 WHEN OTHERS

OTHERS;

;

WITH myint SELECT

outvec <= X1F WHEN 35,

X27 WHEN 2 TO 5,

XFF WHEN OTHERS

OTHERS;

;

Synthesis result

10

12

CENG 5534 : Advanced Digital System Design

When--Else Statement

When

When--Else Statement

When

Conditions

Also called a conditional signal assignment statement

Concurrent statement

Boolean expressions

Similar to a sequential IFIF-THEN

THEN--ELSE statement

S t off conditions

Set

diti

NOT necessarily

il mutually

t ll exclusive

l i or allll inclusive

i l i

First true condition determines the value assigned

Last value assigned if all conditions FALSE

Select one of several values to drive an output signal

Selection based on first condition that is TRUE

Syntax:

Synthesis results

out signal <=

out_signal

value1 WHEN condition1 ELSE

value2 WHEN condition2 ELSE

value9;

value9

;

If conditions are mutually exclusive, it synthesizes to a simple

multiplexer like the WITHWITH-SELECT

SELECT--WHEN statement

Otherwise, it synthesizes to a more complex priority encoder,

encoder,

with the first condition having highest priority

13

When--Else Statement

When

opcode <=

out <=

Combining Bits into Vectors

Aggregate

add WHEN (addsub =

0

0) ELSE

sub WHEN (addsub =

1

1) ELSE

nop;

nop

;

1011

1011

WHEN (a =

0

0) ELSE

11

11---

WHEN (b =

0

0) ELSE

x OR y WHEN (a AND b)=

)=1

1 ELSE

0000

0000;

;

-- 4-to

to-2 priority encoder

outcode <= 11

11

WHEN in3 =

=1

1

10

10

WHEN in2 =

=1

1

01

01

WHEN in1 =

=1

1

00

00

WHEN in0 =

=1

1

00

00;

;

List of compatible bits that can be assigned to a vector

Can

C appear on right

i ht side

id off signal

i

l assignment

i

t

Example: xvector <= (a, b, c, d)

Concatenation

ELSE

ELSE

ELSE

ELSE

15

Combinational Logic

14

Concatenate compatible bits into a vector

Can appear on right side of signal assignment

Can be used in a WHEN condition or IF condition

Example: xvector <= (a & b & c & d)

16

CENG 5534 : Advanced Digital System Design

Dont Cares in Conditions

Relational Operators in Conditions

Conditions with dont care values - should not be used in IF and

WHEN--ELSE statements

WHEN

Theyy are literallyy compared

p

to the - value in simulation

They always evaluate to FALSE for synthesis

Example: IF a = 0-0--

THEN

Test equality and inequality (=

(= and /=

/=))

Test relative ordering or magnitude (<

(<, <=

<=,, >, >=

>=))

Returns boolean TRUE or FALSE

Defined for all types, even user defined

Two operand base types must match:

However, dont cares CAN be used with the std_match function

std_match available in numeric_std packages

Format: std_match

std match (name

(name, bitstring)

IF a_std_logic_vector = 125 THEN

IF a_bit = 101 THEN

IF a_integer

g

= X2F THEN

Returns true for either 0 or 1 in place of the -

IF a_std_logic_vector = X2F THEN

Example: IF std_match(a, 0-0--)

) THEN

IF a_bit = 1 THEN

-- syntax error

-- syntax error

-- syntax

y

error

IF a_integer = 125 THEN

17

18

Combinational Logic - Sequential

Statements

Component Instantiations

Behavioral style, inside a process or (function, or procedure)

Concurrent statements used to implement combinational logic

Represent the interconnection of other entities called components

Must specify one or more packages that contain the components

being connected

(e.g. USE work.mypkg.ALL;

work.mypkg.ALL;)

Process is a concurrent statement

C

Consists

i t off sequential

ti l statements

t t

t

statement order matters

execute in zero simulation time

No relationship to sequential logic, clocked logic, or state machines

Sequential statements:

Syntax:

instance_label: component_name PORT MAP

(ordered_list_of_signals);

ordered_list_of_signals);

Boolean equations (assignment statements)

IF--THENIF

THEN-ELSE

CASE--WHEN

CASE

Temporary variables may be used inside a process

19

Combinational Logic

but signals must be used for all process inputs and outputs

20

CENG 5534 : Advanced Digital System Design

IF--THEN

IF

THEN--ELSE Statement

IF--THEN

IF

THEN--ELSE Statement

Logically equivalent to concurrent conditional signal assignment

(WHEN--ELSE)

(WHEN

Syntax:

label:

label

:

IF condition1 THEN

statements1;

statements1

;

ELSIF condition2 THEN

statements2;

statements2

;

ELSE

statements3;

statements3

;

END IF;

IF;

Latch will be created if a signal is not always given a value each

time the process runs

Example:

-- optional

PROCESS (xbus

xbus)

)

BEGIN

IF xbus = XF THEN

-- optional section

doitnow <= 1;

-- optional section

END PROCESS;

If a latch is NOT desired

Executes the first block of statements following a TRUE condition

No other statement blocks are executed

include

or

a default value assignment

be sure some branch of the IF statement always assigns a value

21

22

IF--THEN

IF

THEN--ELSE Statement

CASE--WHEN Statement

CASE

Logically equivalent to concurrent selected signal assignment

(WITH--SELECT

(WITH

SELECT--WHEN)

Series of conditions forms a priority encoder structure:

PROCESS (x,y,z,a,b,c

x,y,z,a,b,c)

)

BEGIN

IF x = 1 THEN

foo <= a;

ELSIF y = 1 THEN

foo <= b;

ELSIF z = 1 THEN

foo <= c;

ELSE

foo <= d;

END IF;

END PROCESS;

Syntax:

label:

CASE selector_expression IS

WHEN choice1 => statements1

statements1;

;

WHEN choice2 => statements2

statements2;

;

WHEN choice3 => statements3

statements3;

;

WHEN OTHERS => statements4

statements4;

;

END CASE;

-- optional

-- optional

Executes the single block of statements following a valid choice,

or following OTHERS

Result:

Choices must be mutually exclusive and all inclusive

foo = x . a + x . y . b + x . y . z . c + x . y . z . d

23

Combinational Logic

-- output of a set

set-only latch

END IF;

Forms a multiplexer

multiplexer--based logic structure

24

CENG 5534 : Advanced Digital System Design

Summary

Positive Edge Triggered D FlipFlip-flop

Concurrent vs. Sequential Statements

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

Combinational Logic - Concurrent Statements (Dataflow

(Dataflow))

Boolean Equations ((concurrent

concurrent or sequential

sequential))

Logical Operators (watch parentheses!)

parentheses!)

Relational Operators (same

(same types only)

With--SelectWith

Select-When (like Case), WhenWhen-Else (like IfIf-Then)

Aggregate and Concatenation, Dont Care comparisons

Component Instantiations

ENTITY dff IS

PORT (d,

(d, clk : IN std_logic;

q : OUT std_logic);

END dff;

ARCHITECTURE behavior OF dff IS

BEGIN

PROCESS (clk)

clk)

-- sensitive ONLY to clk

BEGIN

-- rising clk edge

IF (clkEVENT

(clkEVENT AND clk = 1

1)

) THEN q <= d

d;

;

ELSE q <= q

q;

;

-- NOT needed (implied)

END IF;

END PROCESS;

END behavior;

Combinational Logic - Sequential Statements (Behavioral

(Behavioral))

If--ThenIf

Then-Else (like WhenWhen-Else), CaseCase-When (like With

With--Select)

Implied Memory (latch) Problem

25

26

Register = Array of FlipFlip-flops

FIFO

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY register8 IS

PORT (d : IN std_logic_vector (0 TO 7); -- 8 bit reg.

clk : IN std_logic;

q : OUT std_logic_vector (0 TO 7));

END register8;

FIFO with array of 8-words by 99-bits of storage

When rd is asserted, enable one word of the FIFO to drive

data_out,, as selected by rdptr

data_out

rdptr;; else float the output

When wr is asserted, store data_in into one word of the FIFO, as

selected by wrptr

ARCHITECTURE behavior OF register8 IS

BEGIN

PROCESS (clk

clk)

)

BEGIN

IF rising_edge

rising_edge(

(clk

clk)

) THEN q <= d

d;

; -- using the fn.

END IF;

END PROCESS;

END behavior;

27

Combinational Logic

rdinc and wrinc increment either rdptr or wrptr to the next word

rdptrclr and wrptrclr reset either rdptr or wrptr to the first word

rst clears all counters and data registers

28

CENG 5534 : Advanced Digital System Design

FIFO

FIFO

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.std_arith.all;

ENTITY fifo8x9

fif 8 9 IS PORT(

clk, rst:

rst:

rd, wr, rdinc, wrinc:

wrinc:

rdptrclr, wrptrclr:

wrptrclr:

data_in:

data_in

:

IN

data_out:

data_out

:

OUT

END fifo8x9;

8x9 FIFO

0

1

2

3

4

5

6

7

IN std_logic;

IN std_logic;

IN std_logic;

std_logic_vector(8 DOWNTO 0);

std_logic_vector(8 DOWNTO 0));

ARCHITECTURE archfifo8x9

hfif 8 9 OF fifo8x9

fif 8 9 IS

TYPE fifo

fifo_array

_array IS ARRAY(7 DOWNTO 0) OF

std_logic_vector(8 DOWNTO 0);

SIGNAL fifo

fifo:

:

fifo_array;

SIGNAL wrptr, rdptr

rdptr:

: std_logic_vector(2 DOWNTO 0);

SIGNAL en

en:

:

std_logic_vector(7 DOWNTO 0);

SIGNAL dmuxout

dmuxout:

:

std_logic_vector(8 DOWNTO 0);

29

FIFO

FIFO

READ COUNT

-- read pointer

read_count:

read_count

: PROCESS (rst, clk

clk)

)

BEGIN

IF rst = '

'1

1' THEN

Reset

rdptr <= (OTHERS => '

'0

0');

ELSIF (clk'event and clk='

clk='1

1') THEN

IF rdptrclr = '

'1

1' THEN

Pointer clear

rdptr <= (OTHERS => '

'0

0');

ELSIF rdinc = '

'1

1' THEN

Pointer increment

rdptr

d t <=

< rdptr

d t + 1

1;

;

END IF;

IF;

END IF;

END PROCESS;

30

WRITE COUNT

-- write pointer

write_count:

write_count

: PROCESS (rst, clk)

clk)

BEGIN

IF rst = '

'1

1' THEN

Reset

wrptr <= (OTHERS => '

'0

0');

ELSIF (clk'event and clk

clk='

='1

1') THEN

IF wrptrclr = '

'1

1' THEN

Pointer clear

wrptr <= (OTHERS => '

'0

0');

ELSIF wrinc = '

'1

1' THEN

wrptr <= wrptr + 1;

1;

Pointer

P i t increment

i

t

END IF;

END IF;

END PROCESS;

31

Combinational Logic

REGISTER ARRAY

BEGIN

-- fifo register array:

reg_array: PROCESS (rst, clk)

clk)

BEGIN

RESET

IF rst

t = '1

'1' THEN

FOR i IN 7 DOWNTO 0 LOOP

fifo(i) <= (OTHERS => '

'0

0');

END LOOP;

ELSIF (clk'event

(clk'event and clk = '

'1

1') THEN

IF wr = '

'1

1' THEN

FOR i IN 7 DOWNTO 0 LOOP

WRITE

IF en(i) = '

'1

1' THEN

fifo(i) <= data_in

data in;

data_in;

in;

ELSE

fifo(i) <= fifo(i)

fifo(i);

;

END IF;

END LOOP;

END IF;

END IF;

END PROCESS;

32

CENG 5534 : Advanced Digital System Design

FIFO

FIFO

OUTPUT

REGISTER SELECTOR

-- FIFO register selector decoder

-- 8:1 output data mux

WITH wrptr SELECT

p

SELECT

WITH rdptr

dmuxout <=

,

"00000001" WHEN "000",

en <=

fifo(0) WHEN "000",

"00000010" WHEN "001",

fifo(1) WHEN "001",

"00000100" WHEN "010",

fifo(2) WHEN "010",

"00001000" WHEN "011",

fifo(3) WHEN "011",

"00010000" WHEN "100",

fifo(4) WHEN "100",

"00100000" WHEN "101",

fifo(5) WHEN "101"

101 ,

"01000000"

01000000 WHEN "110"

110 ,

fifo(6) WHEN "110",

"10000000" WHEN OTHERS;

fifo(7) WHEN OTHERS;

33

FIFO

34

rd

TRI--STATE OUTPUT

TRI

9

data_in(8:0)

fifo(0) 9

D Q

En

> R

wr

-- three

three-state control of outputs

en(0)

three_state:

three_state

: PROCESS (rd,

rd, dmuxout

dmuxout)

)

wrptr(2:0)

BEGIN

IF rd = '

'1

1' THEN

wrptrclr

wrinc

data_out <= dmuxout

dmuxout;

;

..

.

..

.

counter

Clr Q

3

En

>R

data_out <= (OTHERS => '

'Z

Z');

en(7)

data_out(8:0)

fifo(7)

D Q

9

En

> R

counter

rdptrclr

rdinc

END PROCESS;

END archfifo8x9;

Clr Q

En

>R

rdptr(2:0)

rst

clk

35

Combinational Logic

9

dmuxout

ELSE

END IF;

..

.

36

Potrebbero piacerti anche

- ECE545 Lecture5 DataflowDocumento85 pagineECE545 Lecture5 Dataflowzalmighty78Nessuna valutazione finora

- Synthesizable VHDL Slides AyonDocumento39 pagineSynthesizable VHDL Slides AyonSreeja DasNessuna valutazione finora

- VHDL 1Documento42 pagineVHDL 1Rajesh ShahNessuna valutazione finora

- ECE545 Lecture5 Dataflow 6Documento15 pagineECE545 Lecture5 Dataflow 6Utpal DasNessuna valutazione finora

- System Verilog ImpDocumento59 pagineSystem Verilog ImpPanku RangareeNessuna valutazione finora

- Unit 1 HDL DesignDocumento93 pagineUnit 1 HDL DesignSavi AkolkarNessuna valutazione finora

- VHDLDocumento42 pagineVHDLRajesh ShahNessuna valutazione finora

- Lecture 04-Hardware ModelingDocumento136 pagineLecture 04-Hardware ModelingNguyễn Tấn ĐịnhNessuna valutazione finora

- Chapter 5 VHDL UITM Sem 6 Electrical EngineeringDocumento46 pagineChapter 5 VHDL UITM Sem 6 Electrical EngineeringDyrul SyaznanNessuna valutazione finora

- Verilog Session: General Introduction To Verilog HDL: EE282 Spring Quarter, 2001-2002Documento11 pagineVerilog Session: General Introduction To Verilog HDL: EE282 Spring Quarter, 2001-2002anum11Nessuna valutazione finora

- VerilogDocumento18 pagineVerilogReggie Fresco AguilarNessuna valutazione finora

- Introduction To Verilog HDL: Presented by K.SwathiDocumento35 pagineIntroduction To Verilog HDL: Presented by K.SwathiswathikomatiNessuna valutazione finora

- Verilog HDL: Dr. Shoab KhanDocumento61 pagineVerilog HDL: Dr. Shoab KhanSufyan AsgharNessuna valutazione finora

- VerilogDocumento18 pagineVerilogvortex2910_899547857Nessuna valutazione finora

- Synthesis HintsDocumento44 pagineSynthesis HintsPrathamesh GangalNessuna valutazione finora

- VHDL TutorijalDocumento26 pagineVHDL TutorijalAnonymous 0D7EJeNessuna valutazione finora

- Verilog BasicDocumento48 pagineVerilog BasicDaksh BothraNessuna valutazione finora

- Lecture #2: Verilog HDL: Paul Hartke Phartke@stanford - Edu Stanford EE183 April 8, 2002Documento10 pagineLecture #2: Verilog HDL: Paul Hartke Phartke@stanford - Edu Stanford EE183 April 8, 2002asfsfsafsafasNessuna valutazione finora

- VerilogDocumento61 pagineVerilogAnonymous 13LTklH9myNessuna valutazione finora

- Introduction To VerilogDocumento88 pagineIntroduction To Verilogmaster vijayNessuna valutazione finora

- Introduction To IT and Com SystemsDocumento122 pagineIntroduction To IT and Com SystemsAbdullah HolifNessuna valutazione finora

- Lecture VHDLDocumento27 pagineLecture VHDLryan10rajNessuna valutazione finora

- Introduction To VerilogDocumento77 pagineIntroduction To VerilogParesh SawantNessuna valutazione finora

- Unit I HDL DesignDocumento81 pagineUnit I HDL DesignvinodNessuna valutazione finora

- VHDLDocumento46 pagineVHDLNischay MahamanaNessuna valutazione finora

- Digital System Design With VHDLDocumento70 pagineDigital System Design With VHDLMohammed Wagih EmamNessuna valutazione finora

- VHDL For Synthesis: Summary Notes From: Appendix A: Synthesis The Designer's Guide To VHDL, 2 EdDocumento33 pagineVHDL For Synthesis: Summary Notes From: Appendix A: Synthesis The Designer's Guide To VHDL, 2 EdsridharmirNessuna valutazione finora

- Lab 2Documento59 pagineLab 2J JAYDONNessuna valutazione finora

- Verilog: Yogesh Tiwari Assistant Professor Cspit, CharusatDocumento40 pagineVerilog: Yogesh Tiwari Assistant Professor Cspit, CharusatYogesh TiwariNessuna valutazione finora

- 2011verilog Lec v1 PDFDocumento82 pagine2011verilog Lec v1 PDFpeter26194100% (1)

- VLSI 5 Days Class NotesDocumento26 pagineVLSI 5 Days Class NotesSuresh SurveNessuna valutazione finora

- System VerilogDocumento44 pagineSystem VerilogSonu AgarwalNessuna valutazione finora

- VHDL and HDL Designer Primer: Instructor: Jason D. BakosDocumento46 pagineVHDL and HDL Designer Primer: Instructor: Jason D. BakosAnupam SangalNessuna valutazione finora

- DIGITAL SYSTEM DESIGN Manual1Documento20 pagineDIGITAL SYSTEM DESIGN Manual1Muhammad shehr yarNessuna valutazione finora

- EEL 4783: HDL in Digital System Design: Lecture 2: The Verilog LanguageDocumento64 pagineEEL 4783: HDL in Digital System Design: Lecture 2: The Verilog LanguagesalNessuna valutazione finora

- Data Flow ModellingDocumento55 pagineData Flow ModellingsruthiNessuna valutazione finora

- (Lec 1-3) Introduction To CompilersDocumento34 pagine(Lec 1-3) Introduction To Compilersneagrawal12Nessuna valutazione finora

- Verilog: - A IEEE Standard Hardware Descriptive LanguageDocumento32 pagineVerilog: - A IEEE Standard Hardware Descriptive LanguageS Dinuka MadhushanNessuna valutazione finora

- Oops - Unit - IIDocumento89 pagineOops - Unit - IIdurgaprasad mudiliNessuna valutazione finora

- HDL Synthesis BasicsDocumento58 pagineHDL Synthesis BasicsSUJITHNessuna valutazione finora

- 1up PDF 2015su CS61C L10 SK FSMDocumento47 pagine1up PDF 2015su CS61C L10 SK FSMyanagic605Nessuna valutazione finora

- 15CS202 UnitvDocumento142 pagine15CS202 UnitvChristina josephine malathiNessuna valutazione finora

- To Verilog: Digital DesignDocumento27 pagineTo Verilog: Digital Designbits_who_am_iNessuna valutazione finora

- VHDL PDFDocumento94 pagineVHDL PDFRamuKambalaNessuna valutazione finora

- Writing VHDL For RTL Synthesis: 1 StructureDocumento9 pagineWriting VHDL For RTL Synthesis: 1 StructuremmalgiNessuna valutazione finora

- Digital Systems Verification: Alessandra NardiDocumento29 pagineDigital Systems Verification: Alessandra NardiNaushad SheikNessuna valutazione finora

- Unit-3, 4 and 5Documento123 pagineUnit-3, 4 and 5Aslam KhanNessuna valutazione finora

- Software Project: Instructor: Roded Sharan, Roded@post - Tau.ac - Il TA: Dana Silverbush Course Materials: Virtual - Tau.ac - IlDocumento33 pagineSoftware Project: Instructor: Roded Sharan, Roded@post - Tau.ac - Il TA: Dana Silverbush Course Materials: Virtual - Tau.ac - IlSagie MaozNessuna valutazione finora

- Module 1Documento74 pagineModule 1mksaravanamk1Nessuna valutazione finora

- Chapter 03 Basic of VerilogDocumento109 pagineChapter 03 Basic of VerilogVõ Hoàng Đình KhaNessuna valutazione finora

- Intro Vhdl1Documento30 pagineIntro Vhdl1pandaros000Nessuna valutazione finora

- Ch-1 1Documento29 pagineCh-1 1A_b_qNessuna valutazione finora

- Basic Sequential Components: CT101 - Computing Systems OrganizationDocumento27 pagineBasic Sequential Components: CT101 - Computing Systems OrganizationRotimi OkunolaNessuna valutazione finora

- 13 Gate Level Modeling 20-01-2023Documento15 pagine13 Gate Level Modeling 20-01-2023Back upNessuna valutazione finora

- Two-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachDa EverandTwo-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachNessuna valutazione finora

- Relational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.Da EverandRelational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.Valutazione: 5 su 5 stelle5/5 (1)

- Projects With Microcontrollers And PICCDa EverandProjects With Microcontrollers And PICCValutazione: 5 su 5 stelle5/5 (1)

- Tingalpa Green New Townhouse Development BrochureDocumento12 pagineTingalpa Green New Townhouse Development BrochureMick MillanNessuna valutazione finora

- Employee Conduct Policy StpsoDocumento57 pagineEmployee Conduct Policy StpsoWWLTVWebteamNessuna valutazione finora

- 02-15 QCS 2014Documento17 pagine02-15 QCS 2014Raja Ahmed HassanNessuna valutazione finora

- BCK Test Ans (Neha)Documento3 pagineBCK Test Ans (Neha)Neha GargNessuna valutazione finora

- Uncertainty-Based Production Scheduling in Open Pit Mining: R. Dimitrakopoulos and S. RamazanDocumento7 pagineUncertainty-Based Production Scheduling in Open Pit Mining: R. Dimitrakopoulos and S. RamazanClaudio AballayNessuna valutazione finora

- Reliability EngineerDocumento1 paginaReliability EngineerBesuidenhout Engineering Solutions and ConsultingNessuna valutazione finora

- GK Test-IiDocumento11 pagineGK Test-IiDr Chaman Lal PTNessuna valutazione finora

- Blanko Permohonan VettingDocumento1 paginaBlanko Permohonan VettingTommyNessuna valutazione finora

- White and Yellow Reflective Thermoplastic Striping Material (Solid Form)Documento2 pagineWhite and Yellow Reflective Thermoplastic Striping Material (Solid Form)FRANZ RICHARD SARDINAS MALLCONessuna valutazione finora

- Pay Policy and Salary ScalesDocumento22 paginePay Policy and Salary ScalesGodwin MendezNessuna valutazione finora

- Drg-25 Parts List: Key No Parts No Parts Name Key No Parts No Parts NameDocumento1 paginaDrg-25 Parts List: Key No Parts No Parts Name Key No Parts No Parts NameGergely IvánovicsNessuna valutazione finora

- Asia-Pacific/Arab Gulf Marketscan: Volume 39 / Issue 65 / April 2, 2020Documento21 pagineAsia-Pacific/Arab Gulf Marketscan: Volume 39 / Issue 65 / April 2, 2020Donnie HavierNessuna valutazione finora

- Ex-Capt. Harish Uppal Vs Union of India & Anr On 17 December, 2002Documento20 pagineEx-Capt. Harish Uppal Vs Union of India & Anr On 17 December, 2002vivek6593Nessuna valutazione finora

- Slope Stability Analysis Using FlacDocumento17 pagineSlope Stability Analysis Using FlacSudarshan Barole100% (1)

- Pace 349 ScheduleDocumento3 paginePace 349 Schedulesaxman011100% (1)

- Report - Fostering The Railway Sector Through The European Green Deal PDFDocumento43 pagineReport - Fostering The Railway Sector Through The European Green Deal PDFÁdámHegyiNessuna valutazione finora

- The Consulting Services For PreparationDocumento50 pagineThe Consulting Services For PreparationJay PanitanNessuna valutazione finora

- Autonics KRN1000 DatasheetDocumento14 pagineAutonics KRN1000 DatasheetAditia Dwi SaputraNessuna valutazione finora

- Calio Z: Type Series BookletDocumento24 pagineCalio Z: Type Series BookletDan PopescuNessuna valutazione finora

- TrustworthinessDocumento24 pagineTrustworthinessJamsheed Raza100% (1)

- TDS - Total - Carter 68 - Wyh - 202201 - en - IdnDocumento1 paginaTDS - Total - Carter 68 - Wyh - 202201 - en - IdnAnya J PamungkasNessuna valutazione finora

- Smart Meter Are HarmfulDocumento165 pagineSmart Meter Are HarmfulknownpersonNessuna valutazione finora

- Manual de Partes Dm45-50-lDocumento690 pagineManual de Partes Dm45-50-lklausNessuna valutazione finora

- GTAG 1 2nd EditionDocumento36 pagineGTAG 1 2nd EditionChristen Castillo100% (2)

- APCJ Directory 2019Documento34 pagineAPCJ Directory 2019Anonymous Pu3OF7100% (3)

- E-Booklet Tacompact Board 2021Documento6 pagineE-Booklet Tacompact Board 2021embenNessuna valutazione finora

- 2017 Directory WO Member PagesDocumento112 pagine2017 Directory WO Member PagessberkowitzNessuna valutazione finora

- CPC Project PDFDocumento18 pagineCPC Project PDFsiddharthNessuna valutazione finora

- DOLE Vacancies As of 01 - 10 - 13Documento17 pagineDOLE Vacancies As of 01 - 10 - 13sumaychengNessuna valutazione finora

- HP-exampleDocumento30 pagineHP-exampleAnonymous 105zV1Nessuna valutazione finora