Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Identification of Optimal SVPWM Technique For MLI Fed Induction Motor Drive

Caricato da

Manu ThomasDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Identification of Optimal SVPWM Technique For MLI Fed Induction Motor Drive

Caricato da

Manu ThomasCopyright:

Formati disponibili

Identification Of Optimal SVPWM Technique For

MLI Fed Induction Motor Drive

Chobris C Benny, ManuThomas, Chitra A

School of Electrical Engineering, VIT University, Vellore-632014

Abstract The increasing need for high power and

distortion less operation of industrial motor drives require

the use of higher level multilevel inverters (MLI) with

effective modulation techniques for controlling the inverter

switching. This demands MLI topologies with reduced

number of switches and highly effective SVPWM

techniques. This paper identifies a Carrier based SVPWM

(CBSVPWM) for switching a seven level reduced switch

multilevel inverter. This technique possesses all the

inherent qualities of the conventional SVPWM techniques

and implementation easiness of the carrier based PWM

technique. The proposed technique has been simulated in

MATLAB/SIMULINK and results were validated.

Keywordsreduced swich MLI, carrier based SVPWM,

common mode voltage, triplen harmonic injection

I. INTRODUCTION

Nowadays industries are looking for high power AC drives to

control the speed and torque of industrial motors. With the

advent of power electronic converter the speed and torque

control of induction motors are easier than never before.

Conventionally the control of induction machines are carried

out by two level inverters. But there is a call for high

performance and highly reliable motor drive circuits.

Multilevel inverters have inherent advantages of high voltage

handling and good harmonic rejection capabilities than

conventionally used two level inverters. As the levels goes on

increasing the voltage handling capability and power rating

increases. These are achieved at the cost of increased number

of switches and thereby increased switching losses. The

commonly used MLI topologies are diode clamped, flying

capacitor, cascaded H-bridge inverters. There are many

derived topologies like modular multilevel inverters, hybrid

inverter, Generalized P2-Cell multilevel inverter and so on.[12] The paper examines a Reduced Switch Multilevel Inverter

topology capable of producing a seven level voltage output.

There are various modulation techniques to achieve the

switching sequence for controlling the multilevel inverters.

Most widely used are the PWM techniques and their variants.

There is an increasing trend of using Space Vector Pulse

Width Modulation (SVPWM) technique because of their

easier digital realization. Moreover it can obtain higher output

voltage for the same DC bus voltage, lower switching losses

and better harmonic reduction when compared to other PWM

techniques.[3-6] SVPWM techniques includes:

a) Sector selection based space Vector Modulation.

b) Reduced switching Space Vector Modulation

c) Carrier based Space Vector Modulation

d) Reduced switching carrier based Space Vector

Modulation

Any balanced three-phase voltage reference signal can be

represented by a rotating space vector , whose tip gives the

voltage magnitude for a particular time instant. A conventional

SVPWM technique uses the nearest three states (nodes of the

triangle containing the vector) to approximate the desired

voltage vector. During each switching period, the triangle is

traversed back and forth once. The switching sequence and

dwell times in each state are determined using volt-seconds

comparison produced by switching state vectors equal to that

of the reference vector [2]. For higher level MLIs this

computation is complex and associates approximation errors.

This paper focuses on a Carrier based SVPWM technique to

run a reduced switched multilevel inverter which can be

effectively implemented as an induction motor drive control

circuit. This proposed scheme combines all the qualities of

SVPWM along with the simplicity in the implementation

level.

I.

PROPOSED SEVEN LEVEL MLI TOPOLOGY

The total number of switches in a MLI is a major concern

when going for higher orders and power ratings. Reducing the

number of switches in turn reduces the complexity of control

circuits as well as switching losses. The other factors of

concern are the reliability and cost of the driving circuits. This

paper proposes a compact MLI topology to achieve a seven

level output with reduced number of switches. The reduced

MLI topology has only five switches viz. Sw1, Sw2, Sw3,

Sw4 and Sw5 where two switches are bidirectional. Here Sw2

and Sw3 are bidirectional as shown in fig. 1

Let n total number of voltage steps in the inverter output.

Maximum output voltage Vo=(n-1)Vdc. The various voltage

levels are generated by the given switching sequence as in

table 1.

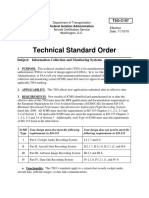

TABLE 1 SWITCHING SEQUENCE FOR MLI

Voltage Level

Switches

Voltage Level

Switches

3 Vdc

SW1 & SW5

-3 Vdc

SW3 & SW4

2 Vdc

SW2 & SW5

-2 Vdc

SW2 &SW4

1 Vdc

SW3 & SW5

-1 Vdc

SW1 & SW4

0 Vdc

All OFF

All OFF

All OFF

FIG. 1: MLI TOPOLOGY

drives applications third harmonic injection method may not

be suitable. In proposed Carrier based SVPWM method a a

common mode voltage is added to the reference phase voltage.

This common mode voltage has an inherent third harmonic

effect. There wont be any difficulties arising here as the

calculation of Common mode offset voltage is done based on

the switching states of the inverter, hence it can be updated in

every computational cycle.

A. Implementation of csvpwm technique

The section explains the steps to generate modulating signals

for all the three phases (a,b,c). These reference phase voltages

are obtained from the reference voltage vector V d and Vq of

the stationary reference frame d-q axis. The imaginary phase

voltages have the information of line-to-line voltages as being

seen by the load. The reference modulating signal,

''

V k , where k=a , b , c , for all the three phases are

produced by adding a corresponding common mode offset

voltage

to

three

individual

reference

phases

V K ,(k =a , b , c) .This will centralize the space-vectors

in the corresponding switching periods and thereby match the

carrier modulation to get optimized space vector modulation.

The centralized space-vector modulation thereby injects a

particular common-mode harmonic function into the reference

three phase voltages [2]. This is obtained by:

V off =V dc

Max ( V a , V b ,V c + min ( V a , V b ,V c ))

2

V 'k =( V k + V off ) mod

2 V dc

, k =a , b , c

N1

( )

'

'

'

'

'

'

Vdc Max ( V a ,V b , V c ) +min (V a , V b ,V c )

V =

N1

2

'

off

II.

CARRIER BASED SVPWM TECHNIQUE

In case of multi-level system, there are many output vectors

and as the voltage level increases, the complexity of

conventional SVPWM increases. Therefore, the Carrier based

SVPWM(CSVPWM) with triangular intersection technique is

necessary for multi-level applications. When we adopt the

conventional Carrier based SVPWM for multi-level system, it

shows good characteristics in linear modulation range.

Third Harmonic Injection technique injects a triplen harmonic

voltage to the reference signal. But determination of third

harmonic is difficult as the output inverter phase-voltage may

abruptly change from cycle to cycle. Hence, it is difficult to

add specific third harmonic voltage[8]. So, for the electric

where

V dc

is 1 p.u. The modulated phase voltage is

obtained by adding

V K ,V of f ,V 'off .

For an n-level Carrier based SVPWM, [n-1] carriers are

required. The carriers have the same frequency and magnitude

to occupy the continuous band. The sampled space vector is

used to generate the switching pulses for the corresponding

switches of the MLI.

III.

SIMULATION RESULTS

Simulation has been carried out for the proposed CSVPWM

and Multi-Carrier PWM (MC-PWM) with an open-loop

control scheme. Simulation is done in MATLAB/SIMULINK

platform. The tables 3 and 4 shows the performance analysis

Parameter

Value

Max. DC link voltage

400V

Common mode voltage level

100%

Switching Frequency

1 KHz

TABLE 2: SIMULATION

PARAMETERS

PWM Technique

CSPWM/MC-PWM

Modulation Index

0 to 1

and effect of switching frequencies for CBSVPWM and CBPWM modulation strategies respectively. THD analysis is

given in figure 2. The corresponding voltage and current

waveforms are given as figures 3, 4 and 5.

FIG. 2: THD ANALYSIS FOR OUTPUT PHASE VOLTAGE Va

TABLE 3: PERFORMANCE ANALYSIS WITH TWO MODUTATION STRATEGIES

FIG 3: CURRENT WAVEFORM FOR R-L LOAD FOR 1 KHz [CBSVPWM]

TABLE 4: EFFECT OF FC ON THE TWO MODULATION STRATEGIES

FIG 4:OUTPUT VOLTAGE WAVEFORM FOR R-L LOAD (1 KHz) [CBSVPWM]

FIG 5: OUTPUT THREE PHASE VOLTAGE WAVEFORM FOR R-load (1 KHz)

[MC-PWM]

IV.

CONCLUSIONS

Highly efficient and easy to implement carrier based SVPWM

technique is simulated and compared with the conventional

multicarrier SVPWM technique for a reduced switch seven

level MLI topology. The result shows that the DC bus

utilization factor has increased with reduced number of

switching. The THD has also reduced comparably. The best

case is produced at a unity power factor and a modulation

index (M=1). The results shows that the better harmonic

performance of proposed PWM strategy compared to its

CBSVM exists in the entire range of the modulation index.

.

REFERENCES

[1] J. Rodreguez, J.S. Lai, F.Z. Peng; Multilevel Inverters: A

Survey of Topologies, Control and Applications, IEEE Trans.

Ind. Electron, Aug. 2002

[2] Xiaoling Wen, Xianggen Yin, The SVPWM Fast

Algorithm for Three-Phase Inverters International Power

Engineering Conference(Ipec 2007)

[3] Jang-Hwan Kim, Seung-Ki Sul, Prasad N.Enjeti, A

Carrier-Based PWM Method with Optimal Switching

Sequence for a Multilevel Four-Leg Voltage Source Inverter

IEEE Trans. on Ind. Appl., VOL.44,404,2008

[4] Yo- Han Lee, Rae-Young Kin, Dong-Scok Hyun, A Novel

SVPWM Strategy Considering DC-Link Balancing for a

Multilevel Voltage Source Inverter IEEE 1999

[5] Dae-Wook Kang, Yo-Han Lee, Bum-Seok Suh, An

Improved Carrier-Based SVPWM Method Using Leg Voltage

Redundancies in Generalized Cascaded Multilevel Inverter

Topology IEEE Trans. On Power Electc., 2003

[6] Yo-Han Lee, Dong-Hyun Kim, Dong-Seok Hyun, Carrier

Based SVPWM Method for Multi-Level System with Reduced

HDF IEEE 2000.

[7] Rohit Basanwal, Kanshik Basu, Ned Mohan, CarrierBased Implementation of SVPWM for Dual Two-Level VSI

and Dual Matrix Converter with Zero Common-Mode

Voltage IEEE Trans. on Power Electc., March 2015

[8] U.V Patil, H.M Suryawanshi, M.M Renge. Multicarrier

SVPWM Controlled Diode Clamped Multilevel Inverter

Based DTC Induction Motor Drive using DSP IEEE

International Conf. on Power Electronics, Drives and Energy

Systems. 2013

[9] Jesmin. F. Khan, Sharif M.A Bhuiyan, Kazi. M. Rahman,

Gregory .V. Murphy, Space vetor PWM for a two phase

VSI, Science direct, Electrical power and energy system, 51

(2013) 265-277.

[10] Shieheng Zheng, Taotao Cui, Mu-Tian Cheng, Long

Chen, Research on variable frequency with three level

topology and SVPWM control, IEEE conference paper June

2012,978-1-4577-2088-8/11

[11] C.Bharatiraja, Dr.S.Jeevananthan, R. Latha, Dr. S.S.

Dash, A Space vector pulse width modulation approach for

DC link voltage balancing in diode clamped multilevel

inverter, Science direct AASRI Procedia 3- 2012,133-140

Potrebbero piacerti anche

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDa EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetValutazione: 2 su 5 stelle2/5 (1)

- Old Highland Park Baptist Church E01Documento74 pagineOld Highland Park Baptist Church E01Lawrence Garner100% (2)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDa EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNessuna valutazione finora

- 3 A Sanitary Standards Quick Reference GuideDocumento98 pagine3 A Sanitary Standards Quick Reference GuideLorettaMayNessuna valutazione finora

- FPGA Based SVM Comtroller Report FinalDocumento34 pagineFPGA Based SVM Comtroller Report FinalShiva Prasad MNessuna valutazione finora

- Space Vector Pulse Width Modulation-Libre PDFDocumento6 pagineSpace Vector Pulse Width Modulation-Libre PDFlongNessuna valutazione finora

- SPWM V/HZ InverterDocumento51 pagineSPWM V/HZ InverterLabi BajracharyaNessuna valutazione finora

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDocumento12 pagineLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNessuna valutazione finora

- An Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterDocumento10 pagineAn Effective Control Technique For Medium-Voltage High-Power Induction Motor Fed by Cascaded Neutral-Point-Clamped InverterRaviraj VishvakarmaNessuna valutazione finora

- International Journal of Computational Engineering Research (IJCER)Documento7 pagineInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)Nessuna valutazione finora

- Electrical Power and Energy Systems: Sherif M. Dabour, Abd El-Wahab Hassan, Essam M. RashadDocumento7 pagineElectrical Power and Energy Systems: Sherif M. Dabour, Abd El-Wahab Hassan, Essam M. RashadSherif M. DabourNessuna valutazione finora

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocumento5 pagineImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNessuna valutazione finora

- Mali 2019Documento7 pagineMali 2019aymenNessuna valutazione finora

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocumento7 pagineSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNessuna valutazione finora

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocumento6 pagineSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNessuna valutazione finora

- Fuzzy Logic Controller Based On Voltage Source Converter-Hvdc SystemDocumento7 pagineFuzzy Logic Controller Based On Voltage Source Converter-Hvdc SystemBhuvneshRathoreNessuna valutazione finora

- 3.1) Artigo - NSPWM e Sobretensões - HavaDocumento12 pagine3.1) Artigo - NSPWM e Sobretensões - HavaAndréNessuna valutazione finora

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocumento12 pagineDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNessuna valutazione finora

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveDocumento7 pagineDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretNessuna valutazione finora

- Introducing The Low Switching Frequency Space Vector Modulated Multi-Modular Three-Level Converters For High Power Applications Switching StrategiesDocumento6 pagineIntroducing The Low Switching Frequency Space Vector Modulated Multi-Modular Three-Level Converters For High Power Applications Switching StrategiesmaheshwareshwarNessuna valutazione finora

- New Multilevel Inverter Topology With Reduced Number of SwitchesDocumento6 pagineNew Multilevel Inverter Topology With Reduced Number of SwitchesVikram PrasadNessuna valutazione finora

- Space Vector PWM With Reduced Common-Mode Voltage For Five-Phase Induction Motor Drives Operating in Overmodulation Zone PDFDocumento10 pagineSpace Vector PWM With Reduced Common-Mode Voltage For Five-Phase Induction Motor Drives Operating in Overmodulation Zone PDFS Karan NagarNessuna valutazione finora

- FBCD PDFDocumento9 pagineFBCD PDFshoaib ehsanNessuna valutazione finora

- Neural Network Control of Grid-Connected Fuel Cell Plants For Enhancement of Power QualityDocumento7 pagineNeural Network Control of Grid-Connected Fuel Cell Plants For Enhancement of Power Qualityashikhmd4467Nessuna valutazione finora

- Space-Vector Modulation in A Two-Phase Induction Motor Drive For Constant-Power OperationDocumento8 pagineSpace-Vector Modulation in A Two-Phase Induction Motor Drive For Constant-Power OperationinfodotzNessuna valutazione finora

- Cascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementDocumento5 pagineCascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementSiri SarojaNessuna valutazione finora

- Multistring Five-Level Inverter With Novel PWMDocumento13 pagineMultistring Five-Level Inverter With Novel PWMsandeepbabu28Nessuna valutazione finora

- 04285962, DJSDocumento9 pagine04285962, DJSDeepu ChinnaNessuna valutazione finora

- MW Scas 2008Documento4 pagineMW Scas 2008pk27575Nessuna valutazione finora

- A Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsDocumento9 pagineA Novel Space Vector Modulation (SVM) Controlled Inverter For Adjustable Speed Drive ApplicationsInternational Journal of Engineering Inventions (IJEI)Nessuna valutazione finora

- Simulation and Comparison of SPWM and SVPWM Control For Two Level InverterDocumento6 pagineSimulation and Comparison of SPWM and SVPWM Control For Two Level InverterIkram RidhoNessuna valutazione finora

- 94 Jicr April 2023Documento7 pagine94 Jicr April 2023Phani RamNessuna valutazione finora

- Novel SVPWM Strategy Considering DC-link Balancing For A Multi-Level Voltage Source InverterDocumento6 pagineNovel SVPWM Strategy Considering DC-link Balancing For A Multi-Level Voltage Source InvertermücahitNessuna valutazione finora

- A General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationDocumento10 pagineA General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationxuanthamdhqnNessuna valutazione finora

- PEMD2014 0282 FinalDocumento6 paginePEMD2014 0282 FinalSherif M. DabourNessuna valutazione finora

- A Study of Comparative Analysis of Different PWMDocumento6 pagineA Study of Comparative Analysis of Different PWMwilliam chaconNessuna valutazione finora

- PSPICE Simulation of Three-Phase Inverters by Means of Swiching Functions (Salazar Joós)Documento8 paginePSPICE Simulation of Three-Phase Inverters by Means of Swiching Functions (Salazar Joós)luism_falconiNessuna valutazione finora

- Unipolar and Bipolar SPWM Voltage Modulation Type Inverter For Improved SwitchingDocumento5 pagineUnipolar and Bipolar SPWM Voltage Modulation Type Inverter For Improved SwitchingOdnamra AlvarezNessuna valutazione finora

- Comparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsDocumento5 pagineComparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsJeya RamNessuna valutazione finora

- Ridley 1991Documento10 pagineRidley 1991mounicapaluru_351524Nessuna valutazione finora

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDocumento6 pagineMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNessuna valutazione finora

- A Capacitor Voltage Balancing Method For Nested Neutral Point Clamped (NNPC) InverterDocumento9 pagineA Capacitor Voltage Balancing Method For Nested Neutral Point Clamped (NNPC) InverterSaravanan MaleNessuna valutazione finora

- Fem PWM Inverter MaxwellDocumento15 pagineFem PWM Inverter MaxwellBala KrishnanNessuna valutazione finora

- A Novel SVPWM Overmodulation Technique Based On Voltage Correcting FunctionDocumento8 pagineA Novel SVPWM Overmodulation Technique Based On Voltage Correcting Functionsravya saiNessuna valutazione finora

- A New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterDocumento8 pagineA New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterVenktesh MishraNessuna valutazione finora

- 17 120920231241 Phpapp02 PDFDocumento9 pagine17 120920231241 Phpapp02 PDFPhani PhaniNessuna valutazione finora

- Chapter 2 NewDocumento11 pagineChapter 2 NewKyaw SoeNessuna valutazione finora

- Fault Elimination in Transmission Line Using Eleven Level StatcomDocumento7 pagineFault Elimination in Transmission Line Using Eleven Level Statcomsurendiran123Nessuna valutazione finora

- 72342Documento71 pagine72342Aidil AzharNessuna valutazione finora

- An Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesDocumento9 pagineAn Optimized Control Method Based On Dual Three-Level Inverters For Open-End Winding Induction Motor DrivesCharles KellyNessuna valutazione finora

- 2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterDocumento10 pagine2013 A Simple Carrier-Based Modulation For The SVM of The Matrix ConverterTran Quoc HoanNessuna valutazione finora

- A Novel Space-Vector PWM Computations For A Dual Three-Level T-Type Converter Applied To An Open End-Winding Induction MachineDocumento6 pagineA Novel Space-Vector PWM Computations For A Dual Three-Level T-Type Converter Applied To An Open End-Winding Induction MachineHieu VuNessuna valutazione finora

- Vsi Fed 3ph ImDocumento13 pagineVsi Fed 3ph ImWisemin LinsNessuna valutazione finora

- 2009A M HavaandE nPerformanceanalysisofreducedcommon-modevoltagePWMmethodsandcomparisonwithstandardPWMmethodsforthree-phasevoltage-sourceinvertersDocumento12 pagine2009A M HavaandE nPerformanceanalysisofreducedcommon-modevoltagePWMmethodsandcomparisonwithstandardPWMmethodsforthree-phasevoltage-sourceinverters21 roseNessuna valutazione finora

- Zero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellsDocumento8 pagineZero-Steady-State-Error Input-Current Controller For Regenerative Multilevel Converters Based On Single-Phase CellssghfqweNessuna valutazione finora

- Fuzzy Logic Control For Single Phase Multilevel InverterDocumento6 pagineFuzzy Logic Control For Single Phase Multilevel InverterMohan KumarNessuna valutazione finora

- Photovoltaic Applications A Comparative Study of Cascaded Z-Source and Quasi Z-Source Multilevel Inverter ForDocumento5 paginePhotovoltaic Applications A Comparative Study of Cascaded Z-Source and Quasi Z-Source Multilevel Inverter ForArun KumarNessuna valutazione finora

- 11-Level Cascaded H-Bridge Grid-Tied Inverter Interface With Solar PanelsDocumento19 pagine11-Level Cascaded H-Bridge Grid-Tied Inverter Interface With Solar Panelssantu212Nessuna valutazione finora

- Speed Control of Space Vector Modulated Inverter Driven Induction MotorDocumento11 pagineSpeed Control of Space Vector Modulated Inverter Driven Induction MotorPraba HaranNessuna valutazione finora

- 2004 A Carrier-Based PWM Method For Three-Phase Four-LegDocumento10 pagine2004 A Carrier-Based PWM Method For Three-Phase Four-LegTài Nguyễn Minh NhậtNessuna valutazione finora

- Authors:: M.V.S.Prajith B.NagarjunaDocumento18 pagineAuthors:: M.V.S.Prajith B.NagarjunaKALYANpwnNessuna valutazione finora

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorDa EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorNessuna valutazione finora

- Pell (2017) - Trends in Real-Time Traffic SimulationDocumento8 paginePell (2017) - Trends in Real-Time Traffic SimulationJorge OchoaNessuna valutazione finora

- Blank FacebookDocumento2 pagineBlank Facebookapi-355481535Nessuna valutazione finora

- Sungbo's Eredo, Southern Nigeria: Nyame Akuma NoDocumento7 pagineSungbo's Eredo, Southern Nigeria: Nyame Akuma NosalatudeNessuna valutazione finora

- Prospectus (As of November 2, 2015) PDFDocumento132 pagineProspectus (As of November 2, 2015) PDFblackcholoNessuna valutazione finora

- Advanced Statistical Approaches To Quality: INSE 6220 - Week 4Documento44 pagineAdvanced Statistical Approaches To Quality: INSE 6220 - Week 4picalaNessuna valutazione finora

- Facultybooklet2011-2012final - 006 (Unlocked by WWW - Freemypdf.com)Documento199 pagineFacultybooklet2011-2012final - 006 (Unlocked by WWW - Freemypdf.com)kalam19892209Nessuna valutazione finora

- AT10 Meat Tech 1Documento20 pagineAT10 Meat Tech 1Reubal Jr Orquin Reynaldo100% (1)

- Chapter 5 - Amino acids and Proteins: Trần Thị Minh ĐứcDocumento59 pagineChapter 5 - Amino acids and Proteins: Trần Thị Minh ĐứcNguyễn SunNessuna valutazione finora

- Cs Fujitsu SAP Reference Book IPDFDocumento63 pagineCs Fujitsu SAP Reference Book IPDFVijay MindfireNessuna valutazione finora

- Ccu 3900alDocumento3 pagineCcu 3900alTourchianNessuna valutazione finora

- RIBA PoWUpdate 131009 ProbynMiersDocumento28 pagineRIBA PoWUpdate 131009 ProbynMiersYellowLightNessuna valutazione finora

- Capital Structure and Leverage: Multiple Choice: ConceptualDocumento53 pagineCapital Structure and Leverage: Multiple Choice: ConceptualArya StarkNessuna valutazione finora

- ERP22006Documento1 paginaERP22006Ady Surya LesmanaNessuna valutazione finora

- Maintenance Performance ToolboxDocumento6 pagineMaintenance Performance ToolboxMagda ScrobotaNessuna valutazione finora

- Indian Traditional Musical InstrumentsDocumento3 pagineIndian Traditional Musical InstrumentsPiriya94Nessuna valutazione finora

- Written Report in Instructional PlanningDocumento6 pagineWritten Report in Instructional PlanningRose Aura HerialesNessuna valutazione finora

- Conjunctions in SentencesDocumento8 pagineConjunctions in SentencesPunitha PoppyNessuna valutazione finora

- Tso C197Documento6 pagineTso C197rdpereirNessuna valutazione finora

- Brachiocephalic Artery: AnteriorDocumento37 pagineBrachiocephalic Artery: AnteriorFarah FarahNessuna valutazione finora

- PC's & Laptop Accessories PDFDocumento4 paginePC's & Laptop Accessories PDFsundar chapagainNessuna valutazione finora

- Final Notice To Global Girls Degree CollgeDocumento2 pagineFinal Notice To Global Girls Degree CollgeIbn E AdamNessuna valutazione finora

- Online Shopping MallDocumento17 pagineOnline Shopping MallMerin LawranceNessuna valutazione finora

- STRUNK V THE STATE OF CALIFORNIA Etal. NYND 16-cv-1496 (BKS / DJS) OSC WITH TRO Filed 12-15-2016 For 3 Judge Court Electoral College ChallengeDocumento1.683 pagineSTRUNK V THE STATE OF CALIFORNIA Etal. NYND 16-cv-1496 (BKS / DJS) OSC WITH TRO Filed 12-15-2016 For 3 Judge Court Electoral College ChallengeChristopher Earl Strunk100% (1)

- The Function and Importance of TransitionsDocumento4 pagineThe Function and Importance of TransitionsMarc Jalen ReladorNessuna valutazione finora

- AYUSH Warli Art 100628Documento10 pagineAYUSH Warli Art 100628adivasi yuva shakti0% (1)

- Appendix 3 COT RPMS For T I III SY 2020 2021 in The Time of COVID 19Documento12 pagineAppendix 3 COT RPMS For T I III SY 2020 2021 in The Time of COVID 19Marjun PachecoNessuna valutazione finora

- Huawei - ESM48100 - User ManualDocumento44 pagineHuawei - ESM48100 - User ManualNguyen Minh ThanhNessuna valutazione finora

- SLTMobitel AssignmentDocumento3 pagineSLTMobitel AssignmentSupun ChandrakanthaNessuna valutazione finora