Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Interrupciones LPC 214x (Capitulo 7)

Caricato da

Guille RojasCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Interrupciones LPC 214x (Capitulo 7)

Caricato da

Guille RojasCopyright:

Formati disponibili

Captulo 7: LPC214x VIC

7.1 Caractersticas

Controlador de Interrupciones Vectorizadas ARM (VIC)

32 entradas de interrupcin

16 interrupciones vectorizadas IQS

16 niveles de prioridades dinmicamente asignadas a las peticiones

de interrupcin.

Generacin de interrupcin por Software.

7.2 Descripcin

El controlador de interrupciones vectorizadas (VIC) toma 32 entradas de

peticin de interrupcin programables y las asignas a las mismas en 3

categoras, FIQ, IRQ vectorizadas e IRQ no vectorizadas. El esquema de

asignacin programable significa que las prioridades de las interrupciones

de los distintos perifricos se pueden asignar dinmicamente y ser

ajustadas.

Fast Interrupt Request (FIQ) son las peticiones que tienen mayor prioridad.

Si ms de un pedido es asignado a FIQ, el VIC realiza una OR con los

pedidos para producir la seal FIQ en el procesador ARM. La latencia FIQ

ms rpida posible se logra cuando una nica solicitud se clasifica como

FIQ, porque entonces la rutina de servicio de FIQ simplemente puede

empezar a tratar con ese dispositivo. Pero si mas de una peticin es

asignada a la clase FIQ, la rutina de servicio FIQ puede leer una palabra

desde el VIC que identifique cual es la fuente de FIQ peticionando la

interrupcin.

Las IRQs vectorizadas tienen una prioridad mediana, pero solo 16 de los 32

pedidos pueden ser asignados a esta categora. Cualquiera de estas 32

peticiones pueden ser asignadas a cualquiera de los 16 espacios del vector

de IRQ, entre los cuales el espacio 0 tiene la mayor prioridad y el 15 tiene la

menor.

El VIC realiza una operacin OR con los pedidos de todas las IRQ,

vectorizadas y no vectorizadas, para producir la seal en el procesador ARM.

La rutina de servicio de interrupcin puede comenzar leyendo un registro

desde el VIC y saltar al servicio en s. Si cualquiera de las IRQs vectorizadas

son peticionadas, el VIC provee la direccin del servicio de interrupcin de la

IRQ con mayor prioridad, de lo contrario, proporciona la direccin de una

rutina predeterminada que es compartida por todas las IRQs no

vectorizadas. La rutina por defecto puede leer otro registro del VIC para

conocer cuales son las IRQs que se encuentran activas.

Todos los registros en el VIC son registro de una palabra. La lectura y

escritura de bytes y media palabra no se encuentran permitidas.

7.3 Descripcin de los Registros

El VIC presenta los registros que se encuentran el la Tabla 41

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 1

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 2

7.4 Registros del VIC

La siguiente seccin describe los registros del VIC en el orden en los cuales

son utilizados en la lgica del VIC, desde los ms cercanos a las entradas de

peticin de interrupcin hasta aquellos ms abstractos para el uso de

software. Para la mayora de las personas, este es el mejor orden para leer

acerca de los registros cuando se est aprendiendo sobre el VIC.

7.4.1 Software Interrupt register (VICSoftInt - 0xFFFF F018)

El contenido de este registro es sometido a una OR con los 32 pedidos

de interrupcin de varios perifricos antes que cualquier lgica sea

aplicada.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 3

7.4.2 Software Interrupt Clear register (VICSoftIntClear - 0xFFFF

F01C)

Este registro permite limpiar uno o ms bits del Software Interrupt

Register sin tener que leerlo previamente.

7.4.3 Raw Interrupt status register (VICRawIntr - 0xFFFF F008)

Este es un registro de solo lectura. Este registro lee el estado de los

32 pedidos de interrupcin y las interrupciones por software sin tener

en cuenta su habilitacin o clasificacin.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 4

7.4.4 Interrupt Enable register (VICIntEnable - 0xFFFF F010)

Este es un registro de lectura y escritura. Controla cuales de los 32

pedidos de interrupcin e interrupcin por software contribuyen a los

FIQs o IRQs.

7.4.5 Interrupt Enable Clear register (VICIntEnClear - 0xFFFF F014)

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 5

Este es un registro de solo escritura. Este registro permite limpiar por

software uno o mas bits del Interrupt Enable Register (ver Section

7.4.4 Interrupt Enable register (VICIntEnable -0xFFFF F010)), sin

tener que leerlo previamente.

7.4.6 Interrupt Select register (VICIntSelect - 0xFFFF F00C)

Este es un registro accesible para lectura y escritura. Clasifica cada

una de las 32 solicitudes de interrupcin, contribuyendo a FIQ o IRQ.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 6

7.4.7 IRQ Status register (VICIRQStatus - 0xFFFF F000)

Este es un registro de solo lectura. Lee el estado de los pedidos de

interrupciones que se encuentran habilitadas y clasificadas como IRQ.

No diferencia si las mismas son vectorizadas o no vectorizadas.

7.4.8 FIQ Status register (VICFIQStatus - 0xFFFF F004)

Este es un registro de solo lectura. En este se pueden leer el estado

de aquellos pedidos de interrupcin que se encuentran habilitadas y

clasificadas como FIQ. Si mas de una peticin es clasificada como FIQ,

la rutina de servicio FIQ puede leer este registro para saber cual es la

solicitud activa.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 7

7.4.9 Vector Control registers 0-15 (VICVectCntl0-15 - 0xFFFF F20023C)

Estos son registros de escritura y lectura. Cada uno de estos registros

controla un de los 16 espacios de las IRQ vectorizadas. El espacio 0

tiene la prioridad mas alta y el espacio 15 la menor. Note que

deshabilitando una IRQ vectorizada en uno de los registros

VICVectCntl no deshabilita la interrupcin en si misma sino que la

cambia a la forma no vectorizada.

Por ejemplo, las siguientes dos lineas asigna el espacio 0 al pedido de

interrupcin de SPI0 IRQ y el espacio 1 al pedido de interrupcin de

TIMER0IRQ.

VICVectCntl0=0x20|10;

VICVectCntl1=0x20|4;

7.4.10 Vector Address registers 0-15 (VICVectAddr0-15 - 0xFFFF

F100-13C)

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 8

Estos son registros de lectura y escritura. Estos registros mantienen la

direccin de las rutinas de servicio de interrupcin para los 16

espacios de las IRQs vectorizadas.

7.4.13 Protection Enable register (VICProtection - 0xFFFF F020)

Este es un registro accesible por lectura y escritura. Controla el

acceso a los registros VIC a travs de software corriendo en el modo

usuario.

7.5 Fuente de interrupciones

La tabla 63 hace una lista de las fuentes de interrupciones para cada

funcin perifrica. Cada dispositivo perifrico posee una lnea de

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 9

interrupcin conectado al VIC, pero puede tener varias banderas de

interrupciones internas. Las banderas de interrupciones individuales pueden

tambin representar ms de una fuente de interrupcin.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 10

4.5 Entradas para interrupciones externas

El LPC2141/2/4/6/8 incluye 4 entradas para interrupciones externas

que pueden ser seleccionadas como funciones de los pines.

Las entradas externas de interrupcin pueden ser utilizadas

opcionalmente para sacar al procesador del modo Power-down.

4.5.1 Descripcin de los registros.

La funcin de interrupcin externa posee cuatro registros

asociados a ella. El registro EXTINT contiene las banderas de

interrupcin, y el registro EXTWAKEUP contiene los bits que

habilitan las interrupciones externas individuales para sacar al

microcontrolador del modo Power-down. Los registros EXTMODE

y EXTPOLAR especifican los parmetros de nivel y sensitividad

de flanco.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 11

4.5.2 External Interrupt Flag register (Registro de banderas de las

interrupciones externas) (EXTINT - 0xE01F C140)

Cuando un pin es seleccionado para la funcin de interrupcin

externa, el nivel o el flanco en dicho pin (los cuales sern

seleccionados por los bits de los registros EXTPOLAR y

EXTMODE) pondr a uno las banderas de interrupcin en este

registro. Esto asegura la solicitud de interrupcin

correspondiente a la VIC, lo que provocar una interrupcin si

las interrupciones desde el pin se encuentran habilitadas.

Escribir un 1 a los bits EINT0 hasta EINT3 en el registro

EXTINT limpia el bit correspondiente. En el modo sensible por

nivel (level-sensitive) esta accin solo es eficaz cuando el pin

se encuentra en su modo inactivo.

Una vez que un bit de EINT0 a EINT3 es puesto a 1 y un

cdigo apropiado se comienza a ejecutar (manejar un

despertador y/o una interrupcin externa), este bit en el

registro EXTINT debe ser limpiado. De otra forma, el evento que

dispar la actividad en el pin del EXTINT no ser reconocido en

un futuro.

Observacin: siempre que un cambio de modo de

funcionamiento externo de interrupcin (es decir, nivel activo /

flanco) se lleva a cabo (incluyendo la inicializacin de una

interrupcin externa), El bit correspondiente en el registro

EXTINT debe ser limpiado! Para ms detalles vea Seccin 4.5.4

External Interrupt Mode register (EXTMODE - 0xE01F C148) y

Section 4.5.5 External Interrupt Polarity register (EXTPOLAR 0xE01F C14C).

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 12

4.5.3 Interrupt Wakeup register (INTWAKE - 0xE01F C144)

Habilitar algunos bits en el registro INTWAKE permite a las interrupciones

externas y a otras fuentes a sacar al microprocesador del modo powerdown. La funcin relacionada EINTn debe ser asignada al pin de manera que

el proceso de activacin tome lugar. No es necesario, que la interrupcin

sea habilitada en el vector controlador de interrupciones (VIC) para que una

activacin tenga lugar. Este arreglo permite capacidades adicionales, tales

como tener una entrada de interrupcin externa que permita sacar al

microprocesador del modo power-down sin causar una interrupcin

(simplemente reanudando la operacin), o permitir que una interrupcin sea

habilitada durante el modo power-down sin sacar de este estado al

procesador si alguna llega a suceder (eliminando la necesidad de

deshabilitar la interrupcin si la caracterstica de activacin no es deseada

en la aplicacin).

Para que un pin sea una fuente de interrupcin, el cual active al

microprocesador del modo power-down, tambin es necesario limpiar el bit

correspondiente en el registro EXTINT (Seccin 4.5.2 en la pgina 6).

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 13

4.5.4 External Interrupt Mode register (Registro modo de interrupcin

externa) (EXTMODE - 0xE01F C148)

Los bits en este registro seleccionan si cada pin del registro EINT es

sensitivo por nivel o flanco. Solo los bits que son seleccionados para la

funcin EINT y habilitados por medio del registro VICIntEnable pueden

causar interrupciones por medio de la funcin de interrupcin externa

(aunque, por supuesto los pines seleccionados para otras funciones pueden

causar interrupciones desde esas funciones).

Nota: El software slo debera cambiar un bit en este registro cuando su

interrupcin est desactivada en el registro VICIntEnable, y debe escribir el

correspondiente 1 al registro EXTINT antes de habilitar (inicializacin) o

volver a habilitar la interrupcin, para borrar el bit EXTINT que podra

establecerse cambiando el modo.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 14

4.5.5 External Interrupt Polarity register (EXTPOLAR - 0xE01F C14C)

En el modo sensitivo por nivel, los bits de este registro seleccionan si el pin

correspondiente es activo por bajo o por alto. En el modo sensitivo por

flanco, estos seleccionan si el pin es activo por flanco ascendente o

descendente. Solamente los pines que son seleccionados para la funcin

EINT y se encuentran habilitados en el registro VICIntEnable pueden causar

interrupciones desde la funcin de interrupcin externa (aunque, por

supuesto los pines seleccionados para otras funciones pueden causar

interrupciones desde esas funciones).

Nota: El software slo debera cambiar un bit en este registro cuando su

interrupcin est desactivada en el registro VICIntEnable, y debe escribir el

correspondiente 1 al registro EXTINT antes de habilitar (inicializacin) o

volver a habilitar la interrupcin, para borrar el bit EXTINT que podra

establecerse cambiando el modo.

Ing. Sanchez Rojas Guillermo- Electronica Digital III 2012

Pgina 15

Potrebbero piacerti anche

- AnalisisReal II PD5Documento4 pagineAnalisisReal II PD5CESAR ERNESTO ROQUE CISNEROSNessuna valutazione finora

- Oncenio de LeguiaDocumento40 pagineOncenio de LeguiaLeonardo Ramos MedranoNessuna valutazione finora

- Factores de Crecimiento de La PlantaDocumento3 pagineFactores de Crecimiento de La PlantaJosé ManuelNessuna valutazione finora

- Informe Tecnico PedagogicoDocumento11 pagineInforme Tecnico PedagogicoAntony Orga Araujo100% (2)

- Cultivo Maiz BlancoDocumento36 pagineCultivo Maiz BlancoPeter AguirreNessuna valutazione finora

- Rompe Los Limites MentalesDocumento133 pagineRompe Los Limites MentalesSteven ValderramaNessuna valutazione finora

- Cuentos para Niños. Uga La TortugaDocumento10 pagineCuentos para Niños. Uga La TortugaPaola CardozoNessuna valutazione finora

- Los Tres FiatDocumento1 paginaLos Tres FiatDácil Coello Cabrera100% (1)

- El Enfoque de Los Derechos Humanos en Las Politicas Publicas Ideas para Un Debate en Ciernes PDFDocumento30 pagineEl Enfoque de Los Derechos Humanos en Las Politicas Publicas Ideas para Un Debate en Ciernes PDFSilvana CamusNessuna valutazione finora

- 01 Apersonamiento y OtrosDocumento3 pagine01 Apersonamiento y OtrosJuan Jose Romero MedinaNessuna valutazione finora

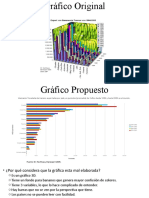

- Clase 1, GráficoDocumento3 pagineClase 1, GráficoobandocristianNessuna valutazione finora

- Cap 3 Diagrama de FlujoDocumento13 pagineCap 3 Diagrama de Flujoenaulad511Nessuna valutazione finora

- Res.10-2010 D.C.Y M de MendozaDocumento44 pagineRes.10-2010 D.C.Y M de MendozaMar DdNessuna valutazione finora

- Dome 2Documento5 pagineDome 2Jean Pierre ContrerasNessuna valutazione finora

- 05-Rutinas de Entrada y SalidaDocumento15 pagine05-Rutinas de Entrada y Salidadave dogNessuna valutazione finora

- Señor Juez Público Familiar 14Documento5 pagineSeñor Juez Público Familiar 14mary mamaniNessuna valutazione finora

- TransDocumento11 pagineTranssamuelNessuna valutazione finora

- Batalla Del NiloDocumento4 pagineBatalla Del NiloMarco AntonioNessuna valutazione finora

- Van Rensselaer Potter: Un Paradigma de VidaDocumento22 pagineVan Rensselaer Potter: Un Paradigma de VidaSandra ContrerasNessuna valutazione finora

- Ensayo Entorno Organizacional en Las Empresas Por Cecilio CarcacheDocumento2 pagineEnsayo Entorno Organizacional en Las Empresas Por Cecilio CarcacheCecilio CarcacheNessuna valutazione finora

- Fase 8 Plantilla de EvidenciasDocumento3 pagineFase 8 Plantilla de Evidenciasjuan degoNessuna valutazione finora

- Yucatan - KaambalDocumento13 pagineYucatan - Kaambalaespinosapat7562Nessuna valutazione finora

- Virtudes de MaríaDocumento4 pagineVirtudes de MaríaBryan EsparzaNessuna valutazione finora

- Intoxicación Con PropanoDocumento2 pagineIntoxicación Con PropanoDavid EduardoNessuna valutazione finora

- Guías Envía Transportadora Colombia LogísticaDocumento5 pagineGuías Envía Transportadora Colombia LogísticaStevenson Rivera50% (2)

- Tipos de Sociedades Mercantiles en MéxicoDocumento3 pagineTipos de Sociedades Mercantiles en MéxicoRodrigo de la Cruz100% (2)

- Oportunidad Inversion CARBOMEX-4Documento21 pagineOportunidad Inversion CARBOMEX-4GerardoNessuna valutazione finora

- Comunicado de Prensa - Desalojo de La RotondaDocumento2 pagineComunicado de Prensa - Desalojo de La RotondaRubén E. Morales RiveraNessuna valutazione finora

- El Romance y La Décima 7°Documento5 pagineEl Romance y La Décima 7°Marcela Sánchez ConchaNessuna valutazione finora

- Distribuciones DiscretasDocumento48 pagineDistribuciones DiscretasAlejandrina De BoutaudNessuna valutazione finora

- Lógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosDa EverandLógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosValutazione: 3.5 su 5 stelle3.5/5 (7)

- 7 tendencias digitales que cambiarán el mundoDa Everand7 tendencias digitales que cambiarán el mundoValutazione: 4.5 su 5 stelle4.5/5 (87)

- Guía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaDa EverandGuía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaValutazione: 3.5 su 5 stelle3.5/5 (2)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaDa EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaValutazione: 4.5 su 5 stelle4.5/5 (117)

- Excel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteDa EverandExcel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteValutazione: 1 su 5 stelle1/5 (1)

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másDa EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másValutazione: 2.5 su 5 stelle2.5/5 (3)

- Curso básico de Python: La guía para principiantes para una introducción en la programación con PythonDa EverandCurso básico de Python: La guía para principiantes para una introducción en la programación con PythonNessuna valutazione finora

- Todo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainDa EverandTodo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainNessuna valutazione finora

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Da EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Valutazione: 4 su 5 stelle4/5 (51)

- La psicología del trading de una forma sencilla: Cómo aplicar las estrategias psicológicas y las actitudes de los comerciantes ganadores para operar con éxito en línea.Da EverandLa psicología del trading de una forma sencilla: Cómo aplicar las estrategias psicológicas y las actitudes de los comerciantes ganadores para operar con éxito en línea.Valutazione: 4.5 su 5 stelle4.5/5 (3)

- El mito de la inteligencia artificial: Por qué las máquinas no pueden pensar como nosotros lo hacemosDa EverandEl mito de la inteligencia artificial: Por qué las máquinas no pueden pensar como nosotros lo hacemosValutazione: 5 su 5 stelle5/5 (2)

- Cómo ser un Ninja Social: Supera el miedo a hablar con desconocidos, crea conexiones con cualquiera y se la persona más interesante del lugarDa EverandCómo ser un Ninja Social: Supera el miedo a hablar con desconocidos, crea conexiones con cualquiera y se la persona más interesante del lugarValutazione: 4.5 su 5 stelle4.5/5 (4)