Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Iaetsd-Design of A Low Power Multiband Clock Distribution Circuit

Caricato da

iaetsdiaetsdTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Iaetsd-Design of A Low Power Multiband Clock Distribution Circuit

Caricato da

iaetsdiaetsdCopyright:

Formati disponibili

Proceedings of International Conference On Current Innovations In Engineering And Technology

ISBN : 978 - 1502851550

DESIGN OF A LOW POWER MULTIBAND CLOCK DISTRIBUTION CIRCUIT

USING SINGLE PHASE CLOCK

T.BhavyaBhavani (1), Dr.K.Seshadri Sastry (2), Dr.G.R.L.V.N Srinivas Raju (3)

T.BhavyaBhavani (1), M.Tech student -VLSI Design, Dept of ECE, Shri Vishnu Engg College for Women

Dr.K.Seshadri Sastry (2), Professor, Dept of ECE, Shri Vishnu Engineering College for Women

Dr.G.R.L.V.N Srinivas Raju (3), Professor and H.O.D, Dept of ECE, Shri Vishnu Engg College for Women

ABSTRACT:

The clock distribution network consumes nearly

70% of the total power consumed by the

integrated circuit since this is the only signal

which has the highest switching activity. Normally

for a multiband clock domain network we develop

a multiple PLL to cater the need. This project aim

for developing a low power true single phase

clock(TSPC) multiband network which will

supply for the multi clock domain network. In this

paper, a wide band 2/3 prescaler is verified in the

design of proposed wide band multimodulus

32/33/47/48 or 64/65/78/79 prescaler. A dynamic

logic multiband flexible integer-n divider based on

pulse swallow topology is proposed which uses a

low power wide band 2/3 prescaler and a wide

band multimodulus 32/33/47/48 or 64/65/78/79

prescaler. Since the multimodulus 32/33/47/48 or

64/65/78/79 prescaler has a maximum operating

frequency of 6.2GHz, the values of P and S

counters can actually be programmed to divide

over the whole range of frequencies. However the

P and S counter are programmed accordingly.

The proposed multiband flexible divider also uses

an improved loadable bit cell for swallow counter

and consumes a power of 0.96 and 2.2mW. This

project is highly useful and recommended for

communication applications like Bluetooth,

Zigbee, IEEE 802.15.4 and 802.11 a/b/g WLAN

frequency synthesizers which are proposed based

on pulse swallow topology. This design is modelled

using Verilog simulated tool MODELSIM 6.4b

and implemented and synthesized using Xilinx

ISE 10.1.

Keywords: True single phase clock (TSPC),

Frequency synthesizer, Multimodulus prescaler,

Phase locked loop (PLL)

1. INTRODUCTION

Wireless LAN (WLAN) in the multi

gigahertz bands, such as HIPER LAN II and Network

standards like IEEE 802.11a/b/g are recognized as

leading standards for high-rate data transmissions,

and standards like Network protocol IEEE 802.15.4

are recognized for low-rate data transmissions. The

integrated synthesizers for

Wireless

LAN

applications at 5GHz reported in and consume up to

24 mw in CMOS realizations, where the first-stage

divider is implemented using an Injection-locked

divider which consumes large chip area and has a

narrow locking range. The best published frequency

synthesizer at 5GHz consumes 9.6 mw at 1-V supply,

where its complete divider consumes power around 6

mw, where the first-stage divider is implemented

using the source-coupled logic (SCL) circuit, which

allows higher operating Frequencies but uses more

power. Dynamic latches are faster and consume less

power compared to static dividers.

High speed divide-by- counter (also called

prescaler) is a fundamental module for frequency

synthesizers. Its design is crucial because it operates

at a higher frequency and consumes higher power

consumption. A divide-by- counter consists of flipflops (FF) and extra logic, which determines the

terminal count. Conventional high speed FF based

divide by counter designs use current-mode logic

(CML) latches and suffer from the disadvantage of

large load capacitance. This not only limits the

maximum operating frequency and current-drive

capabilities, but also increases the total power

consumption. Alternatively, FF based divide-by

designs adopt dynamic logic FFs such as true-singlephase clock (TSPC). The designs can be further

enhanced by using extended true-single-phase-clock

(E-TSPC) FFs for high speed and low power

applications. E-TSPC designs remove the transistor

International Association Of Engineering & Technology For Skill Development

19

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

stacked structure so that all the transistors are free of

the body effect. They are thus more sustainable for

high operating frequency operations in the face of

low voltage supply. Past optimization efforts on

prescaler designs focused on simplifying the logic

part to reduce the circuit complexity and the critical

path delay. For example, an E-TSPC design

embedded with one extra P-MOS/N-MOS transistor

can form an integrated function of FF and AND/OR

logic. Moving part of the control logic to the first FF

to reduce unnecessary FF toggling yields another

version of prescaler design .These two classic designs

each contains 16 transistors only and the mode

control logic uses as few as 4 transistors. To achieve

such circuit simplicity, it calls for a rationed structure

in the FF design. Despite its distinct speed

performance, the incurred static and short circuit

power consumptions are significant. Latest designs

presented in adopt a general TSPC logic family

containing both rationed and ratio less inverter

alternatives. Since the maximum height of transistor

stacking is up to 5, these designs lose their

performance advantages when working under a low

scenario. In a power gating technique by inserting an

extra PMOS between and the FF is employed in two

novel divide-by-2/3 counter designs. The unused FF

can be shut down when working in the divide-by-2

mode. Due to the increase in the number of transistor

stacking (up to 4), these designs are not suitable for

low operations. Due to the quadratic dependence of

power consumption on supply voltage, lowering is a

very effective measure to reduce the power at the

expense of speed performance. .In particular, here

focus on low operations for power saving without

sacrificing the speed performance. In this design,

rationed E-TSPC FFs are employed due to its circuit

simplicity and speed performance. Only one pass

transistor is needed to implement the mode control

logic. The proposed design is capable of working at a

maximum frequency of 531 MHz when the supply

voltage is as low as 0.6 V.

ISBN : 978 - 1502851550

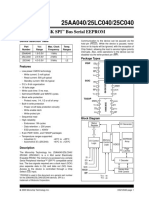

Fig 1: Proposed dynamic logic multiband

flexible divider.

The TSPC and E-TSPC designs are able to drive

the dynamic latch with a single clock phase and avoid

the skew problem. However, the adoption of singlephase clock latches in frequency dividers has been

limited to PLLs with applications below 5GHZ. The

frequency synthesizer reported in [6] uses an E-TSPC

prescaler as the first-stage divider, but the divider

consumes around 6.25 mw. Most Network protocol

IEEE 802.11a/b/g frequency synthesizers employ

SCL dividers as their first stage, while dynamic

latches are not yet adopted for multiband

synthesizers. In this paper, a dynamic logic multiband

flexible integer-N divider based on pulse-swallow

topology is proposed which uses a low-power

wideband 2/3 prescaler and a wideband multi

modulus 32/33/47/48 prescaler as shown in Fig. 1.

The divider also uses an improved low power

loadable bit-cell for the Swallow-counter.

2. DESIGN CONSIDERATIONS

The key parameters of high-speed digital

circuits are the propagation delay and power

consumption. The maximum operating frequency of a

digital circuit is calculated and is given by

f max = 1/(tpLH + tpH L)

Where tpLH and tpHL are the propagation

delays of gates respectively. The total power

consumption of the CMOS digital circuits is

determined by the switching and short circuit power.

International Association Of Engineering & Technology For Skill Development

20

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

The switching power is linearly proportional to the

operating frequency and is given by the sum of

switching power at each output node as in

n

P Switching= fclkCLiVdd2

i=1

where n is the number of switching nodes

fclk is the clock frequency CLi is the load capacitance

at the output node of the stage, and Vdd is the supply

voltage. Normally, the short-circuit power occurs in

dynamic circuits when there exists direct paths from

the supply to ground which is given by

Psc = Isc * Vdd

where Isc is the short-circuit current. The

analysis shows that the short-circuit power is much

higher in E-TSPC logic circuits than in TSPC logic

circuits. However, TSPC logic circuits exhibit higher

switching power compared to that of E-TSPC logic

circuits due to high load capacitance. For the E-TSPC

logic circuit, the short-circuit power is the major

problem. The E-TSPC circuit has the merit of higher

operating frequency than that of the TSPC circuit due

to the reduction in load capacitance, but it consumes

significantly more power than the TSPC circuit does

for a given transistor size. The following analysis is

based on the latest design using the popular and lowcost 0.18 _m CMOS process.

3. WIDEBAND E-TSPC 2/3 PRESCALER

The E-TSPC 2/3 prescaler consumes large

short circuit power and has a higher frequency of

operation than that of TSPC 2/3 prescaler. The

wideband single-phase clock 2/3 prescaler used in

this design consists of two D-flip-flops and two NOR

gates embedded in the flip-flops. The first NOR gate

is embedded in the output of DFF1, and the second

NOR gate is embedded in the first stage of DFF2.

Fig 2: Wideband single-phase clock 2/3 prescaler

ISBN : 978 - 1502851550

When logic signal MC switches from "1" to

"0", the logic value at the input of DFF1 is

transferred to the input of DFF2 as one of the input of

the NOR gate embedded in DFF1 is "0" and the

wideband prescaler operates at the divide-by-3 mode.

During the divide-by-2 operation, only DFF2 actively

participates in the operation and contributes to the

total power consumption since all the switching

activities are blocked in DFF1. Thus, the wideband

2/3 prescaler has benefit of saving more than 50% of

power during the divide-by-2 operation. The

measured results shows that the wideband 2/3

prescaler has the maximum operating frequency of

6.5GHz.

4. MULTIMODULUS 32/33/47/48 or 64/65/78/79

PRESCALER

The proposed wideband multimodulus

prescaler which can divide the input frequency by 32,

33,47, and 48 or 64, 65,78 and 79 is shown in Fig. 3.

It is similar to the 32/33 or 64/65 prescaler used in,

but with an additional inverter and a multiplexer. The

proposed prescaler performs additional divisions

(divide-by-47 and divide-by-48 or divide-by-78 and

divide-by-79) without any extra flip flop, thus saving

a considerable amount of power and also reducing

the complexity of multi band divider.

The multimodulus prescaler consists of the

wideband

2/3

(N1/(N1+1))

prescaler,

four

asynchronous TSPC divide-by-2 circuits ((AD)=16)

and combinational logic circuits to achieve multiple

division ratios.

Fig 3: Proposed Multimodulus 32/33/47/48

(or) 64/65/78/79 Prescaler

International Association Of Engineering & Technology For Skill Development

21

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

Beside the usual MOD signal for controlling

N/(N+l) divisions, the additional control signal sel is

used to switch the prescaler between 32/33and 47/48

modes.

1) Case 1: sel='0'

When sel='0', the output from the NAND2

gate is directly transferred to the input of 2/3

prescaler and the multimodulus prescaler operates as

the normal 32/33 prescaler, where the division ratio is

controlled by the logic signal MOD. If MC=1, the 2/3

prescaler operates in the divide-by-2 mode and when

MC=O, the 2/3 prescaler operates in the divide-by-3

mode. If MOD=1, the NAND2 gate output switches

to logic "I" (MC=1) and the wideband prescaler

operates in the divide-by-2 mode for entire operation.

The division ratio N performed by the multi modulus

prescaler is

N = (AD*N1) + (0*(N1+ 1)) = 32

Where N1=2 and AD=16 is fixed for the entire

design. If MOD = 0 , for 30 input clock cycles MC

remains at logic "1", where wideband prescaler

operates in divide-by-2 mode and for three input

clock cycles, MC remains at logic "0" where the

wideband prescaler operates in the Divide-by-3

mode. The division ratio N+ 1 performed by the

multi modulus prescaler is

N+l = ((AD - l)*N1) + (1 * (N1 +1)) = 33

S2 switch to logic "0" and the bit-cell does not

perform any function. The MOD signal goes

logically high only when the S-counter finishes

counting down to zero. If MOD and LD are logically

low, the bit-cell acts as a divide-by-2 unit. If MOD is

logically low and LD is logically high, the input bit

PI is transferred to the output. In the initial state,

MOD = 0, the multimodulus prescaler selects the

divide-by-N+ 1 mode (divide-by-33 or32).

2) Case 2: sel =' l'

When sel=' 1', the inverted output of the

NAND2 gate is directly transferred to the input of 2/3

prescaler and the multimodulus prescaler operate as a

47/48 prescaler, where the division ratio is controlled

by the logic signal MOD. If MC= 1, the 2/3 prescaler

operates in divide-by- 3 mode and when MC=0, the

2/3 prescaler operates in divide-by-2 mode which is

ISBN : 978 - 1502851550

quite opposite to the operation performed when

sel='0' If MOD=1, the division ratio N+ 1 performed

by the multimodulus prescaler is same except that the

wideband prescaler operates in the divide by-3 mode

for the entire operation given by

N + l = (AD * (N1+1)) + (0 * Nl) = 48

If MOD=1, the division ratio N performed by the

multimodulus prescaler is

N = ((AD - l ) * (N1 + 1)) + (1 * Nl)=47.

In order to get 64/65/78/79 clock cycles we need to

operate 4/5 prescaler by making the control signal sel

of second MUX to 1.To get 32/33/47/48 prescaler,

the second MUX should be equal to 0 means the

control signal sel of the second MUX should be equal

to 0 and to get 64/65/78/79 prescaler, the second

MUX should be equal to 1 means the control signal

sel of the second MUX should be equal to 1.

1) Case 1: sel='0'

When sel='0', the output from the NAND2

gate is directly transferred to the input of 4/5

prescaler and the multimodulus prescaler operates as

the normal 64/65 prescaler, where the division ratio is

controlled by the logic signal MOD. If MC=1, the 4/5

prescaler operates in the divide-by-2 mode and when

MC = 0, the 4/5 prescaler operates in the divide-by-3

mode. If MOD=1, the NAND2 gate output switches

to logic "1" (MC=1) and the wideband prescaler

operates in the divide-by-2 mode for entire operation.

The division ratio N performed by the multi modulus

prescaler is

N = (AD*N1) + (0*(N1+ 1)) = 64

Where N1=2 and AD=16 is fixed for the entire

design. If MOD = 0 , for 62 input clock cycles MC

remains at logic "1", where wideband prescaler

operates in divide-by-2 mode and for three input

clock cycles, MC remains at logic "0" where the

wideband prescaler operates in the Divide-by-3

mode. The division ratio N+ 1 performed by the

multi modulus prescaler is

N+l = ((AD - l)*N1) + (1 * (N1 +1)) = 65

International Association Of Engineering & Technology For Skill Development

22

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

S2 switch to logic "0" and the bit-cell does not

perform any function. The MOD signal goes

logically high only when the S-counter finishes

counting down to zero. If MOD and LD are logically

low, the bit-cell acts as a divide-by-2 unit. If MOD is

logically low and LD is logically high, the input bit

PI is transferred to the output. In the initial state,

MOD=0, the multimodulus prescaler selects the

divide-by-N+ 1 mode (divide-by-64 or 65)

2) Case 2: sel =' l'

When sel=' 1', the inverted output of the

NAND2 gate is directly transferred to the input of 4/5

prescaler and the multimodulus prescaler operate as a

64/65 prescaler, where the division ratio is controlled

by the logic signal MOD. If MC= 1, the 4/5 prescaler

operates in divide-by- 3 mode and when MC=0, the

4/5 prescaler operates in divide-by-2 mode which is

quite opposite to the operation performed when

sel='0' If MOD=1, the division ratio N+ 1 performed

by the multimodulus prescaler is same except that the

wideband prescaler operates in the divide by-3 mode

for the entire operation given by

ISBN : 978 - 1502851550

uses two additional transistors M6 and M7whose

inputs are controlled by the logic signal MOD. If

MOD is logically high, nodes S1 (divide-by-48 or

divide-by-79) and P, S counters start down counting

the input clock cycles. When the S-counter finishes

counting, MOD switches to logic "1" and the

prescaler changes to the divide-by-n mode (divideby-32 or divide-47 or divide-by-64 or divide-78) for

the remaining P-S clock cycles. During to a specified

value from 0 to 31 for the lower band and 0 to 48 for

the higher band of operation. this mode, since Scounter is idle, transistors M6 and M7 which are

controlled by MOD, keep the nodes S1 and S2 at

logic "0," thus saving the switching power in S

counter for a period of (N*(P-S)) clock cycles. Here,

the programmable input (PI) is used to load the

counter.

N + l = (AD * (N1+1)) + (0 * Nl) = 79

If MOD=1, the division ratio N performed by the

multimodulus prescaler is

N = ((AD - l ) * (N1 + 1)) + (1 * Nl)=78.

5. MULTIBAND FLEXIBLE DIVIDER

The single-phase clock multiband flexible

divider which is shown in Fig 1 consists of the multi

modulus 32/33/47/48or 64/65/78/79 prescaler, a 7-bit

programmable (P) counter and a 6-bit swallow(S)

counter. The control signal Sel decides whether the

divider is operating in lower frequency band (2.4

GHz) or higher band (5-5.825 GHz).

I .Swallow (S) Counter:

The 6-bit s-counter shown in Fig.4 consists of

six asynchronous loadable bit-cells, a NORembedded DFF and additional logic gates to allow it

to be programmable from 0 to 31 or 0 to 63 for lowfrequency band and from 0 to 47 or 0 to 78 for the

high-frequency band. The asynchronous bit cell used

in this design .It is similar to the bit-cell except it

Fig 4: Swallow (S) Counter

II. Programmable (P) Counter:

The programmable P-counter is a 7-bit

asynchronous down counter which consists of 7

loadable bit-cells and additional logic gates. Here, bit

P7 is tied to the Sel signal of the multi modulus

prescaler and bits P4 and P7 are always at logic "1."

The remaining bits can be externally programmed

from 75 to 78 for the lower frequency band and from

105 to 122 for the upper frequency band. When the

P-counter finishes counting down to zero, LD

switches to logic "1" during which the output of all

the bit-cells in S-counter switches to logic "1" and

output of the NOR embedded DFF switches to logic

"0" (MOD = 0) where the programmable divider get

International Association Of Engineering & Technology For Skill Development

23

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

reset to its initial state and thus a fixed division ratio

is achieved. If a fixed 32/33 (N/(N+ 1)) dual-modulus

prescaler is used, a 7 bit P counter is needed for the

low-frequency band (2.4 GHz) while an 8-bit Scounter would be needed for the high frequency

band(5-5.825 GHz) with a fixed 5-bit S counter.

Thus, the multimodulus 32/33/47/48 prescaler eases

the design complexity of the P-counter.

ISBN : 978 - 1502851550

cycles. Thus division ratio of 33(N+ 1) is performed.

N and N+ 1 are given by

N = (AD * N1) = 32

N + 1 = ((AD -1) * N1) + (1 * (N1 + 1)) = 33

2) When Sel=l:

When Sel=l, the inverted output from

NAND2 gate is given to the input of 2/3 prescaler

and multimodulus prescaler operates in 47/48 mode.

MOD signal controls the division ratio. When

MOD=1 and MC=1 prescaler operated in divide-by-3

for the entire input cycles and division ratio of 48

(N+l) is performed. When MOD=1 and MC=0

divideby-2 is selected for entire input clock cycles for

prescaler and the division ratio of 47(N) is

performed. N and N+l are given by

N = ((AD -1) * (N1 + 1)) + (1 * N1) = 47

N + 1 = (AD * (N1 + 1)) = 48

Fig 5: Programmable (P) Counter

6 .RESULTS AND CONCLUSION

TABLE I

PRESCALAR FREQUENCY DIVIDE RATIOS

1) When Sel='0':

When Sel='0' the output from NAND2 gate

is given to the prescaler and the multimodulus

prescaler selects 32/33 mode and the division ratio is

controlled by MOD signal. When MOD=1 the output

from NAND2 gate switches to logic' 1 ' and the

prescaler operates in divide-by-2 for entire operation.

i.e., now division ratio of 32 (N) is performed.

Similarly when MOD = 0, MC remains high for first

30 input clock cycles and goes low for 3 input clock

In order to get 64/65/78/79 clock cycles we need to

operate 4/5 prescaler by making the control signal sel

of second MUX to 1.To get 32/33/47/48 prescaler,

the second MUX should be equal to 0 means the

control signal sel of the second MUX should be equal

to 0 and to get 64/65/78/79 prescaler, the second

MUX should be equal to 1 means the control signal

sel of the second MUX should be equal to 1

3) When Sel='0':

When Sel='0' the output from NAND2 gate

is given to the prescaler and the multimodulus

prescaler selects 64/65 mode and the division ratio is

controlled by MOD signal. When MOD=1 the output

from NAND2 gate switches to logic' 1 ' and the

prescaler operates in divide-by-2 for entire operation.

i.e., now division ratio of 64 (N) is performed.

Similarly when MOD = 0, MC remains high for first

62 input clock cycles and goes low for 3 input clock

cycles. Thus division ratio of 65(N+ 1) is performed.

N and N+ 1 are given by

N = (AD * N1) = 64

N + 1 = ((AD -1) * N1) + (1 * (N1 + 1)) = 65

International Association Of Engineering & Technology For Skill Development

24

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

ISBN : 978 - 1502851550

4) When Sel=l:

When Sel=l, the inverted output from

NAND2 gate is given to the input of 2/3 prescaler

and multimodals prescaler operates in 78/79 mode.

MOD signal controls the division ratio. When

MOD=1 and MC=1 prescaler operated in divide-by-3

for the entire input cycles and division ratio of 79

(N+l) is performed. When MOD=1 and MC = 0

divideby-2 is selected for entire input clock cycles for

prescaler and the division ratio of 78(N) is

performed. N and N+l are given by

N = (( AD -1) * (N1 + 1)) + (1 * N1) = 78

N + 1 = (AD * (N1 + 1)) = 79

The results are shown below:

DIVIDE BY 32/33/47/48

PRESCALER 2/3

International Association Of Engineering & Technology For Skill Development

25

DIVIDE BY 64/65/78/79

www.iaetsd.in

Proceedings of International Conference On Current Innovations In Engineering And Technology

ISBN : 978 - 1502851550

7. CONCLUSION

In this paper a simple approach for the low

power multiband clock distribution using single

phase clock distribution for Wireless Local Area

Networks frequency synthesizer is presented. In this

project, a wideband 2/3 or 4/5 prescaler is verified by

the design of modified wide band multimodulus

32/33/47/48 or 64/65/78/79 prescaler. A dynamic

logic multiband flexible integer N divider is designed

which uses the wide band 2/3 prescaler,

multimodulus 32/33/47/48 or 64/65/78/79 prescaler.

The technique for low power fully programmable

divider using design of reloadable bit cells for P and

S Counter is given. P and S counters can be

programmed accordingly for the required bands of

frequencies, so that it provides solution to the low

power PLL synthesizers for Bluetooth, Zigbee, IEEE

802.15.4 and IEEE 802.11 a/b/g WLAN applications

with variable channel spacing. In this paper we

worked on the four modes like 32/33, 47/48, 64/65

and 78/79 prescaler. The future work will be

combining wide band 2/3 prescaler, 4/5 prescaler and

8/9 prescaler to provide six modes of operations like

32/33, 47/48, 64/65, 78/79, 128/129 and 143/144.

This means a wide band 2/3 or 4/5 or 8/9 prescaler is

verified by the design of multimodulus 32/33/47/48

or 64/65/78/79 or 128/129/143/144 prescaler in

future work. So future flexible divider controls more

number of frequency bands.

REFERENCES

[4] L. Lai Kan Leung et al., A 1-V 9.7-mW CMOS

Frequency

synthesizer

for

IEEE

802.11a

transceivers, IEEE Trans. Microwind. Theory Tech.,

vol. 56, no. I, pp. 39-48, Jan. 2008.

[5] M. Alioto and G. Palumbo, Model and Design of

Bipolar and MOS Current-Mode Logic Digital

Circuits. New York: Springer, 2005.

[6] Y. Jorgen etc all, "A true single-phase-clock

Dynamic CMOS circuit technique," IEEE J. SolidState Circuits, vol. 24, no. 2, pp. 62-70, Feb. 1989.

[7] S. Pellerano etc, A 13.5-mW 5 GHz frequency

synthesizer with dynamic-logic frequency divider,

IEEE J. Solid-State Circuits, vol. 39, no. 2, pp. 378383, Feb. 2004

[8] V. K. Manthena et al., A low power fully

programmable J MHz resolution 2.4 GHz CMOS

PLL frequency synthesizer, in Proc. IEEE Biomed.

Circuits Syst. Conf, Nov. 2007.pp 187-19.

[9] X.P.Y u et al., Design and optimization of the

extended true single phase clock based prescaler,

IEEE Trans. Microw. Theory Tech., vol.56, no. 11,

pp.3828-3835, Nov.2006.

[10] X.P.Y u et al., Design of a low power wideband

high resolution programmable frequency divider,

IEEE Trans. Very Large Scale Integr. (VLSI) Syst.,

vol.13, no. 9, pp.1098-1103, Sep.2005.

[1] Vamshi Krishna Manthena, Manh Anh Do, Chirn

Chye Boon, and Kiat Seng Yeo A Low-Power

Single-Phase Clock Multiband Flexible Divider ,

IEEE transactions on very large scale integration

(VLSI) systems, vol. 20, no. 2, February 2012.

[2] H.R.Rategh et al., A CMOS frequency

synthesizer with an injected locked frequency divider

for 5-GHz wireless LAN receiver, IEEE J. SolidState Circuits, vol. 35, no. 5, pp. 780-787, May 2000.

[3] P. Y. Deng et al., A 5GHz frequency synthesizer

with an injection locked frequency divider and

differential switched capacitors, IEEE Trans.

Circuits Syst. I, Reg. Papers, vol. 56, no. 2, pp. 320326, Feb. 2009.

International Association Of Engineering & Technology For Skill Development

26

www.iaetsd.in

Potrebbero piacerti anche

- Sediment Classification Using Side Scan SONARDocumento5 pagineSediment Classification Using Side Scan SONARiaetsdiaetsdNessuna valutazione finora

- Slow Intelligence System Based Software TestingDocumento6 pagineSlow Intelligence System Based Software TestingiaetsdiaetsdNessuna valutazione finora

- A Novel and Green Route For Synthesis of Pyrazoline Derivatives in An Aqueous Media by Using Ionic Liquid at Reflux ConditionDocumento4 pagineA Novel and Green Route For Synthesis of Pyrazoline Derivatives in An Aqueous Media by Using Ionic Liquid at Reflux ConditioniaetsdiaetsdNessuna valutazione finora

- IOT Based Waste Management System For Smart CityDocumento7 pagineIOT Based Waste Management System For Smart Cityiaetsdiaetsd100% (2)

- A Survey - Data Security and Privacy Big DataDocumento6 pagineA Survey - Data Security and Privacy Big DataiaetsdiaetsdNessuna valutazione finora

- Design of Transformer Peripharals by Computer Aided Design Drafting (Cadd)Documento8 pagineDesign of Transformer Peripharals by Computer Aided Design Drafting (Cadd)iaetsdiaetsdNessuna valutazione finora

- The Impact of Partition As Revealed in Bapsi Sidhwa's Ice Candy ManDocumento9 pagineThe Impact of Partition As Revealed in Bapsi Sidhwa's Ice Candy ManiaetsdiaetsdNessuna valutazione finora

- MHD Flow With Silver (Ag) and Titanium (TiO2) Water Based Nano Fluid Over A Non-Linearly Stretching/strinking SheetDocumento8 pagineMHD Flow With Silver (Ag) and Titanium (TiO2) Water Based Nano Fluid Over A Non-Linearly Stretching/strinking SheetiaetsdiaetsdNessuna valutazione finora

- Mathematical Model For Marangoni Convection MHD Flow of Carbon Nanotubes Through A Porous MediumDocumento7 pagineMathematical Model For Marangoni Convection MHD Flow of Carbon Nanotubes Through A Porous MediumiaetsdiaetsdNessuna valutazione finora

- In Vitro Propagation of Anisochilus Carnosus (LF.) Wallich - A Medicinal PlantDocumento3 pagineIn Vitro Propagation of Anisochilus Carnosus (LF.) Wallich - A Medicinal PlantiaetsdiaetsdNessuna valutazione finora

- A Review Paper On Online Restaurant Management System - Http://iaetsdjaras - OrgDocumento5 pagineA Review Paper On Online Restaurant Management System - Http://iaetsdjaras - OrgiaetsdiaetsdNessuna valutazione finora

- A Comparative Analysis of Income and Expenditure Pattern of Working and Non-Working Women in TamilnaduDocumento8 pagineA Comparative Analysis of Income and Expenditure Pattern of Working and Non-Working Women in TamilnaduiaetsdiaetsdNessuna valutazione finora

- Retrofitting of Reinforced Column by Using Ferrocement JacketingDocumento4 pagineRetrofitting of Reinforced Column by Using Ferrocement JacketingiaetsdiaetsdNessuna valutazione finora

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Barrel ShifterDocumento2 pagineBarrel Shifteraarthi100Nessuna valutazione finora

- Qca - b2g RepDocumento42 pagineQca - b2g Repsanoop joseNessuna valutazione finora

- Latches, Flip-Flops and TimerDocumento44 pagineLatches, Flip-Flops and TimerAbushe SolomonNessuna valutazione finora

- Electronics PDFDocumento41 pagineElectronics PDFSumerNessuna valutazione finora

- Bca SyllabusDocumento38 pagineBca SyllabusMohammed JeelanNessuna valutazione finora

- CPS213 - Chaptert 5 - Set1Documento24 pagineCPS213 - Chaptert 5 - Set1Duong Dinh KhanhNessuna valutazione finora

- TCL M113 Tmpa8809 MC4406 SMDocumento90 pagineTCL M113 Tmpa8809 MC4406 SMYanto LufiNessuna valutazione finora

- SABC167CSL40MDocumento81 pagineSABC167CSL40MEdson CostaNessuna valutazione finora

- Example 2.13 Problem: Determine The Output Waveform For The Truth Table As Shown BelowDocumento36 pagineExample 2.13 Problem: Determine The Output Waveform For The Truth Table As Shown BelowShuvoshreeNessuna valutazione finora

- Hardware Lecture 10Documento8 pagineHardware Lecture 10charles0% (1)

- Verilog Code For JK Flip FlopDocumento3 pagineVerilog Code For JK Flip FlopDarwin60% (10)

- Multiplexer 4 Inputs and Test BenchDocumento7 pagineMultiplexer 4 Inputs and Test BenchsagarNessuna valutazione finora

- MCQ in Computer Fundamentals Part 2 ECE Board ExamDocumento18 pagineMCQ in Computer Fundamentals Part 2 ECE Board ExamLuelson CordovaNessuna valutazione finora

- Archive: DatasheetDocumento45 pagineArchive: DatasheetRamon LopezNessuna valutazione finora

- Co Po DLCDocumento31 pagineCo Po DLCramachandranNessuna valutazione finora

- Name-Aarohan Verma Batch-Coe19 Rollno.101903497 Email-Averma2 - Be19@Thapar - Edu Assignment - 4Documento14 pagineName-Aarohan Verma Batch-Coe19 Rollno.101903497 Email-Averma2 - Be19@Thapar - Edu Assignment - 4Aarohan Verma50% (2)

- Lab E2 Group 22Documento7 pagineLab E2 Group 22Andy NgoNessuna valutazione finora

- 25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMDocumento22 pagine25AA040/25LC040/25C040: 4K Spi Bus Serial EEPROMAgustin AndrokaitesNessuna valutazione finora

- P3T32 en M F006 IEC Web PDFDocumento374 pagineP3T32 en M F006 IEC Web PDFMardiansyah AtrimaNessuna valutazione finora

- CS5532Documento50 pagineCS5532Héctor LiendoNessuna valutazione finora

- Good One - Standard Cell CharacterDocumento33 pagineGood One - Standard Cell CharacterGagandeep Singh DhingraNessuna valutazione finora

- Micom P642 Final Settings PDFDocumento10 pagineMicom P642 Final Settings PDFsupermannon100% (2)

- SIS: A System For Sequential Circuit SynthesisDocumento45 pagineSIS: A System For Sequential Circuit Synthesisrajat835Nessuna valutazione finora

- Vlsi Rec 7th Sem VtuDocumento50 pagineVlsi Rec 7th Sem VtuSagar S Poojary100% (1)

- Johnson Ring CounterDocumento8 pagineJohnson Ring CounterJohn Brix BalisterosNessuna valutazione finora

- PCD IB38-737-5 IssueF 122304Documento384 paginePCD IB38-737-5 IssueF 122304SpecForceNessuna valutazione finora

- ELEC-E3520 Digital Microelectronics I: Marko KosunenDocumento38 pagineELEC-E3520 Digital Microelectronics I: Marko KosunenMuhammad Royyan ZahirNessuna valutazione finora

- UC5895Documento8 pagineUC5895aniNessuna valutazione finora

- VLSI Front End Lab ManualDocumento88 pagineVLSI Front End Lab ManualAllanki Sanyasi RaoNessuna valutazione finora

- Third Semester SyllabusDocumento7 pagineThird Semester SyllabusVishu KukkarNessuna valutazione finora