Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Datasheet 74ls74

Caricato da

minhquyen_130689Descrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Datasheet 74ls74

Caricato da

minhquyen_130689Copyright:

Formati disponibili

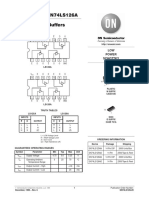

SN54/74LS74A

DUAL D-TYPE POSITIVE

EDGE-TRIGGERED FLIP-FLOP

The SN54 / 74LS74A dual edge-triggered flip-flop utilizes Schottky TTL cir-

cuitry to produce high speed D-type flip-flops. Each flip-flop has individual

clear and set inputs, and also complementary Q and Q outputs. DUAL D-TYPE POSITIVE

Information at input D is transferred to the Q output on the positive-going EDGE-TRIGGERED FLIP-FLOP

edge of the clock pulse. Clock triggering occurs at a voltage level of the clock

pulse and is not directly related to the transition time of the positive-going LOW POWER SCHOTTKY

pulse. When the clock input is at either the HIGH or the LOW level, the D input

signal has no effect.

J SUFFIX

LOGIC DIAGRAM (Each Flip-Flop) CERAMIC

CASE 632-08

14

1

SET (SD)

4 (10)

Q

5 (9)

CLEAR (CD)

1 (13) N SUFFIX

PLASTIC

CLOCK 14 CASE 646-06

3 (11)

Q 1

6 (8)

D

2 (12)

D SUFFIX

SOIC

14

1 CASE 751A-02

ORDERING INFORMATION

SN54LSXXJ Ceramic

MODE SELECT — TRUTH TABLE SN74LSXXN Plastic

SN74LSXXD SOIC

INPUTS OUTPUTS

OPERATING MODE

SD SD D Q Q

Set L H X H L

LOGIC SYMBOL

Reset (Clear) H L X L H

*Undetermined L L X H H 4 10

Load “1” (Set) H H h H L

Load “0” (Reset) H H l L H

2 D SD Q 5 12 D SD Q 9

* Both outputs will be HIGH while both SD and CD are LOW, but the output states are unpredictable

if SD and CD go HIGH simultaneously. If the levels at the set and clear are near VIL maximum then 3 11

CP CP

we cannot guarantee to meet the minimum level for VOH.

H, h = HIGH Voltage Level 6 8

L, I = LOW Voltage Level

CD Q CD Q

X = Don’t Care

i, h (q) = Lower case letters indicate the state of the referenced input (or output) one set-up time 1 13

i, h (q) = prior to the HIGH to LOW clock transition.

VCC = PIN 14

GND = PIN 7

FAST AND LS TTL DATA

5-72

SN54/74LS74A

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High 54, 74 – 0.4 mA

IOL Output Current — Low 54 4.0 mA

74 8.0

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter Min Typ Max Unit Test Conditions

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

All Inputs

54 0.7 Guaranteed Input LOW Voltage for

VIL Input LOW Voltage V

74 0.8 All Inputs

VIK Input Clamp Diode Voltage – 0.65 – 1.5 V VCC = MIN, IIN = – 18 mA

54 2.5 3.5 V VCC = MIN, IOH = MAX, VIN = VIH

VOH Output HIGH Voltage

74 2.7 3.5 V or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 4.0 mA VCC = VCC MIN,

VOL Output LOW Voltage VIN = VIL or VIH

74 0.35 0.5 V IOL = 8.0 mA per Truth Table

Input High Current

Data, Clock 20 µA VCC = MAX, VIN = 2.7 V

IIH Set, Clear 40

Data, Clock 0.1

mA VCC = MAX, VIN = 7.0 V

Set, Clear 0.2

Input LOW Current

IIL Data, Clock – 0.4 mA VCC = MAX, VIN = 0.4 V

Set, Clear – 0.8

IOS Output Short Circuit Current (Note 1) – 20 –100 mA VCC = MAX

ICC Power Supply Current 8.0 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C, VCC = 5.0 V)

Limits

Symbol Parameter Min Typ Max Unit Test Conditions

fMAX Maximum Clock Frequency 25 33 MHz Figure 1

VCC = 5.0 V

tPLH 13 25 ns

Clock, Clear, Set to Output Figure 1 CL = 15 pF

tPHL 25 40 ns

AC SETUP REQUIREMENTS (TA = 25°C)

Limits

Symbol Parameter Min Typ Max Unit Test Conditions

tW (H) Clock 25 ns Figure 1

tW (L) Clear, Set 25 ns Figure 2

Data Setup Time — HIGH 20 ns VCC = 5.0 V

ts Figure 1

Data Setup Time — LOW 20 ns

th Hold Time 5.0 ns Figure 1

FAST AND LS TTL DATA

5-73

SN54/74LS74A

AC WAVEFORMS

D* 1.3 V 1.3 V

th(H)

th(L)

ts(L) tW(H) ts(H)

tW(L)

1.3 V 1.3 V

CP

1

fMAX

tPHL tPLH

Q

1.3 V 1.3 V

tPHL

tPLH

1.3 V 1.3 V

Q

*The shaded areas indicate when the input is permitted to change for predictable output performance.

Figure 1. Clock to Output Delays, Data

Set-Up and Hold Times, Clock Pulse Width

tW

SET

1.3 V 1.3 V

tW

CLEAR

1.3 V 1.3 V

tPLH tPHL

1.3 V 1.3 V

Q

tPHL tPLH

Q

1.3 V 1.3 V

Figure 2. Set and Clear to Output Delays,

Set and Clear Pulse Widths

FAST AND LS TTL DATA

5-74

Potrebbero piacerti anche

- Dual D-Type Positive Edge-Triggered Flip-Flop SN54/74LS74A: Low Power SchottkyDocumento3 pagineDual D-Type Positive Edge-Triggered Flip-Flop SN54/74LS74A: Low Power Schottkygd8uj123100% (1)

- 74LS109Documento2 pagine74LS109jaja558Nessuna valutazione finora

- 74LS112Documento2 pagine74LS112jaja558Nessuna valutazione finora

- 74LS73N DatasheetDocumento3 pagine74LS73N DatasheetHennie SerfonteinNessuna valutazione finora

- 74LS113Documento2 pagine74LS113jaja558Nessuna valutazione finora

- 74LS76Documento2 pagine74LS76manjunath212coolNessuna valutazione finora

- SN74LS74A Dual D-Type Positive Edge-Triggered Flip-Flop: LOW Power SchottkyDocumento8 pagineSN74LS74A Dual D-Type Positive Edge-Triggered Flip-Flop: LOW Power SchottkyjannamuNessuna valutazione finora

- Sn74ls76a DDocumento5 pagineSn74ls76a Djuanmmm41Nessuna valutazione finora

- 74LS375Documento3 pagine74LS375jaja558Nessuna valutazione finora

- Dual JK Negative Edge-Triggered Flip-Flop SN54/74LS113A: Low Power SchottkyDocumento3 pagineDual JK Negative Edge-Triggered Flip-Flop SN54/74LS113A: Low Power SchottkyDivianisOktaviyaniNessuna valutazione finora

- Dual JK Negative Edge-Triggered Flip-Flop SN54/74LS114A: Low Power SchottkyDocumento4 pagineDual JK Negative Edge-Triggered Flip-Flop SN54/74LS114A: Low Power SchottkyThoif ZaraNessuna valutazione finora

- 74LS173Documento4 pagine74LS173jaja558Nessuna valutazione finora

- Quad D Flip-Flop SN54/74LS175: Low Power SchottkyDocumento5 pagineQuad D Flip-Flop SN54/74LS175: Low Power SchottkyNicolasNessuna valutazione finora

- 74LS112Documento4 pagine74LS112Rick CastilloNessuna valutazione finora

- Compuerta 74 LS132Documento3 pagineCompuerta 74 LS132richarbmwNessuna valutazione finora

- 74LS174Documento3 pagine74LS174jaja558Nessuna valutazione finora

- 74LS42 PDFDocumento3 pagine74LS42 PDFbeesahNessuna valutazione finora

- 74LS165Documento6 pagine74LS165jaja558Nessuna valutazione finora

- 74LS138 EdDocumento2 pagine74LS138 EdThiago AlvesNessuna valutazione finora

- Quad Set-Reset Latch SN54/74LS279: Low Power SchottkyDocumento5 pagineQuad Set-Reset Latch SN54/74LS279: Low Power Schottkytzf32799Nessuna valutazione finora

- 74LS242Documento3 pagine74LS242jaja558Nessuna valutazione finora

- 74LS125 PDFDocumento5 pagine74LS125 PDFneko1212121515123001Nessuna valutazione finora

- 74LS155Documento4 pagine74LS155jaja558Nessuna valutazione finora

- Datasheet Ic 74hc32aDocumento9 pagineDatasheet Ic 74hc32aNayla AzzahraNessuna valutazione finora

- 74 Ls 138Documento3 pagine74 Ls 138RushabhShahNessuna valutazione finora

- 74LS125ADocumento5 pagine74LS125Abl19cm7Nessuna valutazione finora

- 74LS125Documento3 pagine74LS125jaja558Nessuna valutazione finora

- Datasheet Ic 74hc165aDocumento9 pagineDatasheet Ic 74hc165aNayla AzzahraNessuna valutazione finora

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocumento6 pagineHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataMuhammad Rizwan Haider DurraniNessuna valutazione finora

- 74LS151Documento3 pagine74LS151Kang RoyNessuna valutazione finora

- Onsms12244 1Documento8 pagineOnsms12244 1HeartBraveNessuna valutazione finora

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDocumento6 pagineHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataAmirNessuna valutazione finora

- MC74HC04A Hex Inverter: High Performance Silicon Gate CMOSDocumento9 pagineMC74HC04A Hex Inverter: High Performance Silicon Gate CMOSjavierNessuna valutazione finora

- 74LS190Documento8 pagine74LS190jaja558Nessuna valutazione finora

- 74LS164Documento4 pagine74LS164jaja558Nessuna valutazione finora

- 74LS194 MotorolaDocumento4 pagine74LS194 MotorolawolfstarprojectsNessuna valutazione finora

- SN74LS00 Quad 2-Input NAND Gate: ESD 3500 VoltsDocumento16 pagineSN74LS00 Quad 2-Input NAND Gate: ESD 3500 VoltsChris KehayiasNessuna valutazione finora

- TTL Ic 7448Documento3 pagineTTL Ic 7448haseeb ahmad ch.0% (1)

- 4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyDocumento4 pagine4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyEden K.CNessuna valutazione finora

- 74LS377Documento5 pagine74LS377jaja558Nessuna valutazione finora

- HC74ADocumento7 pagineHC74AAnthony AndreyNessuna valutazione finora

- 74LS157Documento3 pagine74LS157jaja558Nessuna valutazione finora

- 74LS12Documento2 pagine74LS12jaja558Nessuna valutazione finora

- Anais Do Workshop De Micro-ondasDa EverandAnais Do Workshop De Micro-ondasNessuna valutazione finora

- Lenovo G50-45 NM-A281P ACLU5-ACLU6Documento61 pagineLenovo G50-45 NM-A281P ACLU5-ACLU6Sadiq Al-MohandisNessuna valutazione finora

- OckeybDocumento72 pagineOckeybAnonymous 1Rb4QLr100% (1)

- ActuatorsDocumento3 pagineActuatorselavarasanNessuna valutazione finora

- Octave Ultrasonic Installation - GuideDocumento16 pagineOctave Ultrasonic Installation - GuideCHRISTIAN JOSE BARRETO ROJASNessuna valutazione finora

- Mati Internship ReportDocumento26 pagineMati Internship ReportMėłkë Ýeśhtīla100% (3)

- Limit Switches: PresentationDocumento2 pagineLimit Switches: PresentationAlejandro NicolasNessuna valutazione finora

- Biological Effects of Electromagnetic Radiation-Radiowaves and Microwaves-Eurasian Communist CountriesDocumento35 pagineBiological Effects of Electromagnetic Radiation-Radiowaves and Microwaves-Eurasian Communist Countriesbasiliolik100% (2)

- Errors SCH-1 PDFDocumento946 pagineErrors SCH-1 PDFAshraful ShohagNessuna valutazione finora

- 3rd Edition Blue Book Electrical Section by John DallimoreDocumento6 pagine3rd Edition Blue Book Electrical Section by John Dallimoretynafkm08Nessuna valutazione finora

- Trends Periodic WorksheetDocumento1 paginaTrends Periodic WorksheetmydqueNessuna valutazione finora

- Nokia SamsungDocumento68 pagineNokia SamsungVarun JainNessuna valutazione finora

- GNU Radio lab: Instructor: Proff Do Trong Tuan Group: Kim Trung Hiếu Đỗ Thu Hà Tạ Thị Thanh Lâm DinaliDocumento36 pagineGNU Radio lab: Instructor: Proff Do Trong Tuan Group: Kim Trung Hiếu Đỗ Thu Hà Tạ Thị Thanh Lâm DinaliThanh LâmNessuna valutazione finora

- 1241 WS4 PDFDocumento76 pagine1241 WS4 PDFmoussa89% (9)

- Specifications - Appendix GDocumento141 pagineSpecifications - Appendix GRaziel VelazquezNessuna valutazione finora

- Earthquake Instrumentation For Nuclear FacilitiesDocumento13 pagineEarthquake Instrumentation For Nuclear FacilitiesPradana AnggaNessuna valutazione finora

- StudioLive Software Library Manual - EnglishDocumento150 pagineStudioLive Software Library Manual - Englishzeuta1Nessuna valutazione finora

- Somi Khan: Personal ObjectiveDocumento2 pagineSomi Khan: Personal ObjectivesomiNessuna valutazione finora

- RADAR BRIDGE MASTER ''E'' Series Radar Ship's ManualDocumento161 pagineRADAR BRIDGE MASTER ''E'' Series Radar Ship's Manualtoumassis_p100% (11)

- Panasonic Th-103pf9uk Th-103pf9ek CH Gpf9dDocumento121 paginePanasonic Th-103pf9uk Th-103pf9ek CH Gpf9dkrutologNessuna valutazione finora

- Micno Ke300a 01 Solar Pump Inverter CatalogDocumento8 pagineMicno Ke300a 01 Solar Pump Inverter CatalogIbrahima DialloNessuna valutazione finora

- SWOLE o CLOCK MANUAL !!!Documento2 pagineSWOLE o CLOCK MANUAL !!!Aleksandar DimovskiNessuna valutazione finora

- Access Is AKB500 Keyboard Getting Started GuideDocumento13 pagineAccess Is AKB500 Keyboard Getting Started GuideAnonymous f8GuYDh6Nessuna valutazione finora

- Plastic Caps Moulding Machine Production & MaintenanceDocumento204 paginePlastic Caps Moulding Machine Production & MaintenancePeter Calvo90% (10)

- Ensto Phase Balancer: Corrects Unbalanced Three Phase LoadDocumento5 pagineEnsto Phase Balancer: Corrects Unbalanced Three Phase LoadTBS Máy Phát ĐiệnNessuna valutazione finora

- Bubble PowerDocumento16 pagineBubble Powersachinsdurgad100% (1)

- 5kVA Dry Type Transformer SpecsDocumento1 pagina5kVA Dry Type Transformer SpecsKillua X Ma'rufNessuna valutazione finora

- Please Note That Cypress Is An Infineon Technologies CompanyDocumento22 paginePlease Note That Cypress Is An Infineon Technologies Company20c552244bNessuna valutazione finora

- Exp 6 SquidDocumento5 pagineExp 6 SquidNischayNessuna valutazione finora

- EDS - NDrive ManualDocumento115 pagineEDS - NDrive Manuallfba_16Nessuna valutazione finora

- Manual Sensor A B Sense GuardDocumento5 pagineManual Sensor A B Sense GuardMateus Rodolfo DiasNessuna valutazione finora