Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

THAT 4301 Datasheet

Caricato da

SaverioCorCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

THAT 4301 Datasheet

Caricato da

SaverioCorCopyright:

Formati disponibili

THAT Analog Engine

IC Dynamics Processor

THAT 4301

FEATURES

APPLICATIONS

High-Performance Blackmer

Voltage Controlled Amplifier

Compressors

Limiters

High-Performance RMS-Level

Detector

Gates

Expanders

Three General-Purpose Opamps

De-Essers

Wide Dynamic Range: >115 dB

Duckers

Low THD: <0.03%

Noise Reduction Systems

Low Cost

Wide-Range Level Meters

DIP & Surface-Mount Packages

Description

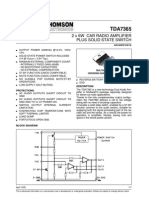

THAT 4301 Dynamics Processor, dubbed

THAT Analog Engine, combines in a single IC

all the active circuitry needed to construct a wide

range of dynamics processors. The 4301 includes

a high-performance, exponentially-controlled

VCA, a log-responding RMS-level sensor and

three general- purpose opamps.

The VCA provides two opposing-polarity,

voltage-sensitive control ports. Dynamic range

exceeds 115 dB, and THD is typically 0.003% at

0 dB gain. The RMS detector provides accurate

rms-to-dc conversion over an 80 dB dynamic

range for signals with crest factors up to 10. One

opamp is dedicated as a current-to-voltage

18

19

17

11

14

VCC

OA1

20

Model

20 pin

DIP

Package

20 pin

SO

Package

4301

4301P20-U

4301W20-U

OA3

EC+

EC-

The combination of exponential VCA gain

control and logarithmic detector response

decibel-linear response simplifies the mathematics of designing the control paths of dynamics

processors. This makes it easy to design audio

compressors, limiters, gates, expanders, deessers, duckers, noise reduction systems and the

like. The high level of integration ensures excellent temperature tracking between the VCA and

the detector, while minimizing the external parts

count.

12

13

SYM

VCA OUT

IN

converter for the VCA, while the other two may be

used for the signal path or control voltage

processing.

15

THAT4301

1

RMS

IN

16

IT

OUT

CT

OA2

GND VEE

4

10

Figure 1. Block Diagram

Table 2. Ordering Information

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation; Document 600069 Rev 08

Document 600069 Rev 08

Page 2 of 12

THAT4301Analog Engine

IC Dynamics Processor

SPECIFICATIONS 1,2

Absolute Maximum Ratings (T A =25C) 3

Positive Supply Voltage (VCC)

Negative Supply Voltage (VEE)

Supply Current (ICC)

+18 V

-18 V

20 mA

Power Dissipation (PD) (TA = 75C)

Operating Temperature Range (TOP)

Storage Temperature Range (TST)

700 mW

0 to +70 C

-40 to +125 C

Overall Electrical Characteristics

Parameter

Symbol

Conditions

Min

Typ

Max

Units

Positive Supply Voltage

VCC

+7

+15

Negative Supply Voltage

VEE

-7

-15

Positive Supply Current

ICC

12

18

mA

Negative Supply Current

IEE

-12

-18

mA

VCA Electrical Characteristics 4

Parameter

Symbol

Conditions

Min

Typ

Max

Units

IB(VCA)

No Signal

30

400

pA

Input Offset Voltage

VOFF(VCA In)

No Signal

15

mV

Input Signal Current

IIN(VCA) or IOUT(VCA)

175

750

Arms

Input Bias Current

Gain at 0V Control

G0

EC+ = EC = 0.000V

-0.4

0.0

+0.4

dB

EC+/Gain (dB)

EC-/Gain (dB)

TA = 25C (TCHIP @ 55C)

-60 dB < gain < +40dB

EC+ & SYM

EC-

6.4

-6.4

6.5

-6.5

6.6

-6.6

mV/dB

mV/dB

EC / TCHIP

Ref TCHIP= 27C

+0.33

%/C

-60 to +40 dB gain

0.5

110

115

dB

1

2

5

3

10

25

mV

mV

mV

20

20 Hz-20 kHz

Rout = 20k

0 dB gain

+15 dB gain

-96

-85

-94

-83

dBV

dBV

VIN= 0 dBV, 1 kHz

0 dB gain

0.003

0.007

Gain-Control Constant

Gain-Control TempCo

Gain-Control Linearity

Off Isolation

Output Offset Voltage Change

Gain Cell Idling Current

Output Noise

Total Harmonic Distortion

EC+=SYM=-375mV, EC-=+375mV

VOFF(OUT)

Rout = 20k

0 dB gain

+15 dB gain

+30 dB gain

IIDLE

en(OUT)

THD

1. All specifications are subject to change without notice.

2. Unless otherwise noted, T A=25C, VCC=+15V, VEE=-15V; VCASYM adjusted for min THD @ 1V, 1 kHz, 0 dB gain.

3. If the device is subjected to stress above the Absolute Maximum Ratings, permanent damage may result. Sustained operation at or near

the Absolute Maximum Ratings conditions is not recommended. In particular, like all semiconductor devices, device reliability declines

as operating temperature increases.

4. Test circuit is the VCA section only from Figure 2.

5. Except as noted, test circuit is the RMS-Detector section only from Figure 2.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 3 of 12

THAT4301 Analog Engine

IC Dynamics Processor

SPECIFICATIONS 1,2 (Cont'd.)

VCA Electrical Characteristics 4 (Cont'd.)

Parameter

Symbol

Total Harmonic Distortion (contd.) THD

Symmetry Control Voltage

VSYM

Conditions

VIN = +10 dBV, 1 kHz

0 dB gain

15 dB gain

VOUT= +10 dBV, 1 kHz

+15 dB gain

minimum THD

Min

Typ

Max

Units

0.03

0.035

0.07

0.09

%

%

0.035

0.09

-2.5

+2.5

mV

RMS Detector Electrical Characteristics 5

Parameter

Symbol

Conditions

Min

Typ

Max

Units

IB (RMS)

No Signal

30

400

pA

Input Offset Voltage

VOFF(RMS In)

No Signal

15

mV

Input Signal Current

IIN(RMS)

175

750

Input Bias Current

Input Current for 0 V Output

Output Scale Factor

Iin0

IT= 7.5 A

8.5

12

EO / 20log(Iin/Iin0)

31.6nA< IIN< 1mA

TA= 25C (TCHIP 55C)

6.4

6.5

6.6

mV/dB

-20 dB < VCA Gain < +20 dB

1A<Iin (DET)<100A

.985

1.015

fIN = 1kHz

1A < Iin< 100A

100nA < Iin< 316A

31.6nA < Iin< 1mA

0.1

0.5

1.5

dB

dB

dB

fIN = 100 Hz, = .001 s

1A< Iin < 100A

20

20

1ms pulse repetition rate

0.2 dB error

0.5 dB error

1.0 dB error

3.5

5

10

Iin 10mA

Iin 3mA

Iin 300nA

100

45

7

kHz

kHz

kHz

1.5

7.5

15

IT = 7.5 A

-10

+20

+50

mV

ICT/IT

IT = 7.5 A

0.90

1.1

1.30

TCHIP = 55C

Eo / TCHIP

Re: TCHIP = 27C

0.33

%/C

IOUT

300mV < VOUT< +300mV

90

100

Scale Factor Match (RMS to VCA)

Output Linearity

Rectifier Balance

Crest Factor

Maximum Frequency for 2 dB Additional Error

Timing Current Set Range

IT

Voltage at IT Pin

Timing Current Accuracy

Filtering Time Constant

Output Temp. Coefficient

Output Current

(0.026 ) CI TT

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 4 of 12

THAT4301Analog Engine

IC Dynamics Processor

SPECIFICATIONS 1,2 (Cont'd.)

Opamp Electrical Characteristics 6

Parameter

Symbol

Input Offset Voltage

Conditions

Min

OA1

Typ Max

Min

OA2

Typ Max

Min

OA3

Typ Max

Units

VOS

0.5

0.5

0.5

mV

Input Bias Current

IB

150

500

150

500

150

500

nA

Input Offset Current

IOS

15

50

15

50

N/A

nA

Input Voltage Range

IVR

13.5

13.5

N/A

RS<10k

100

100

N/A

Common Mode Rej. Ratio CMRR

Power Supply Rej. Ratio

PSRR

VS=7V to 15V

100

100

100

Gain Bandwidth Product

GBW

(@50kHz)

AVO

RL=10k

RL=2k

115

N/A

110

N/A

125

120

13

N/A

13

N/A

14

13

V

V

12

mA

V/s

Open Loop Gain

Output Voltage Swing

VO@RL=5k

VO@RL=2k

Short Circuit Output Current

Slew Rate

SR

Total Harmonic Distortion

THD

1kHz, AV=1, RL=10k

1kHz, AV=1, RL= 2k

0.0007 0.003

N/A

0.0007 0.003

N/A

0.0007 0.003

0.0007 0.003

Input Noise Voltage Density en

fO=1kHz

6.5

10

7.5

12

7.5

12

Input Noise Current Density in

fO=1kHz

0.3

0.3

0.3

6. Test circuit for opamps is a unity-gain follower configuration with loaded resistor R L as specified.3

+15V

R5

VCA SYM

50K

-15V

SIGNAL

IN

C1

C2

R1

47pF

R4

300K

20K0 1%

47uF

R3

R2

51

20K0 1%

+15V

C7

SYM

OA1

VCC

C8

C3

47uF

IN

100n

VCA

OUT

EC+

EC-

SIGNAL

OUT

OA3

THAT4301

VEE

100n

-15V

R6

RMS

IN

+

OA2

OUT

Ct

It

GND

10K0 1%

C6

R7

2M00

1%

22uF

C4

10uF

RMS

OUT

Ec-

-15V

Figure 2. VCA and RMS detector test circuit

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

MHz

%

%

Document 600069 Rev 08

Page 5 of 12

THAT4301 Analog Engine

IC Dynamics Processor

REPRESENTATIVE DATA

dB

GAIN

10

%THD+N

20

0

-20

0.1

-40

-60

0.01

-80

-100

-200

mV

600

400

200

0.001

0.5

Figure 3. VCA Gain vs. Control Voltage (Ec-) at 25C

10

Figure 4. VCA 1kHz THD+Noise vs. Input, -15 dB Gain

%THD+N

10

0.1

0.1

0.01

0.01

Vin

rms

0.001

0.1

%THD+N

0.001

0.5

Figure 5. VCA 1kHz THD+Noise vs. Input, +15 dB Gain

1

Vin

rms

10

1.0

Vin

rms

10

1.0

Figure 6. VCA 1kHz THD+Noise vs. Input, 0 dB Gain

%THD+N

mV Out

300

Note: 0 dBr = 85 m Vrms

200

0.1

100

0

-100

0.01

-200

1kHz

-300

0.001

20

100

1k

10k

Hz

20k

Figure 7. VCA THD vs. Frequency, 0 dB Gain, 1Vrms Input

30

mV Error

-40

20

40

mV Out

+40 dBr

+30 dBr

200

20

dBr

In

-20

Figure 8. RMS Output vs. Input Level, 1 kHz & 10 kHz

300

Note: 0 dBr = 85 m Vrms

10kHz

-400

-60

+20 dBr

100

+10 dBr

10

0 dBr

-10 dBr

0

-100

-20 dBr

-30 dBr

-10

-200

-40 dBr

-20

-60

dBr

In

-40

-20

20

40

Figure 9. Departure from Ideal Detector Law vs. Level

-300

20

100

1k

10k

Hz

20k

Figure 10. Detector Output vs. Frequency at Various Levels

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 6 of 12

THAT4301Analog Engine

IC Dynamics Processor

Theory of Operation

THAT 4301 Dynamics Processor combines THAT

Corporations proven Voltage-Controlled Amplifier

(VCA) and RMS-Level Detector designs with three

general-purpose opamps to produce an Analog

Engine useful in a variety of dynamics processor

applications. For details of the theory of operation of

the VCA and RMS-Detector building blocks, the interested reader is referred to THAT Corporations data

sheets on the 2180 Series VCAs and the 2252 RMSLevel Detector. Theory of the interconnection of

exponentially-controlled VCAs and log-responding

level detectors is covered in THAT Corporations

application note AN101, The Mathematics of LogBased Dynamic Processors.

The VCA in Brief

THAT 4301 VCA is based on THAT Corporations

highly successful complementary log-antilog gain cell

topology, as used in THAT 2180-Series IC VCAs.

THAT

4301

is

integrated

using

a

fully

complementary, BiFET process. The combination of

FETs with high-quality, complementary bipolar transistors (NPNs and PNPs) allows additional flexibility

in the design of the VCA over previous efforts.

Input signals are currents to the VCA IN pin. This

pin is a virtual ground, so in normal operation an

input voltage is converted to input current via an

appropriately sized resistor (R1 in Figure 2, Page 4).

Because dc offsets present at the input pin and any

dc offset in preceeding stages will be modulated by

gain changes (thereby becoming audible as thumps),

the input pin is normally ac-coupled (C1 in Figure 2).

The VCA output signal is also a current, inverted

with respect to the input current. In normal operation, the output current is converted to a voltage via

inverter OA3, where the ratio of the conversion is

determined by the feedback resistor (R2, Figure 2)

connected between OA3s output and its inverting

input. The signal path through the VCA and OA3 is

noninverting.

The gain of the VCA is controlled by the voltage

applied to EC, EC+, and SYM. Gain (in decibels) is

proportional to EC+ EC-, provided EC+ and SYM are

at essentially the same voltage (see below). The constant of proportionality is 6.5 mV/dB for the voltage

at EC, and 6.5 mV/dB for the voltage at EC+ and SYM.

needed to drive the positive VCA control port; circuitry associated with OA1, OA2 and the RMS detector has been omitted.

R5

50K

Positive Control In

C1

C2 47pF

R1

Signal In

47uF

VCA SYM

20K0 1%

R3

R4

300K

OA1

+

IN

VCA

EC-

R2

20K0 1%

51

SYM

OUT

EC+

OA3

+

Signal

Out

THAT4301

VCC

VEE

IN

It

RMS

OUT

Ct

GND

+

OA2

-

Figure 11. Driving the VCA via the Positive Control Port

While the 4301s VCA circuitry is very similar to

that of the THAT 2180 Series VCAs, there are several

important differences, as follows:

1) Supply current for the VCA is fixed internally.

Approximately 2 mA is available for the sum of input

and output signal currents. (This is also the case in a

2180 Series VCA when biased as recommended.)

2) The signal current output of the VCA is internally connected to the inverting input of an on-chip

opamp. In order to provide external feedback around

this opamp, this node is brought out to a pin.

3) The control-voltage constant is approximately

6.5 mV/dB, due primarily to the higher internal operating temperature of the 4301 compared to that of

the 2180 Series.

4) The input stage of the 4301 VCA uses integrated P-channel FETs rather than a bias-current

corrected bipolar differential amplifier. Input bias

currents have therefore been reduced.

The RMS Detector in Brief

As mentioned, for proper operation, the same

voltage must be applied to EC+ and SYM, except for a

small (2.5 mV) dc bias applied between these pins.

This bias voltage adjusts for internal mismatches in

the VCA gain cell which would otherwise cause small

differences between the gain of positive and negative

half-cycles of the signal. The voltage is usually

applied via an external trim potentiometer (R5 in Figure 2), which is adjusted for minimum signal distortion at unity (0 dB) gain.

The 4301s detector computes rms level by rectifying input current signals, converting the rectified

current to a logarithmic voltage, and applying that

voltage to a log-domain filter. The output signal is a

dc voltage proportional to the decibel-level of the rms

value of the input signal current. Some ac component

(at twice the input frequency) remains superimposed

on the dc output. The ac signal is attenuated by a logdomain filter, which constitutes a single-pole rolloff

with cutoff determined by an external capacitor and a

programmable dc current.

The VCA may be controlled via EC-, as shown in

Figure 2, or via the combination of EC+ and SYM.

This connection is illustrated in Figure 11. Note that

this figure shows only that portion of the circuitry

As in the VCA, input signals are currents to the

RMS IN pin. This input is a virtual ground, so a

resistor (R6 in Figure 2) is normally used to convert

input voltages to the desired current. The level

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 7 of 12

detector is capable of accurately resolving signals

well below 10 mV (with a 10 k input resistor). However, if the detector is to accurately track such lowlevel signals, ac coupling is normally required.

The log-domain filter cutoff frequency is usually

placed well below the frequency range of interest. For

an audio-band detector, a typical value would be

5 Hz, or a 32 ms time constant (). The filters time

constant is determined by an external capacitor

attached to the CT pin, and an internal current

source (ICT) connected to CT. The current source is

programmed via the IT pin: current in IT is mirrored

to ICT with a gain of approximately 1.1. The resulting

time constant is approximately equal to 0.026 CT/IT.

Note that, as a result of the mathematics of RMS

detection, the attack and release time constants are

fixed in their relationship to each other.

The dc output of the detector is scaled with the

same constant of proportionality as the VCA gain

control: 6.5 mV/dB. The detectors 0 dB reference

(Iin0, the input current which causes 0 V output), is

determined by IT as follows: I in0 = 9.6 A I T The

detector output stage is capable of sinking or

sourcing 100 A.

Differences between the 4301s RMS-Level Detector circuitry and that of the THAT 2252 RMS Detector are as follows:

1) The rectifier in the 4301 RMS Detector is internally balanced by design, and cannot be balanced via

an external control. The 4301 will typically balance

positive and negative halves of the input signal within

1.5%, but in extreme cases the mismatch may

reach 15%. However, a 15% mismatch will not significantly increase ripple-induced distortion in

dynamics processors over that caused by signal ripple alone.

2) The time constant of the 4301s RMS detector

is determined by the combination of an external

capacitor (connected to the CT pin) and an internal,

programmable current source. The current source is

THAT4301 Analog Engine

IC Dynamics Processor

equal to 1.1 IT. Normally, a resistor is not connected

directly to the CT pin on the 4301.

3) The 0 dB reference point, or level match, is not

adjustable via an external current source. However,

as in the 2252, the level match is affected by the timing current, which, in this case, is drawn from the IT

pin and mirrored internally to CT.

4) The input stage of the 4301 RMS detector uses

integrated P-channel FETs rather than a bias-current

corrected bipolar differential amplifier. Input bias

currents are therefore negligible, improving performance at low signal levels.

The Opamps in Brief

The three opamps in the 4301 are intended for

general purpose applications. All are 5 MHz opamps

with slew rates of approximately 2V/s. All use bipolar PNP input stages. However, the design of each is

optimized for its expected use. Therefore, to get the

most out of the 4301, it is useful to know the major

differences among these opamps.

OA3, being internally connected to the output of

the VCA, is intended for current-to-voltage conversion. Its input noise performance, at 7.5nV/ Hz ,

complements that of the VCA, adding negligible noise

at unity gain. Its output section is capable of driving

a 2 k load to within 2V of the power supply rails,

making it possible to use this opamp directly as the

output stage in single-ended designs.

OA1 is the quietest opamp of the three. Its input

noise voltage, at 6.5nV/ Hz , makes it the opamp

of choice for input stages. Note that its output drive

capability is limited (in order to reduce the chips

power dissipation) to approximately 3 mA. It is

comfortable driving loads of 5 k or more to within

1V of the power supply rails.

OA2 is intended primarily as a control-voltage

processor. Its input noise parallels that of OA3, and

its output drive capability parallels that of OA1.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 8 of 12

THAT4301Analog Engine

IC Dynamics Processor

Applications

The circuit of Figure 12 shows a typical application for THAT 4301. This simple compressor/

limiter design features adjustable hard-knee

threshold, compression ratio, and static gain1.

The applications discussion in this data sheet will

center on this circuit for the purpose of illustrating important design issues. However, it is posslble to configure many other types of dynamics

processors with THAT 4301. Hopefully, the following discussion will imply some of these

possibilities.

as thumps. Note that C1, in conjunction with R1,

will set the low frequency limit of the circuit.

The VCA output is connected to OA3, configured as

an inverting current-to-voltage converter. OA3s feedback

components (R2, 20 k, and C2, 47 pf) determine the

constant of current-to-voltage conversion. The simplest

way to deal with this is to recognize that when the VCA

is set for unity (0 dB) gain, the input to output voltage

gain is simply R2/R1, just as in the case of a single inverting stage. If, for some reason, more than 0 dB gain is

required when the VCA is set to unity, then the resistors

may be skewed to provide it. Note that the feedback

capacitor (C2) is required for stability. The VCA output

has approximately 45 pf of capacitance to ground,

which must be neutralized via the 47 pf feedback

capacitor across R2.

Signal Path

As mentioned in the section on theory, the VCA

input pin is a virtual ground with negative feedback provided internally. An input resistor (R1,

20k) is required to convert the ac input voltage

to a current within the linear range of the 4301.

(Peak VCA input currents should be kept under

1 mA for best distortion performance.) The coupling capacitor (C1, 47 f) is strongly recommended to block dc current from preceding stages

(and from offset voltage at the input of the VCA).

Any dc current into the VCA will be modulated by

varying gain in the VCA, showing up in the output

VCA SYM

C1

R1

47uF

20K0 1%

+15

CCW

The VCA gain is controlled via the EC terminal,

whereby gain will be proportional to the negative of the

voltage at EC. The EC+ terminal is grounded, and the

SYM terminal is returned nearly to ground via a small

resistor (R3, 51 ). The VCA SYM trim (R5, 50 k)

allows a small voltage to be applied to the SYM terminal

via R4 (300 k). This voltage adjusts for small mismatches within the VCA gain cell, thereby reducing evenorder distortion products. To adjust the trim, apply to

R5

50K

R9

THRESHOLD

R11

R12

10K

383K 1%

R10

CW

-15

10K0 1%

C9

+15

22p

R4

300K

CR2

R2

51

CR1

20K0 1%

2M00 1%

-15

R8

C7

4k99 1%

+15

100n

C8

100n

IN

C3

CW

IN

EC-

SYM

VCA OUT

EC+

-15 R6

IN

IT

RMS OUT

CT

10K0 1%

R14

1K43

1%

22uF

GND

OUT

+

OA2

R16

R7

2M00

1%

4k99 1%

C4

10uF

C5

100N

-15

R17

R15

CCW

OA3

+

THAT4301

VCC

C6

R13

10K

OA1

+

VEE

47uF

COMPRESSION

47pF

C2

R3

10K0

1%

590K

1%

+15

GAIN

CW

R18

10K

CCW

-15

Figure 12. Typical Compressor/Limiter Application Circuit

1. More information on this compressor design, along with suggestions for converting it to soft-knee operation, is given in THAT Design

Note DN00A, Basic Compressor Limiter Design. The designs in DN00A are based on THAT Corporations 2180-Series VCAs and 2252

RMS Detector, but are readily adaptable to the 4301 with only minor modifications. In fact, the circuit presented here is functionally

identical to the hard-knee circuit published in DN00A.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 9 of 12

the input a middle-level, middle-frequency signal (1 kHz

at 1 V is a good choice with this circuit) and observe

THD at the signal output. Set the trim for minimum

THD.

RMS-Level Detector

The RMS detectors input is similar to that of the

VCA. An input resistor (R6, 10 k) converts the ac

input voltage to a current within the linear range of

the 4301. (Peak detector input currents should be

kept under 1 mA for best linearity.) The coupling

capacitor (C3, 47 f) is recommended to block dc

current from preceeding stages (and from offset voltage at the input of the detector). Any dc current into

the detector will limit the low-level resolution of the

detector, and will upset the rectifier balance at low

levels. Note that, as with the VCA input circuitry, C3

in conjunction with R6 will set the lower frequency

limit of the detector.

The time response of the RMS detector is determined by the capacitor attached to CT (C4, 10 f) and

the size of the current in pin IT (determined by R7,

2 M and the negative power supply, 15V). Since

the voltage at IT is approximately 0 V, the circuit of

Figure 12 produces 7.5 A in IT. The current in IT is

mirrored with a gain of 1.1 to the CT pin, where it is

available to discharge the timing capacitor (C4). The

combination produces a log filter with time constant

equal to approximately 0.026 CT/IT (~35 ms in the

circuit shown).

The waveform at CT will follow the logged

(decibel) value of the input signal envelope, plus a dc

offset of about 1.3 V (2 VBE). This allows a polarized

capacitor to be used for the timing capacitor, usually

an electrolytic. The capacitor used should be a lowleakage type in order not to add significantly to the

timing current.

The output stage of the RMS detector serves to

buffer the voltage at CT and remove the 1.3 V dc offset, resulting in an output centered around 0 V for

input signals of about 85 mV. The output voltage

increases 6.5 mV for every 1 dB increase in input signal level. This relationship holds over more than a

60 dB range in input currents.

Control Path

A compressor/limiter is intended to reduce its

gain as signals rise above a threshold. The output of

the RMS detector represents the input signal level

over a wide range of levels, but compression only

occurs when the level is above the threshold. OA1 is

configured as a variable threshold detector to block

envelope information for low-level signals, passing

only information for signals above threshold.

OA1 is an inverting stage with gain of 2 above

threshold and 0 below threshold. Neglecting the

action of the THRESHOLD control (R12) and its associated resistors (R11 and R10), positive signals from

the RMS detector output drive the output of OA1

negative. This forward biases CR2, closing the feedback loop such that the junction of R9 and CR2 (the

THAT4301 Analog Engine

IC Dynamics Processor

output of the threshold detector) sits at -(R9/R8)

RMSOUT. For the circuit of Figure 12, this is

2 RMSOUT. Negative signals from the RMS detector

drive the output of OA1 positive, reverse biasing CR2

and forward biasing CR1. In this case, the junction of

R9 and CR2 rests at 0 V, and no signal level informaion is passed to the threshold detectors output.

In order to vary the threshold, R12, the THRESHOLD control, is provided. Via R11 (383 k), R12 adds

up to 39.2 A of current to OA1s summing

junction, requiring the same amount of oppositepolarity current from the RMS detector output to

counterbalance it. At 4.99 k, the voltage across R8

required to produce a counterbalancing current is

195 mV, which represents a 30 dB change in

RMS detector input level.

Since the RMS detectors 0 dB reference level is

85 mV, the center of the THRESHOLD pots range

would be 85 mV, were it not for R10 (2 M), which

provides an offset. R10 adds an extra 7.5 A to OA1s

summing junction, which would be counterbalanced

by 37.4 mV at the detector output. This corresponds

to 5.8 dB, offsetting the THRESHOLD center by this

much to 165 mV, or approximately -16 dBV.

The output of the threshold detector represents

the signal level above the determined threshold, at a

constant of about 13 mV/dB (from [R9/R8] 6.5mV/dB).

This signal is passed on to the COMPRESSION control (R13), which variably attenuates the signal passed

on to OA2. Note that the gain of OA2, from the wiper

of the COMPRESSION control to OA2s output, is

R16/R15 (0.5), precisely the inverse of the gain of OA1.

Therefore, the COMPRESSION control lets the user

vary the above-threshold gain between the RMS

detector output and the output of OA1 from zero to a

maximum of unity.

The gain control constant of the VCA, 6.5 mV/dB,

is exactly equal to the output scaling constant of the

RMS detector. Therefore, at maximum COMPRESSION, above threshold, every dB increase in input

signal level causes a 6.5 mV increase in the output of

OA2, which in turn causes a 1 dB decrease in the

VCA gain. With this setting, the output will not

increase despite large increases in input level above

threshold. This is infinite compression. For intermediate settings of COMPRESSION, a 1 dB increase in

input signal level will cause less than a 1 dB decrease

in gain, thereby varying the compression ratio.

The resistor R14 is included to alter the taper of

the COMPRESSION pot to better suit common use. If

a linear taper pot is used for R13, the compression

ratio will be 1:2 at the middle of the rotation. However, 1:2 compression in an above-threshold compressor is not very strong processing, so 1:4 is often

preferred at the midpoint. R14 warps the taper of R13

so that 1:4 compression occurs at approximately the

midpoint of R13s rotation.

The GAIN control (R18) is used to provide static

gain or attenuation in the signal path. This control

adds up to 130 mV offset to the output of OA2

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

R 16

Page 10 of 12

R 16

(from V + R 17 to V R 17 ), which is approximately

20 dB change in gain of the VCA. C5 is used to

attenuate the noise of OA2, OA1 and the resistors R8

through R16 used in the control path. All these active

and passive components produce noise which is

passed on to the control port of the VCA, causing

modulation of the signal. By itself, the 4301 VCA produces very little noise modulation, and its performance can be significantly degraded by the use of noisy

components in the control voltage path.

Overall Result

The resulting compressor circuit provides hardknee compression above threshold with three essential user-adjustable controls. The threshold of

compression may be varied over a 30 dB range

from about 46 dBV to +14 dBV. The compression

ratio may be varied from 1:1 (no compression) to

THAT4301Analog Engine

IC Dynamics Processor

:1. And, static gain may be added up to 20 dB.

Audio performance is excellent, with THD running

below 0.05% at middle frequencies even with 10 dB

of compression, and an input dynamic range of over

115 dB.

Perhaps most important, this example design

only scratches the surface of the large body of applications circuits which may be constructed with THAT

4301. The combination of an accurate, widedynamic-range, log-responding level detector with a

high-quality, exponentially-responding VCA produces

a versatile and powerful analog engine. The opamps

provided in the 4301 enable the designer to configure

these building blocks with few external components

to construct gates, expanders, de-essers, noise reduction systems and the like.

For further information, samples and pricing,

please contact us at the address below.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 11 of 12

THAT4301 Analog Engine

IC Dynamics Processor

Package Characteristics

Parameter

Symbol

Thru Hole Package

JA

Thermal Resistance

Conditions

Typ

See below for pinout and dimensions

20 pin DIP

DIP package soldered to board

65

Environmental Regulation Compliance

C/W

Complies with RoHS requirements

Surface Mount Package

JA

Thermal Resistance

Units

See below for pinout and dimensions

20 pin SO

SO package soldered to board

70

Soldering Reflow Profile

C/W

JEDEC JESD22-A113-D (260 C)

Moisture Sensitivity Level

MSL

Environmental Regulation Compliance

20

Complies with RoHS requirements

11

C

1

10

E1

A

D

O

G

c

A2

SEATING

PLANE

L1

A1

b x 20

SYM

A

B

C

D

E

F

G

H

J

L

N

O

P

Inches

MM

Min

Max

1.025

1.035

0.300 BSC

0.245

0.255

0.300

0.325

0.100 BSC

0.014

0.022

0.005

0.045

0.070

0.320

0.380

0.125

0.135

0.015

0.025

0.115

0.150

0.008

0.012

Min

Max

26.04

26.29

7.62 BSC

6.23

6.48

7.62

8.26

2.54 BSC

0.36

0.56

0.12

1.14

1.78

8.12

9.64

3.18

3.43

0.38

0.64

2.92

3.81

0.20

0.30

Figure 13. 20 pin DIP package outline

Pin Name

RMS IN

IT

No Internal Connection

RMS OUT

CT

OA2 -IN

OA2 OUT

OA2 +IN

GND

VEE

Pin Number

1

2

3

4

5

6

7

8

9

10

SYM

A

A1

A2

b

c

D

E1

E

e

L

L1

Inches

Min

Max

0.096

0.104

0.005

0.012

0.089

0.096

0.012

0.020

0.008

0.030

0.502

0.510

0.291

0.299

0.396

0.416

0.050 TYP

0.016

0.050

0.051

0.059

0

8

MM

Min

Max

2.43

2.64

0.13

0.30

2.26

2.44

0.30

0.50

0.20

0.76

12.75

12.95

7.39

7.60

10.05

10.57

1.27 TYP

0.41

1.27

1.29

1.50

0

8

Figure 14. 20 pin SO package outline

Pin Name

OA1 +IN

OA1 -IN

OA1 OUT

VCA IN

ECEC+

SYM

VCA OUT

OA3 OUT

VCC

Pin Number

20

19

18

17

16

15

14

13

12

11

Table 2. THAT 4301 pin assignments

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Document 600069 Rev 08

Page 12 of 12

THAT4301Analog Engine

IC Dynamics Processor

Revision History

Revision

ECO

Date

Changes

00

6/24/1999

01

7/5/2006

02

8/24/2007

Added missing pin numbers to Table 2

Corrected symbols in specs.

03

1/26/2009

Corrected equation typos in the opamp section.

04

2748

12/10/2012

Corrected typo. in the surface mount package diagram.

05

2849

1/28/2014

Moved Package Characteristics and Outline drawings to page 11.

06

2855

3/10/2014

Corrected pin assignments in Table 2.

11

07

2866

3/31/2014

Added watermark that A version is discontinued.

08

2867

4/1/2014

Removed 'A' version, Chg'd lead finish, added 20p SO Wide pkg

Initial release.

Added C9 to Figure 14; Moved order information chart.

THAT Corporation; 45 Sumner Street; Milford, MA 01757-1656; USA

Tel: +1 508 478 9200; Fax: +1 508 478 0990; Email: info@thatcorp.com; Web: www.thatcorp.com

Copyright 2014, THAT Corporation

Page

1, 9

2, 3, 5

1, 5, 11

Potrebbero piacerti anche

- Ada4661 2Documento32 pagineAda4661 2Pravin MevadaNessuna valutazione finora

- Description Features: S e M I C o N D U C T o RDocumento3 pagineDescription Features: S e M I C o N D U C T o RjoniseN78Nessuna valutazione finora

- Ssm2120 2 ExpanderDocumento12 pagineSsm2120 2 ExpandershirtquittersNessuna valutazione finora

- Preliminary Technical DataDocumento4 paginePreliminary Technical DataHeri AltisNessuna valutazione finora

- OpAmp - MCP6244Documento38 pagineOpAmp - MCP6244Ludwig SchmidtNessuna valutazione finora

- Dual op amp IC features low noise, high slew rateDocumento5 pagineDual op amp IC features low noise, high slew rateAnonymous vKD3FG6RkNessuna valutazione finora

- Iramx 16 Up 60 ADocumento17 pagineIramx 16 Up 60 AJandfor Tansfg ErrottNessuna valutazione finora

- 04 Spec Sheet PWM Controller ChipDocumento16 pagine04 Spec Sheet PWM Controller Chipxuanhiendk2Nessuna valutazione finora

- Ultralow Distortion, Ultralow Noise Op Amp AD797 : ÷HZ Typ (1.2 NV/÷HZ Max) Input VoltageDocumento16 pagineUltralow Distortion, Ultralow Noise Op Amp AD797 : ÷HZ Typ (1.2 NV/÷HZ Max) Input Voltagemanto22Nessuna valutazione finora

- LME49720 Dual High Performance, High Fidelity Audio Operational AmplifierDocumento34 pagineLME49720 Dual High Performance, High Fidelity Audio Operational AmplifierFran MarinNessuna valutazione finora

- Lm6172 Op Amp DobleDocumento19 pagineLm6172 Op Amp DobleGREKO_ONENessuna valutazione finora

- B1660NDocumento9 pagineB1660NchipquangdtNessuna valutazione finora

- LM741 Complete Data Sheet and SpecsDocumento10 pagineLM741 Complete Data Sheet and SpecsscribdexpressNessuna valutazione finora

- AN4558 (AN6552), AN4558S (AN6552S) : Dual Operational AmplifiersDocumento4 pagineAN4558 (AN6552), AN4558S (AN6552S) : Dual Operational AmplifiersRicardo SoniNessuna valutazione finora

- LM4250 Programmable Operational Amplifier: Literature Number: SNOSC17ADocumento14 pagineLM4250 Programmable Operational Amplifier: Literature Number: SNOSC17AGaston Rodrigo PotenzaNessuna valutazione finora

- 2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionDocumento8 pagine2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionMiloud ChouguiNessuna valutazione finora

- Silicon Planar Epitaxial PNP Transistor: Absolute Maximum RatingsDocumento3 pagineSilicon Planar Epitaxial PNP Transistor: Absolute Maximum RatingsbebeusNessuna valutazione finora

- AD8561Documento11 pagineAD8561ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNessuna valutazione finora

- DUAL HIGH-GAIN OP AMPDocumento10 pagineDUAL HIGH-GAIN OP AMPvictory_1410Nessuna valutazione finora

- Applications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Documento10 pagineApplications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Arjuna Ajita Ananta VijayaNessuna valutazione finora

- 78 S 40Documento9 pagine78 S 40Luis AlbertoNessuna valutazione finora

- Tda 7313Documento14 pagineTda 7313ClaudiuMaxmiucNessuna valutazione finora

- AD820 Single Supply, Rail to Rail Low Power FET-Input Op Amp Data SheetDocumento17 pagineAD820 Single Supply, Rail to Rail Low Power FET-Input Op Amp Data SheetR4PH431Nessuna valutazione finora

- Tda 7250Documento12 pagineTda 7250killer_jj100% (1)

- 8-Pin Bi-Directional Transistor Optocoupler: PreliminaryDocumento5 pagine8-Pin Bi-Directional Transistor Optocoupler: PreliminaryRruga EdibresNessuna valutazione finora

- RPV311 DS en V01Documento2 pagineRPV311 DS en V01Fabian EspinozaNessuna valutazione finora

- MAX480Documento7 pagineMAX480soft4gsmNessuna valutazione finora

- AZ7500BC D1.3 070427nDocumento13 pagineAZ7500BC D1.3 070427nroozbehxoxNessuna valutazione finora

- Amplificador Operacional An6562Documento4 pagineAmplificador Operacional An6562falsouserNessuna valutazione finora

- 132mW Stereo Audio AmplifierDocumento11 pagine132mW Stereo Audio AmplifierTomescu MarianNessuna valutazione finora

- LMH6703Documento13 pagineLMH6703Daniel SuarezNessuna valutazione finora

- LTC 1052Documento25 pagineLTC 1052roozbehxoxNessuna valutazione finora

- Dual Op Amp in 8-Pin DIP and SOP PackagesDocumento5 pagineDual Op Amp in 8-Pin DIP and SOP PackagesMarcosMoraesNessuna valutazione finora

- Ultra-Low Noise Dual Operational AmplifierDocumento8 pagineUltra-Low Noise Dual Operational AmplifierFrancisco FerrerNessuna valutazione finora

- Amplificatori OperazionaliDocumento7 pagineAmplificatori Operazionaliconti51Nessuna valutazione finora

- KA2201Documento4 pagineKA2201Shriniwas SalunkeNessuna valutazione finora

- Descriptio: FeaturesDocumento12 pagineDescriptio: FeaturesgdfsndhgfdvhjzdNessuna valutazione finora

- Datasheet PW460 EN 20120907Documento1 paginaDatasheet PW460 EN 20120907ppNessuna valutazione finora

- 60 W Hi-Fi Dual Audio Driver: DescriptionDocumento12 pagine60 W Hi-Fi Dual Audio Driver: DescriptionLenin BabuNessuna valutazione finora

- Datasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic SemiconductorDocumento17 pagineDatasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic Semiconductorfernandog251186Nessuna valutazione finora

- 34119w SDM Amplificador PDFDocumento17 pagine34119w SDM Amplificador PDFIvan Tarazona AcostaNessuna valutazione finora

- mc1776 - Datasheet PDFDocumento12 paginemc1776 - Datasheet PDFLg GnilNessuna valutazione finora

- AMP02Documento12 pagineAMP02ivan bragaNessuna valutazione finora

- AD8541Documento20 pagineAD8541gliga vasileNessuna valutazione finora

- Test Relay System SpecsDocumento1 paginaTest Relay System SpecsViswanathan NarayananNessuna valutazione finora

- Datasheet Sensitec CDS4010 DSE 07Documento12 pagineDatasheet Sensitec CDS4010 DSE 07Núñez D. PauliNessuna valutazione finora

- Utc Tea1062/1062A Linear Integrated Circuit: Low Voltage Telephone Transmission Circuit With Dialler InterfaceDocumento14 pagineUtc Tea1062/1062A Linear Integrated Circuit: Low Voltage Telephone Transmission Circuit With Dialler InterfaceSai KrishnaNessuna valutazione finora

- Dac121 - 12bit DacDocumento19 pagineDac121 - 12bit DackoltearunNessuna valutazione finora

- LMH6550 Differential, High Speed Op Amp: R R V V ADocumento25 pagineLMH6550 Differential, High Speed Op Amp: R R V V AJavier Felipe AlvaradoNessuna valutazione finora

- SSC2001S Application NoteDocumento18 pagineSSC2001S Application NoteGerardo Mendez CamarilloNessuna valutazione finora

- Tda 7250Documento11 pagineTda 7250Mazariegôs JJNessuna valutazione finora

- MC1458 OnDocumento8 pagineMC1458 OnDanteLupuNessuna valutazione finora

- LM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeDocumento20 pagineLM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeBuga BuniciNessuna valutazione finora

- sc7001q Ay 961Documento18 paginesc7001q Ay 961r2c1Nessuna valutazione finora

- Aplicacion Note UC3843Documento11 pagineAplicacion Note UC3843Luis PapaNessuna valutazione finora

- Operational Amplifier OP470Documento17 pagineOperational Amplifier OP470gotcha75100% (1)

- LM340T 15Documento21 pagineLM340T 15roozbehxoxNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- Tolnikova Pussy RiotDocumento190 pagineTolnikova Pussy RiotSaverioCorNessuna valutazione finora

- Advanced Military CryptographyDocumento115 pagineAdvanced Military CryptographygerrooNessuna valutazione finora

- Ebook - C Programming 4 Embedded Systems - Kirk ZurellDocumento191 pagineEbook - C Programming 4 Embedded Systems - Kirk Zurellmanojiitd2363100% (1)

- Theory of Robotics Arm Control With PLCDocumento61 pagineTheory of Robotics Arm Control With PLCSaverioCorNessuna valutazione finora

- RPSU Issue 1 User ManualDocumento13 pagineRPSU Issue 1 User ManualSaverioCorNessuna valutazione finora

- Advanced Electronics CommunicationsDocumento195 pagineAdvanced Electronics CommunicationsFeragut Fergalush100% (1)

- A Concise Grammar of Russian Language PDFDocumento306 pagineA Concise Grammar of Russian Language PDFSaverioCorNessuna valutazione finora

- Advanced Electronics CommunicationsDocumento3 pagineAdvanced Electronics CommunicationsSaverioCorNessuna valutazione finora

- Construction Guide: Oakley Sound SystemsDocumento34 pagineConstruction Guide: Oakley Sound SystemsSaverioCorNessuna valutazione finora

- SQO Instruction Sequences Through An ArrayDocumento1 paginaSQO Instruction Sequences Through An ArraySaverioCorNessuna valutazione finora

- Arp Psu Bom Rev01Documento1 paginaArp Psu Bom Rev01SaverioCorNessuna valutazione finora

- Defcon 17 Joseph Mccray Adv SQL InjectionDocumento72 pagineDefcon 17 Joseph Mccray Adv SQL InjectionRoSilenTNessuna valutazione finora

- SINAMICS V20 Getting Started 072012 en-US PDFDocumento66 pagineSINAMICS V20 Getting Started 072012 en-US PDFKo J YarNessuna valutazione finora

- SQI - SQO - SQL Sample Program For RSLogix 5000Documento1 paginaSQI - SQO - SQL Sample Program For RSLogix 5000SaverioCorNessuna valutazione finora

- Use of Immediate Mask Values in ControlLogix ControllersDocumento2 pagineUse of Immediate Mask Values in ControlLogix ControllersSaverioCorNessuna valutazione finora

- Basics of Reverse OsmosisDocumento14 pagineBasics of Reverse OsmosisNagarjuna Tadiparti100% (2)

- Comparing SQC and SQI Instruction OperationDocumento3 pagineComparing SQC and SQI Instruction OperationSaverioCor100% (1)

- Franchised Panel Builder Hand Book PDFDocumento105 pagineFranchised Panel Builder Hand Book PDFSaverioCorNessuna valutazione finora

- Simulacion RSlogixEmulate5000Documento6 pagineSimulacion RSlogixEmulate5000SaverioCorNessuna valutazione finora

- Control Panel Technical Guide PDFDocumento72 pagineControl Panel Technical Guide PDFchem_taNessuna valutazione finora

- Simulation of Model-Based Predictive Control Applied To A Solar-ADocumento11 pagineSimulation of Model-Based Predictive Control Applied To A Solar-ASaverioCorNessuna valutazione finora

- sdd2000 Service Manual PDFDocumento27 paginesdd2000 Service Manual PDFSaverioCorNessuna valutazione finora

- XD - Windows 7 Optimization GuideDocumento9 pagineXD - Windows 7 Optimization GuideCharNessuna valutazione finora

- 500 ManDocumento65 pagine500 ManSaverioCorNessuna valutazione finora

- A2 Service Manual PDFDocumento34 pagineA2 Service Manual PDFSaverioCorNessuna valutazione finora

- Intro To MechatronicsDocumento33 pagineIntro To MechatronicscorozcogarciaNessuna valutazione finora

- The C Puzzle BookDocumento93 pagineThe C Puzzle Bookabhijeetnayak67% (3)

- VMware View OptimizationGuideWindows7 enDocumento60 pagineVMware View OptimizationGuideWindows7 enSaverioCorNessuna valutazione finora

- Percussion and Max - A Collection of Short Works For Solo PercussiDocumento142 paginePercussion and Max - A Collection of Short Works For Solo PercussiSaverioCorNessuna valutazione finora

- MIDI Violin - A Digital Music Input Device For Nonprofessional VioDocumento65 pagineMIDI Violin - A Digital Music Input Device For Nonprofessional VioSaverioCorNessuna valutazione finora

- Reboiler Selection CriteriaDocumento5 pagineReboiler Selection CriteriamineralgroupstmfiNessuna valutazione finora

- Reliability Centered SparesDocumento2 pagineReliability Centered SparesMoustafa HelmyNessuna valutazione finora

- Unit 1 - Ways Informatics Transforming Health CareDocumento22 pagineUnit 1 - Ways Informatics Transforming Health CareRaquel MonsalveNessuna valutazione finora

- International Conference of Advance Research and Innovation (ICARI-2015) PDFDocumento1 paginaInternational Conference of Advance Research and Innovation (ICARI-2015) PDFAbhilash KumarNessuna valutazione finora

- Introduction: Nature and Background of the StudyDocumento24 pagineIntroduction: Nature and Background of the StudyJm BalessNessuna valutazione finora

- Soil Investigations & Testing For The Proposed Road 1 North, Kidurong Industrial Estate (Kinda) For Bintulu Development Authority PDFDocumento8 pagineSoil Investigations & Testing For The Proposed Road 1 North, Kidurong Industrial Estate (Kinda) For Bintulu Development Authority PDFracing.phreakNessuna valutazione finora

- Roy Peter Clark 14 Traits of Good Writers and Elements of NewsDocumento2 pagineRoy Peter Clark 14 Traits of Good Writers and Elements of Newsroniella delos reyesNessuna valutazione finora

- Minor ProjectDocumento22 pagineMinor ProjectKunwar IndrajeetNessuna valutazione finora

- Lab 7 Fluid SaturationDocumento6 pagineLab 7 Fluid SaturationRichard OwusuNessuna valutazione finora

- Statistics MCQ'S I.Com Part 2Documento8 pagineStatistics MCQ'S I.Com Part 2Shafique Ur Rehman82% (17)

- Demonstration of Wireless Gas Sensor Using Reduced Graphene Oxide Loaded Patch AntennaDocumento3 pagineDemonstration of Wireless Gas Sensor Using Reduced Graphene Oxide Loaded Patch AntennaJeff SalesNessuna valutazione finora

- Endurance Test Report MKP 2P Relay PGCILDocumento5 pagineEndurance Test Report MKP 2P Relay PGCILTravis WoodNessuna valutazione finora

- Digital Surround Sound Receiver: FR960 FR970Documento24 pagineDigital Surround Sound Receiver: FR960 FR970Dj CostyNessuna valutazione finora

- BP Energol-ThbDocumento2 pagineBP Energol-ThbRajesh BNessuna valutazione finora

- IYSS Gloucester ModelDocumento16 pagineIYSS Gloucester ModelcseightNessuna valutazione finora

- Top 20 Automation Testing Interview Questions and AnswersDocumento36 pagineTop 20 Automation Testing Interview Questions and AnswersBilal Achernan100% (1)

- Manual de Feeder Gravimetrico PDFDocumento0 pagineManual de Feeder Gravimetrico PDFEfrain SaldañaNessuna valutazione finora

- Alan Maley Poster 2Documento1 paginaAlan Maley Poster 2Cory KobyNessuna valutazione finora

- Summer Solstice Webquest - WorksheetDocumento3 pagineSummer Solstice Webquest - WorksheetLauraNessuna valutazione finora

- BrochureDocumento68 pagineBrochure7063673nasNessuna valutazione finora

- Create a Project Management Dashboard in ExcelDocumento4 pagineCreate a Project Management Dashboard in ExcelImran Mulani100% (5)

- Telling Time and Telephone Communication: He O LLDocumento33 pagineTelling Time and Telephone Communication: He O LLnovaNessuna valutazione finora

- Aerofom - Alu Glass Tape Technical Data SheetDocumento1 paginaAerofom - Alu Glass Tape Technical Data SheetChris SolonNessuna valutazione finora

- Building Resilient Teams Workbook FINALDocumento16 pagineBuilding Resilient Teams Workbook FINALКремена П.Nessuna valutazione finora

- Cold-Formed Steel Beam Design - ManualDocumento28 pagineCold-Formed Steel Beam Design - ManualEdwin RamirezNessuna valutazione finora

- Why Me?' The Problem of Chronic Pain After Surgery: JurnalDocumento8 pagineWhy Me?' The Problem of Chronic Pain After Surgery: JurnalnurismafadhliahNessuna valutazione finora

- Early 2011 Macbook Pro SpecsDocumento4 pagineEarly 2011 Macbook Pro SpecsMatthew Timothy PuaNessuna valutazione finora

- Seleccion & Brochure Bomba Griswold BoosterDocumento19 pagineSeleccion & Brochure Bomba Griswold BoosterJonathan Mario Bolivar AldanaNessuna valutazione finora

- Psychometric Testing HandoutDocumento2 paginePsychometric Testing HandoutIchsan FaridzNessuna valutazione finora

- ELEC3030 Notes v1Documento118 pagineELEC3030 Notes v1kosmos3384Nessuna valutazione finora