Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Electronics Engineering - Korea Univ.

Caricato da

deesireeTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Electronics Engineering - Korea Univ.

Caricato da

deesireeCopyright:

Formati disponibili

Electronics by Eunil Won, Korea University

Electronics - 06

: More on Op-Amplifiers

Op-Amplifiers

- Difference Amplifiers

- Instrumentation Amplifiers

Electronics by Eunil Won, Korea University

Electronics by Eunil Won, Korea University

Differential (or difference) Amplifiers

: responds to the difference between the two signals applied at its input

One can parametrize two inputs as their differential and common-mode components

1

+

-

+

-

vIcm +

vId /2

vId /2

vId = vI2 vI1

vI1 = vIcm vId /2

vI2 = vIcm + vId /2

The output voltage:

vIcm =

1

(vI + vI1 )

2 1

vO = Ad vId + Acm vIcm

Ad : amplifier differential gain

Acm: common-mode gain (ideally zero)

Ideally, this term should be zero

The efficiency of a differential amplifier: quantified by common-mode rejection ratio (CMRR)

CMRR = 20 log10

ex) MAXIM MAX4198/4199

differential amplifier

|Ad |

|Acm |

(look at http://korea.maxim-ic.com)

has CMRR = 90 dB

90 = 20 log10

|Ad |

|Acm |

9

|Ad |

= 10 2 31623

|Acm |

CMRR is quite suppressed

Electronics by Eunil Won, Korea University

Electronics by Eunil Won, Korea University

A single op amp difference Amplifiers

R2

Let us start with:

R1

vI1

vI2

We wish to determine vo in terms of

vO

R3

vI1

and

vI2

Circuit is linear so we apply superposition

R4

R2

R1

vI1

i) we reduce vI2 to zero: output = vO1

Therefore, we have

R2

R1

vI2

R2

v

R1

(R3 and R4 do not affect the gain expression)

R4

R3

R3

R4

Electronics by Eunil Won, Korea University

ii) we reduce vI1 to zero: output =

vO2

is altered by the voltage divider formed by R3 and R4

vO2 =

"!

"

R4

R2

vI2

1+

R3 + R 4

R1

3

Electronics by Eunil Won, Korea University

A single op amp difference Amplifiers

Now we require that the gain magnitudes for inverting and non-inverting to be same:

R4

R3 + R 4

R2

1+

R1

and we have

"

R2

R1

R4

vO = vI2

R 3 + R4

1

=

R3

+

1

R4

R4

R2

=

R3 + R 4

R 1 + R2

R2

1+

R1

"

1

R1

R2 + 1

R3

R1

=

R4

R2

R2

vI2

R1

The superposition of i) and ii) tells us that

vO = vO1 + vO2 =

Ad =

R2

R1

R2

R2

R2

R2

vI2

vI1 =

(vI2 vI1 ) =

vId

R1

R1

R1

R1

and we usually select R3 = R1 and R4 = R2

Next, lets consider the circuit with only a common-mode signal applied at the input

R4

and it should be same as the

i2

vIcm

R2

The voltage at + terminal =

R3 + R4

voltage at the - terminal

i1 R1

!

"

1

R4

1

R3

i1 =

vIcm

vIcm =

vIcm

R1

R3 + R 4

R1 R3 + R 4

i1 = i2 the output voltage becomes

vIcm

+

-

R3

vO

R4

=

=

Electronics by Eunil Won, Korea University

Thus

Acm

R4

R4

1

R3

vIcm i2 R2 =

vIcm

vIcm R2

R3 + R4

R 3 + R4

R 1 R 3 + R4

!

"

R4

R2 R3

1

vIcm

R3 + R4

R1 R4

VO

R4

=

=

vIcm

R3 + R 4

R2 R3

1

R1 R4

"

= 0 ( R4 /R3 = R2 /R1 ) so it rejects common

mode signal

Electronics by Eunil Won, Korea University

A single op amp difference Amplifiers

In addition to rejecting common-mode signals, a difference amplifier is usually required to have a high input resistance

To find out the input resistance between the two input terminals (resistance seen by vId), called the differential input

resistance ( RId ), lets consider the following circuit

Here we assumed: R3 = R1

R2

iI

R1

iI

RId

R1

RId

R2

and R4 = R2

vId

iI

Since the two input terminals of the op amp track each other in potential, we may

write a loop equation and obtain

vId = R1 iI + 0 + R1 iI

virtual short circuit

thus:

RId = 2R1

Limitation: note that if the amplifier is required to have a large differential gain (R2/R1), then R1 will be relatively

small and the input resistance will be correspondingly low, a drawback of this circuit. Another drawback of the

circuit is that it is not easy to vary the differential gain of the amplifier (see the next instrumentation amplifier)

Electronics by Eunil Won, Korea University

Electronics by Eunil Won, Korea University

The Instrumentation Amplifier

The low-input resistance problem of the difference amplifier can be solved by buffering the two input terminals using

!

"

voltage followers:

R2

1+

non-inverting configuration, gain =

vI1

+

A1

-

R2

R1

X

R1

R3

R2

vI2

A3

+

vO

R4

A2

+

non-inverting configuration, gain =

vI1

i) 1st stage: non-inverting configuration

ii) 2nd stage: difference amplifier

R4

R3

R1

1+

input to 2nd stage:

R4

vO =

R3

R2

1+

R1

R2

1+

R1

"

"

(vI2 vI1 ) =

vI2

R2

1+

R1

"

vId

vId

R4

and differential gain is Ad =

R3

"

R2

R1

R2

1+

R1

"

and the common-mode gain will be zero because of the

differencing action of the 2nd-stage amplifier

Now the above circuit has the advantage of very high input resistance and high differential gain - however has three

major disadvantages:

i) vIcm is amplified in the first stage so A3 may be saturated or CMRR will be reduced

ii) Two amplifiers in the 1st stage have to be perfectly matched, otherwise a spurious signal is amplified in

the 2nd stage

iii) To vary Ad, two resistors labeled R1 or R2 have to be varied simultaneously (difficult)

Electronics by Eunil Won, Korea University

remedy in the next design

Electronics by Eunil Won, Korea University

The Instrumentation Amplifier

All three problems can be solved with a very simple wiring change: disconnect the node between R1 (node X), from

ground

Virtual short circuit at A1 and A2 causes input voltages

vI1

+

appear (-) on A1 and (-) on A2

vO1

vI1

A1

-

R2

i=

vId

i=

2R1

2R1

i=

vI2

vI2

vId

2R1

R3

vId

2R1

R3

R2

A2

+

so vI2 vI1 = vId appears across 2R1

vId

i=

and it flows to R2 in A1 and A2

2R

1

+

R4

A3

+

vO

R4

vO2

At the 2nd stage:

R4

R4

vO =

(vO2 vO1 ) =

R3

R3

Now

vO2 vO1

R2

1+

R1

"

vId

vId

R2

2R1

vId

vO2 = vI2 +

R2

2R1

!

"

R2

R2

= vI2 vI1 +

vId = 1 +

vId

R1

R1

vO1 = vI1

R4

Ad =

R3

R2

1+

R1

"

Note: i) the proper differential operation does not depend on the matching of two R2: if we have R2 and R2

!

"

R4

R2 + R2!

1+

then the new gain becomes Ad =

(no need for simultaneous adjustment)

R3

2R1

ii) common-mode input gives zero current flowing in the R2 resistors: (because of the virtual short circuit)

iii) The gain can be varied by changing only one resistor 2R1

Electronics by Eunil Won, Korea University

Electronics by Eunil Won, Korea University

Single Time Constant Circuits

Single time Constant (STC) circuits are those circuits that are composed of, or can be reduced to, one reactive

component (inductance or capacitance) and one resistance

Evaluating the time constant: suppose we are given with the below circuit. What is the time constant of this circuit?

R1

+

-

R2

R1

R2

R3

+

R4

vO

i) reducing the excitation to zero: short the voltage source and

open the current source

ii) find the equivalent resistor value

R3

R4

vO

R3

(R1 ||R2 )

Req = [(R1 ||R2 ) + R3 ] || R4

R4

vO

ii) put the excitation to the original state and calculate the STC

+ [(R1 ||R2 ) + R3 ] || R4

-

Electronics by Eunil Won, Korea University

vO

= Req C = [(R1 ||R2 ) + R3 ] || R4 C

8

Electronics by Eunil Won, Korea University

Frequency Response of STC Circuits

Transfer function T(s): the transfer function is a mathematical representation of the relation between the input and

output of analog electronic circuits

Mathematically, we define T(s) as, for given input vI (t) and output vO (t)

VO (s) = T (s)VI (s)

where

Low-pass circuit

with

VO (s)

the magnitude of the

transfer function at =0

High-pass circuit

T (s) =

VI (s)

K

1 + (s/0 )

T (s) =

0 = 1/

and

or

T (s) =

VO (s)

L{vO (t)}

=

VI (s)

L{vI (t)}

are the Laplace transform of

and for physical frequencies, T (j) =

K

!

|T

(j)|

=

magnitude:

1 + (/0 )2

Ks

s + 0

and for physical frequencies,

K

!

|T

(j)|

=

magnitude:

1 + (0 /)2

Electronics by Eunil Won, Korea University

vI (t)

and

vO (t)

K

1 + j(/0 )

phase: () = tan1 (/0 )

T (j) =

K

1 j(0 /)

phase: () = tan1 (0 /)

9

Electronics by Eunil Won, Korea University

Frequency Dependence of the open-loop gain

The differential open-loop gain of an op amp is not infinite; rather it is finite and decreases with frequency (due to

internal capacitances : internally compensated op amp)

AO 100

3 dB

The gain at dc is high but it starts to fall of at a rather low

frequencies (~10 Hz in this example)

- 20 dB/decade

75

The uniform - 20 dB/decade gain roll off : character of

internally compensated op amps

50

A0 =

25

0

105

b = 2 x 10 rad/s

10

102

103

104

105

fb

106

ft

By analogy to the response of low-pass STC circuits, the gain A(s) of an internally compensated op amp may be

expressed as:

A0

A0

A(j)

=

A(s) =

and for physical frequencies,

1 + s/b

1 + j/b

: the 3-dB frequency (corner frequency)

A0

: the dc gain

The gain |A| reaches unity ( 0dB) at t

For higher frequencies

A(j)

t = A0 b

! b

A0 b

A

(responsible for the

and |A(j)| 0 b

straight line above)

j

and ft = t /2 : unity-gain bandwidth

Thus if ft is known, (106 Hz in our example), one can easily determine the magnitude of the op-amp gain at a

given frequency f

Electronics by Eunil Won, Korea University

10

Electronics by Eunil Won, Korea University

Frequency Dependence of the open-loop gain

Example)

Note that this is a

normalized gain

When you do real life research,

you should be able to understand

the parameters in the date sheet!

(my best guess)

! A(j) !

!

20 log10 !

A0

Electronics by Eunil Won, Korea University

400 MHz is here

11

Electronics by Eunil Won, Korea University

Frequency Dependence of Closed-Loop Amplifiers

Inverting Amplifier:

R2 /R1

the closed loop gain of inverting amplifier was

1 + (1 + R2 /R1 )/A

A0

since the transfer characteristic A(s) =

of the closed loop gain is

A0 b = t

1 + s/b

VO (s)

R2 /R1

!

"

!

=

R2

1

Vi (s)

1 + 1 + R1 A0 1 +

For A0 !

R2

1+

R1

"

s

b

"=

1+

(usually the case)

and the corner frequency becomes

1

A0

R2 /R1

"

!

R2

s

1 + R1 + A0 b 1 +

3dB =

Similarly, for A0 !

"

(usually the case)

and the corner frequency becomes

Electronics by Eunil Won, Korea University

1

A0

R2 /R1

"

R2

s

1 + R1 + t /(1+R

2 /R1 )

T (s) =

K

1 + (s/0 )

t

2

1+ R

R1

the closed loop gain of non-inverting amplifier was

R2

1+

R1

1+

VO (s)

R2 /R1

: same form as the low pass network

s

Vi (s)

1 + t /(1+R

/R

)

2

1

Non-inverting Amplifier:

R2

R1

"=

1 + R2 /R1

1 + (1 + R2 /R1 )/A

Vo (s)

1 + R2 /R1

: same form as the low pass network

s

Vi (s)

1 + t /(1+R2 /R1 ) with a dc gain gain of (1+R2/R1)

3dB =

t

2

1+ R

R1

12

Electronics by Eunil Won, Korea University

Frequency Dependence of Closed-Loop Amplifiers

Example) Consider an op amp with the unity gain bandwidth ft = 1 MHz. Find the 3 dB frequency of closed-loop

amplifiers with nominal closed-loop gains of +1000, +100, +10, +1, -1, -10, -100, - and 1000.

At dc:

Vo (0)

= 1 + R2 /R1

Vi (0)

(non-inverting) and

Vo (0)

= R2 /R1 (inverting)

Vi (0)

So,

Closed loop gain

R2/R1

f3dB=ft/(1+R2/R1)

+1000

999

1 kHz

+100

99

10 kHz

+10

+1

9

0

100 kHz

1 MHz

-1

0.5 MHz

-10

10

90.9 kHz

-100

100

9.9 kHz

-1000

1000

~1 kHz

R2 /R1 = 999

+1000 = 1 + R2 /R1

R2 /R1 = 1000

1000 = R2 /R1

and one can fill the columns for R2/R1

And from

3dB =

t

2

1+ R

R1

one can fill the 3rd columns as well

This table clearly illustrates the trade-off between gain and bandwidth: for a given op amp, the lower the closed-loop

gain required, the wider the bandwidth achieved

The non-inverting configuration exhibits a constant gain-bandwidth product equal to ft of the op amp

Electronics by Eunil Won, Korea University

13

Electronics by Eunil Won, Korea University

Large signal operation of op amps

Output voltage saturation: Similar to all other amplifiers, op amps operate linearly over a limited range of output

voltages

Output current limits: output current of op amps is limited to a specified maximum

Slew rate: there is a specific maximum rate of change possible at the output of a real op amp and this maximum is

known as the slow rate (SR)

dvO !!

SR =

dt max

: usually specified on the op-amp date sheet in units of V/s

300 V/s = 3 V/0.01 s

(fast enough?)

vO

vI

vI

The origin of the slewrate phenomenon we

need to know about

the internal circuit of

the op amp (not in the

scope of this class)

slope = SR

vO = vI

(unity gain voltage

follower)

Electronics by Eunil Won, Korea University

14

Electronics by Eunil Won, Korea University

Large signal operation of op amps

Full power bandwidth:

Consider the unity-gain follower with a sine wave input given by vI = Vi sin t

: the rate of change of this waveform is given by

note: if

Vi

vI

= Vi cos t

dt

with max. value of

Vi

exceeds the slew rate of the op amp, the output waveform will be distorted

theoretical output

t

output when op amp

is slew-rate limited

The op amp date sheet usually specify a frequency fM, called the full-power bandwidth: it is the frequency at

which an output sinusoid with amplitude equal to the rated output voltage of the amp begins to show distortion

due to slew-rate limiting

M Vomax = SR

Electronics by Eunil Won, Korea University

or

fM =

SR

2Vomax

Vomax

: the rated output voltage

15

Electronics by Eunil Won, Korea University

DC Imperfections

Offset Voltage:

When two input terminals of the op amp are tied together and connected to ground, the output

show will show a finite dc voltage (dc offset voltage)

A3

+

VO != 0

Actual op amp

circuit model

A3

+

- +

offset-free op amp

VOS

VOS: input offset voltage: it is within 1 mV ~ 5 mV and depends on temperature

Evaluating the output dc offset voltage due to VOS in a closed-loop amplifier:

R2

R1

- +

VOS

Input bias and offset current

A3

+

vO

VO = VOS

R2

1+

R1

"

In order for the op amp to operate, its two input terminals have to be supplied

with dc currents (=input bias current)

IB1 + IB2

2

IB1

IB =

IB2

IOS = |IB1 IB2 |

input bias current

input offset current

(For BJT, IB = 100 nA, IOS = 10 nA and for FET input bias is ~ pA)

Electronics by Eunil Won, Korea University

16

Electronics by Eunil Won, Korea University

DC Imperfections

So far, we have not so explicit in the notation of the current, regarding the

direction and the sign. From now on, we agree on

Current values are all assumed to be positive

When we need to add or subtract current values, we carefully assign

(+) or (-) depending on the direction of currents to be manipulated

Electronics by Eunil Won, Korea University

17

Electronics by Eunil Won, Korea University

DC Imperfections

Input bias and offset current

IB1

R1

:output voltage of the closed-loop amp due to the input bias current?

(-) terminal is at 0 V

I1 is through R2

R2

0V

VO = IB1 R2 IB R2

and this gives an upper limit on the value of R2

IB1

+

+

I2

I1

R1

VO = IB1 R2

IB2

R2

Now with R3 at (+) terminal

(+) terminal : the voltage is IB2 R3

0V

A technique exists for reducing the values of he

output dc voltage due to the input bias currents

(see the below circuit)

I1 = (IB2 R3 )/R1

so

IB1

+

IB2

R3

VO

IB2

If IB1 = IB2 = IB

So, if we choose

I2 = IB1 I1 = IB1 IB2

VO = IB2 R3 + R2

!

"

#$

R2

VO = IB R2 R3 1 +

R1

R2

R1 R2

R3 =

=

2

R 1 + R2

1+ R

R1

Electronics by Eunil Won, Korea University

then we have

R3

IB1 IB2

R1

VO = 0

"

R3

R1

:output voltage of the closedloop amp due to the input bias

current can be set to zero

18

Electronics by Eunil Won, Korea University

DC Imperfections

Input bias and offset current

I2

I1

R1

: effect of a finite offset current IOS?

R2

0V

IB1

+

R3

IB2

then

Vo

=

=

=

=

VO

IB2

Let us assume that

IB1 = IB + IOS /2

IB2 = IB IOS /2

"

R3

IB2 R3 + R2 IB1 IB2

R1

#

$

R1 R2

R1 R2 1

(IB Ios /2)

+ R2 (IB + IOS /2) (IB IOS /2)

R1 + R 2

R1 + R2 R1

R1 R2

R2

IOS R1 R2

IOS

IOS

R2

IB

+ R2 IB R2 IB

+

+ R2

+ R2

R 1 + R2

R1 + R 2

2 R1 + R 2

2

2 R1 + R2

IOS

1

1

Ib

(R1 R2 + R2 (R1 + R2 ) R22 ) +

(R1 R2 + R2 (R1 + R2 ) + R22 )

&'

(

&'

(

R1 + R2 %

2 R1 + R2 %

=0

= IOS R2

=2R2 (R1 +R2 )

and is usually about an order of magnitude smaller than the value obtained

without R3

Electronics by Eunil Won, Korea University

19

Electronics by Eunil Won, Korea University

DC Imperfections

R2

R1

We conclude that to minimize the effect of the input bias currents one

should place in the positive lead a resistance equal to the dc resistance

seen by the inverting terminal

R3 = R 2

R1 R2

R 1 + R2

R2

C1

R1

C2

R3 = R 2

For ac-coupled amplifiers, one must always provide a continuous dc

path between each of the input terminals of the op amp and ground:

for this reason the ac-coupled non-inverting amplifier in the left figure

will not work without the resistance R3 to the ground

Unfortunately, including R3 lowers considerably the input resistance

of the closed-loop amplifier

Electronics by Eunil Won, Korea University

20

Electronics by Eunil Won, Korea University

Integrators and Differentiators (Op amp version)

The op-amp circuit applications we have studied thus far utilized resistors in the op-amp feedback path and in

connecting the signal source to the circuit (feed-in path): as a result circuit operation has been (ideally)

independent of frequency

By allowing the use of capacitors together with resistors in the feedback and and feed-in paths of op-amp, we open

the door to a very wide range of useful and exciting applications of the op amp

The inverting configuration with general impedances

To begin with, consider the inverting closed-loop configuration with impedances Z1(s) and Z2(s) as below

Z2

The closed loop transfer function becomes then

Z1

Vi

Vo

Vo (s)

Z2 (s)

=

Vi (s)

Z1 (s)

(Again, we do not deal with the Laplace transform but infer this equation

from the closed-loop gain of the inverting amplifiers with resistances)

Electronics by Eunil Won, Korea University

21

Electronics by Eunil Won, Korea University

The Inverting Integrator

Let the input be a time-varying function: vI (t)

i1

vI (t)

the current through the resistor

i1 (t) = vI (t)/R

and it flows through the capacitor

will deposit the charge

Therefore the capacitor voltage will change by

1

C

i1 (t) dt

on the capacitor

i1 (t) dt

!

1 t

If VC is the voltage on C at t=0, vC (t) = VC +

i1 (t) dt

C 0

!

! t

1 t

1

The output voltage becomes

vO (t) = vC (t) =

i1 (t) dt VC =

vI (t) dt VC

C 0

RC 0

In frequency domain,

! V (s) !

1

! o !

!

!=

Vi (s)

CR

Z1 (s) = R,

!V !

! o!

! !

Vi

Z2 (s) =

Vo (s)

1

1

=

=

Vi (s)

sCR

jCR

Integrator behaves as a low-pass filter with

a corner frequency of zero

1

RC

Electronics by Eunil Won, Korea University

1

sC

realizing the

mathematical

operation of

integration

It is also known as a

Miller integrator

(log scale)

22

Electronics by Eunil Won, Korea University

The Inverting Integrator

The effect of the input dc input offset voltage (VOS) : consider the following circuit (input signal is shorted for easier

analysis)

VOS /R

(Note: the current flow is opposite so the sign is

changed from the case in the previous slide)

VOS /R

-

C

vO

- +

vO = VOS +

VOS

VOS

t

CR

Thus vO increases linearly with time until the op amp saturates!

The effect of the input dc input offset current (IOS) : consider the following circuit (we added a resistance R in the op

amp positive-input lead in order to keep the input bias current IB

from flowing through C)

I2

I1 = IB2 R/R = IB2

IB1

There are input bias currents: IB1 and IB2

IB2

vO

Voltage at (+) terminal : IB2 R

= Voltage at (-) terminal

negative because

it is an inverting

circuit

I1 = (IB2 R)/R = IB2

I2 = IB1 IB2 = IOS

!

1

IOS Thus vO increases linearly with

vO = IB2 R +

IOS dt = IB2 R +

t

time until the op amp saturates!

C

C

Electronics by Eunil Won, Korea University

23

Electronics by Eunil Won, Korea University

The Inverting Integrator

The Miller integrator with a large resistance RF:

RF

: the dc problem can be alleviated by connecting a resistor RF

across the integrator capacitor C

RF provides a dc path through with (VOS/R) and IOS can flow!

vO

Therefore vO will now have a dc component instead of rising

linearly

vO = VOS 1 +

RF

R

"

due to dc offset + R,RF

+ IOS RF

due to IOS,RF

And the integrator transfer function becomes

Vo (s)

RF /R

=

Vi (s)

1 + sCRF

as opposed to the ideal function of 1/sCR

The lower the values we select for RF, the higher the corner frequency (1/CRF) will be and the more non-ideal

the integrator becomes

Electronics by Eunil Won, Korea University

24

Electronics by Eunil Won, Korea University

The Op-Amp Differentiator

The Miller integrator with a large resistance RF:

i

i

vI (t)

Assume a time varying input voltage : vI (t)

The virtual ground at the inverting input terminal of the op amp

causes vI(t) to appear across the C

The current through C

-

vO

i=

d

dvI (t)

(CvI (t)) = C

dt

dt

and this current flows vO (t) = iR = CR

through R so that

The frequency-domain transfer function of the differentiator circuit can be found by

Vo (s)

Z2 (s)

=

Vi (s)

Z1 (s)

Z1 (s) = 1/sC

and with

Vo (s)

= sCR

Vi (s)

or

Z2 (s) = R

dvI (t)

dt

realizing the

mathematical

operation of

differentiation

Vo (s)

= jCR

Vi (s)

CR: differentiator time-constant

Electronics by Eunil Won, Korea University

25

Potrebbero piacerti anche

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- 3G New SSV Ube0342Documento13 pagine3G New SSV Ube0342Otunba Olakunle Sunday AjayiNessuna valutazione finora

- Huawei AOC4518R8v06Documento7 pagineHuawei AOC4518R8v06RNNicollNessuna valutazione finora

- Alat Alat NavigasiDocumento3 pagineAlat Alat NavigasiIrham FaisalNessuna valutazione finora

- Zet-Horn 131-141 AC Arctic: Zöllner KielDocumento1 paginaZet-Horn 131-141 AC Arctic: Zöllner Kielkhanh123ctm100% (1)

- MU-MIMO in LTEDocumento13 pagineMU-MIMO in LTECM_123Nessuna valutazione finora

- CMI-8338/PCI C3DX PCI-Based HRTF 3D Extension Positional Audio ChipDocumento43 pagineCMI-8338/PCI C3DX PCI-Based HRTF 3D Extension Positional Audio ChipkumasanpapaNessuna valutazione finora

- Ceragon Technical-Brief Advanced Frequency-ReuseDocumento10 pagineCeragon Technical-Brief Advanced Frequency-ReuseIbrahim MousaNessuna valutazione finora

- OPT5548TS Modulator PDFDocumento6 pagineOPT5548TS Modulator PDFJefersson Eduardo Sanchez DiazNessuna valutazione finora

- Web Telemetry Project ReportDocumento8 pagineWeb Telemetry Project ReportDhruv GuptaNessuna valutazione finora

- Basic Components of RadarDocumento4 pagineBasic Components of Radarmas3565560100% (1)

- Ho CH 5 Codes ExerciseDocumento2 pagineHo CH 5 Codes ExerciseGina MarmolNessuna valutazione finora

- Contoh Jumbled WordsDocumento5 pagineContoh Jumbled WordsHenita SNessuna valutazione finora

- List of FM Stations Operating in Rwanda and Their Approximate Coverage As of May 2020Documento19 pagineList of FM Stations Operating in Rwanda and Their Approximate Coverage As of May 2020Elias MukunziNessuna valutazione finora

- Etherchannel in AIXDocumento4 pagineEtherchannel in AIXSunny SinghNessuna valutazione finora

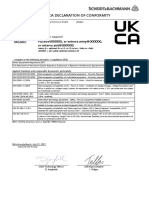

- Pgl40 Ukca Declaration of ConformityDocumento1 paginaPgl40 Ukca Declaration of ConformityILNessuna valutazione finora

- Atm3 4 2006 Ivrlac 1Documento8 pagineAtm3 4 2006 Ivrlac 1aluomcNessuna valutazione finora

- SPP VOR Radial Isec BE90Documento6 pagineSPP VOR Radial Isec BE90Dee VisionNessuna valutazione finora

- General Workflow (Cheat Sheet)Documento2 pagineGeneral Workflow (Cheat Sheet)Maria StfNessuna valutazione finora

- Signal Integrity - Vikas ShuklaDocumento58 pagineSignal Integrity - Vikas Shuklasandee kumarNessuna valutazione finora

- Fairchild 1972 ProdsDocumento12 pagineFairchild 1972 ProdsJOSE COCA GARCIANessuna valutazione finora

- Manual de Usuario GW INSTEK GFG 8200A SERIESDocumento19 pagineManual de Usuario GW INSTEK GFG 8200A SERIESJoshua Leiva MuñozNessuna valutazione finora

- Hands-On Assignment II Solution: Pulse Code Modulation: ReadingDocumento6 pagineHands-On Assignment II Solution: Pulse Code Modulation: ReadingnongonNessuna valutazione finora

- Wide Area Measurement Systems: March 2012Documento21 pagineWide Area Measurement Systems: March 2012DrVikas Singh BhadoriaNessuna valutazione finora

- Conclusion 2 and 3 Comms LabDocumento2 pagineConclusion 2 and 3 Comms LabUhjafwnuijhnfa KmerkgoeNessuna valutazione finora

- Multimedia University of Kenya. Faculty of Engineering and Technology. Bsc. Electrical and Telecommunication EngineeringDocumento8 pagineMultimedia University of Kenya. Faculty of Engineering and Technology. Bsc. Electrical and Telecommunication EngineeringMavineNessuna valutazione finora

- Signal Processing in Seti: For ofDocumento13 pagineSignal Processing in Seti: For oftrc_wmNessuna valutazione finora

- LTE Performance Trouble Shooting and Optimization Guidelines NSN RetainabilityDocumento37 pagineLTE Performance Trouble Shooting and Optimization Guidelines NSN RetainabilityDanyal BasharatNessuna valutazione finora

- GSM Introduction and Cellular Principle: Presented byDocumento28 pagineGSM Introduction and Cellular Principle: Presented byAnoop K JayanNessuna valutazione finora

- Design Filters in SimulinkDocumento5 pagineDesign Filters in SimulinkDramane BonkoungouNessuna valutazione finora

- GSM/GPRS/SMS/UMTS/Ethernet Transmitter EPX400-60: Data Sheet ofDocumento2 pagineGSM/GPRS/SMS/UMTS/Ethernet Transmitter EPX400-60: Data Sheet ofCristina belen Aristizabal mosqueraNessuna valutazione finora