Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

ES Lab4

Caricato da

avneellallu0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

40 visualizzazioni20 pagineembedded systems

Titolo originale

ES-Lab4

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoembedded systems

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

40 visualizzazioni20 pagineES Lab4

Caricato da

avneellalluembedded systems

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 20

1

The University of the South Pacific

Embedded Systems

LABORATORY 4 Date: August 2014 Dr. ASSAF M.

Four-bit Adder Design and Implementation

Overview

In this experiment you will learn to design and implement a simple logic circuit using the ISE

tool and the Adept software. You will generate a bitstream representing your design, program,

and test your design on the Atlys Spartan-6 Development Board.

Methodology

The following primary steps are to be executed in order to download design onto the

Development Board:

1) Creating the project using the ISE tool.

2) Adding Source (Hardware/logic).

3) Assigning Pins using the PlanAhead software.

4) Generating design schematic.

5) Analyzing the created project.

6) Creating a bitstream.

7) Configure and test the Atlys Spartan-6 Development Board.

8) Download bitstream onto the Development Board using the Adept software.

9) Verifying design on the Development Board.

2

Create a new project and name it fourbit_adder.

3

Select Project.

Select Add Source.

4

Copy files full_adder.vhd and fourbit_adder.vhd in working directory.

Select files full_adder.vhd and fourbit_adder.vhd -> click Open.

Explain the two VHDL codes full_adder.vhd and fourbit_adder.vhd.

5

Notice added VHDL files.

Draw the 1-bit Full Adder and the 4-bit Adder circuit diagrams.

Double click Implement Design.

6

Expand (+) User Constraints -> Double-click on I/O Pin Planning (PlanAhead) - Post-

Synthesis.

Explain the role of design constraints.

7

PlanAhead software is launched.

What role does the PlanAhead software play?

8

Expand a(4).

9

Select desired pin number (Site) -> check the pin number (Fixed).

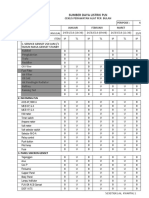

Repeat for the rest of the signals a, b, z, and cout using the pin numbers as shown the figure

below that shows the connection of the pushbuttons, slide switches, and LEDs to the Spartan-6

(FPGAs) pins:

10

The PlanAhead window should look like:

11

Explain the above schematic.

Zoom-in multiple times.

12

In the Package window zoom-in to pin A10 and verify that it is assigned to a[0]. You should

see a[0] written inside the cell at location row A column 10.

Verify the correct assignment of the other pins (a[1], a[3], a[3], b[0], b[1], b[2], b[3], b[4],

z[0], z[1], z[2], z[3], and cout) as well.

Select File -> Save Constraints.

Select File -> Exit.

Select OK.

13

Re-implement design by double-clicking on Implement Design.

14

Double-click on Generate Programming File.

Select Tools -> Schematic Viewer -> RTL

What does RTL stand for?

15

Click Ok.

Expand the (+) sign of the Signals area, select all of the signals, and click the Add -> button.

16

Click Create Schematic.

17

Describe in details the generated schematic.

Click on Generate Programming file.

Power on Spartan-6 board and connect USB cable to PROG port and to PC.

Open Digilent Adept software.

18

Select Browse and locate the generated bit file (fourbit_adder.bit).

What does a (.bit) file represent?

Click Program.

What is the role of the Program button?

19

Once the programming is finished, and if successful, the Adept software should print the

message Programming Successful and LED (DONE) is lit on the board.

To verify that the four-bit adder works correctly, use the slide switches to set inputs a and

b and watch the LEDs. Try different combinations of input values.

20

For example, if we wanted to test a = 2, b = 5, a + b = 7 we would set input a = 0010 and b =

0101 via the slide switches and the output should turn ON the LEDs (LD2, LD1, and LD0) as

shown in the figure below:

Turn off power then power on again the Spartan-6 board. Re-verify the four-bit adder

operations by trying different combinations of input values and observing the output LEDs.

Explain whats happening.

Conclusions

The ISE tools were used to create and analyze a simple project. The PlanAhead software was

used to assign pins, verify pin assignments, and generate design schematic. Then the Adept

software was used to configure and test the Atlys Spartan-6 Development Board.

References

[1] Atlys schematics http://www.digilentinc.com/Data/Products/ATLYS/Atlys_C2_sch.pdf

[2] Atlys reference manual http://www.digilentinc.com/Data/Products/ATLYS/Atlys_rm.pdf

[3] "Xilinx ISE Webpack 11". Gentoo Wiki. Gentoo Community, 2012.

[4] "Adept Application Users Manual, Digilent, 2010.

Potrebbero piacerti anche

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Huawei 1403794073312 ERAN TDD 7 0 RRU3259 DescriptionDocumento8 pagineHuawei 1403794073312 ERAN TDD 7 0 RRU3259 DescriptionOGADUSNENessuna valutazione finora

- NGK NTK Catálogo Motocicletas 2016-2017Documento372 pagineNGK NTK Catálogo Motocicletas 2016-2017ysmael romeroNessuna valutazione finora

- Sumber Daya Listrik PLN: Ceklis Perawatan Alat Per BulanDocumento14 pagineSumber Daya Listrik PLN: Ceklis Perawatan Alat Per BulanmaryantoNessuna valutazione finora

- 9910 An-H48Documento4 pagine9910 An-H48Adii HernandezNessuna valutazione finora

- M1 - Session 6Documento30 pagineM1 - Session 6Amal MonichanNessuna valutazione finora

- Lista de Precios Yim S.A.C. 21-12-20 (20+4)Documento27 pagineLista de Precios Yim S.A.C. 21-12-20 (20+4)ivelha publicidadNessuna valutazione finora

- Idealarc DC-1000: Industrial DC Multi-Process WelderDocumento2 pagineIdealarc DC-1000: Industrial DC Multi-Process WelderVenkat GupthaNessuna valutazione finora

- 8" Rewindable Submersible Motors: Franklinwater - EuDocumento16 pagine8" Rewindable Submersible Motors: Franklinwater - EudraskobulajicNessuna valutazione finora

- Reliability & Maintainability Manual of TBEA Shenyang Transformer ProductsDocumento67 pagineReliability & Maintainability Manual of TBEA Shenyang Transformer ProductsHeptolNessuna valutazione finora

- GV2ME32 TelemecaniqueDocumento2 pagineGV2ME32 TelemecaniqueRasek ResolfNessuna valutazione finora

- Single Phase Full-Wave Controlled Rectifier Fed DC DrivesDocumento3 pagineSingle Phase Full-Wave Controlled Rectifier Fed DC DrivestoshaliNessuna valutazione finora

- Casio M300 Service ManualDocumento12 pagineCasio M300 Service ManualGiovanni OlmoNessuna valutazione finora

- Service and Maintenance. SEW-EURODRIVE Driving The WorldDocumento40 pagineService and Maintenance. SEW-EURODRIVE Driving The Worldraduro100% (1)

- Bobcat 225: May 2003 Eff. W/serial Number KE582332Documento52 pagineBobcat 225: May 2003 Eff. W/serial Number KE582332juan felipe alzate aristizabalNessuna valutazione finora

- FUNAI PLF-76 Service ManualDocumento40 pagineFUNAI PLF-76 Service Manualapi-3711045Nessuna valutazione finora

- Data CommunicationDocumento15 pagineData CommunicationPrachi Arjun GuptaNessuna valutazione finora

- Poe NVR Kit: Image Model Features Package List CH USDDocumento1 paginaPoe NVR Kit: Image Model Features Package List CH USDAnel Alejo BellidoNessuna valutazione finora

- Caddy LHN 130-140-200Documento36 pagineCaddy LHN 130-140-200Sergiu Badaluta100% (3)

- Interfacing Temperature Sensor With MPLAB Xpress Evaluation Board Using I2C CommunicationDocumento13 pagineInterfacing Temperature Sensor With MPLAB Xpress Evaluation Board Using I2C CommunicationsivaNessuna valutazione finora

- Plug Setting Multiplier & Time Setting Multiplier - Electrical4u PDFDocumento8 paginePlug Setting Multiplier & Time Setting Multiplier - Electrical4u PDFNirav ChauhanNessuna valutazione finora

- Textbook Ebook You Had Me at Wolf Terry Spear All Chapter PDFDocumento43 pagineTextbook Ebook You Had Me at Wolf Terry Spear All Chapter PDFsandra.sweet418100% (6)

- Pig Signaller PDFDocumento2 paginePig Signaller PDFMargaret DaughertyNessuna valutazione finora

- CO Unit 1 Chap 1 NotesDocumento11 pagineCO Unit 1 Chap 1 NotesAmisha ShettyNessuna valutazione finora

- Equipment Electrical LayoutDocumento25 pagineEquipment Electrical LayoutAgus Dani100% (1)

- Draft - Sat Procedure For Access Control SystemDocumento11 pagineDraft - Sat Procedure For Access Control SystemVenkataramanan SNessuna valutazione finora

- Pressure Transmitter For General Industrial Applications Model A-10Documento7 paginePressure Transmitter For General Industrial Applications Model A-10brunotavernaNessuna valutazione finora

- GB-Statys 100A Rack-Operating ManualDocumento41 pagineGB-Statys 100A Rack-Operating Manualxuyen tranNessuna valutazione finora

- Abhijeet ShindeDocumento5 pagineAbhijeet ShindeAbhijeet ShindeNessuna valutazione finora

- Automatic Water Pump Controller - Full Circuit AvailableDocumento4 pagineAutomatic Water Pump Controller - Full Circuit AvailableclementNessuna valutazione finora

- Zener Diode+regulationDocumento10 pagineZener Diode+regulationammadm540Nessuna valutazione finora