Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Informe de Laboratorio 1

Caricato da

Julián A. LópezTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Informe de Laboratorio 1

Caricato da

Julián A. LópezCopyright:

Formati disponibili

IEES-1

20 Julio de 2013, Cali, Valle del Cuca, Colombia

Paper No.1

PROYECTO DE LABORATORIO No.1

OPERADORES LGICOS CON TECNOLOGAS TTL Y CMOS

Santiago Blandn, Andrs Prez.

Universidad Autnoma de Occidente

santiago.bldn@gmail.com, andresprzh@hotmail.com.

Abstract En este documento hablara sobre dos

familias lgicas la TTL y la CMOS, de las cuales se

seleccionaran una compuerta de cada una de estas

familias para realizar un anlisis y explorar algunas

caractersticas de cada familia as como tambin

configuraciones especficas.

INTRODUCCION

A medida que han pasado los aos diferentes

dispositivos electrnicos y tecnologas han permitido el

desarrollo de mejores circuitos integrados para la

implementacin de compuertas para el desarrollo de

circuitos digitales.

Cada tecnologa mediante el cual se implementan las

compuertas lgicas son llamadas familias lgicas,

actualmente unas de las ms fuertes son la TTL que es

la lgica de transistor a transistor y esta hace uso de

resistencias, diodos y transistores bipolares para la

llevar a la realidad funciones lgicas. Otra de las

familias es la CMOS tambin denominada lgica MOS

complementaria y esta mediante la implementacin de

MOSFETS que son transistores de efecto metal-oxido

semiconductor logran tambin funciones lgicas.

En ambos casos lo que se busca es llevar las funciones

lgicas a la prctica, pero el uso de diferentes

tecnologas brinda caractersticas distintas de

funcionamiento esto brinda diferentes alternativas a la

hora de disear un circuito digital e implementarlo en la

realidad debido a que los escenarios siempre son

distintos.

MARCO TEORICO

Las familias lgicas son una clasificacin para los

circuitos integrados los cuales implementan compuertas

digitales, cada familia posee su circuito electrnico

bsico, por este se realizan circuitos digitales de mayor

complejidad, dependiendo de la composiciones cada

familia cada una de estas obtienen diferentes

caractersticas de funcionamiento.

Al realizar operaciones lgicas, cuando se representa la

seal binaria a la entrada o a la salida de cada

compuerta esta solo puede tener dos valores por lo tanto

el valor de una seal representa lgica 1 y otro lgica 0.

Debido a que se utilizan dos valores de seal a los dos

valores lgicos existen dos tipos de seales asignadas a

la lgica. Debido a la algebra de Boole se asigna una

seal de funcin dual.

Teniendo una seal binaria como la de la figura 1. Un

valor dentro de la seal tiene que ser diferente al otro

para poder ser distinguido, El nivel alto se denomina H

(high) y el nivel bajo se denomina L (low), de igual

manera hay dos formas para ver la lgica de la seal, la

lgica positiva Figura 1 (a) y la lgica negativa Figura 1

(b),

(a) (b)

Figura 1. Seal Binaria. Lgica Positiva (a), Lgica

Negativa (b)

Tomada de Lgica digital y diseo de computadores,

Morris Mano.

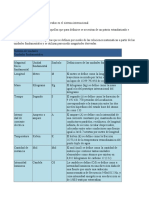

Los diferentes datasheets trabajan en trminos de H y L

y no en lgica 1 o lgica 0, en la tabla 2 se tienen los

niveles de H y L en las dos familias lgicas que

trataremos en este informe la TTL y la CMOS.

[2]

Familia

Lgica

Vcc[V] H [V] L[V]

Rango Tpico Rango Tpico

TTL 5 2,4 ~

5

3,5 0 ~

0,4

0,2

CMOS 3 ~ 10 Vcc Vcc 0 ~

0,5

0

Lgica Positiva: 1 0

Lgica Negativa: 0 1

Tabla 1. Niveles de H y L en algunas familias lgicas

El Fan-out es una caracterstica que especifica el

nmero de salidas que la salida del dispositivo puede

accionar sin distorsionar la normal operacin, una carga

normal es la cantidad de corriente necesitada para la

entrada de otra compuerta en la misma familia, la salida

del dispositivo suministra una cantidad limitada de

corriente por lo por encima de esta corriente el

dispositivo no opera bien y se encuentra sobrecargada.

Debido a que cada entrada consume cierta cantidad de

potencia de la compuerta de entrada de modo que cada

conexin adicional se agrega a la carga de la compuerta,

mediante la regla de se especifican la mxima

cantidad de carga permisible para cada salida del

circuito.

[1]

La disipacin de potencia es la potencia suministrada

necesaria para operar la compuerta y muestra la

potencia real utilizada por la compuerta, este no incluye

la potencia suministrada por otra compuerta, esta

potencia es solo debido a la fuente,

El retardo de propagacin es el tiempo promedio en el

cual se demora la transicin de propagacin de una al

de entrada a la salida, Cuando el valor de una seal

binaria varia, este cambio demora cierto tiempo

mientras la seal de entrada se propaga a la salida.

El Margen de ruido es el mximo voltaje de ruido que

se agrega a una seal de entrada que no cause un

significativo a la salida del circuito, existen dos clases

de ruido. El DC originado por la desviacin en los

niveles de voltaje de una seal y el ruido AC que es un

pulso aleatorio que se puede crear por otras seales

conmutadas, este parmetro representa la mxima seal

de ruido que puede ser tolerada por la compuerta.

[4]

( ) ( )

( ) ( )

ANALISIS Y RESULTADOS.

Para el proyecto se usaron 2 compuertas lgicas de

diferentes familias, la SN7409 y la CD4071B.

El dispositivo CD4071B, pertenece a la familia lgica

CMOS (Complementary Metal-Oxide-Semiconductor

Field Effect Transistor), la cual es una familia basada en

tecnologa de transistores MOSFET.

Este dispositivo realiza la operacin OR y se encuentra

compuesto por 4 compuertas independientes. Tabla 2.

Min [V] Max [V]

3 18

(a) Rango de operacin

Min [V] Tipo [V] Max [V]

VIH 0.7*Vcc - -

VIL - - 0.3*Vcc

VOH Vcc-0.05 Vcc -

VOL 0 0.05

(b) Rangos de nivel lgico.

Tabla 2. Rangos de voltaje para el CD4071B.

En la tabla 3 puede observarse la tabla de verdad de una

compuerta or.

A B A OR B

0 0 0

0 1 1

1 0 1

1 1 1

Tabla 3. Tabla de la verdad compuerta OR.

En la figura 2 puede verse el datasheet del CD4071B

este al permanecer a la familia CMOS como se dijo

anteriormente su composicin interna se basa a partir de

MOSFET.

Figura 2. Esquema suministrado por el datasheet del

CD4071B.

Tomada de Fairchild Semiconductor.

El dispositivo SN7409 pertenece a la familia lgica

TTL (transistor-transitor logical), la cual esta echa a

partir de resistencias, diodos y transistores de unin

bipolar (BJT), esta familia lgica tiene la caracterstica

de ser ms rpido a comparacin de la FAMILIA lgica

CMOS

El circuito integrado SN7409 realiza la operacin AND,

y est compuesto por 4 compuertas independientes, su

tabla de verdad y comportamiento lgico se pueden

observar en la tabla 5

Min [V] Max [V]

4.5 5.5

a) Rango de operacin

Min [V] Tip [V] Max [V]

VIH 2 - 5

VIL 0 - 0.8

VOH - 5 5.5

VOL 0 0.2 0.4

b) Rangos de nivel lgico

Tabla 4.rango voltaje para integrado SN7409

A B A AND B

0 0 0

0 1 0

1 0 0

1 1 1

Tabla 5. Tabla de verdad compuerta AND

En la figura 3, se puede observar el esquemtico del

circuito de una compuerta AN7409

Figura 3. Esquema suministrado por el datasheet del

CD4071B.

Tomado de Texas Instruments

Simulacin

En la figura 4 se encuentra el esquema simulado y la

grfica para para dos diferentes seale lgicas de

entrada, como se pudo ver en la tabla 3 en la figura 4

solo se presenta un cero en la salida cuando las seales

U3 y U1 tienen un valor L (0) y mientras en una de las

seales U3 y U1 exista un H (1) la salida ser un H (1).

Figura 4. Simulacin del CD4071B.

En la figura 5 se observa el esquema de la compuerta

TTL SN7409, si se compara este esquema con el de la

figura 2 se puede ver que se le ah adicionado una

resistencia roll-up entre la tencin de retroalimentacin

y la salida de la compuerta AND, esto dado que se

necesita que haya un voltaje entre el emisor y el

colector cuando el transistor est en corte.

En la figura 5 tambin se puede observar la respuesta

del integrado ante diferentes entradas, de tal manera

que solo entregue un H (1) como salida, cuando las

entradas tengan un valor H (1).

Figura 5. Simulacin SN7409

El margen de ruido

El margen de ruido indica la cantidad de ruido que es

necesario para afectar una tencin de salida a tal punto

de que no se pueda reconocer como una entrada lgica,

este margen de ruido se divide en margen de ruido en

estado alto y margen de ruido en estado bajo, la cual

mide el margen, para salidas altas y bajas

respectivamente. Estos mrgenes miden principalmente

la mxima amplitud de una tencin, para que la seal de

salida siga considerndose 1 o 0 segn si el margen de

ruido es de estado alto o bajo respectivamente.

En la figura 6 se puede observar cual es el margen de

ruido en un esquema.

Q1

IRF9240

VCC 5V

Q4

IRF131

Q5

IRF131

Q3

IRF9240

Q2

IRF131

Q7

IRF131

Q8

IRF9240

Q9

IRF131

Q10

IRF9240

Q6

100um 100um

U3

100 Hz

U1

50 Hz

OUT

1k

Q1

2N2222A

Q2

2N2222A

Q3

2N2222A Q4

2N2222A

Q5

2N2222A

Q7

2N2222A

R1

4k

R2

2k

R3

1.8k

R5

800

R6

1k

V1

5 V

D1

DIODE_VIRTUAL

D5

DIODE_VIRTUAL

D2

DIODE_VIRTUAL

R4

1k

U1

1kHz

U2

0.5kHz

Figura 6. Margen del ruido del esquema.

De esto se puede ver que el margen de ruido en estado

alto se calcula, haciendo la diferencia entre V

OHmin

y

V

IHmin

.

SN7409

Tambin se puede observar que el margen de ruido en

estado bajo se calcula con la diferencia entre V

ILMAX

y

V

OLmax.

CD4071b

Impedancia entrada

Para las hallar las impedancias de entradas, de las

diferentes compuertas lgicas utilizadas, es necesario

saber las los rangos lgicos de voltaje y te tencin de

entrada del dispositivo en especfico, conociendo esto

se puede aplicar la ley de ohm y hallar la impedancia

de entrada

Impedancia entrada para integrado SN7409:

De esta ecuacin se obtiene que la

impedancia de entrada en estado alto es

igual a:

Tambin se puede obtener la impedancia de entrada en

estado bajo:

Impedancia entrada para integrado CD4071B

Impedancia entrada altos:

Impedancia entrada bajos

Impedancia salida

La impedancia de salida se puede hallar de la misma

manera que la impedancia de entrada, usando la

siguiente ecuacin:

Impedancia salida SN7409

Impedancia de entrada en estado alto es igual a:

Impedancia de entrada en estado bajo:

Impedancia salida CD4071

Impedancia de entrada en estado alto es igual a:

Impedancia de entrada en estado bajo:

Fan-out

El Fan-out es la cantidad de entradas que una compuerta

lgica puede controlar sin afectar sus especificaciones

de carga, esta medida depende tanto de las

caractersticas de salida como de las caractersticas de

entrada que se estn controlando. Cabe mencionar que

el fan-out de las compuertas de la familia CMOS tiene

resolucin ilimitada, debido a que no necesitan

suministrar corriente a las compuertas siguientes.

Fan-out con corrientes

El fan out se puede calcular con las corrientes de

entrada y de salida en alto y bajo que posee el

dispositivo, dando como resultado 2 respuestas al fan-

out, una alta y otra baja, por este motivo, para hallar el

fan-out se seleccionar el de menor valor

[5]

| |

| |

|

Dado que el fan-out, menor es el alto (

) se

toma a este como el valorel valor real que es 6 para el

integrado SN7409.

Fan out mtodo impedancias.

Con este mtodo lo que se hace es usar la ley de ohm

para obtener ecuacin de fan-out en trminos de

impedancias y tencin.

[5]

Sensibilidad a la electricidad esttica

La familia lgica TTL no es sensible a la electricidad

esttica debido a que los daos generados por la esttica

se basan que al estar en contacto con los pines se crea

un divisor de tensin entre el cuerpo en contacto y el

pin de la compuerta debido en que los TTL las

impedancias son levemente grande en la entrada

pequea en la salida la tensin no cae totalmente en la

compuerta a diferencia de los CMOS que debido a su

composicin de MOSFETS tienen grandes impedancias

de entrada por lo tanto las cargas electro estticas

pueden crear voltajes peligrosos para el circuito, esto se

evita en cierta medida utilizando protecciones con

diodos zener pero de igual manera en algunos casos con

solo tocar los pines es suficiente para echar a perder el

integrado de la familia CMOS

[4]

Disipacin potencia

Las compuertas que disipan menos potencia son las de

la familia CMOS esto se debe de igual manera a la alta

impedancia el consumo de un dispositivo CMOS se

encuentra alrededor de los nW, esto se puede corroborar

por la relacin entre potencia y voltaje y impedancia.

Drenaje corriente entrada

Debido que la impedancia de entrada de las compuertas

de la familia TTL es mucho menor que la CMOS en la

familia TTL drenara menos corriente en la entrada.

Rango de tensin de alimentacin

Como se pudo ver en los dataheet de ambos

dispositivos integrados el SN7409 TTL solo tiene un

rango de alimentacin de 0.75 V a diferencia del CMOS

CD4071B que su rango es de 15V, ambos rangos son

caractersticos de cada familia.

Rango frecuencia de operacin

Debido a la velocidad de transmisin de cada familia se

sabe que por definicin los dispositivos TTL tienen una

mejor velocidad de transmisin que los CMOS. Tabla 6.

Min [ns] Typ [ns] Max [ns]

T PLH 21 32

T PHL 16 24

(a) Tiempo de propagacin para el SN7409

Vcc [v] Typ [ns] Max [ns]

T PHL,

T PLH

5 125 250

10 60 120

15 45 90

(b) Tiempo de propagacin CD4071B

Tabla 6. Tiempo de propagacin para los dos

dispositivos usados.

Como se pudo ver en la anterior tabla los tiempos de

propagacin el mximo para el SN7409 es de 32ns y

para el CD4071B es de 250 nS una gran diferencia, de

igual manera con esta informacin se corrobora lo

mencionado anteriormente de las caractersticas de las

familias.

Configuracin Colector abierto

La configuracin de colector abierto es una

configuracin especfica para la familia TTL utilizada

para excitacin de dispositivos tales como rels

lmparas y leds, la construccin de un sistema de base

comn y la conformacin lgica alambrada. Debido a

que estos necesitan un mayor consumo de corriente que

la familia TTL no puede manejar. Figura 7.

Al utilizar colector abierto se obtiene una mayor

capacidad en el manejo de corriente y tensin. En la

figura se puede observar un ejemplo de una compuerta

TTL con colector abierto. Mediante el uso de una

resistencia limitada externa al tener una salida baja el

transistor Q3 se satura, haciendo que la corriente

conduzca desde la fuente hasta tierra accionando la

lmpara

[2]

Figura 7. Esquema transistorizado de circuito familia

TTL con configuracin de colector abierto.

Compuerta tri-estado

Las compuertas de 3 estados por su nombre se

componen de tres estados en la salida. Un estado Alto,

un estado bajo y un estado de alta impedancia.

El estado de alta impedancia permite una conexin

directa de muchas salidas a una lnea comn,

remplazando las compuertas de colector abierto en

configuracin de bus. Cabe de resaltar que hay una

pequea corriente de fuga de entrada o salida asociada

con el tercer estado pero esta es muy pequea y se

presenta en una configuracin totmico. En si este

estado lo que genera es una impedancia alta a tierra y a

Vcc.

[1]

CONCLUSIONES.

Los dispositivos electrnicos de los se basan cada

familia lgica le brindan caractersticas nicas respecto

a las otras haciendo de esta manera algunas mucho

mejores para ciertas aplicaciones

Para un dispositivo CMOS adquiere una mayor

velocidad de propagacin a una mayor potencia.

La ventaja de trabajar con dispositivos CMOS es la baja

potencia para la cual estos trabajan.

Un dispositivo de la familia TTL es mucho ms rpido

operando que un dispositivo de la familia CMOS.

Es importante a la hora de disear tener en cuenta el

Fan-in y el Fan-out de los dispositivos para no alterar

los niveles lgicos durante la operacin.

Para el accionamiento de dispositivos que exigen ms

corriente en la familia TTL se utiliza la configuracin

de colector abierto logrando manejar un poco ms de

corriente.

La resistencia de externa en la configuracin abierta

permite obtener los 3 estados

Al trabajar con una compuerta debe tenerse en cuenta a

que familia pertenece y las caractersticas principales de

trabajo de esta.

La gran impedancia de entrada y baja impedancia de

salida brinda a la familia CMOS buenas caractersticas

pero tambin lo hace sensible a la electricidad esttica.

BIBLIOGRAFIA

[1] WAKERLY, Jhon F. Diseo digital Principios y

prcticas.

[2] MORRIS Mano. Lgica digital y diseo de

computadores, Editorial Prentice-Hall Internacional

[3]Ortega Carlos, Flores Gonzales Yamil, Electronica

digital II. Circuitoss TTL.

[4] Ventura Grandes Henry Edison, Introduccin a la

electrnica digital, UNI-FIEE

[5] Ronald J. Tocci Digital systems Principles and

applications

Potrebbero piacerti anche

- Decreto 0780 de 2016 Decreto Unico Sector SaludDocumento672 pagineDecreto 0780 de 2016 Decreto Unico Sector SaludCANDIOTA DE VINOS Y LICORES SANessuna valutazione finora

- Politicas Públicas para La Salud PúblicaDocumento6 paginePoliticas Públicas para La Salud PúblicaJulián A. López100% (1)

- Proceso Habilitación UCIDocumento51 pagineProceso Habilitación UCIJulián A. LópezNessuna valutazione finora

- Protocolo DICOMDocumento29 pagineProtocolo DICOMJulián A. LópezNessuna valutazione finora

- Estado del arte de la ingeniería clínicaDocumento7 pagineEstado del arte de la ingeniería clínicaJulián A. López100% (1)

- Conversion de Binario A BCDDocumento4 pagineConversion de Binario A BCDJulián A. LópezNessuna valutazione finora

- Laboratorio ElectrocardiogramaDocumento3 pagineLaboratorio ElectrocardiogramaJulián A. LópezNessuna valutazione finora

- Lista de Combinaciones de Teclas y Alias de Comandos de AutoCADDocumento41 pagineLista de Combinaciones de Teclas y Alias de Comandos de AutoCADRomer Aramayo Calle100% (1)

- EstequiometríaDocumento50 pagineEstequiometríaFranciscoGonzalezNessuna valutazione finora

- MA263 2020 01 Sesi N Presencial 13.3 Clase Integradora PC3 PDFDocumento4 pagineMA263 2020 01 Sesi N Presencial 13.3 Clase Integradora PC3 PDFBRIAN OSCANOANessuna valutazione finora

- Anillo Con Distrib D Carga No UniformelDocumento4 pagineAnillo Con Distrib D Carga No Uniformelkoalagris100% (1)

- Clase 1 (Fisica)Documento13 pagineClase 1 (Fisica)Oliver MichelNessuna valutazione finora

- Tierra - David Brin PDFDocumento637 pagineTierra - David Brin PDFEdith PatiñoNessuna valutazione finora

- 12CyT 02lasmaquinasdeleonardoDocumento10 pagine12CyT 02lasmaquinasdeleonardosarinita58Nessuna valutazione finora

- Mejora del sistema de agua potable de LacabambaDocumento3 pagineMejora del sistema de agua potable de LacabambaSarita Santiago MirandaNessuna valutazione finora

- Practica 2 Hombre en MovimientoDocumento7 paginePractica 2 Hombre en MovimientoJuan Daniel Caraballo VillavicencioNessuna valutazione finora

- Sistema puesta tierra horizontalDocumento6 pagineSistema puesta tierra horizontalCarlos MegoNessuna valutazione finora

- Instituto Tecnológico de Iztapalapa III Ing. CivilDocumento10 pagineInstituto Tecnológico de Iztapalapa III Ing. CivilEduardo PilleNessuna valutazione finora

- Termodinámica conceptos fluidos masa presiónDocumento3 pagineTermodinámica conceptos fluidos masa presiónJorge DuranNessuna valutazione finora

- Flujo Multifasico Tuberias HorizontalesDocumento25 pagineFlujo Multifasico Tuberias HorizontalesRaul Alberto Jimenez Cruz100% (1)

- Sondeos Electricos Verticales y Calicatas ElectricasDocumento34 pagineSondeos Electricos Verticales y Calicatas ElectricasWilson Jeff Espinoza Condor0% (1)

- ModelDelft3DWaveDocumento9 pagineModelDelft3DWaveSully Rivas CaceresNessuna valutazione finora

- No Se Pueden CopiarDocumento89 pagineNo Se Pueden CopiarmarioNessuna valutazione finora

- Origen de La Teoría AtómicaDocumento10 pagineOrigen de La Teoría Atómicamaria bayonaNessuna valutazione finora

- Sesión 2 Resitencia GADocumento32 pagineSesión 2 Resitencia GACRISTIAN LEONARDO RAMOS SERRANONessuna valutazione finora

- Analisis SustentacionDocumento39 pagineAnalisis SustentacionJavier PiconNessuna valutazione finora

- Ecuacion de EstadoDocumento8 pagineEcuacion de EstadoStalin ChelaNessuna valutazione finora

- Ejercicios de Curso de Física y Química de 4º 1 PDFDocumento9 pagineEjercicios de Curso de Física y Química de 4º 1 PDFhousegrjNessuna valutazione finora

- Esterilización hospitalaria guíaDocumento12 pagineEsterilización hospitalaria guíaMaria teresaNessuna valutazione finora

- Practica - Vectores #03Documento3 paginePractica - Vectores #03Hans Jheferson Nuñez Suxe50% (2)

- Aspectos Geologicos en La Construccion de TunelesDocumento2 pagineAspectos Geologicos en La Construccion de Tuneles8kathleen100% (1)

- Conservación TérmicaDocumento3 pagineConservación TérmicaAnita Espinosa80% (5)

- Trabajo Practico El UniversoDocumento8 pagineTrabajo Practico El UniversoFabricio Martinez50% (2)

- Dimensionamiento de Banco de Baterías-1Documento5 pagineDimensionamiento de Banco de Baterías-1gilbertomjcNessuna valutazione finora

- Bertin PerezDocumento6 pagineBertin PerezBertin Perez RamosNessuna valutazione finora