Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Simoreg1q Device Braking To Defined Speed PDF

Caricato da

Gregory StewartDescrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Simoreg1q Device Braking To Defined Speed PDF

Caricato da

Gregory StewartCopyright:

Formati disponibili

SIMOREG DC Master

6RA70 Series

Application

SIMOREG 1Q-device, braking to

defined speed using reversing

Microprocessor-Based Converters from 6kW to 1900kW

for Variable-Speed DC Drives

Edition 01

Edition 01 02.01

Siemens AG 2001 All rights reserved

NOTE

This application documentation does not purport to handle or take into account all of the equipment

details or versions or to cover every conceivable operating situation or application.

If you require more detailed information, or if special problems occur, which are not handled in enough

detail in this document, please contact your local Siemens office.

The contents of this application documentation are not part of an earlier or existing agreement or legal

contract and neither do they change it. The actual purchase contract represents the complete liability of

the A&D Variable-Speed Drives Group of Siemens AG. The warrant conditions, specified in the contract

between the two parties, is the only warranty which will be accepted by the A&D Variable-Speed Drives

Group. The warranty conditions specified in the contract are neither expanded nor changed by the

information provided in this application documentation.

WARNING

These converters contain hazardous electrical voltages, hazardous rotating machinery (fans)

and control rotating mechanical components (drives). Death, serious bodily injury or

substantial damage to property will occur if the instructions in the relevant operating manuals

are not observed.

Only qualified personnel who are thoroughly familiar with all safety notices contained in the

operating instructions as well as erection, operating and maintenance instructions must be

allowed to work on these devices.

Successful and safe operation of this equipment is dependent on careful transportation, proper

storage and installation as well as correct operation and maintenance.

The reproduction, transmission or use of this document or contents is

not permitted without express written authority. Offenders will be liable

for damages. All rights, including rights created by patent grant or

registration of a utility model or design, are reserved.

We have checked that the contents of this publication agree with the

hardware and software described herein. Nonetheless, differences

might exist and therefore we cannot guarantee that they are completely

identical. The information given in this publication is reviewed at regular

intervals and any corrections that might be necessary are made in the

subsequent printings. Suggestions for improvement are welcome at all

times.

SIMOREG is a registered trademark of Siemens

02.01 Edition 01

Siemens AG 3-10

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

0 Contents

Page

1 Applications...........................................................................................................4

1.1 Function description ........................................................................................................................... 4

2 Parameter list ........................................................................................................6

3 Function diagrams................................................................................................8

Edition 01 02.01

4-10 Siemens AG

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

1 Applications

Using this application note, it is possible to implement a braking function in a 1-Q SIMOREG. In comparison

to the 4-Q Simoreg, where braking is performed automatically depending on the applied setpoint, the braking

process is started using a binary signal and a reduced setpoint value.

NOTICE

The setpoint has to be positive. Negative values can not be used, because during the internal field

reversing sequence, the actual speed value is inverted, and closed loop control would not be functional.

This Application Note is especially useful for drives, that do not need 4-Q functionality, but require braking to

a defined speed > 0. (for example paper mills, operating mode change from operation to crawl ).

ACTIVATION of Option S00 is required for this application.

The application is based on direction of rotation reversal using field reversal described in operating manual

section 9.18.1.

WARNING

Also make sure, the appropriate overvoltage protection is present.

(See Application Note Simoreg as a field supply unit, Section 5)

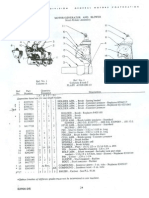

1.1 Function description

Using a binary signal, braking is initialized, requesting field reversal, and setting the main setpoint to the

braking setpoint. According to section 9.18.1 the internal sequence for field reversal is initialized. The field is

reversed, reducing the speed of the motor. Once the setpoint has been reached, a limit-value monitor resets

the RS-flip flop initializing the sequence to establish the previous field state.

The braking setpoint stays active, until a reset signal is applied to the brake to defined speed storing RS-flip

flop.

For example

Should the signal braking to defined speed be used to reset the RS-flip flop, an inverter has to be inserted

and connected to U416.2 (RS-flip flop Reset).

This example is shown in the function diagram and highlighted in gray. If one of SIMOREGs digital inputs is

used, the inverted signal is provided by default, eliminating the need for an inverter.

The braking operation can be canceled any time (even when field reversal is active), by resetting this RS-flip

flop.

02.01 Edition 01

Siemens AG 5-10

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

To prevent the brake setpoint from exceeding the main setpoint, a limitter is used. The adjoining multiplexer

is used to disable altering of the brake setpoint while braking is active.

(Contact function diagrams at the end of the document for details)

Please note that at the moment of field reversal, the armature current and field current are 0.

The hysteresis ( U 188 ) has to be set according to system specification.

The hysteresis value depends on inertia, drive friction, etc. .If this is not taken into account, the drives speed

is reduced below the setpoint, therefore accelerating again to reach the appropriate speed once the original

field direction is present. The hysteresis ( U 188 ) should be set to a value for the limiter to react in advance.

If the brake setpoint reaches the hysteresis of the actual value prior to braking, the signal brake to defined

speed is blocked, and field reversal is not performed.

Also make sure, that the function blocks of option S00 are enabled and processed in correct order. Contact

SIMOREG DC MASTER operating instructions Section 11.79,11.81 and 11.82 for details.

The processing sequence has to be maintained according to the following list:

Limit-value monitor block 70

Inverter block 180

(Inverter block 181 OPTIONAL)

AND block 120

RS-flip-flop block 216

Limiter block 65

Multiplexer block 86

OR block 150

Timer(pulse generator) block 240

RS-flip-flop block 215

Connector changeover switch block 90

Sampling times have to be set using parameters U950,U951 and U952 according to SIMOREG Operating

Manual. By default, sampling time for all of the freely assignable function blocks used in this application note

is set to 1.

Edition 01 02.01

6-10 Siemens AG

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

2 Parameter list

Parameter Description Value

U175.1 Source for input signal limiter 1 Braking setpoint source

U175.2 Positive limit limiter 1 Main setpoint

U175.3 Negative limit limiter 1 0

U310.1 Source for control bits for the

multiplexer; is used for freezing the

braking setpoint during braking

operation.

Source of Brake signal

U311.1 Multiplexer input 1 K9167 value of limited brake setpoint

U311.2 Multiplexer input 2 K9450 value of Multiplexer output for

setpoint freezing

U380 Inverter for signal from limit-value

monitor

B9162 limit-value monitor output (A=B)

U320.1 And input 1 Signal brake to defined speed. Source

according to system specification (for

example Digitalinput, or Profibus,...)

U320.2 And input 2 B9450 inverter output

U416.1 RS-flip-flop set B9350 And output

U416.2 RS-flip-flop reset System specific; see description for

details.

U241 Connector changeover switch; source

for control signal

Source of Brake signal

U240.1 Connector changeover switch;

Source 1

Source of main setpoint

(for example K207)

U240.2 Connector changeover switch;

Source 2

K9450 braking setpoint

P443 Source of main setpoint K9210 output of connector changeover

switch

U185.1 Limit-value monitors with filtering,

Source signal A

K166 actual speed value (absolute value)

U185.2 Limit-value monitors with filtering,

Source signal B

K9450 multiplexer output

U188 Hysteresis setting Setting according to system

specifications

U440.1 Timer source; set pulse generation for

RS-flip-flop (block 215) field reversal

B9552 RS-flip-flop output (block 216)

U441 Time for timer 1 (length of pulse) 0,1->100ms

U442 Mode of timer 1 3 = pulse generation

U415.1 Source of RS-flip flop Set signal B9580 TIMER 1 output

U415.2 Source of RS-flip flop Reset signal B9380 OR 1 output

U350.1 OR 1 Source 1 B9162 limit-value monitor output

U350.2 OR 1 Source 2 B9553 RS-flip-flop (block 216) inverted

output

02.01 Edition 01

Siemens AG 7-10

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

Parameter Description Value

U977 Enable option S00 PIN-Number (Contact Operating Manual

section 11.82)

n978 S00 enabled display

U960 S00 execution sequence Index 1 = 70 (Limit-value monitor)

Index 2 = 180 (Inverter)

Index 3 = 120 (And)

Index 4 = 216 (RS-flip flop)

Index 5 = 65 (limiter)

Index 6 = 86 (Multiplexer)

Index 7 = 150 (Or)

Index 8 = 240 (Timer)

Index 9 = 215 (RS-flip flop)

Index 10 =90 (Connector changeovr. sw.)

U950-U952 Sampling time settings for the freely

assignable function blocks. (Contact

Simoreg operating manual section

11.79 for details)

All function bolocks used in this

Application Note, have to be processed in

time slice No. 1.

Edition 01 02.01

8-10 Siemens AG

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

3 Function diagrams

8

7

5

6

4

3

2

1

4

6

4

7

M

4

8

5

4

M

X

1

7

1

(

C

U

D

1

)

M

K

2

0

K

2

1

k

2

0

k

2

1

R

S

V

1

1

C

1

1

D

1

3

C

3

D

*

)

R

S

R

S

V

1

k

2

0

k

2

1

P

5

8

0

.

B

(

0

)

B

0

2

6

0

B

0

2

6

1

P

5

8

1

.

B

(

0

)

B

P

0

9

2

(

0

,

0

.

.

.

1

0

,

0

s

)

P

7

7

1

(

0

)

B

P

7

7

5

=

0

P

7

7

0

.

0

1

=

0

P

7

7

2

(

0

)

B

P

7

7

0

.

0

2

=

0

2

6

0

2

6

1

P

7

7

6

=

0

B

9

5

5

0

K

0

1

6

7

B

0

2

1

5

B

0

2

1

6

D

i

r

e

c

t

i

o

n

o

f

r

o

t

a

t

i

o

n

r

e

v

e

r

s

a

l

u

s

i

n

g

f

i

e

l

d

r

e

v

e

r

s

a

l

B

r

a

k

i

n

g

w

i

t

h

f

i

e

l

d

r

e

v

e

r

s

a

l

F

o

r

w

a

r

d

d

i

r

e

c

t

i

o

n

R

e

v

e

r

s

e

d

i

r

e

c

t

i

o

n

F

i

e

l

d

r

e

v

e

r

s

a

l

w

i

t

h

S

I

M

O

R

E

G

s

i

n

g

l

e

-

q

u

a

d

r

a

n

t

c

o

n

v

e

r

t

e

r

C

o

n

t

r

o

l

l

o

g

i

c

f

o

r

f

i

e

l

d

r

e

v

e

r

s

a

l

(

n

o

t

i

n

v

e

r

t

e

d

)

*

)

P

r

o

t

e

c

t

i

v

e

c

i

r

c

u

i

t

a

)

w

i

t

h

p

r

o

t

e

c

t

i

v

e

r

e

s

i

s

t

o

r

1

0

0

0

V

R

S

=

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

I

f

i

e

l

d

r

a

t

e

d

b

)

w

i

t

h

v

a

r

i

s

t

o

r

A

p

r

o

t

e

c

t

i

v

e

c

i

r

c

u

i

t

w

i

t

h

v

a

r

i

s

t

o

r

c

a

n

b

e

u

s

e

d

i

f

t

h

e

f

o

l

l

o

w

i

n

g

a

p

p

l

i

e

s

:

I

f

i

e

l

d

r

a

t

e

d

2

*

L

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

<

4

0

0

W

s

2

R

S

1

.

5

k

V

1

=

B

3

2

k

4

2

0

(

S

I

O

V

,

b

l

o

c

k

v

a

r

i

s

t

o

r

)

(

n

o

t

i

n

v

e

r

t

e

d

)

I

f

<

I

f

m

i

n

(

f

r

o

m

S

h

e

e

t

M

e

s

s

a

g

e

s

2

)

I

f

<

I

f

x

(

f

r

o

m

S

h

e

e

t

M

e

s

s

a

g

e

s

2

)

1

=

S

w

i

t

c

h

o

n

f

i

e

l

d

c

o

n

t

a

c

t

o

r

1

(

p

o

s

i

t

i

v

e

f

i

e

l

d

d

i

r

e

c

t

i

o

n

)

1

=

S

w

i

t

c

h

o

n

f

i

e

l

d

c

o

n

t

a

c

t

o

r

2

(

n

e

g

a

t

i

v

e

f

i

e

l

d

d

i

r

e

c

t

i

o

n

)

A

c

t

u

a

l

s

p

e

e

d

v

a

l

u

e

(

s

i

g

n

e

d

)

.

0

1

(

3

,

0

s

)

:

D

e

l

a

y

t

i

m

e

f

o

r

f

i

e

l

d

r

e

d

u

c

t

i

o

n

b

e

f

o

r

e

o

p

e

n

i

n

g

o

f

t

h

e

c

u

r

r

e

n

t

f

i

e

l

d

c

o

n

t

a

c

t

o

r

.

0

2

(

0

,

2

s

)

:

D

e

l

a

y

t

i

m

e

b

e

f

o

r

e

a

c

t

u

a

t

i

o

n

o

f

t

h

e

n

e

w

f

i

e

l

d

c

o

n

t

a

c

t

o

r

.

0

3

(

0

,

1

s

)

:

D

e

l

a

y

t

i

m

e

b

e

f

o

r

e

e

n

a

b

l

e

o

f

t

h

e

f

i

e

l

d

f

i

r

i

n

g

p

u

l

s

e

s

.

0

4

(

3

,

0

s

)

:

D

e

l

a

y

t

i

m

e

a

f

t

e

r

f

i

e

l

d

b

u

i

l

d

-

u

p

b

e

f

o

r

e

a

r

m

a

t

u

r

e

e

n

a

b

l

e

B

i

n

a

r

y

o

u

t

p

u

t

T

e

r

m

i

n

a

l

4

6

/

4

7

(

s

e

e

S

h

e

e

t

"

B

i

n

a

r

y

o

u

t

p

u

t

s

"

)

B

i

n

a

r

y

o

u

t

p

u

t

T

e

r

m

i

n

a

l

4

8

/

5

4

(

s

e

e

S

h

e

e

t

"

B

i

n

a

r

y

o

u

t

p

u

t

s

"

)

(

n

o

d

e

l

a

y

)

(

n

o

d

e

l

a

y

)

R

e

v

e

r

s

e

p

o

l

a

r

i

t

y

a

c

t

u

a

l

s

p

e

e

d

v

a

l

u

e

K

0

1

6

7

t

o

S

h

e

e

t

"

S

p

e

e

d

c

o

n

t

r

o

l

l

e

r

(

2

)

"

S

h

e

e

t

1

02.01 Edition 01

Siemens AG 9-10

SIMOREG DC Master Applikation SIMOREG 1Q-device, braking to defined speed using reversing

8

7

5

6

4

3

2

1

.

0

2

.

0

3

B

+

B

X

<

B

X

>

B

+

B

+

B

y

x

y

x

-

1

6

5

B

9

1

5

1

K

4

3

3

K

0

.

0

1

U

1

7

5

K

0

9

1

6

5

9

1

6

6

B

9

1

5

0

K

9

1

6

6

K

9

1

6

7

U

3

1

0

(

0

)

B

9

5

5

2

BB

.

0

1

.

0

2

U

3

1

1

(

0

)

K

9

1

6

7

K

9

4

5

0

.

0

1

.

0

1

.

0

1

.

0

1

.

0

1

.

0

1

KKKKKK

K

9

4

5

0

.

0

1

.

0

2

.

0

3

8

6

.

Y

1 0

9

0

U

2

4

1

(

0

)

B

9

5

5

2

K

9

2

1

0

.

0

1

.

0

2

U

2

4

0

(

0

)

K

2

0

7

K

9

4

5

0

P

4

4

3

K

9

2

1

0

0

B

A

<

B

A

=

B

A

|

A

|

<

B

A

B

A

B B

U

1

8

8

B

A

00 0

<

1

>

.

0

1

.

0

2

U

1

8

8

U

1

8

8

U

1

8

8

U

1

8

8

/

2

7

0

B

9

1

6

0

B

9

1

6

2

B

9

1

6

1

0

,

0

0

.

.

.

1

9

9

,

9

9

U

1

8

8

(

0

,

0

0

)

0

.

.

.

1

0

0

0

0

m

s

U

1

8

7

(

0

)

U

1

8

5

K

1

6

6

K

9

4

5

0

0

9

1

8

1

K

9

1

8

0

Q

(

Q

=

1

)

(

Q

=

0

)

Q

.

0

1

.

0

2

1

<

1

>

2

1

6

B

9

5

5

2

B

9

5

5

3

U

4

1

6

(

0

)

B

9

3

5

0

B

T

0

T

O

1

T

O

2

T

T

T

3

1

2

4

0

.

0

1

.

0

2

U

4

4

1

(

0

,

0

0

0

)

=

0

,

1

(

0

,

0

0

0

.

.

.

6

0

,

0

0

0

s

)

U

4

4

2

(

0

)

=

3

B

9

5

8

0

B

9

5

8

1

U

4

4

0

(

0

)

B

9

5

5

2

B

&

.

0

1

.

0

2

.

0

3

1

2

0

U

3

2

0

(

1

)

BB

9

4

5

0

B

B

9

3

5

0

1

1

8

0

B

9

4

5

0

U

3

8

0

(

0

)

B

9

1

6

2

1

1

8

1

B

9

4

5

1

U

3

8

1

(

0

)

B

2

)

.

0

1

.

0

2

.

0

3

1

1

5

0

B

9

3

8

0

U

3

5

0

(

0

)

B

9

1

6

2

B

9

5

5

3

B

1

)

1

)

1

)

Q

(

Q

=

1

)

(

Q

=

0

)

Q

.

0

1

.

0

2

1

<

1

>

2

1

5

B

9

5

5

0

B

9

5

5

1

U

4

1

5

(

0

)

B

9

5

8

0

B

9

3

8

0

S

h

e

e

t

2

1

)

B

r

a

k

e

s

e

t

p

o

i

n

t

1

)

M

a

i

n

s

e

t

p

o

i

n

t

S

e

t

p

o

i

n

t

c

h

a

n

g

e

o

v

e

r

B

r

a

k

e

t

o

d

e

f

i

n

e

d

s

p

e

e

d

B

r

a

k

e

t

o

d

e

f

i

n

e

d

s

p

e

e

d

/

r

e

t

u

r

n

t

o

p

r

e

v

i

o

u

s

s

p

e

e

d

B

S

P

.

.

.

.

.

.

.

.

.

B

r

a

k

e

s

e

t

p

o

i

n

t

A

F

R

.

.

.

.

.

.

.

.

.

A

b

o

r

t

F

i

e

l

d

R

e

v

e

r

s

a

l

P

O

W

E

R

O

N

P

O

W

E

R

O

N

t

o

m

a

i

n

s

e

t

p

o

i

n

t

P

4

4

3

S

I

M

O

R

E

G

D

C

M

a

s

t

e

r

,

O

p

e

r

a

t

i

n

g

I

n

s

t

r

u

c

t

i

o

n

s

S

e

c

t

i

o

n

8

,

S

h

e

e

t

G

1

3

0

H

y

s

t

e

r

e

s

i

s

F

i

l

t

e

r

t

i

m

e

A

c

t

u

a

l

v

a

l

u

e

O

N

d

e

l

a

y

O

F

F

d

e

l

a

y

O

N

/

O

F

F

d

e

l

a

y

P

u

l

s

e

g

e

n

e

r

a

t

o

r

M

o

d

e

1

=

R

e

s

e

t

P

u

l

s

e

g

e

n

e

r

a

t

o

r

F

S

F

S

F

S

t

o

S

h

e

e

t

1

,

P

5

8

0

1

)

C

o

n

n

e

c

t

o

r

/

B

i

n

n

e

c

t

o

r

a

s

s

i

g

n

m

e

n

t

s

a

r

e

s

y

s

t

e

m

/

a

p

p

l

i

c

a

t

i

o

n

s

p

e

c

i

f

i

c

2

)

T

h

i

s

f

u

n

c

t

i

o

n

b

l

o

c

k

i

s

o

p

t

i

o

n

a

l

.

I

t

i

s

o

n

l

y

u

s

e

d

t

o

i

n

v

e

r

t

t

h

e

S

i

g

n

a

l

"

b

r

a

k

e

t

o

d

e

f

i

n

e

d

s

p

e

e

d

"

,

t

o

r

e

s

e

t

t

h

e

R

S

-

f

l

i

p

f

l

o

p

a

n

d

c

h

a

n

g

e

b

a

c

k

t

o

t

h

e

o

r

i

g

i

n

a

l

s

p

e

e

d

.

T

h

e

b

l

o

c

k

i

s

n

o

t

n

e

e

d

e

d

,

i

f

s

e

p

e

r

a

t

e

s

i

g

n

a

l

o

r

i

n

v

e

r

t

e

d

"

b

r

a

k

e

t

o

d

e

f

i

n

e

d

s

p

e

e

d

"

s

i

g

n

a

l

(

S

i

m

o

r

e

g

d

i

g

i

t

a

l

i

n

p

u

t

)

i

s

a

v

a

i

l

a

b

l

e

.

U

4

1

6

.

2

(

R

S

-

f

l

i

p

f

l

o

p

2

1

6

,

r

e

s

e

t

)

h

a

s

t

o

b

e

s

e

t

t

o

t

h

e

a

p

r

o

p

r

i

a

t

e

s

o

u

r

c

e

.

B

S

P

B

S

P

A

F

R

A

F

R B

S

P

Edition 01 02.01

Siemens AG

Elektronikwerk Wien

PO Box 83, A-1211 Vienna

Siemens AG, 2001

Subject to change without prior notice

Siemens Aktiengesellschaft SIMOREG DC Master Application

SIMOREG 1Q-device, braking to defined speed using

reversing

Printed in Austria

Potrebbero piacerti anche

- E - Service - 530223 Control Boards OverviewDocumento7 pagineE - Service - 530223 Control Boards OverviewGregory StewartNessuna valutazione finora

- Samsung+CL21M6WKX XAO+CL21A11MQKX+Chassis K57A (N)Documento53 pagineSamsung+CL21M6WKX XAO+CL21A11MQKX+Chassis K57A (N)Gregory StewartNessuna valutazione finora

- User ManualDocumento1 paginaUser ManualGregory StewartNessuna valutazione finora

- SMD CatalogDocumento80 pagineSMD Catalogpbradaric91% (11)

- Samsung K57ADocumento31 pagineSamsung K57ADavid Argote BellidoNessuna valutazione finora

- Marketing ProgramsDocumento8 pagineMarketing ProgramsGregory StewartNessuna valutazione finora

- SMD CatalogDocumento80 pagineSMD Catalogpbradaric91% (11)

- Coin-Operated D-Series Drying TumblersDocumento6 pagineCoin-Operated D-Series Drying TumblersGregory StewartNessuna valutazione finora

- Drill Pipe Size and Specification ChartDocumento1 paginaDrill Pipe Size and Specification ChartGregory StewartNessuna valutazione finora

- General Electric TD1495PBS1Documento6 pagineGeneral Electric TD1495PBS1Gregory StewartNessuna valutazione finora

- SB Self-Service Laundry ENG LoDocumento12 pagineSB Self-Service Laundry ENG LoGregory StewartNessuna valutazione finora

- Technical Support Documentation I N S I D E B O P V A L V E (B V R)Documento1 paginaTechnical Support Documentation I N S I D E B O P V A L V E (B V R)Gregory StewartNessuna valutazione finora

- RDCV - : Technical Instruction ManualDocumento12 pagineRDCV - : Technical Instruction ManualGregory StewartNessuna valutazione finora

- Spare parts request for washer extractor repairDocumento3 pagineSpare parts request for washer extractor repairGregory StewartNessuna valutazione finora

- BVR BOP: Technical Instruction ManualDocumento9 pagineBVR BOP: Technical Instruction ManualGregory StewartNessuna valutazione finora

- Hercules 15 Marketing BrochureDocumento8 pagineHercules 15 Marketing BrochureGregory StewartNessuna valutazione finora

- RDCVDocumento2 pagineRDCVGregory StewartNessuna valutazione finora

- H - W D P W C U D: EVI ATE Rill IPE Eight AND Enter Pset ImensionsDocumento1 paginaH - W D P W C U D: EVI ATE Rill IPE Eight AND Enter Pset ImensionsGregory StewartNessuna valutazione finora

- 8150005S PDFDocumento2 pagine8150005S PDFGregory StewartNessuna valutazione finora

- S S, B C: Tandard Izes Ores AND OnnectionsDocumento1 paginaS S, B C: Tandard Izes Ores AND OnnectionsGregory StewartNessuna valutazione finora

- X Type Safety JointDocumento1 paginaX Type Safety JointGregory StewartNessuna valutazione finora

- Tips 76 PDFDocumento20 pagineTips 76 PDFGregory StewartNessuna valutazione finora

- Heavy PDFDocumento869 pagineHeavy PDFGregory StewartNessuna valutazione finora

- Selection Information H-And J-Frame Thermal-Magnetic Molded Case 150 and 250 Ampere Frame-Class 611Documento1 paginaSelection Information H-And J-Frame Thermal-Magnetic Molded Case 150 and 250 Ampere Frame-Class 611Gregory StewartNessuna valutazione finora

- Porta EscobillaDocumento1 paginaPorta EscobillaGregory StewartNessuna valutazione finora

- Clmetal PDFDocumento35 pagineClmetal PDFGregory StewartNessuna valutazione finora

- Air PDFDocumento59 pagineAir PDFGregory StewartNessuna valutazione finora

- DDEC II and III Wiring DiagramsDocumento13 pagineDDEC II and III Wiring Diagramstwhiteman200682% (49)

- FeldSp en PDFDocumento18 pagineFeldSp en PDFGregory StewartNessuna valutazione finora

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- ICN Question Bank Unit-1, 2 and 3 (Upto GSM Identifier)Documento1 paginaICN Question Bank Unit-1, 2 and 3 (Upto GSM Identifier)Snehal PatelNessuna valutazione finora

- Present Environment and Sustainable Development - Annual Review Report 2015Documento7 paginePresent Environment and Sustainable Development - Annual Review Report 2015catalinlungeanu758Nessuna valutazione finora

- Insulation Resistance TestDocumento7 pagineInsulation Resistance Testcarlos vidalNessuna valutazione finora

- Issues in Diaphragm Forming of Continuous Fiber Reinforced Thermoplastic CompositesDocumento11 pagineIssues in Diaphragm Forming of Continuous Fiber Reinforced Thermoplastic CompositesclaradwisNessuna valutazione finora

- F3 Maths 2012 1stexam Paper1Documento3 pagineF3 Maths 2012 1stexam Paper1YiuhangLeung100% (2)

- DLTSoul DrinkersDocumento7 pagineDLTSoul DrinkersIgnacio Burón García100% (1)

- CS4000 Data SheetDocumento6 pagineCS4000 Data SheetJuan Luis EspinosaNessuna valutazione finora

- Speech and Modes of SpeechDocumento27 pagineSpeech and Modes of SpeechShaira MejaresNessuna valutazione finora

- Holt MCD Earth Science Chapter 30Documento34 pagineHolt MCD Earth Science Chapter 30ADEDAMOPE ODUESONessuna valutazione finora

- PronunciationDocumento5 paginePronunciationHưng NguyễnNessuna valutazione finora

- Nb7040 - Rules For Pipe Connections and Spools: Acc. Building Specification. Rev. 2, November 2016Documento4 pagineNb7040 - Rules For Pipe Connections and Spools: Acc. Building Specification. Rev. 2, November 201624142414Nessuna valutazione finora

- Thrust Equation For A Turbofan Double Inlet/Outlet: Joshtheengineer April 8, 2017Documento7 pagineThrust Equation For A Turbofan Double Inlet/Outlet: Joshtheengineer April 8, 2017Muhammad RidwanNessuna valutazione finora

- Detailed Scheduling Planning Board Technical HelpDocumento6 pagineDetailed Scheduling Planning Board Technical Helpmanojnarain100% (1)

- Vspa 50Documento5 pagineVspa 50elfo111Nessuna valutazione finora

- Disaster Readiness Exam SpecificationsDocumento2 pagineDisaster Readiness Exam SpecificationsRICHARD CORTEZNessuna valutazione finora

- 2016 Book IrrigationAndDrainageEngineeriDocumento747 pagine2016 Book IrrigationAndDrainageEngineeriJesús Garre Ruiz100% (2)

- Filters in GeneralDocumento3 pagineFilters in GeneralJoseGarciaRuizNessuna valutazione finora

- ChuzaChen Hydroelectric Power ProjectDocumento13 pagineChuzaChen Hydroelectric Power ProjectkanabaramitNessuna valutazione finora

- Free Study PDF Download from pebexam BlogDocumento22 pagineFree Study PDF Download from pebexam Blogk_jaiswalNessuna valutazione finora

- Frequently Asked Questions (Faq) FOR New Unifi Mobile Prepaid #BebasDocumento1 paginaFrequently Asked Questions (Faq) FOR New Unifi Mobile Prepaid #BebasNgHanSeongNessuna valutazione finora

- Implementing Product ManagementDocumento156 pagineImplementing Product ManagementJyoti MohantyNessuna valutazione finora

- Name: Keatlaretse Bridgette Surname: Macucwa Module Name: Social Work Practice Module Code: BSW 2605 Assessment No: 2 Due Date: 14 August 2020Documento6 pagineName: Keatlaretse Bridgette Surname: Macucwa Module Name: Social Work Practice Module Code: BSW 2605 Assessment No: 2 Due Date: 14 August 2020keatlaretse macucwaNessuna valutazione finora

- Jason Capital Screw Jobs PDFDocumento50 pagineJason Capital Screw Jobs PDFДжек П100% (3)

- Screen 2014 Nettleton 5 28 PDFDocumento24 pagineScreen 2014 Nettleton 5 28 PDFtaroefNessuna valutazione finora

- Western Preços - SPDocumento28 pagineWestern Preços - SPRobertaoJasperNessuna valutazione finora

- Medical WaiverDocumento1 paginaMedical WaiverCheerBUNessuna valutazione finora

- The Function of Composition and InverseDocumento20 pagineThe Function of Composition and InversenormasulasaNessuna valutazione finora

- Mansarovar Energy-Campo JazminDocumento169 pagineMansarovar Energy-Campo JazminFRANCISCO BADILLONessuna valutazione finora

- LGBT Workplace Equality Policy and Customer Satisfaction: The Roles of Marketing Capability and Demand InstabilityDocumento20 pagineLGBT Workplace Equality Policy and Customer Satisfaction: The Roles of Marketing Capability and Demand InstabilityFatima ZafarNessuna valutazione finora

- SCHEMACSC520Documento3 pagineSCHEMACSC520fazaseikoNessuna valutazione finora