Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: Features Description

Caricato da

Raul CruzTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: Features Description

Caricato da

Raul CruzCopyright:

Formati disponibili

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

D A C 0 8 0 0 / D A C 0 8 0 2 8 - B it D ig ita l - to- A n a l og C on v e r te r s

C he ck for Sa mpl e s : D A C 0 8 0 0 , D A C 0 8 0 2

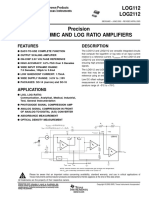

1FEA TURES D ESC RIPTION

The DAC0800 series are monolithic 8-bit high-speed

2 Fa s t Se ttl in g Output C ur r e n t: 10 0 n s

current-output digital-to-analog converters (DAC)

Ful l Sca l e Er r or : 1 LSB

featuring typical settling times of 100 ns. When used

Non l in e a r ity Ov e r Te mpe r a tur e : 0 .1%

as a multiplying DAC, monotonic performance over a

40 to 1 reference current range is possible. The

Ful l Sca l e C ur r e n t D r ift: 10 ppm/ C

DAC0800 series also features high compliance

Hig h Output C ompl ia n ce : 10 V to +18 V

complementary current outputs to allow differential

C ompl e me n ta r y C ur r e n t Outputs

output voltages of 20 Vp-p with simple resistor loads.

The reference-to-full-scale current matching of better

In te r fa ce D ir e ctl y with TTL, C MOS, PMOS a n d

than 1 LSB eliminates the need for full-scale trims in

Othe r s

most applications, while the nonlinearities of better

2 Qua dr a n t Wide Ra n g e Mul tipl yin g C a pa bil ity

than 0.1% over temperature minimizes system error

Wide Powe r Suppl y Ra n g e : 4.5V to 18 V

accumulations.

Low Powe r C on s umption : 33 mW a t 5V

The noise immune inputs will accept a variety of logic

Low C os t

levels. The performance and characteristics of the

device are essentially unchanged over the 4.5V to

18V power supply range and power consumption at

only 33 mW with 5V supplies is independent of logic

input levels.

The DAC0800, DAC0802, DAC0800C and

DAC0802C are a direct replacement for the DAC-08,

DAC-08A, DAC-08C, and DAC-08H, respectively. For

single supply operation, refer to AN-1525.

Typica l A ppl ica tion

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 1. 2 0 V

P- P

Output D ig ita l - to- A n a l og C on v e r te r

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright 19992013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

A bs ol ute Ma ximum Ra tin g s

(1)

Supply Voltage (V

+

V

) 18V or 36V

Power Dissipation

(2)

500 mW

Reference Input Differential Voltage

(V14 to V15) V

to V

+

Reference Input Common-Mode

Range (V14, V15) V

to V

+

Reference Input Current 5 mA

Logic Inputs V

to V

plus 36V

Analog Current Outputs

(V

S

= 15V) 4.25 mA

ESD Susceptibility

(3)

TBD V

Storage Temperature 65C to +150C

Lead Temp. (Soldering, 10 seconds)

PDIP Package (plastic) 260C

CDIP Package (ceramic) 300C

Surface Mount Package

Vapor Phase (60 seconds) 215C

Infrared (15 seconds) 220C

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not

apply when operating the device beyond its specified operating conditions.

(2) The maximum junction temperature of the DAC0800 and DAC0802 is 125C. For operating at elevated temperatures, devices in the

CDIP package must be derated based on a thermal resistance of 100C/W, junction-to-ambient, 175C/W for the molded PDIP package

and 100C/W for the SOIC package.

(3) Human body model, 100 pF discharged through a 1.5 k resistor.

Ope r a tin g C on dition s

(1)

Min Ma x Un its

Temperature (T

A

)

DAC0800L 55 +125 C

DAC0800LC 0 +70 C

DAC0802LC 0 +70 C

V

+

(V

) + 10 (V

) + 30 V

V 15 5 V

I

REF

(V

= 5V) 1 2 mA

I

REF

(V

= 15V) 1 4 mA

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not

apply when operating the device beyond its specified operating conditions.

2 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

El e ctr ica l C ha r a cte r is tics

The following specifications apply for V

S

= 15V, I

REF

= 2 mA and T

MIN

T

A

T

MAX

unless otherwise specified. Output

characteristics refer to both I

OUT

and I

OUT

.

D A C 0 8 0 0 L/

D A C 0 8 0 2 LC

D A C 0 8 0 0 LC

Pa r a me te r Te s t C on dition s Un its

Min Typ Ma x Min Typ Ma x

Resolution 8 8 8 8 8 8 Bits

Monotonicity 8 8 8 8 8 8 Bits

Nonlinearity 0.1 0.19 %FS

To LSB, All Bits Switched ON

100 135 ns

or OFF, T

A

=25C

t

s

Settling Time

DAC0800L 100 135 ns

DAC0800LC 100 150 ns

t

PLH

, Propagation Delay T

A

=25C

t

PHL

Each Bit 35 60 35 60 ns

All Bits Switched 35 60 35 60 ns

TCI

FS

Full Scale Tempco 10 50 10 50 ppm/C

Full Scale Current Change <

V

OC

Output Voltage Compliance 10 18 10 18 V

LSB, R

OUT

>20 M, Typical

V

REF

= 10.000V,

I

FS4

Full Scale Current R14 = R15 = 5.000 k, 1.984 1.992 2.00 1.94 1.99 2.04 mA

T

A

=25C

I

FSS

Full Scale Symmetry I

FS4

I

FS2

0.5 4.0 1 8.0 A

I

ZS

Zero Scale Current 0.1 1.0 0.2 2.0 A

V

= 5V 0 2.0 2.1 0 2.0 2.1

I

FSR

Output Current Range mA

V

= 8V to 18V 0 2.0 4.2 0 2.0 4.2

Logic Input Levels V

LC

= 0V

V

IL

Logic 0 0.8 0.8 V

V

IH

Logic 1 2.0 2.0 V

Logic Input Current V

LC

= 0V

I

IL

Logic 0 10V V

IN

+0.8V 2.0 10 2.0 10 A

I

IH

Logic 1 2V V

IN

+18V 0.002 10 0.002 10 A

V

IS

Logic Input Swing V

= 15V 10 18 10 18 V

V

THR

Logic Threshold Range V

S

= 15V 10 13.5 10 13.5 V

I

15

Reference Bias Current 1.0 3.0 1.0 3.0 A

dl/dt Reference Input Slew Rate (Figure 26) 4.0 8.0 4.0 8.0 mA/s

Positive Power Supply

PSSI

FS+

4.5V V

+

18V 0.0001 0.01 0.0001 0.01 %/%

Sensitivity

Negative Power Supply

PSSI

FS

4.5V V

18V, I

REF

= 1mA 0.0001 0.01 0.0001 0.01 %/%

Sensitivity

I+ 2.3 3.8 2.3 3.8 mA

Power Supply Current V

S

= 5V, I

REF

= 1 mA

I 4.3 5.8 4.3 5.8 mA

I+ 2.4 3.8 2.4 3.8 mA

Power Supply Current V

S

= +5V, 15V, I

REF

= 2 mA

I 6.4 7.8 6.4 7.8 mA

I+ 2.5 3.8 2.5 3.8 mA

Power Supply Current V

S

= 15V, I

REF

= 2 mA

I 6.5 7.8 6.5 7.8 mA

5V, I

REF

= 1 mA 33 48 33 48 mW

P

D

Power Consumption +5V, 15V, I

REF

= 2 mA 108 136 108 136 mW

15V, I

REF

= 2 mA 135 174 135 174 mW

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

C on n e ction D ia g r a ms

Fig ur e 2 . PD IP, C D IP Pa cka g e s - Top Vie w Fig ur e 3. SOIC Pa cka g e - Top Vie w

(Se e Pa cka g e Numbe r NFG0 0 16E or NFE0 0 16A ) (Se e Pa cka g e Numbe r D 0 0 16A )

B l ock D ia g r a m

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 4.

4 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

Typica l Pe r for ma n ce C ha r a cte r is tics

Ful l Sca l e C ur r e n t LSB Pr opa g a tion D e l a y

v s . v s .

Re fe r e n ce C ur r e n t I

FS

Fig ur e 5. Fig ur e 6.

Re fe r e n ce In put Re fe r e n ce A mp

Fr e que n cy Re s pon s e C ommon - Mode Ra n g e

C ur v e 1: C

C

=15 pF, V

IN

=2 Vp-p centered at 1V.

Note. Positive common-mode range is always (V+) 1.5V.

C ur v e 2 : C

C

=15 pF, V

IN

=50 mVp-p centered at 200 mV.

C ur v e 3: C

C

=0 pF, V

IN

=100 mVp-p centered at 0V and applied

through 50 connected to pin 14.2V applied to R14.

Fig ur e 7. Fig ur e 8 .

V

TH

V

LC

Log ic In put C ur r e n t v s . v s .

In put Vol ta g e Te mpe r a tur e

Fig ur e 9. Fig ur e 10 .

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

Typica l Pe r for ma n ce C ha r a cte r is tics (con tin ue d)

Output C ur r e n t

v s .

Output

Vol ta g e (Output Vol ta g e Output Vol ta g e C ompl ia n ce v s .

C ompl ia n ce ) Te mpe r a tur e

Fig ur e 11. Fig ur e 12 .

B it Tr a n s fe r Powe r Suppl y C ur r e n t

C ha r a cte r is tics v s . +V

Note. B1B8 have identical transfer characteristics. Bits are fully

switched with less than LSB error, at less than 100 mV from actual

threshold. These switching points are guaranteed to lie between 0.8

and 2V over the operating temperature range (V

LC

= 0V).

Fig ur e 13. Fig ur e 14.

Powe r Suppl y C ur r e n t Powe r Suppl y C ur r e n t

v s . V v s . Te mpe r a tur e

Fig ur e 15. Fig ur e 16.

6 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

EQUIVA LENT C IRC UIT

Fig ur e 17. Equiv a l e n t C ir cuit

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

TYPIC A L A PPLIC A TIONS

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

I

O

+ I

O

= I

FS

for all logic states

For fixed reference, TTL operation, typical values are:

V

REF

= 10.000V

R

REF

= 5.000k

R15 R

REF

C

C

= 0.01 F

V

LC

= 0V (Ground)

Fig ur e 18 . B a s ic Pos itiv e Re fe r e n ce Ope r a tion

Fig ur e 19. Re comme n de d Ful l Sca l e A djus tme n t Fig ur e 2 0 . B a s ic Ne g a tiv e Re fe r e n ce Ope r a tion

C ir cuit

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

8 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 2 1. B a s ic Un ipol a r Ne g a tiv e Ope r a tion

Ta bl e 1. B a s ic Un ipol a r Ne g a tiv e Ope r a tion

B 1 B 2 B 3 B 4 B 5 B 6 B 7 B 8 I

O

mA I

O

mA E

O

E

O

Full Scale 1 1 1 1 1 1 1 1 1.992 0.000 9.960 0.000

Full ScaleLSB 1 1 1 1 1 1 1 0 1.984 0.008 9.920 0.040

Half Scale+LSB 1 0 0 0 0 0 0 1 1.008 0.984 5.040 4.920

Half Scale 1 0 0 0 0 0 0 0 1.000 0.992 5.000 4.960

Half ScaleLSB 0 1 1 1 1 1 1 1 0.992 1.000 4.960 5.000

Zero Scale+LSB 0 0 0 0 0 0 0 1 0.008 1.984 0.040 9.920

Zero Scale 0 0 0 0 0 0 0 0 0.000 1.992 0.000 9.960

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 2 2 . B a s ic B ipol a r Output Ope r a tion

Ta bl e 2 . B a s ic B ipol a r Output Ope r a tion

B 1 B 2 B 3 B 4 B 5 B 6 B 7 B 8 E

O

E

O

Pos. Full Scale 1 1 1 1 1 1 1 1 9.920 +10.000

Pos. Full ScaleLSB 1 1 1 1 1 1 1 0 9.840 +9.920

Zero Scale+LSB 1 0 0 0 0 0 0 1 0.080 +0.160

Zero Scale 1 0 0 0 0 0 0 0 0.000 +0.080

Zero ScaleLSB 0 1 1 1 1 1 1 1 +0.080 0.000

Neg. Full Scale+LSB 0 0 0 0 0 0 0 1 +9.920 9.840

Neg. Full Scale 0 0 0 0 0 0 0 0 +10.000 9.920

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

(1) Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

(2) If R

L

= R

L

within 0.05%, output is symmetrical about ground.

Fig ur e 2 3. Symme tr ica l Offs e t B in a r y Ope r a tion

Ta bl e 3. Symme tr ica l Offs e t B in a r y Ope r a tion

B 1 B 2 B 3 B 4 B 5 B 6 B 7 B 8 E

O

Pos. Full Scale 1 1 1 1 1 1 1 1 +9.960

Pos. Full ScaleLSB 1 1 1 1 1 1 1 0 +9.880

(+)Zero Scale 1 0 0 0 0 0 0 0 +0.040

()Zero Scale 0 1 1 1 1 1 1 1 0.040

Neg. Full Scale+LSB 0 0 0 0 0 0 0 1 9.880

Neg. Full Scale 0 0 0 0 0 0 0 0 9.960

(1) Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

(2) For complementary output (operation as negative logic DAC), connect inverting input of op amp to I

O

(pin 2), connect

I

O

(pin 4) to ground.

Fig ur e 2 4. Pos itiv e Low Impe da n ce Output Ope r a tion

(1) Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

(2) For complementary output (operation as a negative logic DAC) connect non-inverting input of op am to I

O

(pin 2);

connect I

O

(pin 4) to ground.

Fig ur e 2 5. Ne g a tiv e Low Impe da n ce Output Ope r a tion

10 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

Typical values: R

IN

=5k,+V

IN

=10V

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 2 6. Pul s e d Re fe r e n ce Ope r a tion

V

TH

= V

LC

+ 1.4V

15V CMOS, HTL, HNIL

V

TH

= 7.6V

Note. Do not exceed negative logic input range of DAC.

Fig ur e 2 7. In te r fa cin g with Va r ious Log ic Fa mil ie s

(a ) I

REF

pe a k n e g a tiv e s win g of I

IN

(b) +V

REF

mus t be a bov e pe a k pos itiv e s win g of V

IN

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 2 8 . A ccommoda tin g B ipol a r Re fe r e n ce s

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

SNAS538CJUNE 1999REVISED FEBRUARY 2013 www.ti.com

Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 2 9. Se ttl in g Time Me a s ur e me n t

(1) For 1 s conversion time with 8-bit resolution and 7-bit accuracy, an LM361 comparator replaces the LM319 and the

reference current is doubled by reducing R1, R2 and R3 to 2.5 k and R4 to 2 M.

(2) Pin numbers represent the PDIP package. The SOIC package pin numbers differ from that of the PDIP package.

Fig ur e 30 . A C ompl e te 2 s C on v e r s ion Time , 8 - B it A / D C on v e r te r

12 Submit Documentation Feedback Copyright 19992013, Texas Instruments Incorporated

Product Folder Links: DAC0800 DAC0802

D A C 0 8 0 0 , D A C 0 8 0 2

www.ti.com SNAS538C JUNE 1999REVISED FEBRUARY 2013

REVISION HISTORY

C ha n g e s fr om Re v is ion B (Fe br ua r y 2 0 13) to Re v is ion C Pa g e

Changed layout of National Data Sheet to TI format .......................................................................................................... 12

Copyright 19992013, Texas Instruments Incorporated Submit Documentation Feedback 13

Product Folder Links: DAC0800 DAC0802

PACKAGE OPTION ADDENDUM

www.ti.com 11-Apr-2013

Addendum-Page 1

PACKAGING INFORMATION

Orderable Device Status

(1)

Package Type Package

Drawing

Pins Package

Qty

Eco Plan

(2)

Lead/Ball Finish MSL Peak Temp

(3)

Op Temp (C) Top-Side Markings

(4)

Samples

DAC-08EP ACTIVE PDIP NFG 16 25 TBD Call TI Call TI 0 to 70 DAC0800LCN

DAC-08EP

DAC0800LCM ACTIVE SOIC D 16 48 TBD Call TI Call TI 0 to 70 DAC0800LCM

DAC0800LCM/NOPB ACTIVE SOIC D 16 48 Green (RoHS

& no Sb/Br)

CU SN Level-1-260C-UNLIM 0 to 70 DAC0800LCM

DAC0800LCMX ACTIVE SOIC D 16 2500 TBD Call TI Call TI 0 to 70 DAC0800LCM

DAC0800LCMX/NOPB ACTIVE SOIC D 16 2500 Green (RoHS

& no Sb/Br)

CU SN Level-1-260C-UNLIM 0 to 70 DAC0800LCM

DAC0800LCN ACTIVE PDIP NFG 16 25 TBD Call TI Call TI 0 to 70 DAC0800LCN

DAC-08EP

DAC0800LCN/NOPB ACTIVE PDIP NFG 16 25 Pb-Free

(RoHS)

SN Level-1-NA-UNLIM 0 to 70 DAC0800LCN

DAC-08EP

DAC0802LCMX ACTIVE SOIC D 16 2500 TBD Call TI Call TI 0 to 70 DAC0802LCM

DAC0802LCMX/NOPB ACTIVE SOIC D 16 2500 Green (RoHS

& no Sb/Br)

CU SN Level-1-260C-UNLIM 0 to 70 DAC0802LCM

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability

information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that

lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight

in homogeneous material)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

PACKAGE OPTION ADDENDUM

www.ti.com 11-Apr-2013

Addendum-Page 2

(4)

Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a

continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information

provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.

TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TAPE AND REEL INFORMATION

*All dimensions are nominal

Device Package

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0

(mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

(mm)

Pin1

Quadrant

DAC0800LCMX SOIC D 16 2500 330.0 16.4 6.5 10.3 2.3 8.0 16.0 Q1

DAC0800LCMX/NOPB SOIC D 16 2500 330.0 16.4 6.5 10.3 2.3 8.0 16.0 Q1

DAC0802LCMX SOIC D 16 2500 330.0 16.4 6.5 10.3 2.3 8.0 16.0 Q1

DAC0802LCMX/NOPB SOIC D 16 2500 330.0 16.4 6.5 10.3 2.3 8.0 16.0 Q1

PACKAGE MATERIALS INFORMATION

www.ti.com 26-Mar-2013

Pack Materials-Page 1

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

DAC0800LCMX SOIC D 16 2500 367.0 367.0 35.0

DAC0800LCMX/NOPB SOIC D 16 2500 367.0 367.0 35.0

DAC0802LCMX SOIC D 16 2500 367.0 367.0 35.0

DAC0802LCMX/NOPB SOIC D 16 2500 367.0 367.0 35.0

PACKAGE MATERIALS INFORMATION

www.ti.com 26-Mar-2013

Pack Materials-Page 2

MECHANICAL DATA

N0016E

www.ti.com

N16E (Rev G)

NFG0016E

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other

changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest

issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All semiconductor products (also referred to herein as components) are sold subject to TIs terms and conditions of sale

supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TIs terms

and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary

to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily

performed.

TI assumes no liability for applications assistance or the design of Buyers products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers products and applications, Buyers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information

published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration

and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered

documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service

voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice.

TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which

anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause

harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use

of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TIs goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or enhanced plastic are designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components

which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and

regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive

Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications

Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers

DLP Products www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP dsp.ti.com Energy and Lighting www.ti.com/energy

Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright 2013, Texas Instruments Incorporated

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

Potrebbero piacerti anche

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDocumento0 pagineDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionMiguel Angel García ValerioNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- DAC0808 DatasheetDocumento12 pagineDAC0808 DatasheetRicky CoxNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocumento4 pagineCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiNessuna valutazione finora

- LM 78 L 05Documento21 pagineLM 78 L 05peyuco3333Nessuna valutazione finora

- Features Applications: X+ X - Y+ YDocumento35 pagineFeatures Applications: X+ X - Y+ YAlvaro ChaconNessuna valutazione finora

- OpAmp - MCP6244Documento38 pagineOpAmp - MCP6244Ludwig SchmidtNessuna valutazione finora

- Dac0800 PDFDocumento9 pagineDac0800 PDFCarbon Nano TubeNessuna valutazione finora

- +3 Volt, Serial Input Complete 12-Bit DAC AD8300Documento8 pagine+3 Volt, Serial Input Complete 12-Bit DAC AD8300jnax101Nessuna valutazione finora

- LM 723Documento22 pagineLM 723Zoran DjukicNessuna valutazione finora

- DAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A ConvertersDocumento24 pagineDAC0830/DAC0832 8-Bit P Compatible, Double-Buffered D To A Convertersbhuvi2312Nessuna valutazione finora

- MCP 3201Documento28 pagineMCP 3201Nacer MezghicheNessuna valutazione finora

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDocumento11 pagineDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionFernando FortunaNessuna valutazione finora

- MF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionDocumento35 pagineMF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionAlbeiro Yr TrancerNessuna valutazione finora

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocumento15 pagineDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AYasser Mauricio Flores RamonNessuna valutazione finora

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocumento20 pagineADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982Nessuna valutazione finora

- Data SheetDocumento35 pagineData SheetvvvssssvvvNessuna valutazione finora

- LM3916 Dot/Bar Display Driver: Features DescriptionDocumento31 pagineLM3916 Dot/Bar Display Driver: Features DescriptionIngeniero Mecánico AgrícolaNessuna valutazione finora

- ST 232Documento11 pagineST 232Negru P. PlantatieNessuna valutazione finora

- XTR 117Documento16 pagineXTR 117Compañero DanielqjNessuna valutazione finora

- Distributed byDocumento42 pagineDistributed bydennyjoelNessuna valutazione finora

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDocumento42 pagine2.5V To 6.0V Micropower CMOS Op Amp: Featuresinside121Nessuna valutazione finora

- 2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceDocumento34 pagine2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceManjunatha Ac100% (1)

- Ad 421Documento14 pagineAd 421Vishal Devrao JadhavNessuna valutazione finora

- Dac 0800Documento16 pagineDac 0800Ali A-cNessuna valutazione finora

- LMC 567Documento14 pagineLMC 567saandoNessuna valutazione finora

- TLC 5925Documento27 pagineTLC 5925zektorNessuna valutazione finora

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocumento30 pagineBias Power Supply For TV and Monitor TFT LCD Panels: Featureseduinggv1829Nessuna valutazione finora

- ST3232 Data SheetDocumento12 pagineST3232 Data SheetcredioNessuna valutazione finora

- lm331 PDFDocumento21 paginelm331 PDFOsvaldo Dominguez GonzalezNessuna valutazione finora

- DAC800Documento14 pagineDAC800JaimeAugustoPrietoNessuna valutazione finora

- MAX31865 RTD-to-Digital Converter: General Description FeaturesDocumento25 pagineMAX31865 RTD-to-Digital Converter: General Description FeaturespaKoSTe1Nessuna valutazione finora

- DAC1020Documento14 pagineDAC1020micochangoNessuna valutazione finora

- ADC0804 DatasheetDocumento48 pagineADC0804 DatasheetSaurabh AnmadwarNessuna valutazione finora

- LM741 Operational Amplifier: Features DescriptionDocumento11 pagineLM741 Operational Amplifier: Features Descriptiondariohot21Nessuna valutazione finora

- Transformer Driver For Isolated Power Supplies: Features ApplicationsDocumento29 pagineTransformer Driver For Isolated Power Supplies: Features Applicationsngongpro27Nessuna valutazione finora

- HS-2420RH - Fast Sample and HolDocumento8 pagineHS-2420RH - Fast Sample and HolDeepa DevarajNessuna valutazione finora

- Tda 7250Documento11 pagineTda 7250tica007Nessuna valutazione finora

- Ca3130, Ca3130aDocumento17 pagineCa3130, Ca3130aproctepNessuna valutazione finora

- DAC08Documento20 pagineDAC08Severiano Jaramillo QuintanarNessuna valutazione finora

- 300/600ma, Ultra-Fast Transient Response LDO Regulator: General Description FeaturesDocumento15 pagine300/600ma, Ultra-Fast Transient Response LDO Regulator: General Description FeaturesDouglas RodriguesNessuna valutazione finora

- Adc 0809Documento12 pagineAdc 0809Carbon Nano TubeNessuna valutazione finora

- 1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesDocumento12 pagine1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesStefan GlaserNessuna valutazione finora

- Differential/Cascode Amplifier For Commercial and Industrial Equipment From DC To 120Mhz FeaturesDocumento10 pagineDifferential/Cascode Amplifier For Commercial and Industrial Equipment From DC To 120Mhz FeaturessunantoNessuna valutazione finora

- 2N6027Documento6 pagine2N6027Due Ambi SecchiNessuna valutazione finora

- Discontinued Product: Ratiometric Linear Hall Effect Sensor Ics For High-Temperature OperationDocumento13 pagineDiscontinued Product: Ratiometric Linear Hall Effect Sensor Ics For High-Temperature OperationceferrruNessuna valutazione finora

- ADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDocumento33 pagineADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsRoy Muy GolfoNessuna valutazione finora

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocumento16 pagineμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNessuna valutazione finora

- DG201A, DG202: Quad SPST, CMOS Analog Switches FeaturesDocumento7 pagineDG201A, DG202: Quad SPST, CMOS Analog Switches FeaturesFilozófus ÖnjelöltNessuna valutazione finora

- Ina 168Documento15 pagineIna 168Ernane FreitasNessuna valutazione finora

- LMD18200 3A, 55V H-Bridge: Features ApplicationsDocumento19 pagineLMD18200 3A, 55V H-Bridge: Features ApplicationsLe NhanNessuna valutazione finora

- IC-ON-LINE - CN dm0465r 44841Documento20 pagineIC-ON-LINE - CN dm0465r 44841ubhagavanNessuna valutazione finora

- Adc 0808Documento14 pagineAdc 0808Vikas PatelNessuna valutazione finora

- Features: Single Bilateral SwitchDocumento15 pagineFeatures: Single Bilateral SwitchGaryTechNessuna valutazione finora

- 6th Central Pay Commission Salary CalculatorDocumento15 pagine6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Generative Drafting PDFDocumento469 pagineGenerative Drafting PDFRaul CruzNessuna valutazione finora

- L293DDocumento7 pagineL293Dapi-370080950% (2)

- Interactive Drafting PDFDocumento748 pagineInteractive Drafting PDFRaul CruzNessuna valutazione finora

- Data 3863 CR Motores PDFDocumento2 pagineData 3863 CR Motores PDFRaul CruzNessuna valutazione finora

- PID Tutorial PDFDocumento7 paginePID Tutorial PDFMarlon Isaac CortesNessuna valutazione finora

- PID Tutorial PDFDocumento7 paginePID Tutorial PDFMarlon Isaac CortesNessuna valutazione finora

- Radius: Remote Authentication Dial in User Service (RADIUS) Is A NetworkingDocumento6 pagineRadius: Remote Authentication Dial in User Service (RADIUS) Is A NetworkingVandana SharmaNessuna valutazione finora

- Ethical Hacking PPT Download4575Documento21 pagineEthical Hacking PPT Download4575Anil Kumar50% (2)

- Lower Case To Upper Case MICDocumento12 pagineLower Case To Upper Case MICAvadhut DeshmukhNessuna valutazione finora

- 1 2 3 4 Bro Smart TC Eng PDFDocumento4 pagine1 2 3 4 Bro Smart TC Eng PDFnguyenNessuna valutazione finora

- tc200 Installation Guide PDFDocumento8 paginetc200 Installation Guide PDFSK Salud - AsistenteNessuna valutazione finora

- BIM Research Contribution and ChallengesDocumento22 pagineBIM Research Contribution and ChallengesDivyesh ParmarNessuna valutazione finora

- Castro Franklin ResumeDocumento2 pagineCastro Franklin ResumeFrank CastroNessuna valutazione finora

- En - Synergis Cloud Link Hardware Installation Guide 3.0Documento140 pagineEn - Synergis Cloud Link Hardware Installation Guide 3.0Edison DiazNessuna valutazione finora

- Modelling of Interference Caused by Uplink Signal For Low Earth Orbiting Satellite Ground StationsDocumento5 pagineModelling of Interference Caused by Uplink Signal For Low Earth Orbiting Satellite Ground StationsMurthyNessuna valutazione finora

- Experiment No. 1 - To Study PLC Trainer Kit PDFDocumento8 pagineExperiment No. 1 - To Study PLC Trainer Kit PDFShashikant PrasadNessuna valutazione finora

- Introduction To Digital TransformationDocumento8 pagineIntroduction To Digital TransformationvrjgopiNessuna valutazione finora

- Land Rover Workshop Manuals L322 Range Rover System Description and Operation AUTOMATIC TRANSMISDocumento1 paginaLand Rover Workshop Manuals L322 Range Rover System Description and Operation AUTOMATIC TRANSMISMark ErskineNessuna valutazione finora

- Fast Fourier Transform of Frequency Hopping Spread Spectrum in Noisy EnvironmentDocumento5 pagineFast Fourier Transform of Frequency Hopping Spread Spectrum in Noisy EnvironmentNaveed RamzanNessuna valutazione finora

- How To Configure SAP Purchase Order Release StrategyDocumento12 pagineHow To Configure SAP Purchase Order Release Strategyphogat projectNessuna valutazione finora

- Excel Budget TemplateDocumento5 pagineExcel Budget TemplateChiranjib BanerjeeNessuna valutazione finora

- ODL and OpenStack - Workshop - 0Documento38 pagineODL and OpenStack - Workshop - 0palimariumNessuna valutazione finora

- MySQL TutorialDocumento16 pagineMySQL TutorialNiranjanNessuna valutazione finora

- The 10 Principles at Nike.Documento1 paginaThe 10 Principles at Nike.Olaoluwa SamagbeyiNessuna valutazione finora

- Back-Propagation Artificial Neural Network Approach For Machining Centre SelectionDocumento18 pagineBack-Propagation Artificial Neural Network Approach For Machining Centre SelectionNatarajan KrishnanNessuna valutazione finora

- Mingw w64 Howto BuildDocumento7 pagineMingw w64 Howto Builddsdadsd sadsadNessuna valutazione finora

- EtpPrD0ATC-1000 Quick Start GuideDocumento1 paginaEtpPrD0ATC-1000 Quick Start Guidedung110baclieuNessuna valutazione finora

- Versatech Recloser ManualDocumento40 pagineVersatech Recloser ManualmiveyNessuna valutazione finora

- III. Pinoy Robot GamesDocumento8 pagineIII. Pinoy Robot GamesOrtigas Aileen GraceNessuna valutazione finora

- LOG112Documento21 pagineLOG112Otto Lambertus0% (1)

- Single Data Sheet Linear Luminaire With LED GRP - 6402-4128-6100-152-1110-11-8500 - 267040 - en-GBDocumento6 pagineSingle Data Sheet Linear Luminaire With LED GRP - 6402-4128-6100-152-1110-11-8500 - 267040 - en-GBAlla Naveen KumarNessuna valutazione finora

- Resume ...Documento2 pagineResume ...DharmaNessuna valutazione finora

- Wheeled Loader L958FDocumento3 pagineWheeled Loader L958FWidiMufantoNessuna valutazione finora

- Curriculum Vitae: I. Personal DataDocumento2 pagineCurriculum Vitae: I. Personal DataHendrik V SihombingNessuna valutazione finora

- Short Sums Related To Time StudyDocumento2 pagineShort Sums Related To Time StudyBKC EnterpriseNessuna valutazione finora

- Net View - Net Session - Net File - Net Use - Windows CMD - SS64Documento2 pagineNet View - Net Session - Net File - Net Use - Windows CMD - SS64xavierfelix07Nessuna valutazione finora