Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Logic Design-Lab Manual

Caricato da

RamaWardhanaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Logic Design-Lab Manual

Caricato da

RamaWardhanaCopyright:

Formati disponibili

EXPERIMENT - 1

1. Given any 4-variable logic expression , simply using entered variable Map and realize

the simplied logic expression using 8:1 multiplexer IC.

COMPONENTS REQUIRED:

IC 74151, trainer kit, power chords, patch chords.

THEORY:

Multiplexer (MUX) is a combination circuit with 2

n

inputs, n number of selection lines and only

one output . MUX is generally represented as 2

n

:n:1. MUX is also known as data selector. 8:1

MUX has 8 inputs , 3 selection lines and 1 output.

Entered Variable Map (EVM) or Map Entered Variable (MEV) is a technique which makes

possible to use smaller maps to handle large number of variables. In MEV map, the cells are

allowed to contain single variable or expression along with minterm or maxterm or dont care

term. Rules for entering values in a MEV K-map is as shown below:

Appendix

Lab Manual

Part - A

Logic Design-Lab Manual.indd 1 8/17/2012 12:34:03 PM

2 Logic Design

RULE NO. MEV FUNCTION ENTRY IN MEV MAP

1 0

1

0

0

0

2 0

1

1

1

1

3 0

1

0

1

MEV

4 0

1

1

0

MEV

5 0

1

x

x

x

6 0

1

x

0

0

7 0

1

0

x

0

8 0

1

x

1

1

9 0

1

1

x

1

DESIGN:

[4- Variable logic expression will be given by examiner].

Let us assume that following expression is given in exam and let us design an 8:1 MUX based

on given expression.

f (A,B,C,D) = m (2,4,5,12,15) + d(0, 1, 10,11).

First write the truth table for the given expression:

METHOD 1:

f (A,B,C,D) = m (2,4,5,12,15) + d(0,1,10,11).

A B C D f MEV ENTRY

0

0

0

0

0

0

0

1

x

x

x = D

0

0

0

0

0

1

1

0

1

1

0

D

= MEV= D

1

0

0

1

1

0

0

0

1

1

1

1 = D

2

0

0

1

1

1

1

0

0

0

0

0 = D

3

Logic Design-Lab Manual.indd 2 8/17/2012 12:34:21 PM

LD Lab Manual 3

1

1

0

0

0

0

0

1

0

0

0 = D

4

1

1

0

0

1

1

0

1

x

x

x = D

5

1

1

1

1

0

0

0

1

1

0

D

= MEV= D

6

1

1

1

1

1

1

0

1

0

1

D= MEV= D

7

PIN DIAGRAM:

1 16

15

14

13

12

11

10

9

2

3

4

5

6

7

8

+V

CC

D

4

D

5

D

6

D

7

C

B

A

SELECTION

LINES

INPUTS

D

3

D

2

D

1

D

0

OUTPUT=Y

W

STROBE

GND

INPUTS

7

4

1

5

1

CIRCUIT DIAGRAM: [FOR METHOD 1].

STROBE

W

OUTPUT=Y

+5V

+5V

D

2

D

1

D

0

D

3

D

7404

7404

1

4 3

2

1

2

3

4

5

6

7

8

D

6

D

5

D

4

D

7

+V

CC

C

B

A

D

16

15

14

13

12

11

10

9

7

4

1

5

1

+5V

METHOD 2:

Any given Boolean expression / logic expression can also be simplied using implementation

table method and then realized using 8:1 MUX.

Logic Design-Lab Manual.indd 3 8/17/2012 12:34:21 PM

4 Logic Design

Let us consider following expression and design a circuit using implementation table

method.

f (A,B,C,D) = m(2,3,4,5,13,15) + d(8,9,10,11).

Implementation table is:

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

A

0 1 2 3 4 5 6 7

A 8

10

11

12 13 14 15

0 0

1=+V

CC

=+5V

1 A

1 0 A

Rules to obtain implementation table:

Eg :1

D

0

A

0

A 1

0

If both A

and A are not marked (ie. circled ), then the output of D

0

=0.

Eg:2

D

1

A

1

A 9

1

If both A

and A are marked then the output of D

1

=1.

Eg:3

D

2

A

2

A 10

A

If 2 is marked and 10 is not circled , then take the value of that row which is circled. In this

example, 2 is circled consider its corresponding row =A

as value of D

2

.D

2

= A

.

Logic Design-Lab Manual.indd 4 8/17/2012 12:34:21 PM

LD Lab Manual 5

Eg.4

D

3

A

3

A 11

A

11 is marked and 3 is not marked . Hence take 11s value = A . D

3

=A.

CIRCUIT : [Method 2].

STROBE

W

Y=OUTPUT

+5V

D

2

D

0

D

1

D

3

1

1 2 2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

7

4

1

5

1

+V

CC

= +5V

7404 D

4

D

5

D

6

+5V

D

C

B

A

PROCEDURE:

[For method 1]

1) The given 4-variable logic expression is f (A,B,C,D) = m (2,4,5,12,15) + d(0,

1,10,11).

2) Write the truth table for the given minterms and make MEV entry in the truth table.

3) Make the circuit connections as shown in truth table and obtain the circuit.

4) After making the connections , give the inputs according to the truth table and verify the

output.

RESULT:

The given 4- variable logic expression is simplied using MEV method and thus realized using

8:1 MUX IC.

EXPERIMENT-2

Realize a full adder using 3 - to - 8 decoder IC and 4 input NAND gates.

Logic Design-Lab Manual.indd 5 8/17/2012 12:34:21 PM

6 Logic Design

COMPONENTS REQUIRED:

IC 74138(3 -to- 8 DECODER IC) , IC 7420 (NAND gate), digital trainer kit, patch chords, power

chords.

THEORY:

FULL ADDER is a combinational circuit that performs addition of 3 bits and produces two

outputs: SUM and CARRY.

DECODER is a logic circuit with few inputs and many outputs. 3:8 DECODER is a decoder

with 3 inputs and 8 outputs. The inputs in 3:8 DEC are the control bits ABC.

DESIGN :

INPUT OUTPUT

A B C SUM CARRY

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

SUM = m (1,2,4,7)

CARRY = m (3,5,6,7)

K-map for sum is:

00 01 11 10

0

0

1

1 3

1

2

1

1

4 5

1

7 6

BC

A

Sum = A

C + A

B C

+ A B

C

+ ABC

= A

(B

C + B C

) + A (B

C

+ BC)

Let B

C + B C

= X

WKT B

C + B C

= B C = X

Also, B

C

+ B C = B C= X

= A

X + A X

Logic Design-Lab Manual.indd 6 8/17/2012 12:34:21 PM

LD Lab Manual 7

= A X

Substitute for X = B C = A B C.

K-map for carry is :

00 01 11 10

0

0

1

1

3

1

2

1

4

1

5

1

7

1

6

BC

A

Carry = AB + BC + CA.

PIN DIAGRAM:

1

2

3

4

5

6

8

16

15

14

13

12

11

10

9

7

7

4

1

3

8

A

0

A

1

A

2

E

1

E

2

E

3

GND

+V

CC

INPUT

ENABLE

PINS

O

0

O

1

O

2

O

3

O

4

O

5

O

6

O

7

OUTPUTS

1

2

3

4

5

6

7

14

13

12

11

10

9

8

7

4

2

0

+V

CC

NOT

CONNECTED

NOT

CONNECTED

GND

Logic Design-Lab Manual.indd 7 8/17/2012 12:34:22 PM

8 Logic Design

CIRCUIT DIAGRAM:

A

B

C 3

4

5

6

8

2

1 15

14

13

12

11

10

16

9

7

+5V

GND

8

6

CARRY

SUM

7420

7420

1

2

4

5

9

10

12

13

+5V

7

4

1

3

8

O

0

O

4

O

1

O

5

O

2

O

6

O

3

O

7

E

1

E

2

E

3

PROCEDURE:

1) Write the truth table for full adder.

2) Pin 8 and pin 16 of IC 74138 are connected to ground and + Vcc respectively. In order

to enable 3:8DEC IC , connect the active - low enable pins E

1

and E

2

to ground and active - high

enable pin E

3

to + 5V.

3) Connect pin numbers: 14,13,11,7 of IC 74138 to pin numbers 1,2,4,5 of IC 7420 to find

SUM at pin 6 of IC 7420. Connect pin numbers: 12,10,9,7 of IC 74138 to pin numbers : 9,10,12,13

of IC 7420 to find CARRY at pin 8 of IC 7420.

4) The output SUM is found at pin 6 of IC 7420 and output CARRY is found at pin 8 of IC

7420.

Change the inputs according to truth table and find SUM and CARRY.

RESULT:

Full - adder is verified using 3:8 DEC and 4- input NAND gate ICs.

EXPERIMENT - 3

Realize a J-K Master / Slave flip-flop using NAND gates and verify its working.

COMPONENTS REQUIRED:

IC 7410 (3 input NAND gate), IC 7400 (2 input NAND gate), digital IC trainer kit, patch chords

, power chords.

THEORY:

A flip-flop is a sequential circuit whose output will be set irrespective of varying input changes. A

Logic Design-Lab Manual.indd 8 8/17/2012 12:34:22 PM

LD Lab Manual 9

flip-flop can store a 0 or a 1 indefinitely. While S=R=1 is can undesirable input condition in a SR

flip-flop, J = K = 1 is a valid input in a JK flip-flop. The condition J = K =1 in JK flip-flop is called

as race around condition and this condition can be eliminated using master - slave JK flip-flop.

Information is entered into the master on one edge or level of a control signal and is transferred

to the slave on the next edge or level of control signal. Each section is a latch . Master is positive

- edge triggered and slave is negative - edge triggered.

DESIGN:

The excitation table of JK flip-flop is:

Q

t

Q

t+1

J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

The function table of JK ip-op is:

J K Q

t

Q

t+1

COMMENT

0 0 0

1

0

1

No

Change

0 1 0

1

0

0

Reset

1 0 0

1

1

1

Set

1 1 0

1

1

0

Q

t

PIN DIAGRAM:

14

13

12

11

10

9

8 7

6

5

4

3

2

1 Input 1

Input 1

Input 2

Input 2

Input 2

Output 2

GND

+V

CC

Input 1

Input 3

Input 3

Input 3

Output 1

Output 3

7

4

1

0

Logic Design-Lab Manual.indd 9 8/17/2012 12:34:22 PM

10 Logic Design

14

13

12

11

10

9

8 7

6

5

4

3

2

1 Input 1

Input 1

Output 1

Input 2

Input 2

Output 2

GND

+V

CC

Input 4

Output 4

Input 3

Input 3

Input 4

Output 3

7

4

0

0

CIRCUIT DIAGRAM:

7400

7400 7400

7400 7400

7410

7410 7410

12

6

13

2

4 4'

5'

6'

12'

13'

11'

5

6

2'

10'

1

2

1 3

1' 3' 9' 8'

3

4

5

8

9

10

K

J

CLK

Q

Q

7400

OR

7400

7400 7400

7400

7400

7410

7410

+V

CC

+V

CC

7410

12

13

11

1

1

2'

13'

4

5

6

12

13

11

12'

2

10

Q

Q

1

2 10

9

8

1 3 9 8

3

5

4

6'

3'

4'

5'

7410

K

J

Logic Design-Lab Manual.indd 10 8/17/2012 12:34:22 PM

LD Lab Manual 11

Note: 1, 2 and so on are the pin numbers of different ICs of IC 7400.

PROCEDURE:

1) Check all the ICs before making the connections.

2) Make the connections as shown in circuit diagram.

3) Give supply to the trainer kit.

4) Provide input data to the circuit via switches.

5) Verify the truth table sequence and observe the output.

RESULT:

JK master/ slave ip-op is realized using NAND gates.

EXPERIMENT 4

Design and implement a mod - n (n<8) synchronous up counter using JK ip-op ICs.

COMPONENTS REQUIRED:

IC 7476, Basic gates (depending on design), digital trainer kit, patch chords , power chords.

THEORY:

A counter is a sequential circuit formed by cascading ip-ops. If the clock pulses to be control

are applied simultaneously to the control input of all the ip-ops in cascade, the such counters

are called as synchronous counters. All of these counters progress one count at a time in a strict

binary fashion and have a modulus given by 2

m

where m indicates the number of ip-ops. It is

rst necessary to nd the relation 2

m

n where m= number of ip-ops required and n= number

of count. A state diagram is used to describe the operation of the counter.

DESIGN:

We are supposed to design mod-n synchronous counter. The value of n will be given by the

examiner.

Let us assume that we are supposed to design mod-5 synchronous counter. Here the value of

n=5. The counter counts from 0 to 4. The counter does not count 5,6 and 7. Hence dont cares

={5,6,7}.

Step 1: Find the number of ip-ops required using the relation:

2

m

n

2

m

5 [Here n = 5 as we are supposed to design mod-5 synchronous counter]

m = 3

Total number of flip-flops required to design mod-5 synchronous counter is 3.

Step 2: State diagram for mod-5 synchronous counter is:

Logic Design-Lab Manual.indd 11 8/17/2012 12:34:22 PM

12 Logic Design

000

100

001

011

010

Mod - 5

synchronous

counter

Step 3: Excitation table for JK flip-flop is:

Q

t

Q

t+1

J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Step 4: Let Q

A,

Q

B

and Q

C

be three flip-flop states.

The transition table is:

COUNT Q

A

Q

B

Q

C

Q

A

' Q

B

' Q

C

J

A

K

A

J

B

K

B

J

C

K

C

0 0 0 0 0 0 1 0 X 0 X 1 X

1 0 0 1 0 1 0 0 X 1 X X 1

2 0 1 0 0 1 1 0 X X 0 1 X

3 0 1 1 1 0 0 1 X X 1 X 1

4 1 0 0 0 0 0 X 1 0 X 0 X

d= {5,6,7}.

Q

A,

Q

B

Q

C

= Present state On application of clock pulse Q

A

Q

B

Q

C

changes to Q

A

Q

B

Q

C

which

are the next states.

Initially the counter is in state 0= 000 = Q

A

Q

B

Q

C

on application of clock pulse it changes to

001= Q

A

Q

B

Q

C

which is shown at count = 0 of transition table. Similar explanation holds good

from count=1 to 4.

In order to find J

A

K

A

, compare Q

A

and Q

A

. Here Q

A,

= 0 & Q

A

= 0 [for count = 0]. Find what

is the value of JK if Q

t

Q

t+1

= 00 from excitation table. When Q

t

Q

t+1

= Q

A

Q

A

= 00, the value of JK

= 0x. This is the value of J

A

K

A

as shown in transition table for count = 0.

Similarly, to find J

B

K

C

, compare Q

C

and Q

C

. Then find its corresponding J and K values from

the excitation table.

Logic Design-Lab Manual.indd 12 8/17/2012 12:34:22 PM

LD Lab Manual 13

Step 5: Obtain J

A

, K

A

, J

B

, K

B

, J

C

and K

C

values by drawing K-map and by using step 4.

From step 4:

J

A

= m(3) + d(4) + d(5, 6, 7)

= m(3) + d(4, 5, 6, 7)

[Dont cares = {5, 6, 7} for all J & K values.

J

B

= m(1) + d(2, 3, 5, 6, 7)

J

C

= m(0, 2) + d(1, 3, 5, 6, 7)

K

A

= m(4) + d(0, 1, 2, 3, 5, 6, 7)

K

B

= m(3) + d(0, 1, 4, 5, 6, 7)

K

C

= m(1, 3) + d(0, 2, 4, 5, 6, 7)

Plot these minterms on K-map and find Js and Ks values.

00 01 11 10

0

0 1

1

3

2

1 X

4

X

5

X

7

X

6

J

A

= Q

B

Q

C

Q

B

Q

C

Q

A

00 01 11 10

0 X X X X

1 X X

X X

K

A

= 1 = +5V

Q

B

Q

C

Q

A

00 01 11 10

0 1 X X

1 X

X X

J

B

= Q

C

Q

B

Q

C

Q

A

00 01 11 10

0 X X 1

1 X X

X X

K

B

= Q

C

Q

B

Q

C

Q

A

Logic Design-Lab Manual.indd 13 8/17/2012 12:34:23 PM

14 Logic Design

00 01 11 10

0 1 1 X 1

1 X

X X

J

B

= Q

__

A

Q

B

Q

C

Q

A

Q

B

Q

C

00 01 11 10

0 X 1 1 X

1 X X

X X

K

B

= 1 = + 5V

Q

A

Step 6: Use values of J

A

, K

A

, J

B

, K

B

, J

C

and K

C

from step 5 and draw the circuit diagram.

PIN DIAGRAM:

CLK 1

J

A

+V

CC

CLK 2

PRE 1

CLR 1

PRE 2

CLR 2

1 16

15

14

13

12

11

10

9

2

3

4

5

6

7

8

K

A

Q

A

Q

A

GND

K

B

Q

B

Q

B

J

B

7

4

7

6

Logic Design-Lab Manual.indd 14 8/17/2012 12:34:23 PM

LD Lab Manual 15

CIRCUIT DIAGRAM:

+

5

V

+

5

V

J

A

K

A

Q

A

Q

A

C

L

R

1

3

7476

J

B

K

B

Q

B

Q

B

C

L

R

2

7476

J

C

K

C

Q

C

Q

C

C

L

R

3

7476

C

L

K

1

4

1

1

6

6

1

5

9

1

2

8

3

1

5

2

1

P

R

E

2

P

R

E

1

P

R

E

1

7

1

1

41

6

C

L

K

1

2

Q

C

Q

B

Q

A

7

4

0

8

3

1

2

I

C

2

o

f

7

4

7

6

I

C

1

o

f

7

4

7

6

O

U

T

P

U

T

S

Logic Design-Lab Manual.indd 15 8/17/2012 12:34:23 PM

16 Logic Design

PROCEDURE:

1. Check the ICs and make the connections as shown in circuit diagram.

2. Connect pin numbers of 1, 6 (IC1 of 7476) to pin number 1 (IC2 of 7476) to common

clock.

3. Connect Q

A

, Q

B

and Q

C

to the output and observe the output after giving the clock pulse.

Verify the truth table

4. Remove the connections after observing the output.

RESULT:

The mod-5 synchronous counter is designed and implemented using JK ip-op.

EXPERIMENT 5

Design and implement ring counter using 4-bit shift register.

COMPONENTS REQUIRED:

IC 7495, digital trainer kit, patch chords, power chord.

THEORY:

A ring counter is a circular shift register with only one ip-op being set at any particular time

and all others being cleared. A single bit is shifted from one ip-op to the other to produce the

sequence of timing signals. Here the last output in a shift register is connected back to the serial

input.

DESIGN:

The initial value of the register is 1000 at clock pulse = 0. Single bit is shifted right on the

application of clock pulse and circulates back from Q

3

to Q

0

. Each ip-op is in 1 state once every

four clock pulses.

PIN DIAGRAM:

D

S

= SERIAL INPUT

A = DATA 0

B = DATA 1

C = DATA 2

D = DATA 3

MC = MODE CONTROL

GND

+ V

CC

Q

0

= Q

A

Q

1

= Q

B

Q

2

= Q

C

Q

3

= Q

D

CLK 1

CLK 2

(OUT ENABLE)

1 14

13

12

11

10

9

8

2

3

4

5

6

7

7

4

9

5

Q

0

, Q

1

, Q

2

, Q

3

= outputs

Logic Design-Lab Manual.indd 16 8/17/2012 12:34:23 PM

LD Lab Manual 17

TRUTH TABLE:

The count sequence of a ring counter is:

CLOCK

PULSE

Q

0

Q

1

Q

2

Q

3

0

1 0 0 0

1

0 1 0 0

2

0 0 1 0

3

0 0 0 1

Initially make MC = 1 (Pin 6) and Data 0 = 1 (Pin 2), then apply a clock pulse. Now 1 will

be stored in Q

0

. Now make MC = 0 but do not make any changes to pin 2. Then we will get the

sequence as shown in above table.

If we want the count sequence as shown below then make MC = 1 and Data 2 = 1 [Pin 4]. Then

apply a clock pulse. Make MC = 0 with out changing pin 4.

CLOCK Q

0

Q

1

Q

2

Q

3

0 0 0 1 0

1 0 0 0 1

2 1 0 0 0

3 0 1 0 0

CIRCUIT DIAGRAM:

Circuit diagram to start the sequence from

1000 0100 0010 0001

1

13

12

11

10

8

9

2

3

4

5

6 7 14

Q

A

= Q

0

Q

B

= Q

1

Q

C

= Q

2

Q

D

= Q

3

SERIAL INPUT

CLOCK

A

B

C

D

MC

+V

CC

7

4

9

5

Logic Design-Lab Manual.indd 17 8/17/2012 12:34:23 PM

18 Logic Design

PROCEDURE:

1. Make circuit connections as shown in circuit diagram.

2. Connect last output (ie. Q

3

= Q

D

)to the serial input. That is connect pin 1 to pin 10.

3. Make MC = 1, A = 1 or B = 1 or C = 1 or D = 1 depending on how you want the data to be

shifted. Then make MC = 0 without changing value of A or B or C or D.

4. Verify the output as per truth table.

5. Disconnect the circuit.

RESULT:

A ring-counter using 4-bit shift register has been designed and implemented.

EXPERIMENT 6

Design and implement an asynchronous counter using decade counter IC to count up

from 0 to n (n < = 9).

COMPONENTS REQUIRED:

IC 7490, digital trainer kit, patch chords, power chords

THEORY:

Asynchronous counter is also called as Ripple counter as the i

th

ip-op is toggled by a change

in the (i - 1)

th

ip-op. The pulses to be counted ripple through the counter. These counters are

called as asynchronous counter as the clock pulses are not simultaneously applied to all the ip-

ops.

7490 is a TTL MSI decade counter (can count from 0 - 9 ie. 10). The ip-op Q

B

, Q

C

, Q

D

form

mod-5 counter. Flip-op Q

D

is a RS ip-op that has direct connection from its Q input back to

its R input. The net result in this case Q

D

behaves exactly like a JK ip-ip. If system clock is

applied at input A & Q

A

(ie. pin 14 and pin 12) is connected to input B (ie Pin 1), then we have

a true binary decade counter. On the other hand if system clock is applied at input B and Q

D

is

connected to input A, then we have biquinary counter.

DESIGN:

Decade counter is also known as divide by N-counter. 7490 is a decade counter. Pins Q

A

, Q

B

,

Q

C

and Q

D

are the outputs. Data in pin (pin 1) is connected to pin 12 (Q

A

). MR

1

, MR

2

(master

reset) and MS

1

, MS

2

(master set) are grounded. This set up makes IC 7490 to work as decade

counter.

Logic Design-Lab Manual.indd 18 8/17/2012 12:34:23 PM

LD Lab Manual 19

PIN DIAGRAM:

MR1

MR2

NC

+V

CC

MS1

MS2

NC

QA = Q

A

QD = Q

D

GND

QB = Q

B

QC = Q

C

1 14

13

12

11

10

9

8

2

3

4

5

6

7

7

4

9

0

DATAIN

CLK B

=

CLK A

NC = Not Connected

TRUTH TABLE:

1. 7490 as mod-10 counter:

COUNT Q

D

Q

C

Q

B

Q

A

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

2. 7490 as mod-5 counter:

COUNT Q

D

Q

C

Q

B

Q

A

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

3. 7490 as mod-7 counter:

Logic Design-Lab Manual.indd 19 8/17/2012 12:34:23 PM

20 Logic Design

COUNT Q

D

Q

C

Q

B

Q

A

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

CIRCUIT DIAGRAM:

1. 7490 as decade (mod-10) counter:

1 12

9

8

11

14

2

3

6

7

5 10

Q

A

(LSB)

Q

B

Q

C

Q

D

(MSB)

7

4

9

0

MR2

MS1

MS2

MR1

CLKA

DATA IN

+5V

= +V

CC

2. 7490 as mod-5 asynchronous counter:

Consider 5 =

D C B A

0 1 0 1

(Q , Q , Q , Q )

. Which ever bits are 1, consider those bits. Here Q

A

= 1 and

Q

C

= 1. Connect Q

A

to MR1 and Q

C

to MR2. MS1 and MS2 should be connected to ground.

Logic Design-Lab Manual.indd 20 8/17/2012 12:34:23 PM

LD Lab Manual 21

1 12

9

8

11

14

6

7

2

3

5 10

Q

A

Q

B

Q

C

Q

D

7

4

9

0

MS2

MR1

MR2

MS1

CLKA

DATA IN

+V

CC

3. 7490 as mod-7 asynchronous counter:

Consider 7 =

D C B A

0 1 0 1

(Q , Q , Q , Q )

. Connect Q

A

to MR1. Q

C

is 1 and Q

B

is 1. Connect Q

C

and Q

B

as input for AND gate and connect output of this AND gate to MR2. Ground MS1 and MS2.

MR2

7408

3

1 2

Q

C

Q

B

Q

B

Q

A

Q

C

1

1 1

Q

D

Connect to MR1

7=

Logic Design-Lab Manual.indd 21 8/17/2012 12:34:24 PM

22 Logic Design

1 12

9

8

11

14

6

7

2

3

5 10

Q

A

Q

B

Q

C

Q

D

7

4

9

0

MS2

MR1

MR2

MS1

CLKA

DATA IN

+5V= +V

CC

7408

2 1

3

PROCEDURE:

1. Check IC 7490 using IC tester.

2. Make connections as shown in circuit diagrams.

3. To construct mod-10 asynchronous counter, short MR1, MR2, MS1 and MS2 and connect it

to GND.

4. To construct mod-5 asynchronous counter, short MS1, MS2 and give it to ground. Connect

Q

A

to MR1 and Q

C

to MR2.

5. To construct mod-7 asynchronous counter, ground MS1 and MS2. Connect Q

A

to MR1.

Connect Q

C

and Q

B

as inputs of AND gate (IC 7408). Connect output of AND gate to MR2.

6. Switch on the power supply and verify the truth table.

RESULT:

Asynchronous counter using decade counter for mod-10, mod-5 and mod-7 are designed,

implemented and their truth tables are veried.

EXPERIMENT - 7

Design a 4-bit R-2R ladder D/A converter using OP-AMP. Determine its accuracy and

resolution.

COMPONENTS REQUIRED:

OP-AMP uA 741, Resistors: 1k and 2k, digital multimeter, connecting wires, IC trainer

kit.

Logic Design-Lab Manual.indd 22 8/17/2012 12:34:25 PM

LD Lab Manual 23

THEORY:

R-2R ladder is an digital-to-analog converter (DAC). A ladder is a series/parallel resistor

network. It requires only two resistors: R and 2R. It consists of S

0

, S

1

, S

2

and S

3

which are

electronic switches. These electronic switches are digitally controlled when 1 is present on MSB

line. Switch S

3

connects the resistor 2R to V

ref

.Conversely if 0 is present on MSB line switch S

3

connects the same resistor to the ground line. As the ladder is composed of linear resistors, it is a

linear network and the principle of super position can be used.

A 4-bit DAC using R-2R ladder and an Op-Amp voltage follower acting as a buffer stage D

0

,

D

1

, D

2

, D

3

as digital inputs. Each digital input may be Low (= 0) or High (= 1). The total output

voltage due to combination of input digital levels can be found simply by taking the sum of the

output levels caused by each digital input individually.

DESIGN:

( )

R

0 3 2 1 0

V

V 8D 4D 2D D

24

= + + +

V

R

= Reference voltage = +5V

V

0

= V

R

Number of steps /24

[ ]

[ ]

0

0

5 1

V 0.208V Minimumstepsize

24

5 15

V 3.125V Maximumstepsize

24

Fullscalevoltage

Stepsize

Total number of steps

= =

= =

=

Number of steps = 2

n

- 1

Since it is a 4-bit DAC, 2

4

-1 = 15 steps

3.125

Stepsize 0.2083V

15

= =

PIN DIAGRAM:

OFFSET

INVERTING INPUT

NON - INVERTING INPUT

-V

CC

1 8

7

6

5

2

3

4

NC

+V

CC

OUTPUT

OFFSET

7

4

1

Logic Design-Lab Manual.indd 23 8/17/2012 12:34:25 PM

24 Logic Design

CIRCUIT DIAGRAM:

2R 2R 2R 2R

R R R

2R 2R

(MSB)

S

1

S

0

D

0

D

1

D

2

D

3

S

2

S

3

(LSB)

741

-

+

MULTI

METER

2

3

+15V

7

6

V

0

-15V

V

ref

= +5V

OBSERVATION:

Decimal

Equivalent

DIGITAL INPUTS ANALOG OUTPUT VOLTAGE (VOLTS)

D

3

D

2

D

1

D

0

Theoretical Value V

O

Practical Values V

O

0 0 0 0 0 0

1 0 0 0 1 0.2083

2 0 0 1 0 0.4166

3 0 0 1 1 0.6249

4 0 1 0 0 0.8332

5 0 1 0 1 1.0415

6 0 1 1 0 1.2498

7 0 1 1 1 1.4581

8 1 0 0 0 1.6664

9 1 0 0 1 1.8747

10 1 0 1 0 2.083

11 1 0 1 1 2.2913

12 1 1 0 0 2.4996

13 1 1 0 1 2.7079

14 1 1 1 0 2.9162

15 1 1 1 1 3.1245

Logic Design-Lab Manual.indd 24 8/17/2012 12:34:28 PM

LD Lab Manual 25

Find practical value V

0

from the circuit. Plot the graph as shown below:

0000 0001 0010 0011 0100 1111

DIGITAL INPUTS

0.6

3.6

0.4

0.2

STAIRCASE

OUTPUT

ANALOG

OUTPUT

VOLTAGE

PROCEDURE:

1. Verify all the components and make connections as shown in the circuit diagram.

2. For different digital inputs measure the output voltage using multi-meter.

3. Verify if the theoretical values are matching with the practical values and observe the

outputs.

4. Plot the graph of Digital inputs versus Analog output voltage and observe the staircase out-

put.

RESULT:

A 4-bit R-2R ladder digital to analog convertor using op-amp has been designed and veried.

Logic Design-Lab Manual.indd 25 8/17/2012 12:34:28 PM

26 Logic Design

VHDL/VERILOG LABORATORY MANUAL

1. Write a Verilog / VHDL code for 8: 1 Multiplexer. Simulate and verify its working.

2. Write a Verilog / VHDL code for a Full adder. Simulate and verify its working.

3. Write a Verilog / VHDL code for a D Flip-Flop with positive Edge triggering. Simulate and

verify its working.

4. Write a Verilog / VHDL code for mod 8 up-counter. Simulate and verify its working.

5. Write a Verilog / VHDL code for Switched tail counter. Simulate and verify its working.

(Johnson Counter)

VHDL

Basic design methodology is as shown below:

Part - B

Logic Design-Lab Manual.indd 26 8/17/2012 12:34:28 PM

LD Lab Manual 27

Programmable logic devices can be classied as:

HDL: Hardware Description Language is a programming language used to model the intended

operation of a piece of hardware. A HDL is similar to a typical computer programming language

except that an HDL is used to describe hardware rather than a program to be executed on a

computer.

Many commercial HDLs are available. Some are proprietary, meaning that they are provided by

a particular company and can be used to implement circuits only in the technology provided by

that company.

Two HDLs are IEEE standards: VHDL and Verilog HDL

Both languages are widely used in the industry. Although the two languages differ in many ways,

the choice of using one or the other when studying logic circuits is not particularly important,

because both offer similar features.

VHDL is an Acronym for Very High Speed Integrated Circuits Hardware Description Language.

VHDL was Commissioned in 1981 by Department of Defense; Designed by IBM, TI, Intermetrics;

standardized by IEEE in 1987; this version of the language is known as IEEE Std 1076-1987.

In 1993, VHDL restandardized to clarify and enhance the language resulting in 9 value logic

package; this package was called STD_LOGIC_1164, VHDL Standard 1164-1993.

General features of VHDL:

The language can be used as an exchange medium between chip vendors and CAD tool user

and can be used as communication medium between CAD and CAE tools.

It supports hierarchy.

It is not a case sensitive language.

Logic Design-Lab Manual.indd 27 8/17/2012 12:34:28 PM

28 Logic Design

It is strongly type checked language.

It provides design portability and exible design methodologies: top down, bottom up or

mixed

It supports both synchronous and asynchronous timing models.

Nominal Propagation delays, min-max delays, setup and hold timing constraint and spike

detection can be described in this language.

VHDL can be written using 4- Modeling system. They are:

Data ow modeling

Behavioral modeling

Structural modeling

Mixed modeling

Simulation: A design description or model written in VHDL is usually run through a VHDL

simulator to demonstrate the behavior of the modeled system.

Logic Synthesis: Some parts of VHDL can be used with logic synthesis tools for producing a

physical design.

In particular many VLSI gate array vendors can convert a VHDL design description into a gate

level net list from which a customized integrated circuit component can then be built.

The application of VHDL is:

Simulation: behavior verication of design

Synthesis: generating net list (component).

Documentation: documenting the design

Designing using VHDL refers to writing code and then verifying the function using simulator and

using synthesis tool develop net list of gates / ip ops/mux etc. VHDL is Technology Independent

which means that irrespective of the technologies adopted in the manufacture, or upgrading the

features and facilities of any IC the coding remains unchanged as we are describing the Hardware

and its logic. The language supports hierarchies, reusable components, error management and

verication. Hierarchies are dened using structural representation of VHDL and also with

procedures and functions.

Design Phases: Start with a design idea Generate behavioral model denition. Specify the overall

functionality and the input and output mapping. Logic design is the next phase. This Involves use

of primitive gates and ip ops for the implementation of data registers busses, logic units and

their controlling hardware. Final step is the manufacturing which uses transistor list or layout

specication to burn fuses of eld programmable (PLDs) device or to generate masks for IC

fabrication.

Limitations: For Digital Design the VHDL is very useful but for analog there are limitations.

VHDL cannot be used for Physical information for layout manufacture information, packaging

power dissipation, electrical operating conditions, reliability worst case timing, and price.

Every VHDL code must be compulsorily added with 2 lines:

Logic Design-Lab Manual.indd 28 8/17/2012 12:34:29 PM

LD Lab Manual 29

LIBRARY IEEE;

USE ieee.std.logic_1164.all;

The library_name represents the location in the computer le system where the package is stored.

A library can either be provided as part of a CAD system, in which case it is termed a system

library or be created by the user, in which case it is called a user library.An example of a

system library is the IEEE library. A special case of a user library is represented by the le-system

directory where the VHDL source code le that declares a package is stored. This directory can

be referred by the library name work, which stands for working directory.

A VHDL package serves as a repository. It is used to hold VHDL code that is of general use,

like the code that denes a type. The IEEE library includes four packages.

STD_logic _1164,

STD_logic_signed,

STD_logic_unsigned &

STD_logic_arith

VHDL consists of following elements:

1. Entity

2. Architecture

3. Process

4. Library

5. Packages

6. Conguration

7. Attribute

8. Generics

9. Data types

10. Subprograms (function and procedures.)

A VHDL model consists of: Entity Declaration and Architecture Body.

The entity describes the external interface to the model (inputs, outputs). It is the Hardware

abstraction of a Digital system, but it does not provide any inner details.

The architecture describes the function/behavior of the model. Behavior of entity is dened

by the relationship of the input to the output. It species the inner details of the circuit.

ENTITY

The entity declaration species the components input/ output connections. Syntax of

entity is:

entity [entity_name] is;

Logic Design-Lab Manual.indd 29 8/17/2012 12:34:29 PM

30 Logic Design

port [sig_name :(port direction ) data type];

end [ entity_name];

* name :signal name which is user dened.

* port direction: signal directions it may be

one of these in, out, inout and buffer

* Datatype :what type of data that the signal carries.

* Entity ,port, end,& is are reserved words.

ARCHITECTURE

An Architecture design unit species the behavior, interconnections and components of a

previously compiled design entity. The architecture denes the function and behavior of design

entity. It species the relationship between the inputs and outputs of design entity that may be

expressed in terms of behavior, data ow or structure. Architecture consists of two parts:

Architecture declarative part

Architecture statement part.

Declarative part starts from the key word is and end before the keyword begin. In this part we

can declare signals, types, components etc. Statement part starts after the keyword begin and

ends before the keyword end architecture In statement part we can write concurrent statements

like when else, with select ,generate statements etc. Syntax of architecture is:

Architecture architecture-name of entity-name is

[architecture item declaration]

Begin

Concurrent statement -- call statement

Process statements -- sequential statement

Generate statements -- concurrent Statement

End architecture Architecture name;

VHDL can be written using 4- Modeling system. They are:

Data ow modeling

Behavioral modeling

Structural modeling

Mixed modeling

Commonly used architecture construct can be written in three forms:

Behavioral Architecture 1.

Structural Architecture 2.

Data ow Architecture. 3.

Logic Design-Lab Manual.indd 30 8/17/2012 12:34:29 PM

LD Lab Manual 31

Behavioral description is basically a black box approach. It accurately models what happens on

the inputs and outputs of the black box, but inside the box. Behavioral description is sometime

referred as High level description.

Process statements are used to express Sequential.

Structural description is basically a modular approach. To make the design more understandable

and maintainable a design is typically decomposed into several blocks. These blocks are then

connected together to form a complete design.

Component Instantiation are used to express structural

Data ow description approach is through Signal ow through the circuit. The Dataow

Architecture species how data will be transferred from Signal to Signal and input to output

without the use of sequential statements. Data ow architecture use concurrent signal assignment.

Concurrent Signal assignment statements are used to express dataow

PROCESS:

A Process is the basic unit of execution in VHDL architecture statement. All operations that are

performed in a simulation of a VHDL description are broken into single or multiple processes. The

process is a region of VHDL code, inside which statements execute in sequence. In architecture

for an entity, all the statements are concurrent. So if we want to write sequential statements inside

the architecture will have to use statement called process statement.

Process statement has two parts:

1. Process declarative.

2. Statement part.

Process declarative part starts from the keyword process and ends before the keyword

begin. In this part we can declare types, variables, constants and subprograms etc.

Statement part starts after the keyword begin and ends before the keyword end. Here we

can write only sequential statements like if then else, case statements, loop statements.etc.

LIBRARY

Technology libraries hold all the information necessary for a synthesis tool to create a net-list for

a design based on the desired logical behavior and constraints on the design. VHDL also allows a

library called WORK to be dened as the library into which design units are compiled if no library

destination is specied. Explicit visibility of items declared in other design units can be achieved

using Library clause, and use clause:

Library IEEE;

Use IEEE.std_logic_1164.all;

In the above declaration the logical name IEEE and the items present in the library are visible

to all design units. Inside the IEEE library a package std_logic_1164.all is declared which

is called in the design using use command. A library clause denes logical names for design

libraries in the host environment. The library clause denes the logical names of design libraries

Logic Design-Lab Manual.indd 31 8/17/2012 12:34:29 PM

32 Logic Design

which are used by the design units. A library is a storage facility for previously analyzed design

units.

PACKAGE

A package contains a collection of denitions that may be referred by many designs at the same

time. A package is a separate design unit in VHDL. Therefore it exists outside of the other design

units that we have explained earlier such as entity, architecture, conguration etc. Declaring Data

Inside the package allows the data to be referenced by other entities. Data can be shared by

any other design entity. A package may contain denitions of constant values, user dened data

types, component declarations or sub programs of VHDL codes that are shared between different

designs.

CONFIGURATION

A conguration statement is used to bind a component instance to an entity architecture pair. A

conguration can be considered as parts list for a design. It describes which behavior to use for

each entity. An entity can have more than one architecture but how does the tool choose which

architecture to use in a given simulation?

ATTRIBUTE

An attribute is a value, function, type, range, signal or constant that can be associated with certain

names within a VHDL description. These names could be among an entity name an architecture

name, a label or a signal. (Clk event) event is an attribute for the clk.

GENERICS

A generic is VHDL term for a parameter that passes information to an entity. For example if an

entity is a gate level model with rise, fall delay and bus width etc. values for the rise, fall delays

and bus size could be passed into the entity with generics.

Syntax for generic is:

generic [generic name] : [(parameter name): range data type];

Generics can be declared before the port declaration in the entity. Parameter values can passed

into the design easily without changing the codes.

SUB PROGRAMS

A Sub Program denes a sequential algorithm that performs certain computations. There are two

kinds of sub programs namely

Functions

Procedures.

Functions are used to describe frequently used algorithms that return a single value. This value is

Logic Design-Lab Manual.indd 32 8/17/2012 12:34:29 PM

LD Lab Manual 33

returned to the calling program using a return statement.

Procedures allow decomposition of large behaviors into modular sections. In contrast to a

function a procedure can return zero or more values using parameters of mode out and inout.

Direction of Signals

Signals hold a list of values, which includes current value and set of future values. Future values

can be assigned to a signal using signal assignment statement. Used in intermediate signals.

Signals can have following directions:

Modes IN: Port receiving data only with respect to systems internals. Read is allowed from that

signal and no write operation is permitted.

Mode OUT: With respect to system internals write is allowed on such signals and no read is

permitted.

Mode INOUT: The port is bi-directional hence it is allowed both read and write into such a

signal.

Buffer: Same as inout but allowed for read only. This signal cannot have more than one source.

Syntax for signal is:

Signal signal name : signal type ( := initial value);

For ex: A signal declaration may be: Signal a,b : std_logic ;

CONCURRENT VHDL STATEMENTS

WHEN ELSE STATEMENT:

These statements directly write in the architecture, unlike sequential statements. This statement

selects different values for the target based on the different condition. This statement is similar to

IF statement.

Syntax:

Target <=expression 1 when condition 1 else

expression 2 when condition 2 else

..

expression N when condition N else

expression N+1;

SEQUENTIAL VHDL STATEMENTS

PROCESS STATEMENT:

Process statement is the primary concurrent statement which allows to write sequential statements

inside. Process denes the sequential behavior of entire or some portion of the design. Process

Logic Design-Lab Manual.indd 33 8/17/2012 12:34:29 PM

34 Logic Design

statement has three parts:

Sensitivity list part. 1.

Declaration part 2.

Statement part 3.

A set of signals to which the process is sensitive is called as sensitivity list. The list of signals

written in bracket followed by the reserve word process is called as sensitivity list.

The process declarative part:

The area between the end of sensitivity list and the key word Begin.

Variables and constants are declared here.

The process statement part:

Starts at the key word Begin and ends at the end Process line.

Syntax:

Process [(sensitivity list)]

declarations1;

declaration2;

Begin

Sequential statement1;

Sequential statement 2 ;

End process;

Sequential Statements: if then else

Syntax:

If condition 1 then statements

Elsif condition 2 then statements

Elsif condition 3 then statements

Else statement

End if;

Case Statements:

Case statements select one of branches for execution based on the value of the expression. case

statement consists of the keyword case followed by an expression and the keyword is.

Syntax is:

Case expression is

when choice1=>statements

when choice2=>statements

when choice n=>statements

when others=> statements

end case;

Logic Design-Lab Manual.indd 34 8/17/2012 12:34:29 PM

LD Lab Manual 35

Loop Statements:

Loop statement is used whenever an operation needs to be repeated. Loop statements are used

when powerful iteration capability is needed to implement a model. Iteration (Repetitive operations

or cyclic operations) loop statements include the sequence of statements to be executed repeatedly

once at least or more number of times depending on the statement. Types of loop statements are:

1. For loop 2. While loop

Syntax for for loop is:

[label]: For loop_parameters in discrete range loop statements

Syntax for while loop is:

[label]: while condition loop

statements

end loop[label];

SYNTHESIS TOOLS:

Currently there is No single free synthesis tool available. Following is a list of commercially

available synthesis tools.

Xilinx, Isc

xilinx XST (Modelsim)

Altera

QuartusII Tool (Modelsim)

Synopsys, Inc.

Design Compiler and Behavioral Compiler

Synplicity, Inc.

Synplify

Exemplar Logic

Leonardo Spectrum

Mentor Graphics Corp.

AutoLogic and PLDSynthesis

Avanti

Asyn

Cadence Design Systems Inc.

Ambit

Logic Design-Lab Manual.indd 35 8/17/2012 12:34:29 PM

36 Logic Design

VHDL CODE

1.b. Write a Verilog / VHDL code for 8: 1 Multiplexer. Simulate and verify its

working.

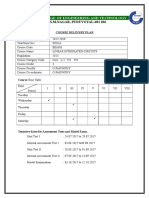

Truth table for 8:1 MUX

Decimal s2 s1 s0 MUX OUTPUT=y

0 0 0 0 D0

D1 1 0 0 1

2 0 1 0 D2

D3 3 0 1 1

4 1 0 0 D4

D5 5 1 0 1

6 1 1 0 D6

D7 7 1 1 1

VHDL code for 8:1 MUX

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity MUX is

Port ( d : in STD_LOGIC_vector(7 downto 0); //Input for 8:1 Mux

s : in STD_LOGIC_vector(2 downto 0); //Selection Lines s2,s1,s0

y : out STD_LOGIC); // Output of Mux

end MUX;

Architecture Behavioral of MUX is

Begin

y<=d(0) when s=000 else

d(1) when s=001 else

d(2) when s=010 else

Logic Design-Lab Manual.indd 36 8/17/2012 12:34:30 PM

LD Lab Manual 37

d(3) when s=011 else

d(4) when s=100 else

d(5) when s=101 else

d(6) when s=110 else

d(7);

End behavioral;

STEPS TO OBTAIN OUTPUT WAVEFORM FOR 8:1 multiplexer:

Step 1: Synthesis for 8:1 multiplexer.

Double click on Xilinx icon.

Open File New project

Type Project name and click Next.

Click Next.

Logic Design-Lab Manual.indd 37 8/17/2012 12:34:30 PM

38 Logic Design

Click Next.

Click Next.

Logic Design-Lab Manual.indd 38 8/17/2012 12:34:30 PM

LD Lab Manual 39

Click Finish.

Logic Design-Lab Manual.indd 39 8/17/2012 12:34:30 PM

40 Logic Design

Go to Processes Double click on Create New Source.

Click on VHDL Modulethen type the le name i.e. MUX click Next.

Dene input and output ports. Then click Next. Here d, s are input ports and y is output port.

Click Finish.

Logic Design-Lab Manual.indd 40 8/17/2012 12:34:31 PM

LD Lab Manual 41

Type the code here.

Type the code and then click on Save.

Logic Design-Lab Manual.indd 41 8/17/2012 12:34:31 PM

42 Logic Design

Go to Processes Implement Design Synthesize-XST click on Check Syntax.

If there are no errors, a tick mark appears in Check Syntax and the screen is as shown below:

Logic Design-Lab Manual.indd 42 8/17/2012 12:34:31 PM

LD Lab Manual 43

Step 2: Simulation for 8:1 multiplexer.

After Synthesis/Implementation go to Sources for change Synthesis/Implementation to

Behavioral Simulation. Go to Processes ModelSim Simulator.

Here U=undened. Dened ands. Right click ond and dene some values ford.

Logic Design-Lab Manual.indd 43 8/17/2012 12:34:32 PM

44 Logic Design

The values forced for d=d7 d6 d5 d4 d3 d2 d1 d0= 1010 1101(assume. We can change the values

ford for our convenience).

Next, force values fors from 000 t0 111 as s2 s1 s0 are selection lines.

Logic Design-Lab Manual.indd 44 8/17/2012 12:34:32 PM

LD Lab Manual 45

Following is the output for d=10101101. Depending on the values of s, we can nd the output

waveform. If s =001(Decimal equivalent of 001=1), then y=0 as d1=0 in d=10101101= d7 d6 d5

d4 d3 d2 d1 d0.

Similarly, if s =111(Decimal equivalent of 111=7), then y=1 as d7=1 in d=10101101= d7 d6 d5

d4 d3 d2 d1 d0.

2. b Write a Verilog / VHDL code for a Full adder. Simulate and verify its working.

Truth table for Full adder

A B C Sum Cout

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Logic Design-Lab Manual.indd 45 8/17/2012 12:34:32 PM

46 Logic Design

VHDL code for Full adder

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity fulladder is

Port ( a,b,c : in STD_LOGIC;

sum, cout : out STD_LOGIC);

End fulladder;

Architecture Behavioral of fulladder is

Begin

sum <=a xor b xor c;

cout<=(a and b) or (b and c) or (c and a);

End Behavioral;

STEPS TO OBTAIN OUTPUT WAVEFORM FOR Full adder:

Step 1: Synthesis for full adder.

Double click on Xilinx icon.

Open File New project

Logic Design-Lab Manual.indd 46 8/17/2012 12:34:33 PM

LD Lab Manual 47

Type project name E.g. Fulladder Next

You will get New Project Wizardthen click Next

Logic Design-Lab Manual.indd 47 8/17/2012 12:34:33 PM

48 Logic Design

Create New Source screen Click Next.

Add Existing Sources screen Click Next

Logic Design-Lab Manual.indd 48 8/17/2012 12:34:33 PM

LD Lab Manual 49

Project Summary screen Click Finish

Select Synthesis/ Implementation from Sources for as shown below:

Logic Design-Lab Manual.indd 49 8/17/2012 12:34:34 PM

50 Logic Design

Go to Processes and double click on Create New Source.

Select Source type as VHDL module (If you are writing VHDL code), then type the le name

click Next.

Logic Design-Lab Manual.indd 50 8/17/2012 12:34:34 PM

LD Lab Manual 51

Dene module (i.e. Dene input and output ports).

Click Next and Finish.

Logic Design-Lab Manual.indd 51 8/17/2012 12:34:34 PM

52 Logic Design

Type VHDL code.

Save VHDL code.

Logic Design-Lab Manual.indd 52 8/17/2012 12:34:35 PM

LD Lab Manual 53

Click on Implement Design in Processes Synthesize-XST click on Check Syntax.

If there are no errors in VHDL code, then we can nd a tick mark in Check Syntax shown

below:

Above explained steps are for Synthesis.

Logic Design-Lab Manual.indd 53 8/17/2012 12:34:35 PM

54 Logic Design

Step 2: The following steps hold good for Simulation.

Go to Sources for Click on Behavioral Simulation.

Then click on fulladder.

Go to Processes and double click on Xilinx ISE Simulator. Then double click Simulate

Behavioral Model. Here U=undened.

Right click on input a go to Force.

Logic Design-Lab Manual.indd 54 8/17/2012 12:34:36 PM

LD Lab Manual 55

Then change the value U to 0 or 1.

Change U to 0 or 1 then click ok. Similarly change values of b and c to 0 or 1. Check for all

possible combinations of abc=000 to 111.

Click Run after a,b,c values are dened.

Logic Design-Lab Manual.indd 55 8/17/2012 12:34:36 PM

56 Logic Design

Output waveform for abc=000 then s=sum=0 and cout=carry=0.

Output waveform for abc=001 then s=sum=1 and cout=carry=0.

Output waveform for abc=000 to 111.

3.b Write a Verilog / VHDL code for a D Flip-Flop with positive edge triggering. Simulate

and verify its working.

Logic Design-Lab Manual.indd 56 8/17/2012 12:34:36 PM

LD Lab Manual 57

Truth table for D ip-op

D Q Qbar

0 0 1

1 1 0

VHDL code for D ip-op

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity dff is

Port ( clk,d : in STD_LOGIC;

q ,qbar: out STD_LOGIC);

End dff;

Architecture Behavioral of dff is

Begin

Process(clk)

Begin

if(clkevent and clk=1) then // Rising edge or write as: if(rising_edge(clk)) then

q<=d;

qbar<=not(d);

end if ;

end process;

End Behavioral;

Logic Design-Lab Manual.indd 57 8/17/2012 12:34:36 PM

58 Logic Design

STEPS TO OBTAIN OUTPUT WAVEFORM FOR D ip-op:

Step 1: Synthesis for D ip-op: Synthesis step is left as an exercise to the reader and follows

the same steps as explained in 8:1 mux and full adder programs.

Step 2: After Synthesis/Implementation go to Sources for change Synthesis/Implementation

to Behavioral Simulation. Go to Processes ModelSim Simulator.

Dene values for clk and d. To force value for clk, click on Clock.

Logic Design-Lab Manual.indd 58 8/17/2012 12:34:36 PM

LD Lab Manual 59

Then click OK.

Force value of d to 0 or 1. According to truth table, output q follows d i.e if d=0 then q is also

equal to 0 (therefore qbar=1) and if d=1 then q is also equal to 1 (therefore qbar=0).

Logic Design-Lab Manual.indd 59 8/17/2012 12:34:37 PM

60 Logic Design

Force value for d=0 or 1.

Then click Run. Here we can see that if d=0 then q=0 and qbar=1.

Then change i.e. forced to 1 and observe changes in q. When d=1 then q=1 and qbar=0.

Logic Design-Lab Manual.indd 60 8/17/2012 12:34:37 PM

LD Lab Manual 61

4.b Write a Verilog / VHDL code for mod 8 up-counter. Simulate and verify its working.

Truth table for mod 8 up-counter

Count Q2 Q1 Q0

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

VHDL code for mod 8 up-counter

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity Counter is

Port ( clk: in STD_LOGIC;

q : inout STD_LOGIC_vector(2 downto 0):=000);

End Counter;

Architecture Behavioral of Counter is

Begin

Process(clk)

Begin

if(clkevent and clk=1) then

q<=q+1;

end if;

end process;

End Behavioral;

Logic Design-Lab Manual.indd 61 8/17/2012 12:34:37 PM

62 Logic Design

Step 1: Synthesis.

Step 2:After Synthesis/Implementation go to Sources for change Synthesis/Implementation

to Behavioral Simulation. Go to Processes ModelSim Simulator.

Dene value for clk.

Next Dene Clock.

Logic Design-Lab Manual.indd 62 8/17/2012 12:34:37 PM

LD Lab Manual 63

Then click Run. For the 1

st

clk pulse q changes from 000 to 001. Then click run again. Here q

changes from 001 to 010. Click on Run and verify the truth table.

The counter here counts from 000001010011100101110111. This is mod-8

counter.

Output waveform when Q2 Q1 Q0 =011.

Similarly check for mod-5 counter.

Logic Design-Lab Manual.indd 63 8/17/2012 12:34:37 PM

64 Logic Design

Truth table for mod 5 up-counter

Count Q0 Q1 Q2

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

VHDL code for mod 5 up-counter

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity Counter is

Port ( clk: in STD_LOGIC;

q : inout STD_LOGIC_vector(2 downto 0):=000);

End Counter;

Architecture Behavioral of Counter is

Begin

Process(clk)

Begin

if(clkevent and clk=1) then

q<=q+1;

if(q<=101) then

q<=000;

end if;

end if;

end process;

end Behavioral;

Logic Design-Lab Manual.indd 64 8/17/2012 12:34:38 PM

LD Lab Manual 65

Step 1: Synthesis.

Step 2:After Synthesis/Implementation go to Sources for change Synthesis/Implementation

to Behavioral Simulation. Go to Processes ModelSim Simulator.

5.b Write a Verilog / VHDL code for Switched tail counter. Simulate and verify its

working. (Johnson Counter)

FUNCTION TABLE FOR JOHNSON COUNTER/ SWITCHED TAIL COUNTER

clk Q3 Q2 Q1 Q0

0

1

2

3

4

5

6

7

0

1

1

1

1

0

0

0

0

0

1

1

1

1

0

0

0

0

0

1

1

1

1

0

0

0

0

0

1

1

1

1

Repeats

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

Entity jcounter is

Port ( clk : in STD_LOGIC;

q : inout STD_LOGIC_vector(3 downto 0):=0000);

End jcounter;

Architecture Behavioral of jcounter is

Begin

Process(clk)

Begin

if(clkevent and clk=1) then

q<= not(q(0)) & (q(3 downto 1));

end if;

end process;

end Behavioral;

Logic Design-Lab Manual.indd 65 8/17/2012 12:34:38 PM

66 Logic Design

Step 1: Synthesis.

Step 2:After Synthesis/Implementation go to Sources for change Synthesis/Implementation

to Behavioral Simulation. Go to Processes ModelSim Simulator.

Dene value for clk.

Here Dene Clock.

Logic Design-Lab Manual.indd 66 8/17/2012 12:34:38 PM

LD Lab Manual 67

Then click OK Run. Initially q=0000. For the 1

st

clk pulse q changes from 0000 to 1000. Then

click run again. Here q changes from 1000 to 1100. Click on Run and verify the truth table.

Logic Design-Lab Manual.indd 67 8/17/2012 12:34:38 PM

68 Logic Design

VERILOG CODE

1. Verilog code for 8-to-1 multiplexer

module mux8to1(a, b, c, d,e,f,g,h s, out);

input a, b, c, d,e,f,g,h;

input [2:0] s;

output out;

reg out;

// used in procedural statement

always @ (s or a or b or c or d or e or f or g or h)

case (s)

3b 000: out = a;

3b 001: out = b;

3b 010: out = c;

3b 011: out = d;

3b 100: out = e;

3b 101: out = f;

3b 110: out = g;

3b 111: out = h;

endcase

endmodule

Logic Design-Lab Manual.indd 68 8/17/2012 12:34:38 PM

LD Lab Manual 69

2. Verilog code for Full Adder

module adder (output carryOut, sum, input aInput, bInput, carryIn);

input input aInput, bInput, carryIn;

ouput carryOut, sum;

assign sum = aInput ^ bInput ^ carryIn;

carryOut = (aInput & bInput) | (bInput & carryIn) | (aInput & carryIn);

endmodule

3. Verilog code for D ip-op

module Dipop(D, Clk, Q, Qbar);

input D, Clk;

output Q, Qbar;

reg Qint;

// always is a procedural construct

// any assignment may be made only to registers

always @(posedge Clk) Qint <= D;

assign Q = Qint;

assign Qbar = ~Qint;

endmodule

4. Verilog Code for mod 8 UP Counter

module counter (C, CLR, Q);

input C, CLR;

output [2:0] q;

reg [2:0] q;

always @ (posedge C or posedge CLR)

begin

if (CLR)

q = 3b000;

else

q = q + 1b1;

end

endmodule

Logic Design-Lab Manual.indd 69 8/17/2012 12:34:38 PM

70 Logic Design

5. Verilog Code for Johnson Counter

module JC(clk,rst, en, q);

input clk, rst, en;

output[3:0] q;

reg[3:0] q;

always@(posedge clk)

begin

if(rst)

assign q=4b0001;

else if(en)

assign q={~q[0],q[3],q[2],q[1]};

end

endmodule

Example

Write Verilog code for 2 bit magnitude comparator.

Behavioral Example: 2 bit magnitude comparator

module comparator (a_greater, b_greater, equal, a, b);

input a, b;

output a_greater, b_greater, equal;

reg a_greater, b_greater, equal;

always @(a or b) // either a or b changes

begin

if (a > b)

begin

a_greater = 1;

b_greater = 0;

equal = 0;

end

if (a<b)

begin

a_greater = 0;

b_greater = 1;

equal = 0;

Logic Design-Lab Manual.indd 70 8/17/2012 12:34:38 PM

LD Lab Manual 71

end

if (a==b)

begin

a_greater = 0;

b_greater = 0;

equal = 1;

end

end

endmodule

2 bit magnitude comparator using conditional assignment:

module comparator (a_greater, b_greater, equal, a, b);

input a, b;

output a_greater, b_greater, equal;

assign a_greater = (a > b) ? 1 : 0;

assign b_greater = (a < b) ? 1 : 0;

assign equal = (a==b) ? 1 : 0;

endmodule

Logic Design-Lab Manual.indd 71 8/17/2012 12:34:39 PM

Potrebbero piacerti anche

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Control Electronics For Semiconductor Spin QubitsDocumento15 pagineControl Electronics For Semiconductor Spin QubitsiviNessuna valutazione finora

- MTE 3105 - AD and DADocumento13 pagineMTE 3105 - AD and DAshafin2031010Nessuna valutazione finora

- The R-2R and C-2C Ladders: A Circuit For All SeasonsDocumento6 pagineThe R-2R and C-2C Ladders: A Circuit For All SeasonsMuhammad YousafNessuna valutazione finora

- A Presentation On: Digital To Analog Conversion (DAC)Documento31 pagineA Presentation On: Digital To Analog Conversion (DAC)KAMARUDHEEN KPNessuna valutazione finora

- DATA CONVERTER AND CONTROL SYSTEM LAB MANUAL EXPERIMENTSDocumento45 pagineDATA CONVERTER AND CONTROL SYSTEM LAB MANUAL EXPERIMENTSSavita Kiran BNessuna valutazione finora

- 4-Bit DAC Design and ComparisonDocumento5 pagine4-Bit DAC Design and ComparisonAnonymous eWMnRr70qNessuna valutazione finora

- Ldica Course Info Sheet and Question BankDocumento28 pagineLdica Course Info Sheet and Question BankDr.B.Krishna KumarNessuna valutazione finora

- VLSI Lab Manual PART-B, VTU 7th Sem KIT-TipturDocumento64 pagineVLSI Lab Manual PART-B, VTU 7th Sem KIT-Tipturpramodkumar_sNessuna valutazione finora

- Lesson Plan Analog and Integrated CircuitDocumento14 pagineLesson Plan Analog and Integrated CircuitSriramNessuna valutazione finora

- RMK College Linear Integrated Circuits Course Delivery PlanDocumento26 pagineRMK College Linear Integrated Circuits Course Delivery Plansriramachandran2011Nessuna valutazione finora

- Unit - 5 8051 Interfacing Andapplications Interfacing of 8051with: Analog Sensors, Keypad & LCD Display, ADC, DAC, DC Motor. LCD InterfacingDocumento31 pagineUnit - 5 8051 Interfacing Andapplications Interfacing of 8051with: Analog Sensors, Keypad & LCD Display, ADC, DAC, DC Motor. LCD InterfacingNusret YılmazNessuna valutazione finora

- Analog-to-Digital and Digital-to-Analog ConversionsDocumento20 pagineAnalog-to-Digital and Digital-to-Analog ConversionsArif HassanNessuna valutazione finora

- Basic Electronics:: Carnegie Mellon Lab ManualDocumento145 pagineBasic Electronics:: Carnegie Mellon Lab ManualPalak AriwalaNessuna valutazione finora

- DAC0830 - DAC0832 8-Bit ΜP Compatible, Double-Buffered D to a Converters-NATIONALDocumento25 pagineDAC0830 - DAC0832 8-Bit ΜP Compatible, Double-Buffered D to a Converters-NATIONALKrista TranNessuna valutazione finora

- Analog-To-Digital Conversion Btech IIIDocumento50 pagineAnalog-To-Digital Conversion Btech IIILisa BhagatNessuna valutazione finora

- ECE3073 P7 Analogue AnswersDocumento5 pagineECE3073 P7 Analogue AnswerskewancamNessuna valutazione finora

- A/D and D/A Conversion: Cosimo Carriero Analog Dialogue Seminar November 2011Documento107 pagineA/D and D/A Conversion: Cosimo Carriero Analog Dialogue Seminar November 2011luc_eluaniNessuna valutazione finora

- Module No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathDocumento32 pagineModule No: 05 Interfacing 8051 To LCD: Course Coordinator:Prof - Mahesh P.YanagimathUday shankar B LNessuna valutazione finora

- II - II Linear Integrated Circuit Analysis Course Plan PDFDocumento9 pagineII - II Linear Integrated Circuit Analysis Course Plan PDFshivgnitNessuna valutazione finora