Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

MPC561PB/D Rev. 1, December 2001

Caricato da

parksungjinDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

MPC561PB/D Rev. 1, December 2001

Caricato da

parksungjinCopyright:

Formati disponibili

MPC561PB/D

MOTOROLA Rev. 1, December 2001

SEMICONDUCTOR

PRODUCT BRIEF

MPC561/MPC562

MPC563/MPC564

Product Brief

MPC561/MPC562 / MPC563/MPC564 RISC MCU

Including Peripheral Pin Multiplexing with

Flash and Code Compression Options

Features

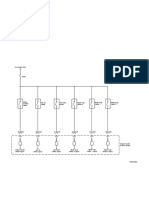

The MPC561/MPC562 / MPC563/MPC564 are members of the Motorola MPC500 RISC Microcontroller

family. As shown in the block diagram, they are composed of:

• High performance CPU system

— High performance core

• Single issue integer core

• Compatible with PowerPC instruction set architecture

• Precise exception model

• Floating point

• Extensive system development support

— On-chip watchpoints and breakpoints

— Program flow tracking

— Background debug mode (BDM)

— IEEE-ISTO Nexus 5001-1999 Class 3 Debug Interface

— MPC500 system interface (USIU, BBC, L2U)

— Fully static design

— Four major power saving modes

• On, doze, sleep, deep-sleep and power-down

— 32-Kbyte static RAM (CALRAM)

— 512-Kbyte flash (UC3F) on MPC563/MPC564

— General-purpose I/O support

• On address (24) and data (32) pins

• 16 GPIO in MIOS14

• Many peripheral pins can be used as GPIO when not used as primary functions

• 2.6-V outputs on external bus pins

• PPM (peripheral pin multiplexing with parallel-to-serial driver) module

• Available in package or die

— Plastic ball grid array (PBGA) packaging

Key Feature Details

MPC500 System Interface (USIU)

• System configuration and protection features:

— Periodic-interrupt timer

— Bus monitor

— Software watchdog timer

— Real-time clock (RTC)

This document contains information on a new product. Specifications and

information herein are subject to change without notice.

© MOTOROLA 2001, All Rights Reserved

— Decrementer

— Time base

• Clock synthesizer

• Power management

• Reset controller

• External bus interface that tolerates 5-V inputs, provides 2.6-V outputs and supports multiple-mas-

ter designs

• Enhanced interrupt controller that supports up to eight external and 40 internal interrupts, simpli-

fies the interrupt structure and decreases interrupt processing time

• USIU supports dual mapping to map part of one internal/external memory to another external

memory

• USIU supports dual mapping of flash on MPC563 and MPC564 to move part of internal flash mem-

ory to external bus for development

• External bus, supporting non-wraparound burst for instruction fetches, with up to 8 instructions per

memory cycle

Burst Buffer Controller (BBC) Module

• Support for enhanced interrupt controller (EIC)

• Support for enhanced exception table relocation feature

• Branch target buffer

• Contains 2-Kbytes of decompression RAM (DECRAM) for code compression. This RAM may also

be used as general-purpose RAM when code compression feature not used.

Flexible Memory Protection Unit

• Flexible memory protection units (MPU) in BBC and L2U

• Default attributes available in one global entry

• Attribute support for speculative accesses

• Up to eight memory regions are supported, four for data and four for instructions

Memory Controller

• Four flexible chip selects via memory controller

• 24-bit address and 32-bit data buses

• 4-Kbyte to one 16-Mbyte (data) or four-Gbyte (instruction) region size support

• Supports enhanced external burst

• Up to eight-beat transfer bursts, two-clock minimum bus transactions

• Use with SRAM, EPROM, flash and other peripherals

• Byte selects or write enables

• 32-bit address decodes with bit masks

• Four regions

512-Kbytes of CDR3 Flash EEPROM Memory (UC3F) – MPC563 Only

• One 512-Kbyte module

• Page read mode

• Block (64 Kbytes) erasable

• External 4.75- to 5.25-V VFLASH power supply for program, erase, and read operations

32-Kbyte static RAM (CALRAM)

• Composed of one 32-Kbyte CALRAM module

— 28-Kbyte static RAM

— 4-Kbyte calibration (overlay) RAM feature that allows calibration of flash-based constants

• Eight 512-byte overlay regions

• One clock fast accesses

• Two-clock cycle access option for power saving

• Keep-alive power (VDDSRAM) for data retention

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

2

General-Purpose I/O Support

• 24 Address pins and 32 data pins can be used for general-purpose I/O in single-chip mode

• 16 GPIO in MIOS14

• Many peripheral pins can be used as GPIO when not used as primary functions

• 2.6-V outputs on external bus pins

• 5-V outputs with slew rate control

NEXUS Debug Port (Class 3)

• Compliant with Class 3 of the IEEE-ISTO Nexus 5001-1999

• Program trace via branch trace messaging (BTM)

• Data trace via data write messaging (DWM) and data read messaging (DRM)

• Ownership trace via ownership trace messaging (OTM)

• Run-time access to on-chip memory map and MPC5xx special purpose registers (SPRs) via the

READI read/write access protocol

• Watchpoint messaging via the auxiliary port

• Reduced-port mode (1 MDI, 2 MDO) or full-port mode (2 MDI. 8 MDO)

• All features configurable and controllable via the auxiliary port

• Security features for production environment

• Supports the RCPU debug mode via the auxiliary port

• READI module can be reset independent of system reset

Integrated I/O System

Two Time Processor Units (TPU3)

• True 5-V I/O

• Two time processing units (TPU3) with16 channels each

• Each TPU3 is a micro-coded timer subsystem

• Eight-Kbytes of dual port TPU RAM (DPTRAM) shared by two TPU3 modules for TPU micro-code

22-Channel Modular I/O System (MIOS14)

• Six modulus counter sub-modules (MCSM)

• 10 double-action sub-modules (DASM)

• 12 dedicated PWM sub-modules (PWMSM)

• One MIOS14 16-bit parallel port I/O sub-modules (MPIOSM)

Two Enhanced Queued Analog-to-Digital Converter Modules (QADC64E)

• Two queued analog-to-digital converter modules (QADC64_A, QADC64_B) providing a total of 32

analog channels

• 16 analog input channels on each QADC64E module using internal multiplexing

• Directly supports up to four external multiplexers

• Up to 41 total input channels on the two QADC64E modules with external multiplexing

• Software configurable to operate in Enhanced or Legacy (MPC555 compatible) mode

• Unused analog channels can be used as digital input/output pins

— GPIO on all channels in Enhanced mode

• 10-bit A/D converter with internal sample/hold

• Typical conversion time of less than 5 µs (>200 K samples/second)

• Two conversion command queues of variable length

• Automated queue modes initiated by:

— External edge trigger

— Software command

— Periodic/interval timer within QADC64E module, that can be assigned to both queue 1 and 2

— External Gated trigger (queue 1only)

• 64 result registers

— Output data is right- or left-justified, signed or unsigned

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

3

• Alternate reference input (ALTREF), with control in the conversion command word (CCW)

Three CAN 2.0B Controller (TouCAN) Modules

• Three TouCAN modules (TOUCAN_A, TOUCAN_B, TOUCAN_C)

• Each TouCAN provides the following features:

— 16 message buffers each, programmable I/O modes

— Maskable interrupts

— Independent of the transmission medium (external transceiver is assumed)

— Open network architecture, multi-master concept

— High immunity to EMI

— Short latency time for high-priority messages

— Low-power sleep mode, with programmable wake-up on bus activity

— TOUCAN_C pins are shared with MIOS14 GPIO or QSMCM

Queued Serial Multi-Channel Module (QSMCM)

• One queued serial module with one queued SPI and two SCIs (QSMCM)

• QSMCM matches full MPC555 QSMCM functionality

• Queued SPI

— Provides full-duplex communication port for peripheral expansion or inter-processor commu-

nication

— Up to 32 preprogrammed transfers, reducing overhead

— Synchronous serial interface with baud rate of up to system clock / 4

— Four programmable peripheral-selects pins:

— Support up to 16 devices with external decoding

— Support up to eight devices with internal decoding

— Special wrap-around mode allows continuous sampling of a serial peripheral for efficient inter-

facing to serial analog-to-digital (A/D) converters

• SCI

— UART mode provides NRZ format and half- or full-duplex interface

— 16 register receive buffers and 16 register transmit buffers on one SCI

— Advanced error detection and optional parity generation and detection

— Word-length programmable as eight or nine bits

— Separate transmitter and receiver enable bits, and double buffering of data

— Wake-up functions allow the CPU to run uninterrupted until either a true idle line is detected,

or a new address byte is received

Peripheral Pin Multiplexing (PPM) PPM

• Synchronous serial interface between the microprocessor and an external device

• Four internal parallel data sources can be multiplexed through the PPM

— TPU3_A: 16 channels

— TPU3_B: 16 channels

— MIOS14: 12 PWM channels, 4 MDA channels

— Internal GPIO: 16 general-purpose inputs, 16 general-purpose outputs

• Software configurable stream size

• Software configurable clock (TCLK) based on system clock

• Software selectable clock modes (SPI mode and TDM mode)

• Software selectable operation modes

— Continuous mode

— Start-transmit-receive (STR) mode

• Software configurable internal modules interconnect (shorting)

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

4

MPC561/MPC562 / MPC563/MPC564 Optional Features

The following are optional features of the MPC561/MPC562 / MPC563/MPC564:

• 56-MHz operation (40 MHz is default)

• Code compression supported on the MPC562 and the MPC564

— Compression reduces instruction memory requirements by 40-50%

— Compression optimized for automotive (non-cached) applications

• 512 Kbytes flash (available on the MPC563/MPC564 only)

— Single array

— Page mode read

— Block (64 Kbytes) erasable

— External 4.75- to 5.25-V VFLASH program, erase, and read power supply

512 Kbytes

JTAG Flash

(on MPC563/

MPC564 only)

Burst

Buffer

Controller U-BUS

E-BUS

USIU

MPC5xx

READI

Core

+

FP

L2U

Int.

L-BUS

32-Kbyte CALRAM

28-Kbyte

SRAM

(No Overlay)

4-Kbyte Overlay

UIMB

QADC64 QADC64 QSMCM PPM

I/F

IMB3

8-Kbyte Tou Tou Tou

TPU3 TPU3 MIOS14

DPTRAM CAN CAN CAN

Figure 1 MPC561/MPC562 / MPC563/MPC564 Block Diagram

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

5

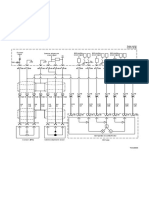

0x00 0000

UC3F Flash*

512 Kbytes

0x07 FFFF 0x2F C000

0x08 0000

USIU Control Registers

Reserved for Flash

2,605 Kbytes

UC3F Control 0x2F C800

Registers*

0x2F 7FFF

0x2F 8000 BBC DECRAM 2 Kbytes

0x30 0000

0x2F 8800 Reserved for BBC DPTRAM Control (32 bytes)

0x2F A000 BBC CONTROL 0x30 0020

0x2F BFFF Reserved (8160 bytes)

0x2F C000

USIU & Flash Control

0x2F FFFF 16 Kbytes

0x30 2000

0x30 0000 DPTRAM (8 Kbytes)

UIMB I/F & IMB

Modules

32 Kbytes TPU3_A (1 Kbyte)

0x30 4000

0x30 7FFF

TPU3_B (1 Kbyte)

0x30 4400

0x30 8000 Reserved for IMB

491 Kbytes QADC64_A (1 Kbyte)

0x30 4800

0x37 FFFF

0x38 0000 0x30 4C00

CALRAM/ QADC64_B (1 Kbyte)

READI Control

256 bytes QSMCM (1 Kbyte)

0x30 5000

0x38 00FF

0x38 0100 Reserved (L-bus Control) 0x30 5400

Reserved (2 Kbytes)

0x38 3FFF ~32 Kbytes

0x38 4000 PPM (64 bytes) 0x30 5C00

Reserved (960 bytes) 0x30 5C80

Reserved (L-bus Mem)

464 Kbytes MIOS14 (4 Kbytes) 0x30 6000

0x3F 7FFF

0x3F 8000

CALRAM TOUCAN_A (1 Kbyte) 0x30 7000

32 Kbytes

0x3F F000 TOUCAN_B (1 Kbyte)

0x30 7400

0x3F FFFF 4-Kbyte Overlay Section TOUCAN_C (1 Kbyte) 0x30 7800

Reserved (896 bytes) 0x30 7C00

*NOTE: Only available on MPC563/MPC564. UIMB Registers 0x30 7F80

(128 bytes) 0x30 7FFF

Figure 2 MPC561 / MPC563 Internal Memory Map

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

6

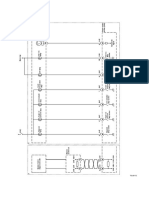

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

A VDD VSS VSS VSS A_TPUCH VSSA VRL A_AN3_A A_AN51_P A_AN55_ A_AN56_P B_AN0_AN B_AN48_ B_AN52_M B_AN56_P VSS ETRIG2_ VSS VSS VDD VSS A

A_TPUCH3 A_TPUCH7 11 A_TPUCH15 NZ_PQB3 QB7 PQA3 QA4 W_PQB0 PQB4 A0_PQA0 QA4 PCS7 MDA13 MDA28

A_AN54_

A_TPUCH ETRIG1_

B VSS VDD VSS VSS A_TPUCH2 A_TPUCH6 A_TPUCH14 VSSA ALTREF A_AN2_A A_AN50_P MA2_PQ A_AN58_P B_AN1_AN B_AN49_ B_AN53_M B_AN57_P VSS MDA14 MDA29 VSS VDD VSS QVDDL B

10 PCS6

NY_PQB2 QB6 A2 QA6 X_PQB1 PQB5 A1_PQA1 QA5

A_AN0_A A_AN52_

A_TPUCH NW_PQB A_AN48_P MA0_PQ A_AN59_P B_AN2_AN B_AN50_ B_AN54_M B_AN58_P

C VSS VSS VDD VSS A_TPUCH1 A_TPUCH4 A_TPUCH12 NVDDL VRH VDDH MDA11 MDA15 VDDH VDD VSS QVDDL VSS C

8 0 QB4 A0 QA7 Y_PQB2 PQB6 A2_PQA2 QA6

A_AN53_

A_TPUCH

D VSS VSS VSS VDD VSS A_TPUCH5 A_TPUCH13 NVDDL VDDA A_AN1_A A_AN49_P MA1_PQ A_AN57_P B_AN3_AN B_AN51_ B_AN55_P B_AN59_P VDDH MDA12 MDA27 VDD VSS QVDDL VSS VSS D

9 NX_PQB1 QB5 A1 QA5 Z_PQB3 PQB7 QA3 QA7

E VDDH VSS VSS VSS QVDDL VSS VSS VSS E

B_T2CLK_P A_T2CLK_ A_TPUCH MPWM0_MD

F QVDDL VDDH MDA30 MDA31 F

CS4 PCS5 0 I1

B_TPUCH1 B_TPUCH B_TPUCH1 MPWM1_MD MPWM3_PP MPWM2_PP

G B_TPUCH12

3 14 5

MPC561 / MPC563 Ball Map O2

MPWM16

M_RX1 M_TX1

G

B_TPUCH B_TPUCH1 MPWM17_M MPWM18_MD MPWM19_M MPIO32B5_

H B_TPUCH8 B_TPUCH9

10 1 (As viewed from top, through the package and silicon) DO3 O6 DO7 MDO5

H

MPIO32B6_

B_TPUCH MPIO32B7_MP MPIO32B8_ MPIO32B9_

J B_TPUCH4 B_TPUCH5 B_TPUCH7 MPWM4_MD J

6 WM5 MPWM20 MPWM21

O6

B_TPUCH MPIO32B12_ MPIO32B11_C MPIO32B10_ MPIO32B13_

K B_TPUCH0 B_TPUCH1 B_TPUCH3 K

2 C_CNTX0 _CNRX0 PPM_TSYNC PPM_TCLK

JCOMP_RS TCK_DSCK VF0_MPIO32 VF1_MPIO32B MPIO32B15_ MPIO32B14_

L B_CNRX0 B_CNTX0 VSS VSS VSS VSS VSS VSS L

TI_B _MCKI B0_MDO1 1_MCKO PPM_TX0 PPM_RX0

VFLS0_MPIO

TDI_DSDI_ TMS_EVTI VDDSRA TDO_DSD VF2_MPIO32B VFLS1_MPIO

M VSS VSS VSS VSS VSS VSS A_CNTX0 32B3_MSEO M

MDI0 _B M O_MDO0 2_MSEI_B 32B4

_B

IRQ3_B_KR

SGPIOC6_

_B_RETRY IWP0_VFL IWP1_VFL PCS2_QGPI PCS0_SS_B_

N FRZ_PTR_ VSS VSS VSS VSS VSS VSS PCS1_QGPIO1 A_CNRX0 N

_B_SGPIO S0 S1 O2 QGPIO0

B

C3

IRQ2_B_C

IRQ0_B_S IRQ1_B_R

IRQ4_B_AT R_B_SGPI SCK_QGPIO MISO_QGPI PCS3_QGPI

P GPIOC0_ SV_B_SG VSS VSS VSS VSS VSS VSS MOSI_QGPIO5 P

2_SGPIOC4 OC2_MDO 6 O4 O3

MDO4 PIOC1

5_MTS

SGPIOC7_I

BB_B_VF2 BG_B_VF BR_B_VF1 RXD1_QGPI TXD2_QGPO2 TXD1_QGPO PULL-SEL

R RQOUT_B_ VSS VSS VSS VSS VSS VSS R

_IWP3 0_LWP1 _IWP2 1 _C_CNTX0 1

LWP0

WE_B_AT WE_B_AT RXD2_QGPI

T WE_B_AT0 WE_B_AT1 VSS VSS VSS VSS VSS VSS EPEE BOEPEE VDDH T

2 3 2_C_CNRX0

U CS0_B CS1_B CS2_B CS3_B CLKOUT VSSF VDDF VFLASH U

ENGCLK_BU

V RD_WR_B OE_B TEA_B TSIZ0 VDD EXTCLK VSS V

CLK

PORESET_B

W TSIZ1 TS_B TA_B BDIP_B HRESET_B SRESET_B KAPWR W

_TRST_B

BI_B_STS_ ADDR_SG ADDR_SG IRQ7_B_MODC RSTCONF_B

Y BURST_B NVDDL VDDSYN Y

B PIOA12 PIOA11 K3 _TEXP

AA VSS VSS VSS QVDDL VSS VSS VSS XFC AA

AB VSS VSS QVDDL VSS QVDDL VSS VSS VSSSYN AB

ADDR_SGP ADDR_SG ADDR_SGPI ADDR_SG ADDR_S DATA_SG DATA_SG DATA_SG DATA_SG DATA_SGP DATA_SG DATA_S

AC VSS QVDDL VSS NVDDL VSS NVDDL NVDDL NVDDL VSS VDD VSS QVDDL VSS EXTAL AC

IOA10 PIOA18 OA20 PIOA23 GPIOA26 PIOD1 PIOD5 PIOD7 PIOD9 IOD11 PIOD12 GPIOD14

IRQ5_B_S

ADDR_SG ADDR_SGPI ADDR_SG ADDR_SGP ADDR_S ADDR_SG DATA_SG DATA_SG DATA_SGP DATA_SG DATA_SGP DATA_SG DATA_SGPI DATA_S

AD QVDDL VSS NVDDL VSS VSS QVDDL GPIOC5_M VSS VDD VSS QVDDL XTAL AD

PIOA13 OA16 PIOA19 IOA21 GPIOA24 PIOA25 PIOD0 PIOD28 IOD26 PIOD24 IOD22 PIOD13 OD15 GPIOD16

ODCK1

ADDR_SG ADDR_SGPI ADDR_SG ADDR_SGP ADDR_S ADDR_SG DATA_SG DATA_SG DATA_SGP DATA_SG DATA_SGP DATA_SG DATA_SGPI DATA_S

AE VSS NVDDL VSS VSS VSS QVDDL IRQ6_B_M VSS VSS VDD VSS QVDDL AE

PIOA14 OA17 PIOA31 IOA30 GPIOA28 PIOA29 PIOD30 PIOD29 IOD27 PIOD25 IOD23 PIOD21 OD19 GPIOD17

ODCK2

ADDR_SG ADDR_SGPI ADDR_SG ADDR_SGP ADDR_S DATA_SG DATA_SG DATA_SG DATA_SGP DATA_SG DATA_SGP DATA_SG DATA_SGPI DATA_S

AF NVDDL VSS VSS VSS VDDH VSS VDDH VSS VSS VSS VDD VSS AF

PIOA15 OA9 PIOA8 IOA22 GPIOA27 PIOD31 PIOD3 PIOD2 IOD4 PIOD6 IOD8 PIOD10 OD20 GPIOD18

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

NOTE: The flash balls are only available on the MPC563 and MPC564. These are no connect balls on

the MPC561 and MPC562. Flash supplies and inputs are located on the following balls: T23, T24, U24,

U25. U26.

Figure 3 MPC561 / MPC563 Ball Map

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

7

Ordering Information

Table 1 MPC561/562 / MPC563/564

Device Order Part Package Info Temperature Maximum Code

Name Number1 Range Frequency Compression

MPC561 MPC561MZP40 388 PBGA -40 – 125° C 40 MHz No

MPC561 MPC561CZP40 388 PBGA -40 – 85° C 40 MHz No

MPC561 MPC561MZP56 388 PBGA -40 – 125° C 56 MHz No

MPC561 MPC561CZP56 388 PBGA -40 – 85° C 56 MHz No

MPC562 MPC562MZP40 388 PBGA -40 – 125° C 40 MHz Yes

MPC562 MPC562CZP40 388 PBGA -40 – 85° C 40 MHz Yes

MPC562 MPC562MZP56 388 PBGA -40 – 125° C 56 MHz Yes

MPC562 MPC562CZP56 388 PBGA -40 – 85° C 56 MHz Yes

MPC563 MPC563MZP40 388 PBGA -40 – 125° C 40 MHz No

MPC563 MPC563CZP40 388 PBGA -40 – 85° C 40 MHz No

MPC563 MPC563MZP56 388 PBGA -40 – 125° C 56 MHz No

MPC563 MPC563CZP56 388 PBGA -40 – 85° C 56 MHz No

MPC564 MPC564MZP40 388 PBGA -40 – 125° C 40 MHz Yes

MPC564 MPC564CZP40 388 PBGA -40 – 85° C 40 MHz Yes

MPC564 MPC564MZP56 388 PBGA -40 – 125° C 56 MHz Yes

MPC564 MPC564CZP56 388 PBGA -40 – 85° C 56 MHz Yes

NOTES:

1. Add R2 suffix for parts shipped in tape and reel media.

Table 2 lists the documents that provide a complete description of the MPC561/563 and are required

to design properly with the part. Documentation is available from a local Motorola distributor, a Motorola

semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola Semicon-

ductor documentation page on the Internet (the source for the latest information).

Table 2 Available Documentation

Document Number Title

MPC561_3RM/AD MPC561/MPC563 Reference Manual

AN1821/D Exception Table Relocation and Multi-Processor

Address Mapping in the Embedded MPC5XX Family

AN2109/D MPC555 Interrupts.

AN2127/D EMC Guidelines for MPC500-Based Automotive Powertrain Systems

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

8

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

9

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

10

MPC561/MPC563 PRODUCT BRIEF MOTOROLA

11

OnCE, DigitalDNA, and the DigitalDNA logo are trademarks of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty,

representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation

consequential or incidental damages. “Typical” parameters which may be provided in Motorola data sheets and/or specifications can

and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must

be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent

rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems

intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the

failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use

Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers,

employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable

attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or

unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola

and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE JAPAN Home Page

Motorola Literature Distribution Motorola Japan Ltd. http://www.motorola.com/semiconductors

P.O. Box 5405 SPS, Technical Information Center

Denver, Colorado 80217 3-20-1, Minami-Azabu, Minato-ku

1-303-675-2140 Tokyo 106-8573 Japan

1-800-441-2447 81-3-3440-3569

Technical Information Center ASIA/PACIFIC

1-800-521-6274 Motorola Semiconductors H.K. Ltd.

Silicon Harbour Centre

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

852-26668334

Order Number MPC561PB/D

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

Potrebbero piacerti anche

- Semiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionDocumento12 pagineSemiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionVicente AlvarezNessuna valutazione finora

- Semiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionDocumento12 pagineSemiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionAlexandrNessuna valutazione finora

- Freescale Semiconductor MC68376BGVFT25 DatasheetDocumento18 pagineFreescale Semiconductor MC68376BGVFT25 DatasheetAhmed Sherif CupoNessuna valutazione finora

- MC9S08QG8Documento314 pagineMC9S08QG8ANgel GarzaNessuna valutazione finora

- MB90F385 FujitsuMediaDevicesDocumento82 pagineMB90F385 FujitsuMediaDevicesali beheshtaeinNessuna valutazione finora

- Micro Tarjeta TermotronicDocumento301 pagineMicro Tarjeta TermotronicLeonardoNessuna valutazione finora

- Datasheet - HK Mb90m408apf 4289720Documento64 pagineDatasheet - HK Mb90m408apf 4289720Sebastian CorreaNessuna valutazione finora

- MC9S12 D Family: X X X XDocumento28 pagineMC9S12 D Family: X X X Xketab_doostNessuna valutazione finora

- Media DevicesDocumento64 pagineMedia DevicesRik JacobNessuna valutazione finora

- CY8C63x7 - BLE SoCDocumento108 pagineCY8C63x7 - BLE SoCropay61705Nessuna valutazione finora

- Doc9166s PDFDocumento109 pagineDoc9166s PDFWaseem WisalNessuna valutazione finora

- MPC5748G NXPDocumento76 pagineMPC5748G NXPCammy KohNessuna valutazione finora

- MC9S08JM60Documento373 pagineMC9S08JM60Mohamed SaadNessuna valutazione finora

- Mc9s08de60 V2 0 9 2007Documento408 pagineMc9s08de60 V2 0 9 2007LuchazoNessuna valutazione finora

- Datasheet Am3359Documento253 pagineDatasheet Am33591jzksharkNessuna valutazione finora

- RM57L843 Hercules™ Microcontroller Based On The ARM® Cortex®-R CoreDocumento223 pagineRM57L843 Hercules™ Microcontroller Based On The ARM® Cortex®-R CoreEdilsn CruzNessuna valutazione finora

- MB90F562 FujitsuMediaDevicesDocumento91 pagineMB90F562 FujitsuMediaDevicesWee Chuan PoonNessuna valutazione finora

- Am 3358Documento248 pagineAm 3358Henrique Tannús CarvalhoNessuna valutazione finora

- MB90860A FujitsuMediaDevicesDocumento62 pagineMB90860A FujitsuMediaDevicesИван АлексиевNessuna valutazione finora

- Module 1 - 411Documento43 pagineModule 1 - 411رفال الجهنيNessuna valutazione finora

- Cypr S A0013039613 1-3004804Documento79 pagineCypr S A0013039613 1-3004804jose diaz lamedaNessuna valutazione finora

- SPC 58 NH 92 C 5Documento147 pagineSPC 58 NH 92 C 5Alan TorreblancaNessuna valutazione finora

- STM32 F4 Series - High-Performance Cortex-M4 MCU - Brstm32f4Documento14 pagineSTM32 F4 Series - High-Performance Cortex-M4 MCU - Brstm32f4test5001Nessuna valutazione finora

- MB90360E SeriesDocumento60 pagineMB90360E SeriesOlga PlohotnichenkoNessuna valutazione finora

- Datasheet MB90803/F804Documento88 pagineDatasheet MB90803/F804richdushNessuna valutazione finora

- 20 Pagini - 16F877.UnlockedDocumento13 pagine20 Pagini - 16F877.UnlockedMariusNastaseNessuna valutazione finora

- AN1242 HC11 To PSD4XX PSD5XXDocumento20 pagineAN1242 HC11 To PSD4XX PSD5XXEr Mahesh BadanaNessuna valutazione finora

- Manual s3c2440Documento560 pagineManual s3c2440Richard ValdiviaNessuna valutazione finora

- PIC18F6585Documento497 paginePIC18F6585Selim YüksektepeNessuna valutazione finora

- Single-Chip Microcontrollers (AMCU) : in Brief - .Documento31 pagineSingle-Chip Microcontrollers (AMCU) : in Brief - .Ãkshay JainNessuna valutazione finora

- SPC 584 C 70 e 3Documento153 pagineSPC 584 C 70 e 3sajeetverma047Nessuna valutazione finora

- Mc9s08en32 V2 0 9 2007Documento324 pagineMc9s08en32 V2 0 9 2007LuchazoNessuna valutazione finora

- Pic 24 Data SheetDocumento554 paginePic 24 Data SheetLewis LiddellNessuna valutazione finora

- Tms 320 C 5517Documento197 pagineTms 320 C 5517M. S. Shafkat TanjimNessuna valutazione finora

- MC9S08AC32Documento348 pagineMC9S08AC32ginolNessuna valutazione finora

- MPC5643LDocumento136 pagineMPC5643LNavya SreeNessuna valutazione finora

- 32-Bit ARM-Based Microcontrollers: SAM D21E / SAM D21G /SAM D21J SummaryDocumento59 pagine32-Bit ARM-Based Microcontrollers: SAM D21E / SAM D21G /SAM D21J Summaryzbhp zNessuna valutazione finora

- MC9S08DZ128 V1 0 5 2008Documento458 pagineMC9S08DZ128 V1 0 5 2008LuchazoNessuna valutazione finora

- At91sam9 PDFDocumento860 pagineAt91sam9 PDFom90xNessuna valutazione finora

- MC9S08DV60 V2 0 9 2007Documento410 pagineMC9S08DV60 V2 0 9 2007LuchazoNessuna valutazione finora

- dsPIC33CK256MP508-Family-Data-Sheet-DS70005349Documento646 paginedsPIC33CK256MP508-Family-Data-Sheet-DS70005349testtestNessuna valutazione finora

- AM335x DatasheetDocumento197 pagineAM335x DatasheetsitasinanNessuna valutazione finora

- SAM D5x-E5xDocumento2.145 pagineSAM D5x-E5xFernando GómezNessuna valutazione finora

- Stm32h563 MCU DataSheetDocumento275 pagineStm32h563 MCU DataSheetdussault.sNessuna valutazione finora

- Tms 320 F 28069Documento173 pagineTms 320 F 28069AlexisNessuna valutazione finora

- 70005144e 1314001 PDFDocumento501 pagine70005144e 1314001 PDFLuis FernandoNessuna valutazione finora

- MC9S08FL16Documento30 pagineMC9S08FL16Causalia SithaNessuna valutazione finora

- 60001290e PDFDocumento382 pagine60001290e PDFBryanMonangWienerNessuna valutazione finora

- Datasheet PDFDocumento92 pagineDatasheet PDFfraurNessuna valutazione finora

- WPC 8769 LDGDocumento5 pagineWPC 8769 LDGOsman EfendiNessuna valutazione finora

- Please Note That Cypress Is An Infineon Technologies CompanyDocumento72 paginePlease Note That Cypress Is An Infineon Technologies CompanyINFO TVNessuna valutazione finora

- Product Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefDocumento16 pagineProduct Brief: MPC565PB/D Rev. 3, 2/2003 MPC565/MPC566 Product BriefMohamedNessuna valutazione finora

- Am 3517Documento221 pagineAm 3517mudit9_mNessuna valutazione finora

- Microprocessor Architectures and Systems: RISC, CISC and DSPDa EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPValutazione: 4 su 5 stelle4/5 (1)

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Da EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Nessuna valutazione finora

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Da EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Nessuna valutazione finora

- Microprocessor Architectures: RISC, CISC and DSPDa EverandMicroprocessor Architectures: RISC, CISC and DSPValutazione: 5 su 5 stelle5/5 (1)

- Tsjj0175e PDFDocumento1 paginaTsjj0175e PDFThong ChanNessuna valutazione finora

- TSHK0351EDocumento1 paginaTSHK0351EThong ChanNessuna valutazione finora

- Vehicle Speed Sensor Starter RelayDocumento1 paginaVehicle Speed Sensor Starter RelayThong ChanNessuna valutazione finora

- TSWG0082EDocumento1 paginaTSWG0082EThong ChanNessuna valutazione finora

- TSUZ0006EDocumento1 paginaTSUZ0006EThong ChanNessuna valutazione finora

- Tshk0015e PDFDocumento1 paginaTshk0015e PDFThong ChanNessuna valutazione finora

- TSJJ0172EDocumento1 paginaTSJJ0172EThong ChanNessuna valutazione finora

- Tsuz0002e PDFDocumento1 paginaTsuz0002e PDFThong ChanNessuna valutazione finora

- Optimizing engine performanceDocumento1 paginaOptimizing engine performanceThong ChanNessuna valutazione finora

- Tswg0082e PDFDocumento1 paginaTswg0082e PDFThong ChanNessuna valutazione finora

- TSHK0025Documento1 paginaTSHK0025Duy KhaNessuna valutazione finora

- TSUZ0083Documento1 paginaTSUZ0083Duy KhaNessuna valutazione finora

- Tsjj0179e PDFDocumento1 paginaTsjj0179e PDFThong ChanNessuna valutazione finora

- TSUZ0004EDocumento1 paginaTSUZ0004EThong ChanNessuna valutazione finora

- Key engine control components and sensorsDocumento1 paginaKey engine control components and sensorsThong ChanNessuna valutazione finora

- TSJJ0172EDocumento1 paginaTSJJ0172EThong ChanNessuna valutazione finora

- Engine control module (ECM) wiring diagramDocumento1 paginaEngine control module (ECM) wiring diagramThong ChanNessuna valutazione finora

- TSWG0035EDocumento1 paginaTSWG0035EDuy KhaNessuna valutazione finora

- TSJJ0174EDocumento1 paginaTSJJ0174EThong ChanNessuna valutazione finora

- Tsjj0181e PDFDocumento1 paginaTsjj0181e PDFThong ChanNessuna valutazione finora

- TSJJ0173EDocumento1 paginaTSJJ0173EThong ChanNessuna valutazione finora

- TSUZ0002EDocumento1 paginaTSUZ0002EThong ChanNessuna valutazione finora

- TSHK0025Documento1 paginaTSHK0025Duy KhaNessuna valutazione finora

- TSJJ0173EDocumento1 paginaTSJJ0173EThong ChanNessuna valutazione finora

- A A ON OFF Start ON OFF: Key SwitchDocumento1 paginaA A ON OFF Start ON OFF: Key SwitchThong ChanNessuna valutazione finora

- Tsjj0169e PDFDocumento1 paginaTsjj0169e PDFThong ChanNessuna valutazione finora

- Tsjj0175e PDFDocumento1 paginaTsjj0175e PDFThong ChanNessuna valutazione finora

- Engine system component diagramDocumento1 paginaEngine system component diagramThong ChanNessuna valutazione finora

- TSJJ0170EDocumento1 paginaTSJJ0170EThong ChanNessuna valutazione finora

- Engine system component identificationDocumento1 paginaEngine system component identificationThong ChanNessuna valutazione finora

- P2041/P2040 Qoriq Integrated Processor Design Checklist: About This DocumentDocumento47 pagineP2041/P2040 Qoriq Integrated Processor Design Checklist: About This DocumentMuhammet BaykalNessuna valutazione finora

- VHDL Code for Basic Gates: AND, OR, NOTDocumento4 pagineVHDL Code for Basic Gates: AND, OR, NOTArpit MetkarNessuna valutazione finora

- Model CT3/5 MB BOARD change historyDocumento42 pagineModel CT3/5 MB BOARD change historyASDFG21Nessuna valutazione finora

- Arduino Button Shield TutorialDocumento1 paginaArduino Button Shield TutorialarurizaNessuna valutazione finora

- HistoryDocumento31 pagineHistoryLucas BorbuonNessuna valutazione finora

- DP Video Intel-XP 15101 DriversDocumento18 pagineDP Video Intel-XP 15101 DriversRaphael Fagundes LopesNessuna valutazione finora

- Hitachi HD64570 Serial Communications Adaptor User's ManualDocumento469 pagineHitachi HD64570 Serial Communications Adaptor User's ManualMiguel Ángel CoriaNessuna valutazione finora

- MotherboardDocumento4 pagineMotherboardMary Ann BalauitanNessuna valutazione finora

- DMR 800 Installation and Hardware Guide2Documento4 pagineDMR 800 Installation and Hardware Guide2Nishant PandyaNessuna valutazione finora

- CD4541 Programmable TimerDocumento7 pagineCD4541 Programmable TimerluisNessuna valutazione finora

- 3 Bit Synchronous CounterDocumento5 pagine3 Bit Synchronous CounterCHERISMA100% (1)

- Real Time Clock Module Application ManualDocumento47 pagineReal Time Clock Module Application ManualProduccion TAMNessuna valutazione finora

- Introduction To Microcomputer Systems: OutlineDocumento28 pagineIntroduction To Microcomputer Systems: OutlineJay MkNessuna valutazione finora

- Tutorial 05 Half Adder Full AdderDocumento2 pagineTutorial 05 Half Adder Full AdderRishanRulzNessuna valutazione finora

- Ball Bonding Process & Chip Packaging StepsDocumento32 pagineBall Bonding Process & Chip Packaging Stepsapurva guptaNessuna valutazione finora

- Crypto Mining Project Cost AnalysisDocumento3 pagineCrypto Mining Project Cost AnalysisifyNessuna valutazione finora

- Electronics and Communication Department The Lnmiit, Jaipur Digital Circuits and Systems (Code: DCS)Documento4 pagineElectronics and Communication Department The Lnmiit, Jaipur Digital Circuits and Systems (Code: DCS)Ravindra KumarNessuna valutazione finora

- TMS320F206 Digital Signal ProcessorDocumento57 pagineTMS320F206 Digital Signal ProcessorMiguel Ángel CoriaNessuna valutazione finora

- Controllogix® Redundancy System Revision 13: When To Use These Release NotesDocumento16 pagineControllogix® Redundancy System Revision 13: When To Use These Release Notesguruh anindraNessuna valutazione finora

- Exp 2Documento10 pagineExp 2NAFISA ISLAM 1808006Nessuna valutazione finora

- Algorithm To Create Multi Line Display From Two Line LCD DisplayDocumento3 pagineAlgorithm To Create Multi Line Display From Two Line LCD DisplayElins JournalNessuna valutazione finora

- 9 - USART - EEPROM - CCP - Realtime Applications PDFDocumento57 pagine9 - USART - EEPROM - CCP - Realtime Applications PDFSrujan KazipetaNessuna valutazione finora

- AssgnStmt 01Documento1 paginaAssgnStmt 01Abinash sonowalNessuna valutazione finora

- m220 Service ManualDocumento49 paginem220 Service ManualDave SharpNessuna valutazione finora

- Conference Presentation SRAM DesignDocumento22 pagineConference Presentation SRAM DesignDương Tuấn KiệtNessuna valutazione finora

- lm80 nt441 15 - CDocumento103 paginelm80 nt441 15 - CAdhiezzz GamingNessuna valutazione finora

- Deca ChoDocumento9 pagineDeca ChoTARANGITNessuna valutazione finora

- Comparing Registers: MIPS vs. ARM AssemblyDocumento12 pagineComparing Registers: MIPS vs. ARM Assemblyshruti chouhanNessuna valutazione finora

- DLD Lecture 1Documento50 pagineDLD Lecture 1sjbv.hardik582Nessuna valutazione finora

- HC11 ArchitectureDocumento28 pagineHC11 ArchitecturebaabysNessuna valutazione finora