Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Expt. No.5 - TTL Cmos Chts

Caricato da

swatagoda0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

12 visualizzazioni3 pagineExpt. No.5_ttl Cmos Chts

Titolo originale

Expt. No.5_ttl Cmos Chts

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoExpt. No.5_ttl Cmos Chts

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

12 visualizzazioni3 pagineExpt. No.5 - TTL Cmos Chts

Caricato da

swatagodaExpt. No.5_ttl Cmos Chts

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 3

EE 214: Digital Circuits Laboratory

Experiment 5: TTL, CMOS Characteristics and CMOS Logic Gates

PURPOSE

Logic gates are classified not only by their logical functions, but also by their logical families. In any

implementation of a digital system, an understanding of a logic element's physical capabilities and limitations,

determined by its logic family, are critical to proper operation. The purpose of this experiment is to provide an

understanding of some of the characteristics of the transistor-transistor logic (TTL) family and Complementary

Metal Oxide Semiconductor logic (CMOS) family.

Objectives:

1. Observe and plot transfer characteristic of a TTL and CMOS inverter.

2. Measure noise margin of a TTL and CMOS inverter.

3. Measure propagation delay of a CMOS inverter

4. Test simple CMOS logic gate circuits.

Background:

TTL FAMILY

The logic family refers to the general physical realization of a logical element, such as the TTL, emitter-

coupled logic (ECL), or complementary metal-oxide semiconductor (CMOS) logic families. Within each logic

family are one or more logic series that have distinctive characteristics, relative to other series within the same

logic family. For example, in the TTL logic family, there are several logic series: the 74 standard, 74L low-

power, 74H high-speed, 74S standard Schottky, 74LS low-power Schottky series, and 74ALS advanced low-

power Schottky series.

The TTL family was the most widely used logic family for several years, characterized by its relatively high

speed operation. However, it has now been largely replaced by CMOS logic.

The physical representation of the binary logic states in these families are high and low voltages. Assuming

positive logic, in the 74LS TTL family LOW (L) voltages in the range 0 V to 0.8 V are considered to be logic

0, and HIGH (H) voltages in the range 2.0 V to 5.5 V are considered to be logic 1.

CMOS Family

In CMOS technology, both p-type and n-type MOSFETs are used to implement digital circuits e.g., logic

gates. CMOS logic gates have the desirable properties of high noise immunity and low static power

consumption. In this experiment, you will use the CD4007 chip which has 3 NMOS and 3 PMOS transistors to

make simple CMOS gates and test them. The figure below shows the details of CD4007.

Note that V

SS

(pin 7) is connected to ground and V

DD

(pin 14) to 5 V. This requires that, for the PMOS

device (6, 13, 14), pin 14 must be treated as the source terminal, and for the NMOS device (6, 7, 8), pin 7 must

be treated as the source terminal.

Parameters to look for in a logic family:

Noise Margins: The noise margins for an inverter are defined as shown in fig. 1(a).

NM

HIGH

=V

OH

- V

IH

, NM

LOW

=V

IL

- V

OL

Propagation Delays: The propagation delays are defined as shown in fig. 1 (b).

t

pLH

=t2 t1, t

pHL

=t4- t3, t

p

=(t

pLH

+t

pHL

) / 2

Rise and Fall times: The rise time and fall times are defined as shown in fig. 1 (c).

Figure 1 (a) Figure 1 (b)

Figure 1 (c)

1. TTL Inverter gate:

a) Vary the input voltage V

in

from 0 V to 5 V in 0.1 V steps and measure the corresponding V

out

with

DMM.

b) Apply 0-5 V, 2 kHz triangular wave as input at V

in

. You can get this voltage range by adding an offset

to the triangular wave output of the function generator. Now observe the voltage transfer curve

directly on the CRO with the help of XY mode by connecting both the input and output

simultaneously. Note down the values of V

IL

, V

OL

, V

IH

and V

OH

. Calculate the noise margin.

2. CMOS inverter gate:

a) Wire the circuit shown in Fig. 2.Vary the input voltage V

in

from 0 V to 5 V in 0.1 V steps and

measure the corresponding V

out

with a DMM.

b) Apply 0-5 V, 2 kHz triangular wave as input at V

in

. You can get this voltage range by adding an offset

to the triangular wave output of the function generator. Now observe the voltage transfer curve

directly on the CRO with the help of XY mode by connecting both the input and output

simultaneously.

c) Apply 0-5 V, 500 kHz square wave as input. Observe the input and output waveforms on CRO. Find

the rise, fall and propagation time as described in Figs. 1 (b) and (c).

Figure 2: CMOS inverter

3. CMOS NAND and NOR gates: Connect the circuits as shown below. Measure the output voltage at Y for

different combinations of input A and B, e.g., 1 and 0. Here 1 and 0 corresponds to 5 V and 0 V,

respectively.

Figure 3: CMOS NAND and NOR gates

Post Lab work:

1. Plot the transfer curve for the inverter using the data obtained in 1 (a) and 2 (a). Find the noise margins.

2. Compare the noise margin, propagation delay, rise time, and fall time with the values specified in the

datasheet of CD4007.

Potrebbero piacerti anche

- ) ) @Ç!! Rq!!!Y+Tcsf : TotalDocumento6 pagine) ) @Ç!! Rq!!!Y+Tcsf : TotalswatagodaNessuna valutazione finora

- Wireless Lan Fa QDocumento5 pagineWireless Lan Fa QvaikaganoNessuna valutazione finora

- A Tale of Two Bloggers - Free Speech and Privacy in The BlogospherDocumento7 pagineA Tale of Two Bloggers - Free Speech and Privacy in The BlogospherswatagodaNessuna valutazione finora

- Grid Emp Induction ListDocumento1 paginaGrid Emp Induction ListswatagodaNessuna valutazione finora

- Acs Ethics Case Studies v2.12Documento45 pagineAcs Ethics Case Studies v2.12swatagodaNessuna valutazione finora

- 02 ITC571 Bibliography TemplateDocumento4 pagine02 ITC571 Bibliography TemplateVishwanath TinkuNessuna valutazione finora

- Homework 1 KEY Fall 2014 CDA3103Documento2 pagineHomework 1 KEY Fall 2014 CDA3103swatagodaNessuna valutazione finora

- Combinational Circuit Analysis and DesignDocumento25 pagineCombinational Circuit Analysis and DesignPECMURUGANNessuna valutazione finora

- ) ) @Ç!! Rq!!!Y+Tcsf : TotalDocumento6 pagine) ) @Ç!! Rq!!!Y+Tcsf : TotalswatagodaNessuna valutazione finora

- ITC556 Sample Exam + SolutionsDocumento11 pagineITC556 Sample Exam + Solutionsswatagoda60% (5)

- 1Documento23 pagine1narendraNessuna valutazione finora

- FSK TutorialDocumento4 pagineFSK TutorialsatelightNessuna valutazione finora

- Acs Ethics Case Studies v2.12Documento45 pagineAcs Ethics Case Studies v2.12swatagodaNessuna valutazione finora

- Class Notes On Topic 5Documento9 pagineClass Notes On Topic 5swatagodaNessuna valutazione finora

- FSK - Signals and DemodulationDocumento8 pagineFSK - Signals and DemodulationMatthew CarterNessuna valutazione finora

- Tutorial 1 Co Solutions Tit 402Documento14 pagineTutorial 1 Co Solutions Tit 402swatagodaNessuna valutazione finora

- Von Nevmann ModelDocumento23 pagineVon Nevmann ModelVinay ShuklaNessuna valutazione finora

- FSK DesmodDocumento10 pagineFSK DesmodFlashPTNessuna valutazione finora

- CRM PDFDocumento31 pagineCRM PDFprince12321Nessuna valutazione finora

- Nisula - Anna 2Documento33 pagineNisula - Anna 2swatagodaNessuna valutazione finora

- Basics of Data Transmission: Our Objective Is To UnderstandDocumento29 pagineBasics of Data Transmission: Our Objective Is To UnderstandswatagodaNessuna valutazione finora

- Delta 1Documento18 pagineDelta 1mayank_gitsNessuna valutazione finora

- 39Documento4 pagine39swatagodaNessuna valutazione finora

- Introduction To Cloud ComputingDocumento6 pagineIntroduction To Cloud ComputingAanchal JalotaNessuna valutazione finora

- Application: FSK Modulation and Demodulation With The MSP430 MicrocontrollerDocumento34 pagineApplication: FSK Modulation and Demodulation With The MSP430 MicrocontrollerKamal UniyalNessuna valutazione finora

- ICBT Examination ProcedureDocumento6 pagineICBT Examination ProcedureswatagodaNessuna valutazione finora

- Level 5 Unit 02 Information Systems in OrganisationsDocumento8 pagineLevel 5 Unit 02 Information Systems in OrganisationsswatagodaNessuna valutazione finora

- Pneumatic SymbolsDocumento2 paginePneumatic SymbolsBharathprabhu100% (1)

- Design and Manufacturing of Low Cost Pneumatic Pick and Place RobotDocumento3 pagineDesign and Manufacturing of Low Cost Pneumatic Pick and Place RobotswatagodaNessuna valutazione finora

- Base Paper PDFDocumento5 pagineBase Paper PDFVigneshwaran SrinivasanNessuna valutazione finora

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (120)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Electronic Circuits - 1 Unit - 3 Small Signal Analysis of JFET and MOSFET Amplifiers Biasing of Fet Amplifiers Fixed BiasDocumento17 pagineElectronic Circuits - 1 Unit - 3 Small Signal Analysis of JFET and MOSFET Amplifiers Biasing of Fet Amplifiers Fixed BiasMutharasu SNessuna valutazione finora

- Xiner-Xnf15n60t C379741Documento1 paginaXiner-Xnf15n60t C379741Imran AslamNessuna valutazione finora

- DLCA - Practical NO 1Documento23 pagineDLCA - Practical NO 104 Tushar BhadrikeNessuna valutazione finora

- MTJ-Based Nonvolatile 9T SRAM CellDocumento5 pagineMTJ-Based Nonvolatile 9T SRAM CellidescitationNessuna valutazione finora

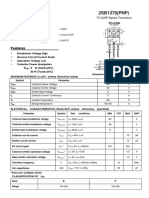

- Silicon PNP Epitaxial Planer Type: TransistorsDocumento1 paginaSilicon PNP Epitaxial Planer Type: Transistorsbusamawan wayanNessuna valutazione finora

- CS 801D PDFDocumento4 pagineCS 801D PDFarnab paulNessuna valutazione finora

- T CH 05Documento18 pagineT CH 05VanarajNessuna valutazione finora

- A Simple Subthreshold Swing Model For SHDocumento7 pagineA Simple Subthreshold Swing Model For SHSwapna BharaliNessuna valutazione finora

- Dif 4Documento1 paginaDif 4GwynbleiddNessuna valutazione finora

- Silicon NPN Power TransistorsDocumento3 pagineSilicon NPN Power TransistorsDaniel ParedesNessuna valutazione finora

- HPS3407 EeDocumento2 pagineHPS3407 EeValdir KoxinhaprNessuna valutazione finora

- University Technology Mara Faculty of Education ED 228: Interfacing With BuzzersDocumento5 pagineUniversity Technology Mara Faculty of Education ED 228: Interfacing With BuzzersHuong TruongNessuna valutazione finora

- F TV Service ManualDocumento9 pagineF TV Service ManualNoel GaskinNessuna valutazione finora

- Teoria Del MosfetDocumento7 pagineTeoria Del Mosfetdarknosferatus666Nessuna valutazione finora

- 1 s2.0 S0168900222005691 MainDocumento5 pagine1 s2.0 S0168900222005691 Main1Nessuna valutazione finora

- Irfb 4020Documento2 pagineIrfb 4020LEWIS RODRIGUEZNessuna valutazione finora

- Data SheetDocumento9 pagineData SheetMd ShitolNessuna valutazione finora

- 2 Sanghun Jeon - SeminarDocumento26 pagine2 Sanghun Jeon - Seminarjeren1228Nessuna valutazione finora

- Experiment No: Aim: Circuit DiagramDocumento3 pagineExperiment No: Aim: Circuit DiagramDharmistha VishwakarmaNessuna valutazione finora

- THGBM 5 G 5 A 1 JbairDocumento1 paginaTHGBM 5 G 5 A 1 JbairONPNessuna valutazione finora

- Short Channel EffectsDocumento27 pagineShort Channel Effectsilg10% (1)

- DMC6040SSD: Complementary Pair Enhancement Mode MosfetDocumento10 pagineDMC6040SSD: Complementary Pair Enhancement Mode MosfetCiro SpanholiNessuna valutazione finora

- KSC5603D NPN Silicon Transistor, Planar Silicon Transistor: FeaturesDocumento5 pagineKSC5603D NPN Silicon Transistor, Planar Silicon Transistor: FeaturesParag IngleNessuna valutazione finora

- DatasheetDocumento1 paginaDatasheetjakob278313Nessuna valutazione finora

- Chapter 4:jfet: Junction Field Effect TransistorDocumento67 pagineChapter 4:jfet: Junction Field Effect TransistorMohammad NasutionNessuna valutazione finora

- Destruction 2. Seahorse Quasi NPN 3. Seahorse Quasi PNP 4. Seahorse XLS5000 5. Seahorse AV-1000sDocumento5 pagineDestruction 2. Seahorse Quasi NPN 3. Seahorse Quasi PNP 4. Seahorse XLS5000 5. Seahorse AV-1000sRoldao AlmeidaNessuna valutazione finora

- 2N2218-2N2219 2N2221-2N2222: High-Speed SwitchesDocumento5 pagine2N2218-2N2219 2N2221-2N2222: High-Speed SwitchesNicolasNessuna valutazione finora

- Monolithic Microwave Integrated Circuit (MMIC) Technology For Space Communications ApplicationsDocumento18 pagineMonolithic Microwave Integrated Circuit (MMIC) Technology For Space Communications ApplicationspratikmevadaNessuna valutazione finora

- 2 SB 1370Documento2 pagine2 SB 1370wilsonNessuna valutazione finora

- Uln 2803 CDocumento22 pagineUln 2803 CJesin KimNessuna valutazione finora