Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

05510122

Caricato da

vishy_2006880 valutazioniIl 0% ha trovato utile questo documento (0 voti)

29 visualizzazioni3 pagineTunneling field-effect transistors have suffered from low ON-current, severe ambipolar behavior, and gradual transition between ONand OFF-states. To address those issues, the authors have proposed hetero-gate-dielectric TFETs. The proposed device enhances ON-current and suppresses ambipolar. Behavior by replacing the source-side gate insulator with a high-k material, which induces a local minimum of the conduction band edge at the tunnel

Descrizione originale:

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoTunneling field-effect transistors have suffered from low ON-current, severe ambipolar behavior, and gradual transition between ONand OFF-states. To address those issues, the authors have proposed hetero-gate-dielectric TFETs. The proposed device enhances ON-current and suppresses ambipolar. Behavior by replacing the source-side gate insulator with a high-k material, which induces a local minimum of the conduction band edge at the tunnel

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

29 visualizzazioni3 pagine05510122

Caricato da

vishy_200688Tunneling field-effect transistors have suffered from low ON-current, severe ambipolar behavior, and gradual transition between ONand OFF-states. To address those issues, the authors have proposed hetero-gate-dielectric TFETs. The proposed device enhances ON-current and suppresses ambipolar. Behavior by replacing the source-side gate insulator with a high-k material, which induces a local minimum of the conduction band edge at the tunnel

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 3

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 57, NO.

9, SEPTEMBER 2010 2317

Hetero-Gate-Dielectric Tunneling

Field-Effect Transistors

Woo Young Choi, Member, IEEE, and Woojun Lee

AbstractA tunneling eld-effect transistor (TFET) is consid-

ered one of the most promising alternatives to a metaloxide

semiconductor eld-effect transistor due to its immunity to

short-channel effects. However, TFETs have suffered from low

ON-current, severe ambipolar behavior, and gradual transition

between ON- and OFF-states. To address those issues, the authors

have proposed hetero-gate-dielectric TFETs. The proposed device

enhances ON-current, suppresses ambipolar behavior, and makes

abrupt ONOFF transition by replacing the source-side gate insu-

lator with a high-k material, which induces a local minimum of

the conduction band edge at the tunneling junction.

Index TermsAmbipolar behavior, gate insulator, hetero-

gate-dielectric, subthreshold swing (SS), tunneling eld-effect

transistor (TFET).

I. INTRODUCTION

R

ECENTLY, various kinds of novel electron devices have

been studied to overcome the scaling limit of MOSFETs

[1][3]. Among them, a tunneling eld-effect transistor (TFET)

is considered one of the most promising alternatives since it

is immune to subthreshold swing (SS) degradation at short-

channel length. On the other hand, it has been reported that

TFETs have low ON-current I

on

, which limits operation speed,

and severe ambipolar behavior, which increases leakage current

I

amb

[4], [5]. Additionally, it is problematic that the SS values

of experimentally demonstrated silicon TFETs are larger than

expected values. In theory, the SS of silicon TFETs can be

reduced smaller than 60 mV/dec at room temperature, which

is the minimal SS of conventional MOSFETs. However, only

a few research groups have succeeded in demonstrating sub-

60-mV/dec SS at room temperature experimentally [6], [7].

Thus, to improve I

on

and SS, a high-k material has been

introduced as a gate insulator [8]. However, using a high-k

material as a gate insulator may increase leakage current I

amb

due to severe ambipolar behavior. To alleviate ambipolar be-

havior, TFETs without gatedrain overlap have been proposed

[9]. However, this approach actually increases drain-to-source

channel length, which signicantly reduces chip density.

In this brief, we have proposed hetero-gate-dielectric TFETs

(HGTFETs) for higher I

on

, lower I

amb

, and smaller SS without

Manuscript received February 9, 2010; revised May 18, 2010; accepted

May 20, 2010. Date of publication July 15, 2010; date of current version

August 20, 2010. This work was supported by the National Research Foun-

dation of Korea, funded by the Ministry of Education, Science and Technology,

under Grants 2009-0082439 and 2009-0084522. The review of this brief was

arranged by Editor C. McAndrew.

The authors are with the Department of Electronic Engineering, Sogang

University, Seoul 121-742, Korea (e-mail: wchoi@sogang.ac.kr).

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TED.2010.2052167

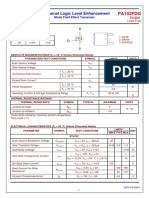

Fig. 1. Schematic of the proposed HG TFET. The HG TFET features different

gate insulators at the source (high-k material) and drain (silicon oxide) sides.

Since gate-to-channel coupling strength is different between channel regions

overlapped by the high-k material and silicon oxide, HG TFETs have a

local minimum of E

c

at the tunneling junction, which improves I

on

and SS.

In addition, because low-k silicon oxide is located at the drain side where

ambipolar behavior occurs, I

amb

can be suppressed.

sacricing chip density, as shown in Fig. 1. The HG TFET fea-

tures different gate dielectric materials at the drain and source

sides, which can be formed by isotropic etching of silicon

oxide followed by high-k material deposition. The proposed

HG TFETs will be compared with two kinds of conventional

devices, namely, TFETs that use only silicon oxide as a gate

insulator (SiO

2

-only TFETs) and TFETs that use only a high-k

material as a gate insulator (high-k-only TFETs). The SiO

2

-

only TFET corresponds to the HG TFET whose length of

silicon oxide under the gate, i.e., L

SiO

2

, is equal to the gate

length L

G

, whereas the high-k-only TFET corresponds to the

HG TFET whose length of high-k material under the gate,

i.e., L

high-k

, is equal to L

G

. The HG TFET is expected to

show higher I

on

and smaller SS than the SiO

2

-only and high-k-

only TFETs by modifying the band energy structure. A high-k

material partially located at the source side induces a local mini-

mum of the conduction band edge E

c

at the tunneling junction,

which will be discussed later from the following sections. In

addition, since silicon oxide whose relative permittivity is low

is located at the drain side, ambipolar behavior can effectively

be suppressed, which lowers I

amb

.

II. RESULTS AND DISCUSSION

To evaluate the merits of the proposed HG TFET, it has been

compared with the SiO

2

-only and high-k-only TFETs by two-

carrier and 2-D device simulation using Silvaco ATLAS [10]. A

nonlocal band-to-band tunneling model has been used [10]. In

simulation, L

G

is 50 nm, which is equal to the sumof L

SiO

2

and

L

high-k

. In addition, the physical thickness of the gate insulator,

i.e., t

ins

, and that of the silicon-on-insulator (SOI) layer, i.e.,

t

SOI

, are 2 and 30 nm, respectively. The relative permittivity of

the high-k material is assumed to be 25, which refers to that

0018-9383/$26.00 2010 IEEE

2318 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 57, NO. 9, SEPTEMBER 2010

Fig. 2. (a) Transfer curves of the HG, SiO

2

-only, and high-k-only TFETs in

the case of n-type doped polysilicon gates. HG TFETs follow SiO

2

-only TFETs

at low V

G

and high-k-only TFETs at high V

G

. (b) Transfer curves of the HG,

SiO

2

-only, and high-k-only TFETs when the gate workfunction is adjusted so

that V

onset

is 0 V for fair comparison. HG TFETs have the highest I

on

due to

their smallest SS.

of HfO

2

. The channel doping concentration is 10

16

cm

3

. An

abrupt junction prole is assumed. In addition, we assume that

the interface between the high-k material and silicon oxide is

abrupt. It is reasonable considering that the diffusion length of

Hf into SiO

2

is only 0.035 nm when the device is annealed

at 1000

C for 5 s [11]. I

on

is dened as the drain current I

D

when both the gate voltage V

G

and the drain voltage V

D

are

1 V, and I

amb

is dened as I

D

when V

G

is 0.2 V and V

D

is

1 V. SS is dened as an average slope when I

D

increases from

1 fA/m to 1 nA/m. The onset voltage V

onset

is dened as

V

G

when I

D

is 1 fA/m at 1-V V

D

.

Fig. 2(a) compares the transfer characteristics of the HG

TFET whose L

high-k

is 6 nm with those of the SiO

2

-only and

high-k-only TFETs in the case of n-type doped polysilicon

gates. Due to the heterogeneous gate dielectric, HG TFETs

follow SiO

2

-only TFETs at low V

G

and high-k-only TFETs at

high V

G

. It is because the ON-state is determined at the source-

to-channel region overlapped by the high-k material, whereas

the OFF-state ambipolar behavior is determined at the drain-to-

channel region overlapped by silicon oxide. It should also be

noted that the minimal leakage current level is determined by

reverse-biased p-i-n diode leakage. For fair comparison, from

now on, the gate workfunction will be adjusted so that V

onset

becomes 0 V. The value of gate workfunction is 4.37 eV,

which is attainable by using metal gates [12]. Fig. 2(b) shows

a redrawn version of Fig. 2(a) when the gate workfunction is

adjusted. It shows that HG TFETs have higher I

on

than high-k

TFETs, whereas they have as low I

amb

as SiO

2

-only TFETs,

which leads to high a ONOFF current ratio. It is because

HG TFETs have smaller SS than SiO

2

-only and high-k-only

TFETs, which can be explained as follows: Fig. 3(a) shows that

HGTFETs have a local minimumof E

c

due to different gate-to-

channel coupling strength between channel regions overlapped

by the high-k material and silicon oxide. Fig. 3(b) compares HG

TFETs with high-k-only TFETs in terms of source-to-channel

tunneling barrier width as a function of V

G

. HG TFETs show

a more abrupt change and a lower value of tunneling barrier

width than high-k-only TFETs. It is because the tunneling

barrier of HG TFETs abruptly narrows when a local minimum

of E

c

is aligned with the valence band edge E

v

of the source,

as shown in the inset of Fig. 3(b). In the case of SiO

2

-only

Fig. 3. (a) Band diagram of the HG TFET whose L

high-k

is 6 nm when V

G

is 0 V and V

D

is 1 V. (b) Source-to-channel tunneling barrier width of the HG

TFET whose L

high-k

is 6 nm compared with that of the high-k-only TFET.

The band diagram located in the box in (a) is magnied into two inset gures

in (b) depending on V

G

.

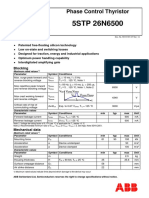

Fig. 4. (a) I

on

and SS and (b) I

amb

of HG TFETs depending on L

high-k

compared with those of SiO

2

-only and high-k-only TFETs. SiO

2

-only and

high-k-only TFETs correspond to HG TFETs whose L

high-k

s are 0 and

50 nm, respectively.

and high-k-only TFETs, source-to-channel tunneling barrier

width gradually decreases since E

c

gradually decreases from

the source-to-channel region. On the other hand, in the case of

HG TFETs, when the gate is biased around V

onset

, tunneling

barrier width is almost the same as that of high-k-only TFETs

because a local minimum of E

c

is not aligned with E

v

of the

source. It means that a local minimum of E

c

has not been

involved in the band-to-band tunneling process yet when V

G

is around V

onset

. However, as V

G

becomes higher, a local

minimum of E

c

is shifted downward and eventually aligned

with E

v

of the source. Therefore, when V

G

exceeds V

onset

, the

length of the tunneling path abruptly decreases because band-

to-band tunneling between a local minimum of E

c

and E

v

of

the source begins to dominate the whole tunneling process.

To optimize the design of HG TFETs, L

high-k

has been opti-

mized. Fig. 4(a) shows I

on

and SS as a function of L

high-k

. Note

that HG TFETs whose L

SiO

2

or L

high-k

is 50 nm correspond to

SiO

2

-only or high-k-only TFETs, respectively. It is observed

that L

high-k

can be optimized in terms of SS and I

on

. The

optimization process is related to the depth and width of the

conduction band well where a local minimum of E

c

is located.

As L

high-k

decreases, the conduction band well becomes shal-

lower, which makes band-to-band tunneling difcult to occur.

On the contrary, as L

high-k

increases, the conduction band well

becomes wider, which leads to a less abrupt transition between

OFF- and ON-states. When L

high-k

is optimized around 6 nm,

CHOI AND LEE: HETERO-GATE-DIELECTRIC TFETs 2319

the optimized HG TFETs show 60% smaller SS and 30%

higher I

on

than high-k-only TFETs. In addition, the HG TFETs

show80% smaller SS and two orders of magnitude higher I

on

than SiO

2

-only TFETs. Further improvement is expected if the

relative permittivity of the high-k material increases. Fig. 4(b)

shows I

amb

as a function of L

high-k

. I

amb

abruptly decreases as

L

high-k

decreases from 50 to 40 nm. It is explained by the fact

that I

amb

is originated from ambipolar behavior at the drain

side. When the high-k material is replaced by silicon oxide

at the drain side, the I

amb

of the HG TFET becomes almost

the same as that of the SiO

2

-only TFET. Compared with high-

k-only TFETs, HG TFETs show seven orders of magnitude

lower I

amb

.

III. CONCLUSION

HG TFETs have been proposed for high performance and

low-power consumption. In addition, device design has been

optimized by modulating L

high-k

. By using a local minimum

of E

c

at the tunneling junction and placing silicon oxide whose

relative permittivity is low at the drain side, the optimized

HG TFETs showed improved device performance than con-

ventional TFETs such as SiO

2

-only and high-k-only TFETs in

terms of I

on

, SS, and I

amb

.

REFERENCES

[1] M. R. William and A. J. A. Gehan, Silicon surface tunnel transistor,

Appl. Phys. Lett., vol. 67, no. 4, pp. 494496, Jul. 1995.

[2] Z. Qin, Z. Wei, and A. Seabaugh, Low-subthreshold-swing tunnel

transistors, IEEE Electron Device Lett., vol. 27, no. 4, pp. 297300,

Apr. 2006.

[3] K. Boucart and A. M. Ionescu, Double-gate tunnel FET with high- gate

dielectric, IEEE Trans. Electron Devices, vol. 54, no. 7, pp. 17251733,

Jul. 2007.

[4] O. M. Nayfeh, C. N. Chleirigh, J. Hennessy, L. Gomez, J. L. Hoyt,

and D. A. Antoniadis, Design of tunneling eld-effect transistors using

strained-silicon/strained-germanium type-II staggered heterojunctions,

IEEE Electron Device Lett., vol. 29, no. 9, pp. 10741077, Sep. 2008.

[5] J. Appenzeller, Y.-M. Lin, J. Knoch, C. Zhihong, and P. Avouris, Com-

paring carbon nanotube transistorsThe ideal choice: A novel tunneling

device design, IEEE Trans. Electron Devices, vol. 52, no. 12, pp. 2568

2576, Dec. 2005.

[6] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, Tunneling eld-effect

transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec,

IEEE Electron Device Lett., vol. 28, no. 8, pp. 743745, Aug. 2007.

[7] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, Band-to-band

tunneling in carbon nanotube eld-effect transistors, Phys. Rev. Lett.,

vol. 93, no. 19, p. 196 805, Nov. 2004.

[8] A. Vandooren, R. Rooyackers, D. Leonelli, F. Iacopi, E. Kunnen,

D. Nguyen, M. Demand, P. Ong, L. Willie, J. Moonens, O. Richard,

A. S. Verhulst, W. G. Vandenberghe, G. Groeseneken, S. D. Gendt, and

M. Heyns, A 35 nm diameter vertical silicon nanowire short-gate tunnel

FET with high-k/metal gate, in Proc. IEEE Silicon Nanoelectron. Work-

shop, 2009, pp. 2122.

[9] S. V. Anne, G. V. William, M. Karen, and G. Guido, Tunnel eld-effect

transistor without gate-drain overlap, Appl. Phys. Lett., vol. 91, no. 5,

p. 053 102, Jul. 2007.

[10] ATLAS Users Manual, SILVACO Int., Santa Clara, CA, 2009.

[11] N. Ikarashi, K. Watanabe, K. Masuzaki, and T. Nakagawa, Thermal

stability of a HfO

2

/SiO

2

interface, Appl. Phys. Lett., vol. 88, no. 10,

p. 101 912, Mar. 2006.

[12] H. Y. Yu, C. Ren, Y.-C. Yeo, J. F. Kang, X. P. Wang, H. H. H. Ma,

M.-F. Li, D. S. H. Chan, and D.-L. Kwong, Fermi pinning-induced

thermal instability of metal-gate work functions, IEEE Electron Device

Lett., vol. 25, no. 5, pp. 337339, May 2004.

Woo Young Choi (S05M10) was born in

Incheon, Korea, in 1978. He received the B.S., M.S.,

and Ph.D. degrees from Seoul National University,

Seoul, Korea, in 2000, 2002, and 2006, respectively.

From 2006 to 2008, he was with the Department

of Electrical Engineering and Computer Sciences,

University of California, Berkeley, as a Postdoctor.

Since 2008, he has been a member of the faculty

of Sogang University, Seoul, Korea, where he is

currently an Assistant Professor with the Depart-

ment of Electronic Engineering. He has authored

or coauthored more than 80 papers in international journals and conference

proceedings. He is the holder of 10 Korean patents. His current research

interests include fabrication, modeling, characterization, and measurement of

CMOS/CMOS-compatible semiconductor devices and nanoelectromechanical

memory cells.

Prof. Choi was the recipient of the Humantech Thesis Prize from Samsung

Electronics in 2005 and the Doyeon Paper Award from the Inter-University

Semiconductor Research Center, Seoul National University.

Woojun Lee was born in Seoul, Korea, in 1984. He

received the B.S. degree in electronic engineering in

2009 from Sogang University, Seoul, Korea, where

he is currently working toward the M.S. degree in

electrical engineering with the Department of Elec-

trical Engineering.

His current research interests include CMOS and

CMOS-compatible novel device modeling.

Potrebbero piacerti anche

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Infineon IRS218!4!44 and IR218 4 44 Comparison An v01 00 enDocumento6 pagineInfineon IRS218!4!44 and IR218 4 44 Comparison An v01 00 enNini FarribasNessuna valutazione finora

- Datasheet Transistor 2SJ567Documento7 pagineDatasheet Transistor 2SJ567Nayla AzzahraNessuna valutazione finora

- NPN Silicon: Semiconductor Technical DataDocumento4 pagineNPN Silicon: Semiconductor Technical DataRicardo VieraNessuna valutazione finora

- IGBT DriversDocumento13 pagineIGBT Driverssdio06Nessuna valutazione finora

- Data Sheet PA102FDGDocumento5 pagineData Sheet PA102FDGSlagalicaSlagalicaNessuna valutazione finora

- ADA026914, Physical Models of MOSFET DevicesDocumento157 pagineADA026914, Physical Models of MOSFET DevicesRGK77Nessuna valutazione finora

- Mixer Interm 642 Service ManualDocumento10 pagineMixer Interm 642 Service ManualAlan RamirezNessuna valutazione finora

- Unit-2 (B) Conventional Si ProcessingDocumento33 pagineUnit-2 (B) Conventional Si ProcessingPrajwal Jaiprakash KelaNessuna valutazione finora

- MOS Layers SticksDocumento55 pagineMOS Layers SticksgnitsiceNessuna valutazione finora

- 15-Types of Op AmpsDocumento37 pagine15-Types of Op AmpsYugandhar TannidiNessuna valutazione finora

- Lab de Mosfet PDFDocumento24 pagineLab de Mosfet PDFLeslye Flores SantiagoNessuna valutazione finora

- DEL ManualDocumento94 pagineDEL ManualAnand BongirNessuna valutazione finora

- Resistors Sources Batteries Capacitors: CrystalsDocumento8 pagineResistors Sources Batteries Capacitors: CrystalsXu Binh NguyenNessuna valutazione finora

- Chapter 3: MOS: Based On Prof. Rabaey and Prof. Allen's LecturesDocumento31 pagineChapter 3: MOS: Based On Prof. Rabaey and Prof. Allen's LecturesgianhuNessuna valutazione finora

- Re Transistor ModelDocumento15 pagineRe Transistor ModelUmar KhanNessuna valutazione finora

- Low-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Documento456 pagineLow-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Jon HimesNessuna valutazione finora

- 5STP 26N6500 - 5SYA1001-07 Mar 14Documento7 pagine5STP 26N6500 - 5SYA1001-07 Mar 14CarlosEduardoSalazarNessuna valutazione finora

- Low Power VLSI Circuits & Systems Complete NotesDocumento66 pagineLow Power VLSI Circuits & Systems Complete NotesSai SreejaNessuna valutazione finora

- Ece3002 Vlsi System Deign Cocob 2019Documento3 pagineEce3002 Vlsi System Deign Cocob 2019Debasis ChandraNessuna valutazione finora

- Government College of Engineering, Yavatmal: 1. EmailDocumento9 pagineGovernment College of Engineering, Yavatmal: 1. EmailKim D'souzaNessuna valutazione finora

- Arduino Basic Connection PDFDocumento39 pagineArduino Basic Connection PDFsabNessuna valutazione finora

- ZVP2110A ZVP2110C: P-Channel Enhancement Mode Vertical Dmos Fet P-Channel Enhancement Mode Vertical Dmos FetDocumento3 pagineZVP2110A ZVP2110C: P-Channel Enhancement Mode Vertical Dmos Fet P-Channel Enhancement Mode Vertical Dmos Fet19aldo97Nessuna valutazione finora

- Fds 4435Documento5 pagineFds 4435Rommel LoayzaNessuna valutazione finora

- Electronic Devices Model Question PapersDocumento2 pagineElectronic Devices Model Question Papersk_kunarajNessuna valutazione finora

- 8-Channel Saturated Sink Driver: UDN2595ADocumento8 pagine8-Channel Saturated Sink Driver: UDN2595AIkram UlhaqNessuna valutazione finora

- Power DissipationDocumento14 paginePower Dissipationvivek singhNessuna valutazione finora

- Seminar Presentation: Topic: Carbon Nano Tube Field Effect TransistorDocumento12 pagineSeminar Presentation: Topic: Carbon Nano Tube Field Effect TransistormukulNessuna valutazione finora

- Organic Solar CellDocumento19 pagineOrganic Solar CellchethanNessuna valutazione finora

- Lecture - 13-14 FET BiasingDocumento16 pagineLecture - 13-14 FET BiasingNaimur RahmanNessuna valutazione finora

- Spice Mosfet Model IntroDocumento58 pagineSpice Mosfet Model IntrodeancjenningsNessuna valutazione finora