Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

CN0350

Caricato da

Narayan ApteDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

CN0350

Caricato da

Narayan ApteCopyright:

Formati disponibili

Circuit Note

CN-0350

Circuits from the Lab reference designs are engineered and

tested for quick and easy system integration to help solve todays

analog, mixed-signal, and RF design challenges. For more

information and/or support, visit www.analog.com/CN0350.

Devices Connected/Referenced

AD8608

Precision, Low Noise, Quad CMOS, Rail

to Rail Input/Output Op Amp

AD7091R 1 MSPS, Ultralow Power, 12-Bit ADC

12-Bit, 1 MSPS, Single-Supply, Two-Chip Data Acquisition System for

Piezoelectric Sensors

EVALUATION AND DESIGN SUPPORT

Circuit Evaluation Boards

CN0350 Circuit Evaluation Board (EVAL-CN0350-PMDZ)

SDP/PMD Interposer board (SDP-PMD-IB1Z)

System Demonstration Platform (EVAL-SDP-CB1Z)

Design and Integration Files

Schematics, Layout Files, Bill of Materials

CIRCUIT FUNCTION AND BENEFITS

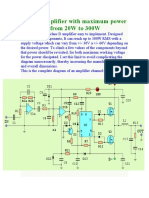

The circuit shown in Figure 1 is a 12-bit, 1 MSPS data

acquisition system utilizing only two active devices.

The system processes charge input signals from piezoelectric

sensors using a single 3.3 V supply and has a total error of less

than 0.25% FSR after calibration over a 10C temperature

range, making it ideal for a wide variety of laboratory and

industrial measurements.

The small footprint of the circuit makes this combination an

industry-leading solution for data acquisition systems where

accuracy, speed, cost, and size play a critical role.

Figure 1. Charge Input Single Supply Data Acquisition System for Piezoelectric Sensors (All Connections and Decoupling Not Shown)

TP1

C

CAL

1nF

C2

1nF

C8

4.7nF

C9

1F

4

J1

3

2

1

TP2 TP3

R3

100M

R1

10k

R2

10k

R7

10k

R10

100

R6

51

R4

1k

R5

270

R8

DNP

TP4

2.5V

+3.3V

+3.3V

+3.3V

TP6

1.25V

U1B

1/4

AD8608

U1A

1/4

AD8608

U1D

1/4

AD8608

U1C

1/4

AD8608

U2

AD7091R

HREF

TP5

VIN

VREF

GND REGCAP

CS

SCLK

CONVST

SDATA

VDRIVE

V

DD

CAL

POS

NEG

INPUT CON

PIEZOELECTRIC SENSOR

GND

SS

SCK

+3.3V

J2

PMOD CON

12 PIN

CONV

MISO

GND

HREF

HREF

+3.3V

1

1

9

1

0

-

0

0

1

Rev. 0

CircuitsfromtheLabreferencedesignsfromAnalogDeviceshavebeendesignedandbuiltbyAnalog

Devices engineers. Standard engineering practices have been employed in the design and

constructionofeachcircuit,andtheirfunctionandperformancehavebeentestedandverifiedinalab

environment at roomtemperature. However, you are solely responsible for testing the circuit and

determiningitssuitabilityandapplicabilityforyouruseandapplication. Accordingly, innoeventshall

AnalogDevicesbeliablefordirect,indirect,special,incidental,consequentialorpunitivedamagesdue

toanycausewhatsoeverconnectedtotheuseofanyCircuitsfromtheLabcircuits. (Continuedonlastpage)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 2014 Analog Devices, Inc. All rights reserved.

CN-0350 Circuit Note

CIRCUIT DESCRIPTION

The circuit consists of an input signal conditioning stage and an

ADC stage. The current input signal is converted to voltage by

charge-to-voltage converter (charge amplifier of the U1A op amp

and capacitor C2) and amplified by a noninverting amplifier

(the U1D op amp and the R7 and R8 resistors). The buffered

and attenuated (the U1B and U1C op amps and the resistors R1

and R2) voltage reference (VREF =2.5 V) from the ADC is used

to generate an offset HREF of 1.25 V for conditioning the ac signal

from sensor to input range of the ADC. Op amps U1A, U1B,

U1C, and U1D are one quad AD8608. The output of the U1D

op amp is 0.1 V to 2.4 V which matches the input range of the

ADC (0 V to 2.5 V) with 100 mV headroom to maintain linearity.

Resistor and capacitor values can be modified to accommodate

other sensor ranges as described in this circuit note.

The circuit design allows single supply operation. The minimum

output voltage specification of the AD8608 is 50 mV for a 2.7 V

power supply and 290 mV for 5 V power supply with 10 mA

load current, over the temperature range of 40C to +125C. A

minimum output voltage of 45 mV to 60 mV is a conservative

estimate for a 3.3 V power supply, a load current less than 1 mA,

and a narrower temperature range.

Considering the tolerances of the parts, the minimum output

voltage (low limit of the range) is set to 100 mV to allow for a

safety margin. The upper limit of the output range is set to 2.4 V

in order to give 100 mV headroom for the positive swing at the

ADC input. Therefore, the nominal output voltage range of the

input op amp is 0.1 V to 2.4 V.

The AD8608 is chosen for this application because of its low

bias current (1 pA maximum), low noise (12 nV/Hz maximum)

and low offset voltage (65 V maximum). Power dissipation is

only 15.8 mW on a 3.3 V supply.

A single-pole RC filter (R6/C8) follows the op amp output stage

to reduce the out-of-band noise. The cutoff frequency of the RC

filter is set to 664 kHz.

The AD7091R 12-bit 1 MSPS SAR ADC is chosen because of its

ultra-low power 349 A at 3.3 V (1.2 mW) which is significantly

lower than any competitive ADC currently available in the market.

The AD7091R also contains an internal 2.5 V reference with

4.5 ppm/C typical drift. The input bandwidth is 7.5 MHz, and

the high speed serial interface is SPI compatible. The AD7091R

is available in a small footprint 10-lead MSOP.

The total power dissipation of the circuit is approximately

17 mW when operating on a 3.3 V supply.

The AD7091R requires a 50 MHz serial clock (SCLK) to achieve

a 1 MSPS sampling rate. In most piezoelectric sensor applications,

a lower sampling rate can be used. The test data taken in this

circuit note used an SCLK of 30 MHz and a sampling rate of

300 kSPS.

The digital SPI interface can be connected to the microprocessor

evaluation board using the 12-pin PMOD-compatible connector

(Digilent PMOD Specifications).

Circuit Design

The circuit shown in Figure 2 converts the input charge to voltage

and level shifts to the ADC input range of 0.1 V to 2.4 V.

Figure 2. Charge Input Signal Conditioning Circuit

Piezoelectric elements are commonly used for the measurement

of acceleration and vibration. Here, the piezoelectric crystal is

used in conjunction with a seismic mass m. If the mass is

subjected to an acceleration a, then there is a resulting inertial

force F = m a acting on the seismic mass and the piezoelectric

crystal. This results in the crystal acquiring a charge q = d F,

where d (measured in coulombs/newton, C/N) is the crystal

charge sensitivity to force.

The resulting steady-state charge sensitivity Sa of piezoelectric

accelerometer is Sa = q/a (measured in C s

2

/m).

Note that acceleration can be converted to g using the

relationship 1 g = 9.81 m/s

2

.

If the accelerometer is used with a charge amplifier with

feedback capacitance C2, as is shown in Figure 2, the voltage

developed across C2 due to a charge q is V = q/C2. The

corresponding steady state voltage sensitivity is:

SV= V/a = Sa/C2. Eq. 1

The first stage of the signal conditioning circuit in Figure 1 is a

charge amplifier (U1A and capacitor C2), where the output

voltage is changing corresponding to Equation 1. The output of

the circuit is shifted to handle bipolar input signals (for example,

vibration measurements). The zero of the circuit is shifted to

the middle of the input range of the ADC, using a reference of

1.25 V. The output voltage of the charge amplifier is:

a

C

S

V

C

q

V dt i

C

V V

a

HREF HREF N HREF O

2 2 2

1

1

+ = + = + =

Eq. 2

The second stage of the signal conditioning circuit in Figure 1 is

a non-inverting amplifier with an output voltage of:

a

C

S

R

R

V V

a

HREF O

|

.

|

\

|

+ + =

2 8

7

1

2

Eq. 3

C2

1nF

R3

100M

R7

10k

R8

DNP

R4

1k POS

NEG

R5

270

V

O1

V

O1

= a

C

S

i

IN

i

IN

=

+3.3V

U1A

1/4

AD8608

U1D

1/4

AD8608

V

O2

HREF

a

(ACCELERATION)

+1.25V

PIEZOELECTRIC

CRYSTAL

dq

dt

S

a

C2

1

1

9

1

0

-

0

0

2

Rev. 0 | Page 2 of 7

Circuit Note CN-0350

The resistor R3 (100 M to 10 G for ceramic sensors and

10 G to 10 T for crystal sensors) provides dc feedback for

the op amp and supplies the input bias current. This resistor

must be as small as possible for the minimum frequency

measured and determines the lowest limit of frequency input

range. At low frequency, the corner frequency fCL is

approximately

2 3 2

1

C R

f

CL

=

Eq. 4

Adding a resistor R4 (1 k to 10 k) in series with the op amp

inverting input improves stability and limits input currents due

to accidental high input voltage. Increasing R4 further leads to a

reduction in the high frequency response. At high frequency R4

may be comparable to the impedance ZS of the sensor (1/CS,

where CS is the capacitance of the piezoelectric sensor).

The high frequency corner frequency fCH is:

S

CH

C R

f

4 2

1

=

Eq. 5

Using Equation 1 to Equation 5, the parameters of the circuit

(C2, R7, R8, fCL, and fCH) can be calculated for a specific

application.

For example, the Kistler type 8002K quartz accelerometer has

the following specifications:

Range, 1000 g

Sensitivity, 1 pC/g

Capacitance, 90 pF typical

Frequency Response, 1%, +5% 0 Hz to 6000 Hz

Insulation Resistance, >10

13

For an output voltage swing at VO1 of 1 V, Equation 1 is used

to calculate C2.

C2 = Sa a /V = (1 pC/g 1000 g)/1 V =1 nF

For an ADC input voltage swing of 0.1 V to 2.4 V (1.25 V

1.15 V), the gain of noninverting amplifier has to be equal to

1.15, and the ratio R7/R8 = 0.15. Choose a standard value

resistor for R7 =10 k, then R8 = 66.67 k.

Choose R3 = 100 M and neglect the input resistance of the op

amp and insulation resistance of the piezoelectric sensor. The

corner frequency at low frequency is (see Equation 4)

Hz

C R

f

CL

6 . 1

10 10 2

1

2 3 2

1

9 8

=

= =

Choosing R4 =1 k, the corner frequency at high frequency is

(see Equation 5)

MHz

C R

f

S

CH

77 . 1

10 90 10 2

1

4 2

1

12 3

=

= =

Thus, the protecting resistor R4 = 1 k does not affect the high

pass frequency response because the upper frequency response

of the sensor is only 6 kHz.

Gain and Offset Error due to Tolerances of Resistors and

Reference Voltage

From Equation 3, the gain of the signal conditioning circuit is

2

1

8

7

1

C R

R

GAIN

|

.

|

\

|

+ =

Eq. 6

The relative gain error is,

G

GAIN

dGAIN

=

Using the logarithmic derivative principle,

2 ln 8 ln ) 7 8 ln( ln C R R R GAIN + =

Taking the derivative of lnGAIN,

2

2

8

8

8 7

7

8 7

8

C

dC

R

dR

R R

dR

R R

dR

GAIN

dGAIN

+

+

+

=

2

2

8

8

8 7

7

7

7

8 7

8

8

8

C

dC

R

dR

R R

R

R

dR

R R

R

R

dR

GAIN

dGAIN

+

+

+

=

2 8 7 8

8 7

7

8 7

8

C R R R G

R R

R

R R

R

+

+

+

=

2 7 8

8 7

7

1

8 7

8

C R R G

R R

R

R R

R

+

+

|

.

|

\

|

+

=

2 7 8

8 7

7

8 7

7

C R R G

R R

R

R R

R

+

+

|

.

|

\

|

+

=

( )

2 8 7

8 7

7

C R R G

R R

R

|

.

|

\

|

+

=

Eq. 7

Using 1% tolerance devices R7, R8 and C2, the summing gain

error can be estimated.

Worst case relative gain error:

% 26 . 1 %) 1 % 2 13 . 0 ( % 1 % 2

7 . 66 10

10

) (

8 7

7

) (

2 8 7 max

= + =

|

.

|

\

|

+

+

=

=

(

+ +

+

=

k k

k

R R

R

C R R G

Mean square error (root-sum-square error):

% 0168 . 1 % 1 % 1 13 . 0 2

) (

8 7

7

) (

2 2 2

2

2

2

8

2

7

2

= + =

+ +

|

.

|

\

|

+

=

C R R MSqE G

R R

R

From Equation 3, the output offset of the signal conditioning

circuit is

REF

V

R R

R

HREF OFFSET

2 1

2

+

= =

Eq. 8

and the relative offset error is

VREF R R OS

R R

R

+

= ) (

2 1

1

1 2

Eq. 9

For 1% tolerance of R1, R2, and VREF, the summing offset error

can be estimated.

Rev. 0 | Page 3 of 7

CN-0350 Circuit Note

Worst case relative offset error:

% 2 ) (

2 1

1

) (

1 2 max

=

(

+ +

+

=

VREF R R OS

R R

R

Mean square offset error (root-sum-square error):

% 225 . 1 % 1 % 1 5 . 0 2 ) (

2 2 2

= + =

MSqE OS

The errors, caused by the tolerances of the resistors, the offsets

of the AD8608 op amps (75 V), and the ADC AD7091R, are

eliminated after calibration procedure. It is still necessary to

calculate and verify that the U1D op amp output is within the

required range (0.1 V to 2.4 V).

Gain and Offset Error due to Temperature Drift of

Resistors and Voltage Reference

Using Equation 7 and Equation 9, the errors due to the temper-

ature drift of components can be calculated. For example, for

100 ppm/C temperature drift of resistors and for 25 ppm/C

drift for reference voltage the worst case gain error is less than

0.013%/C, and the worst case offset error is about 0.01%/C,

which corresponds to a worst case total error of less than 0.25%

for 10C temperature changes.

Effect of Active Component Temperature Coefficients on

Overall Error

The dc offsets of the AD8608 op amps (75 V) and the

AD7091R ADC are eliminated by the calibration procedure.

The offset drift of the AD7091R internal reference is

4.5 ppm/C typical and 25 ppm/C maximum.

The offset drift of the AD8608 op amp is 1.5 V/C typical and

6 V/C maximum.

Note that resistor drift is the largest contributor to total drift if

100 ppm/C resistors are used, and the drift due to active

components can be neglected.

Calibration and Test

Test the sensitivity of a charge amplifier before interfacing it with

the sensor so that the gain in the system can be calibrated. An

electronic calibration system that does not require application

of any mechanical load (acceleration, force, pressure, etc.) is

shown in Figure 3. An adjustable amplitude and frequency low

impedance output voltage source in series with the calibration

capacitor CCAL drives the charge input. The output of the voltage

source must be floating with respect to the circuit board ground

so that it can operate at the HREF common-mode voltage of 1.25 V.

Figure 3. Calibrated Charge Input Signal Conditioning Circuit

The amount of input charge is Q = CCAL VIN. For example, an

input sine wave voltage with 1 V amplitude and a 1 nF calibration

capacitor produces a peak charge input of 1000 pC. This can

be used to calibrate the system. It is important that a 1% tolerance

or better capacitor is selected for CCAL to minimize errors. Note

that the tolerance of CCAL affects the calibration accuracy. The

tolerance of C2 is responsible for the output range, however the

temperature change of C2 affects accuracy.

The circuit can then be checked and adjusted using an external

simulation capacitor CSIM. Another way to check the circuit is to

use the CAL input and an adjustable voltage source. For calibration

and simulation purposes, the capacitor CCAL can be changed by

connecting an external parallel capacitor with the appropriate

value and accuracy across TP1 and TP2. For other input ranges

the capacitor C2 can be changed by connecting an external

parallel capacitor with appropriate value and accuracy across

TP3 and TP4.

Figure 4 shows the measured ADC output for a 1V 1 kHz sine

wave input and CSIM = 1 nF. The charge input is therefore

1000 pC.

Figure 4. ADC Output for 1000 pC Input Charge, 1 kHz Sine Wave

H

REF

= 1.25V

V

IN

= 1V PEAK

1kHz SINE WAVE

C

CAL

C

SIM

CN-0350 BOARD

CAL

C2

INTERPOSER

BOARD

POS

CAL

SIM

NEG

1

1

9

1

0

-

0

0

3

1

1

9

1

0

-

0

0

4

Rev. 0 | Page 4 of 7

Circuit Note CN-0350

Figure 5 shows the actual output using a Loudity LD-BZPN-2312

Piezoelectric Sensor with excitation from a loudspeaker with

about 120 Hz sine wave vibrations. The circuit was calibrated with

a peak input sine wave voltage of 1 V and CCAL = C2 = 10 nF.

Figure 5. Measured Output of LD-BZPN-2312 Piezoelectric Sensor with

Excitation from Loudspeaker with 120 Hz Sine Wave Vibrations

Printed Circuit Board (PCB) Layout Considerations

In any circuit where accuracy is crucial, it is important to consider

the power supply and ground return layout on the board. The

PCB must isolate the digital and analog sections as much as

possible. The PCB for this system was constructed in a simple

2-layer stack up, but a 4-layer stack up will give better EMS. See

the MT-031 Tutorial for more discussion on layout and grounding

and the MT-101 Tutorial for information on decoupling tech-

niques. The power supply to AD8608 must be decoupled with

10 F and 0.1 F capacitors to properly suppress noise and reduce

ripple. The capacitors must be placed as close to the device as

possible with the 0.1 F capacitor having a low ESR value. Ceramic

capacitors are advised for all high frequency decoupling. Power

supply lines must have as large trace width as possible to provide

low impedance path and reduce glitch effects on the supply line.

High impedance circuits for conditioning piezoelectric sensor

output require attention to resistors, insulation (dielectrics), and

cabling. The low impedance input circuit of the charge amplifier

significantly reduce the cabling problems, but the requirements

on the resistors, insulators, and layout of electrometer amplifiers

can also be applied to charge amplifiers built from discrete com-

ponents. A guard ring around the sensitive input terminals on

both sides of printed circuit boards is recommended to

minimize input leakage currents . The guard encircles the

positive terminal and connects to the reference (common)

voltage HREF.

A complete documentation package including schematics,

board layout, and bill of materials (BOM) can be found at

www.analog.com/CN0350-DesignSupport.

COMMON VARIATIONS

The circuit is proven to work with good stability and accuracy

with the component values shown. Other precision op-amps

and other ADCs can be used in this configuration to convert

1000 pC input charge range to digital output and for other

various applications for this circuit.

The circuit in Figure 1 can be designed for other than 1000 pC

input charge ranges, following the equations given in the Circuit

Design section. The connectors TP3 and TP4 can be used to put

additional capacitance in parallel to C2 to build circuits for other

ranges. The connectors TP1 and TP2 can be used to put additional

capacitance in parallel to CCAL to calibrate the circuit for other

ranges.

The AD7091 is similar to the AD7091R, but without the voltage

reference output, and the input range is equal to the power supply

voltage. The AD7091 can be used with an ADR3425 2.5 V refer-

ence. The ADR3425 does not require buffering, therefore a

single AD8605 and dual AD8606 can be used in the circuit.

The ADR3425 is a precision 2.5 V band gap voltage reference,

featuring low power and high precision (8 ppm/C of temperature

drift) in a 6-lead SOT-23 package.

The AD8601, AD8602 and AD8604 are single, dual, and quad

rail-to-rail, input and output, single-supply amplifiers featuring

very low offset voltage and wide signal bandwidth, that can be

used in place of AD8605, AD8606, and AD8608.

The AD7457 is a 12-bit, 100 kSPS, low power, SAR ADC, and can

be used in combination with the ADR3425 voltage reference in

place of AD7091R, when a higher throughput rate is not needed.

CIRCUIT EVALUATION AND TEST

This circuit uses the EVAL-CN0350-PMDZ circuit board, the

SDP-PMD-IB1Z and the EVAL-SDP-CB1Z system demonstration

platform (SDP) evaluation board. The interposer board SDP-

PMD-IB1Z and the SDP board EVAL-SDP-CB1Z have 120-pin

mating connectors. The interposer board and the EVAL-CN0350-

PMDZ board have 12-pin PMOD matching connectors, allowing

quick setup and evaluation of the performance of the circuit.

The EVAL-CN0350-PMDZ board contains the circuit to be

evaluated, as described in this note and the SDP evaluation

board is used with the CN0350 evaluation software to capture

the data from the EVAL-CN0350-PMDZ circuit board.

Equipment Needed

PC with a USB port, Windows XP or Windows Vista (32-

bit), or Windows 7/8 (64-bit or 32-bit)

EVAL-CN0350-PMDZ circuit evaluation board

EVAL-SDP-CB1Z SDP evaluation board

SDP-PMD-IB1Z interposer board

EVAL-CFTL-6V-PWRZ power supply

CN0350 evaluation software

Precision voltage generator

1

1

9

1

0

-

0

0

5

Rev. 0 | Page 5 of 7

CN-0350 Circuit Note

Getting Started

Load the evaluation software by placing the CN0350 evaluation

software disc in the CD drive of the PC. You also can download

the most up to date copy of the evaluation software from

CN0350 evaluation software. Using My Computer, locate the

drive that contains the evaluation software disc and open the

file setup.exe. Follow the on-screen prompts to finish the

installation. It is recommended to install all software

components to the default locations.

Functional Block Diagram

Figure 6 shows the functional diagram of the test setup.

Setup

Connect the EVAL-CFTL-6V-PWRZ (+6 V dc power

supply) to SDP-PMD-IB1Z interposer board via the dc

barrel jack

Connect the SDP-PMD-IB1Z (interposer board) to the

EVAL-SDP-CB1Z SDP board via the 120-pin ConA

connector

Connect the EVAL-SDP-CB1Z (SDP board) to the PC via

the USB cable

Connect the EVAL-CN0350-PMDZ evaluation board to

the SDP-PMD-IB1Z interposer board via the 12-pin

header PMOD connector

Connect the voltage generator to the EVAL-CN0350-

PMDZ evaluation board via terminal block J1Test

Launch the evaluation software. The software is able to communi-

cate to the SDP board if the Analog Devices system development

platform drivers are listed in the device manager. Once USB

communications are established, the SDP board can be used to

send, receive, and capture serial data from the EVAL-CN0350-

PMDZ board. Data can be saved in the computer for various

values of input voltages. Information and details regarding how

to use the evaluation software for data capturing can be found at

CN0350 Software User Guide.

A photo of the EVAL-CN0350-PMDZ board is shown in Figure 7.

Figure 6. Functional Diagram of Test Setup

Figure 7. Photo of EVAL-CN0350-PMDZ Board

J2

PMOD

J3

PMOD

EVAL-CFTL-6V-PWRZ

6V WALL WART

PC

EVAL-SDP-CB1Z

SDP-B BOARD

SDP-PMD-IB1Z

INTERPOSER BOARD

USB

CON A

J1

J4

120 PINS EVAL-CN0350-PMDZ

J1

VOLTAGE

GENERATOR/

PIEZOELECTRIC

SENSOR

1

1

9

1

0

-

0

0

6

1

1

9

1

0

-

0

0

7

Rev. 0 | Page 6 of 7

Circuit Note CN-0350

LEARN MORE

CN0350 Design Support Package:

http://www.analog.com/CN0350-DesignSupport

Pallas-Areny, Ramon and John G. Webster. Sensors and Signal

Conditioning. Copyright 2001, John Wiley & Sons.

MT-031 Tutorial, Grounding Data Converters and Solving the

Mystery of "AGND" and "DGND." Analog Devices.

MT-101 Tutorial, Decoupling Techniques. Analog Devices.

MT-004 Tutorial, The Good, the Bad, and the Ugly Aspects of

ADC Input NoiseIs No Noise Good Noise?. Analog Devices.

Data Sheets and Evaluation Boards

AD8608 Data Sheet

AD7091R Data Sheet

REVISION HISTORY

5/14Revision 0: Initial Version

(Continued from first page) Circuits from the Lab reference designs are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors.

While you may use the Circuits from the Lab reference designs in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual

property by application or use of the Circuits from the Lab reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, Circuits from the

Lab reference designs are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability,

noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties

that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab reference designs at any time without notice but is under no obligation to do so.

2014 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

CN11910-0-5/14(0)

Rev. 0 | Page 7 of 7

Potrebbero piacerti anche

- High Accuracy Impedance Measurements Using 12-Bit Impedance ConvertersDocumento6 pagineHigh Accuracy Impedance Measurements Using 12-Bit Impedance Converterschristobal_huntaNessuna valutazione finora

- CN0217Documento6 pagineCN0217alraca1234Nessuna valutazione finora

- STK400 040Documento10 pagineSTK400 040Carlos Milton Martinez GaleanoNessuna valutazione finora

- DiDocumento5 pagineDiTao Quang BinhNessuna valutazione finora

- AN-1141 Application Note: Powering A Dual Supply Precision ADC With Switching RegulatorsDocumento8 pagineAN-1141 Application Note: Powering A Dual Supply Precision ADC With Switching RegulatorsVINITA AGARWALNessuna valutazione finora

- 7SS522 CT RequirementDocumento4 pagine7SS522 CT RequirementAnonymous 9EV0OmkNessuna valutazione finora

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDocumento13 pagineClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428100% (1)

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDocumento13 pagineClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428Nessuna valutazione finora

- CN0376Documento7 pagineCN0376Milan ĐorđevicNessuna valutazione finora

- 06616415Documento5 pagine06616415jitu_4Nessuna valutazione finora

- Use A Transistor As A Heater PDFDocumento5 pagineUse A Transistor As A Heater PDFFlorin Marica100% (1)

- SG3524 SMPS Control Circuit: Description Pin ConfigurationDocumento5 pagineSG3524 SMPS Control Circuit: Description Pin ConfigurationNiko OlnicasaNessuna valutazione finora

- STK4132IIDocumento8 pagineSTK4132IIAttila SzelelkiNessuna valutazione finora

- High Voltage Power Operational Amplifiers: Features DescriptionDocumento6 pagineHigh Voltage Power Operational Amplifiers: Features DescriptionWaqas Ayub100% (1)

- LM1812 Ultrasonic Transceiver ModuleDocumento10 pagineLM1812 Ultrasonic Transceiver ModuleYogesh RamdasiNessuna valutazione finora

- Simple automatic-shutoff circuit uses few componentsDocumento5 pagineSimple automatic-shutoff circuit uses few componentsJuan Manuel Han MacNessuna valutazione finora

- ACS712 DatasheetDocumento15 pagineACS712 DatasheetHernan PorriniNessuna valutazione finora

- Iso 122Documento18 pagineIso 122rnjlmv83100% (1)

- Green-Mode PWM Controller: General Description FeaturesDocumento10 pagineGreen-Mode PWM Controller: General Description FeaturesLuis Luis GarciaNessuna valutazione finora

- DiDocumento6 pagineDipani256Nessuna valutazione finora

- LA4278Documento7 pagineLA4278aalex28Nessuna valutazione finora

- Ring OscillatorDocumento12 pagineRing OscillatorCmeLiv InmyHart NpaynoRentNessuna valutazione finora

- MC1648 DataSheetDocumento11 pagineMC1648 DataSheetKWojtekNessuna valutazione finora

- 7107 VoltmeterDocumento5 pagine7107 VoltmeterAmir EsmaeeliNessuna valutazione finora

- Forward Design 300W STmicroelectronics App NoteDocumento10 pagineForward Design 300W STmicroelectronics App Notecristi7521Nessuna valutazione finora

- 9-0-9 Step Down TransformerDocumento20 pagine9-0-9 Step Down TransformerSarthak JoshiNessuna valutazione finora

- 15 To 60 Watt Audio Amplifiers Using Complementary Darlington Output Transistors - An-483BDocumento8 pagine15 To 60 Watt Audio Amplifiers Using Complementary Darlington Output Transistors - An-483BAnonymous kdqf49qb100% (1)

- LD7552 DS 00Documento10 pagineLD7552 DS 00BRIGHT_SPARKNessuna valutazione finora

- 25638-Acquire Images With A Sensor and A Micro Controller PDFDocumento5 pagine25638-Acquire Images With A Sensor and A Micro Controller PDFSzilagyi SebaNessuna valutazione finora

- 26070-Test 18 Bit ADCs With An Ultrapure Sine Wave Oscillator PDFDocumento5 pagine26070-Test 18 Bit ADCs With An Ultrapure Sine Wave Oscillator PDFLuca CarboneNessuna valutazione finora

- OP37Documento16 pagineOP37Josef StevanusNessuna valutazione finora

- AFT05MP075NDocumento21 pagineAFT05MP075NjeremyAW2SNessuna valutazione finora

- Test Saturation VoltageDocumento3 pagineTest Saturation VoltageweimichNessuna valutazione finora

- Step Recovery Diode Frequency MultiplierDocumento4 pagineStep Recovery Diode Frequency MultiplierfahkingmoronNessuna valutazione finora

- Analog Devices Circuit NoteDocumento7 pagineAnalog Devices Circuit Notevighnesh shanbhagNessuna valutazione finora

- Simple FSKDocumento6 pagineSimple FSKFaten AliNessuna valutazione finora

- Ir Music TransmitterDocumento20 pagineIr Music TransmitterYedla Avinash Lucky'sNessuna valutazione finora

- ADC0809CCNDocumento16 pagineADC0809CCNFrancesca Castelar BenalcazarNessuna valutazione finora

- Ulta Stepup DC To DC Conveter With Reduced Switch StressDocumento21 pagineUlta Stepup DC To DC Conveter With Reduced Switch StressDRISHYANessuna valutazione finora

- MCP 3201Documento28 pagineMCP 3201Nacer MezghicheNessuna valutazione finora

- La 4278Documento6 pagineLa 4278Carlos López Rivera0% (1)

- CN0216Documento5 pagineCN0216Ram VillaNessuna valutazione finora

- AN1318Documento10 pagineAN1318iarangoNessuna valutazione finora

- TV Modulator Circuit: Semiconductor Technical DataDocumento10 pagineTV Modulator Circuit: Semiconductor Technical Databanduat83Nessuna valutazione finora

- Features Description: D D D D D D D D D D D DDocumento16 pagineFeatures Description: D D D D D D D D D D D D1eugen1Nessuna valutazione finora

- S T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Documento8 pagineS T K 4 2 3 1 I I 2-Channel Loowmin Af Power Amp (Dual Supplies)Arthur JonesNessuna valutazione finora

- Low Cost Analog Multiplier: AD633JN/AD633ANDocumento8 pagineLow Cost Analog Multiplier: AD633JN/AD633ANNarendra BholeNessuna valutazione finora

- An Analog Current Controller Design For Laser Diodes: Todd P. MeyrathDocumento7 pagineAn Analog Current Controller Design For Laser Diodes: Todd P. MeyrathAfzal345Nessuna valutazione finora

- 4 X 25W Quad Bridge Car Radio Amplifier: DescriptionDocumento11 pagine4 X 25W Quad Bridge Car Radio Amplifier: DescriptionJose Juan Cuevas DiazNessuna valutazione finora

- Low Noise An124fDocumento12 pagineLow Noise An124fraulqrvNessuna valutazione finora

- D D D D D D D D: DescriptionDocumento12 pagineD D D D D D D D: DescriptionManuel Aguado EcheverríaNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Da EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Valutazione: 4.5 su 5 stelle4.5/5 (3)

- Rapid Brochure PDFDocumento66 pagineRapid Brochure PDFankur100% (1)

- Premia Panel Lights Guide with Specs and PricesDocumento2 paginePremia Panel Lights Guide with Specs and PricesNarayan ApteNessuna valutazione finora

- OM 4 Sept 19Documento2 pagineOM 4 Sept 19Narayan ApteNessuna valutazione finora

- Ultra Fast Switches for Future MV SwitchgearDocumento7 pagineUltra Fast Switches for Future MV SwitchgearNarayan ApteNessuna valutazione finora

- Maharashtra State Board of Technical EducationDocumento1 paginaMaharashtra State Board of Technical EducationNarayan ApteNessuna valutazione finora

- 2.2 Conventional Methods of Speed Control: Unit-Ii DC DrivesDocumento47 pagine2.2 Conventional Methods of Speed Control: Unit-Ii DC DrivesrajeshNessuna valutazione finora

- Understanding & Using Dc-Ac Inverters: Electus Distribution Reference Data Sheet: INVERTER PDFDocumento4 pagineUnderstanding & Using Dc-Ac Inverters: Electus Distribution Reference Data Sheet: INVERTER PDFragupathiindiaNessuna valutazione finora

- Reactive Power1Documento8 pagineReactive Power1Tulika BhattacharjeeNessuna valutazione finora

- LCL - LC Comparison and DesignDocumento5 pagineLCL - LC Comparison and DesignSimon ZhangNessuna valutazione finora

- Biasing Internally Amplified Accelerometers: Bias RequirementsDocumento4 pagineBiasing Internally Amplified Accelerometers: Bias RequirementsNarayan ApteNessuna valutazione finora

- Tel: (592) 252-9530 (P. R. China) Email:: 2.6 5.5V Avdd DVDD Refp 0.1u Vout R3Documento1 paginaTel: (592) 252-9530 (P. R. China) Email:: 2.6 5.5V Avdd DVDD Refp 0.1u Vout R3Narayan ApteNessuna valutazione finora

- Prezi ShortcutsDocumento1 paginaPrezi ShortcutsNarayan ApteNessuna valutazione finora

- PcbsDocumento4 paginePcbsNarayan ApteNessuna valutazione finora

- Vacuum Switching in Low VoltageDocumento3 pagineVacuum Switching in Low Voltageandrei_filip_3Nessuna valutazione finora

- Tata Docomo Recharge Receipt 350 Rs SuccessfulDocumento1 paginaTata Docomo Recharge Receipt 350 Rs SuccessfulNarayan ApteNessuna valutazione finora

- Development of A Low Cost Touch Trigger Probe For CNC LathesDocumento7 pagineDevelopment of A Low Cost Touch Trigger Probe For CNC LathesNarayan ApteNessuna valutazione finora

- 5.5" PmoledDocumento4 pagine5.5" PmoledNarayan ApteNessuna valutazione finora

- Ascii ChartDocumento6 pagineAscii ChartNarayan ApteNessuna valutazione finora

- HNM BookDocumento268 pagineHNM BookasnsashankNessuna valutazione finora

- TrialDocumento1 paginaTrialNarayan ApteNessuna valutazione finora

- Varistores SIOV - Leaded - StandarD PDFDocumento36 pagineVaristores SIOV - Leaded - StandarD PDFDavid RosalesNessuna valutazione finora

- 5.5" PmoledDocumento4 pagine5.5" PmoledNarayan ApteNessuna valutazione finora

- Data SheetDocumento19 pagineData SheetDiego CaceresNessuna valutazione finora

- Python Web FrameworkDocumento5 paginePython Web FrameworkAdli AzriNessuna valutazione finora

- BGP Routing Protocol: BY: Gebretinsae GDocumento87 pagineBGP Routing Protocol: BY: Gebretinsae GDereje SeyoumNessuna valutazione finora

- Introduction to Open Financial Services (OFS) MessagesDocumento23 pagineIntroduction to Open Financial Services (OFS) Messagesrs reddyNessuna valutazione finora

- Profibus Oi en En-UsDocumento167 pagineProfibus Oi en En-UsHugo DiazNessuna valutazione finora

- Container Mechanics in RKT and LinuxDocumento75 pagineContainer Mechanics in RKT and LinuxAnonymous ryDGv1Nessuna valutazione finora

- Tips for Presenting Seminars and Overcoming ChallengesDocumento2 pagineTips for Presenting Seminars and Overcoming ChallengesMurali GowdaNessuna valutazione finora

- T1689en - MV3000 Technical Manual PDFDocumento169 pagineT1689en - MV3000 Technical Manual PDFleebjb0% (1)

- Support Package Manager PhasesDocumento9 pagineSupport Package Manager PhasesNeelu RaniNessuna valutazione finora

- Daily server monitoring report for August 23Documento6 pagineDaily server monitoring report for August 23Abhishek GaikwadNessuna valutazione finora

- E1-E2 - Text - Chapter 14. PAN TECHNOLOGY OVERVIEW, PAN SWITCHES AND OCPANDocumento8 pagineE1-E2 - Text - Chapter 14. PAN TECHNOLOGY OVERVIEW, PAN SWITCHES AND OCPANabhimirachi7077Nessuna valutazione finora

- Java Swing Calculator AppDocumento9 pagineJava Swing Calculator AppGayatri KateNessuna valutazione finora

- 5g, Oran & Lte Premium SyllabusDocumento12 pagine5g, Oran & Lte Premium SyllabusVishwaNessuna valutazione finora

- HND in Computing Networking Unit 2 Assignment 1 SampleDocumento85 pagineHND in Computing Networking Unit 2 Assignment 1 SampleronicaNessuna valutazione finora

- Tekjoht 6 S 04Documento32 pagineTekjoht 6 S 04Toulouse18Nessuna valutazione finora

- Bonfiglioli ACU R00 0 e PDFDocumento88 pagineBonfiglioli ACU R00 0 e PDFThiago MouttinhoNessuna valutazione finora

- Modem StandardsDocumento28 pagineModem StandardsPonmani SelviNessuna valutazione finora

- 17fin6542 Atm Fraud Inspection Guide NCR RGBDocumento11 pagine17fin6542 Atm Fraud Inspection Guide NCR RGBBoby JosephNessuna valutazione finora

- A Comprehensive Guide To The Essential EightDocumento14 pagineA Comprehensive Guide To The Essential EightXemox XenimaxNessuna valutazione finora

- TKR 750 850 Function v101Documento75 pagineTKR 750 850 Function v101sv6jhaNessuna valutazione finora

- Logcat 1Documento246 pagineLogcat 1Anonymous SmPmKWNessuna valutazione finora

- Elektor 1955Documento11 pagineElektor 1955Sandra M. LopezNessuna valutazione finora

- 2240-Article Text-6476-1-10-20230324Documento6 pagine2240-Article Text-6476-1-10-20230324drs.nasihin mkesNessuna valutazione finora

- Introducing Snowflake: Data Warehousing For EveryoneDocumento15 pagineIntroducing Snowflake: Data Warehousing For EveryoneMorozov AlexanderNessuna valutazione finora

- Panasonic Sa-Vkx65 SMDocumento100 paginePanasonic Sa-Vkx65 SMAjith Priyalal80% (10)

- FIR Ece2610 Chap5Documento38 pagineFIR Ece2610 Chap5bongo77priestNessuna valutazione finora

- SP3000 DDR3 DIMM 1600Mhz New BrochureDocumento5 pagineSP3000 DDR3 DIMM 1600Mhz New Brochureharvey1specter-1Nessuna valutazione finora

- Company Profile - DcsDocumento46 pagineCompany Profile - DcsRacer-XNessuna valutazione finora

- VSOL V2801F Datasheet V1.0Documento5 pagineVSOL V2801F Datasheet V1.0Антон ЛузгинNessuna valutazione finora

- BallsDocumento3 pagineBallsnikto dolezityNessuna valutazione finora