Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Final Lab 1 Ee635m

Caricato da

Stephano Guanilo Briones0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

44 visualizzazioni5 pagineEste documento presenta los resultados de una serie de experimentos realizados para comparar las características eléctricas de las puertas lógicas CMOS y TTL. Los experimentos midieron parámetros como los niveles de voltaje de entrada/salida, funciones lógicas, tiempos de subida y bajada, márgenes de ruido, retardo de propagación y efectos de la carga capacitiva. Los resultados mostraron que las puertas CMOS tienen tiempos de subida y bajada más rápidos, mayores márgenes de ruid

Descrizione originale:

Copyright

© © All Rights Reserved

Formati disponibili

PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoEste documento presenta los resultados de una serie de experimentos realizados para comparar las características eléctricas de las puertas lógicas CMOS y TTL. Los experimentos midieron parámetros como los niveles de voltaje de entrada/salida, funciones lógicas, tiempos de subida y bajada, márgenes de ruido, retardo de propagación y efectos de la carga capacitiva. Los resultados mostraron que las puertas CMOS tienen tiempos de subida y bajada más rápidos, mayores márgenes de ruid

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

44 visualizzazioni5 pagineFinal Lab 1 Ee635m

Caricato da

Stephano Guanilo BrionesEste documento presenta los resultados de una serie de experimentos realizados para comparar las características eléctricas de las puertas lógicas CMOS y TTL. Los experimentos midieron parámetros como los niveles de voltaje de entrada/salida, funciones lógicas, tiempos de subida y bajada, márgenes de ruido, retardo de propagación y efectos de la carga capacitiva. Los resultados mostraron que las puertas CMOS tienen tiempos de subida y bajada más rápidos, mayores márgenes de ruid

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 5

Final N01: Comprobacin Experimental de las

caractersticas elctricas de las puertas CMOS y

TTL

Stephano Guanilo Briones, Luis Antonio Selis Vasquez, Steve Rocha Mamani, Gustavo Lapa Velasquez

Facultad de Ingeniera Elctrica y Electrnica, Universidad Nacional de Ingeniera

Lima, Per

2014-2

sguanilob@hotmail.com

I. INFORME FINAL

1. Operacin CMOS

a) Completar los niveles de voltaje en la tabla desde los

resultados determinados en el laboratorio para el CMOS

CD4001. Circuito integrado:

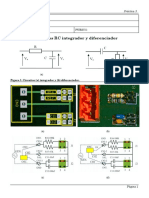

Circuito 1. Operacin CMOS

b) Cul es la tabla de verdad resultante suponiendo lgica

positiva? Qu funcin lgica se realiza?

Lgica positiva:

Realiza la uncin lgica NOR

-(p v q)

c) Cul es la tabla de verdad resultante suponiendo lgica

negativa? Qu funcin lgica se realiza en este caso?

Lgica negativa:

Realiza la uncin lgica NAND

-(p q)

A= LOW

B=LOW

C=HIGH

A= LOW

B=HIGH

C=LOW

A= LOW

B=HIGH

C=LOW

2. Curva de Transferencia de Voltaje CMOS y TTL

a) Plotear la curva de transferencia de tensin de la compuerta

TTL y CMOS, determinado en el laboratorio.

Fig. 1. Curva de transferencia de voltaje CMOS y TTL

b) Cul es el umbral de tensin resultante?

Como se puede ver en el grafico la tencin umbral resultante es

3.4V

c) Ilustrar grficamente el procedimiento para la determinacin

de VIL y VIH para una puerta TTL.

VIH=3.4V

Para determinar VIL de disminuye el voltaje desde 5V hasta

que la salida de un 0 lgico

VIL=3.16V

d) Cules son los mrgenes de ruido DC0 y DC1 para esta

puerta? Mostrar la forma en que se determinaron.

El margen de ruido DC0=VIL-VOL y DC1=VIH-VOH

DC0=3.16-0.4=2.76V

DC1=3.4-2.4=1V

3. Tiempos de Subida y Bajada (Rise y Fall)

a) En el siguiente grfico, plotear ambas formas de onda de

salida que resulta cuando una onda cuadrada de 307,2 kHz se

aplica a una puerta CMOS y una puerta TTL.

Circuito 2. Tiempo de Subida y bajada

Fig. 2. Curva de tiempo de subida y bajada

Primera Seal de color amarillo es el TTL

Segunda Seal de color azul es el CMOS

b) Qu familia de dispositivos para este dispositivo, TTL o

CMOS, tiene el rise y fall time ms rpido?

Como podemos apreciar en la grafica, el TTL tiene rise y fall

time de ms duracin que el CMOS. Pues como se ve, el

CMOS tiene menos rise que el TTL, viendo en la grfica, el

CMOS va casi en forma directa (en cierto de intervalo de

tiempo) pero el TTL muestra curvas en su trayectoria (en el

mismo intervalo de tiempo). Adems, el CMOS tiene un menor

tiempo de cada que el TTL, esto muestra entonces que el fall

time del CMOS es ms rpido que del TTL.

Esto se puede comprobar de los datos del osciloscopio en la

grafica:

T. Bajada CMOS: 124 ns.

T. Bajada TTL: 22 ns.

4. Margen de Ruido

a) Cul es el margen de ruido DC0 medido por la puerta

CMOS?

Fig. 3. Margen de ruido CMOS

En la figura vemos las ondas obtenidas:

Como se observa el voltaje pico de la primera onda es 5V

mientras que el voltaje pico de la senda es 4.4V entonces el

margen de ruido es 0.6V

b) Como resultado de esta medicin y los resultados en la

Segunda c) para la determinacin del ruido margen de

dispositivos TTL, qu familia de dispositivos sera el mejor

candidato para usar en el diseo de circuitos digitales para un

entorno elctricamente "ruidoso"?

En un entorno elctricamente ruidoso convendra usar la familia

CMOS en vez de la TTL ya que la familia CMOS HCXX tiene

mayor margen de ruido.

5. Retardo de Propagacin

a) Trace la forma de onda de salida observada en la parte E de

este experimento para determinar el retardo de propagacin a

travs de puertas CMOS.

Fig. 4. Ondas de retardo de propagacin

En la figura tenemos, como de color amarillo, a la seal entre

dos puertas CMOS y, como de color azul, la seal de salida en

una puerta CMOS.

b) Cul es el tiempo de propagacin media resultante por

puerta? Indique cmo fue determinado. Compararlo con el

retraso medio de propagacin de una compuerta TTL (por

ejemplo, un inversor 74LS04) y que figura en la ficha de datos

TTL.

De lo cual, superponindolas para encontrar el tiempo promedio

entre ella es.

Fig. 5. Superposicion de ondas CMOS y TTL

En el grafico podemos apreciar la superposicin de las ondas, y,

gracias al Osciloscopio, podemos obtener el retardo de

propagacin promedio por puerta CMOS que es igual a 220 ns.

6. Carga Capacitiva.

a) Representa grficamente la dos formas de onda de salida

obtenidos en la Parte F:

Fig. 6. Efectos de la carga en el osciloscopio

b) Qu efecto capacitivo de carga se tiene en la subida y

bajada de las salidas de la puerta? Calcular la subida y cadas

con y sin carga capacitiva.

Usando los cursores del osciloscopio y haciendo la diferencia

notamos que:

Por el canal 1 el tiempo de subida es de 84ns mientras que en el

canal 2 el tiempo de subida es de 72ns.

Por el canal 1 el tiempo de bajada es de 80ns mientras que el

tiempo de bajada por el canal 2 es de 40ns

7. Sobrepico de Corriente.

a) Grfico de salida de la puerta y formas de onda de tensin de

alimentacin obtenida en la parte G.

Circuito 3. Sobre pico de corriente

Fig. 7. Sobre pico de corriente

b) Si esta degradacin de la fuente de alimentacin no se

controla en grandes circuitos, la operacin del circuito puede

ser afectada. Las numerosas salidas de compuerta de

conmutacin en un momento breve, pretenden elaborar grandes

cantidades de corriente al mismo tiempo. La fuente de

alimentacin puede no ser capaz de satisfacer esta demanda

repentina de corriente. Cmo puede eludirse este problema?

Para eludir este problema es necesario el uso de un capacitor

estos tratarn de contrarrestar ese efecto oponindose al

cambio, si es un pico lo absorbern y si es una baja de tensin,

otorgarn a la lnea parte de la energa almacenada por ellos,

tratando siempre que la lnea se encuentre a la misma tensin.

Este depender de la aplicacin y su respuesta con la

frecuencia, ya que no puede colocarse cualquier capacitor. Es

recomendable para altas frecuencias el uso de capacitores de

Tantalio.

8. Resumen

Estados fsicos representado bits en diferentes

Tecnologa Bit de representacin de estado

0 1

CMOS 0 - 1.5 V 3.5 - 5.0 V

TTL 0 - 0.8 V 2.0 - 5.0 V

Mrgenes de ruido de CD

Indica cuanto ruido se necesita para corromper un voltaje de

salida en un valor que no puede ser reconocido adecuadamente

por una entrada.

En general, las salidas CMOS tienen excelentes mrgenes de

ruido de CD cuando excitan a otras entradas CMOS (1.25 V).

Sin importar el voltaje que se aplica en la entrada de un inversor

CMOS, la entrada consume muy poca corriente.

Este es un contraste considerable con los circuitos bipolares de

lgica como TTL, cuyas entradas pueden consumir una

cantidad considerable de corriente.

Comportamiento de circuitos CMOS Y TTL

En sistemas CMOS puros, todos los dispositivos lgicos del

circuito son CMOS, los niveles de salida permanecen muy

cerca de las lneas de alimentacin y ninguno de los

dispositivos desperdicia energa en sus salidas.

Por otra parte, si las salidas TTL se conectan a las entradas

CMOS, entonces las salidas CMOS utilizan ms energa.

9. Recomendaciones y Observaciones

La estabilidad y exactitud en los circuitos reales son difciles de

obtener. Estos se ven afectados por las tolerancias de

fabricacin de sus componentes, cambios de voltaje de

alimentacin y ruidos creados creado por otros circuitos, entre

otras cosas.

Potrebbero piacerti anche

- Lab Diseño 1Documento7 pagineLab Diseño 1Juls FloresNessuna valutazione finora

- Lab 3 .Compuertas LogicasDocumento5 pagineLab 3 .Compuertas LogicassokaNessuna valutazione finora

- Informe Previo 1 EE644N Diseño Lógico DigitalDocumento9 pagineInforme Previo 1 EE644N Diseño Lógico DigitalFRANCK DAVID SORIA PINEDONessuna valutazione finora

- CE3 Lab2Documento9 pagineCE3 Lab2Jhosep Jeanpool Valdez LuqueNessuna valutazione finora

- CEA Lab2Documento11 pagineCEA Lab2Shanella ChallcoNessuna valutazione finora

- Taller 4 - Conceptos de Lógica CMOS, TTL y Circuitos Lógicos CombinacionalesDocumento21 pagineTaller 4 - Conceptos de Lógica CMOS, TTL y Circuitos Lógicos CombinacionalesSebastian Guarnizo PerdomoNessuna valutazione finora

- Circuitos Cmos 1Documento9 pagineCircuitos Cmos 1Paul R. ZamudioNessuna valutazione finora

- 3° Practica LaboratorioDocumento14 pagine3° Practica Laboratorioandy77740Nessuna valutazione finora

- Generadores de PulsoDocumento18 pagineGeneradores de PulsocoleccionarinformacNessuna valutazione finora

- Características Operacionales Y Parámetros Básicos: Ihmin Ilmax Ohmin Olmax Ihmin Ilmax Ohmin OlmaxDocumento8 pagineCaracterísticas Operacionales Y Parámetros Básicos: Ihmin Ilmax Ohmin Olmax Ihmin Ilmax Ohmin OlmaxDaniel MedauraNessuna valutazione finora

- Lab 1Documento7 pagineLab 1Julita Nelson GordonNessuna valutazione finora

- Practixca 1Documento5 paginePractixca 1giancarlos gallo camposNessuna valutazione finora

- Circuitos CombinacionalesDocumento12 pagineCircuitos CombinacionalesCarlos RaulNessuna valutazione finora

- 8-Compuerta Real ShortDocumento4 pagine8-Compuerta Real ShortMiguel Esteban MartinezNessuna valutazione finora

- Inversor CmosDocumento4 pagineInversor CmosJhony LlanoNessuna valutazione finora

- Tecnicas DigitalesDocumento25 pagineTecnicas DigitalesHector VallejosNessuna valutazione finora

- Laboratorio 1 Electr Nica DigitalDocumento5 pagineLaboratorio 1 Electr Nica DigitalDanaNessuna valutazione finora

- Circuitos TTL y CmosDocumento5 pagineCircuitos TTL y CmosAlondra TaveraNessuna valutazione finora

- Familias Logicas Practica 1Documento5 pagineFamilias Logicas Practica 1Oscar AndresNessuna valutazione finora

- Compuertas LogicasDocumento6 pagineCompuertas LogicasPablo RafaelNessuna valutazione finora

- Feb 00Documento10 pagineFeb 00Sasuke BacusNessuna valutazione finora

- Circuitos A Régimen ImpulsivoDocumento20 pagineCircuitos A Régimen ImpulsivoPato GuaracaNessuna valutazione finora

- Familias LógicasDocumento15 pagineFamilias LógicasErnestoVázquezNessuna valutazione finora

- Sistemas Logicos - 2 - Guia de PracticosDocumento23 pagineSistemas Logicos - 2 - Guia de PracticosPieroNessuna valutazione finora

- Informe 3Documento14 pagineInforme 3Sophia Calle MedinaNessuna valutazione finora

- Familias TTL y CmosDocumento14 pagineFamilias TTL y CmosDiana OlivaresNessuna valutazione finora

- Familias Lógicas y Lineales de Circuitos Integrados PDFDocumento9 pagineFamilias Lógicas y Lineales de Circuitos Integrados PDFanxoNessuna valutazione finora

- Informe Tecnico Cerradura ElectricaDocumento14 pagineInforme Tecnico Cerradura ElectricaYaritza CardenasNessuna valutazione finora

- Informe Electronica IIDocumento20 pagineInforme Electronica IIMelissa Escandon CampusanoNessuna valutazione finora

- Capitulo 1Documento9 pagineCapitulo 1Cesar Idvorsky Gutiérrez CachiqueNessuna valutazione finora

- Compuerta or de 3 EntradasDocumento9 pagineCompuerta or de 3 EntradasKevin MendezNessuna valutazione finora

- Reporte Cruce Por Cero GERARDODocumento8 pagineReporte Cruce Por Cero GERARDOfirst_second12Nessuna valutazione finora

- Detectores de Cruze Por CeroDocumento5 pagineDetectores de Cruze Por CeroIsrael FonsecaNessuna valutazione finora

- Familia TTLDocumento8 pagineFamilia TTLKenia JohanssonNessuna valutazione finora

- CarlosCuartas 22 Tarea5Documento25 pagineCarlosCuartas 22 Tarea5cdmancilla100% (2)

- Guardado Con Autorrecuperación de IEEE-FSK-Navidad - AsdDocumento9 pagineGuardado Con Autorrecuperación de IEEE-FSK-Navidad - AsdDaniel CavaNessuna valutazione finora

- Cuáles Son Las Series Más Comunes CMOS y TTLDocumento9 pagineCuáles Son Las Series Más Comunes CMOS y TTLKevinAlxChrNessuna valutazione finora

- Práctica-1 Diseño DigitalDocumento18 paginePráctica-1 Diseño DigitalDaniel GómezNessuna valutazione finora

- Lab 1 SCRDocumento6 pagineLab 1 SCRAlexander GonzalezNessuna valutazione finora

- Compuertas LogicasDocumento21 pagineCompuertas Logicasfer6669993Nessuna valutazione finora

- Informe 5 PrevioDocumento5 pagineInforme 5 PrevioEmmanuel AlvizNessuna valutazione finora

- Practica 3Documento5 paginePractica 3ALFREDO SANTILLANNessuna valutazione finora

- Definición de Los TTL y CMOSDocumento7 pagineDefinición de Los TTL y CMOSNestor RamosNessuna valutazione finora

- Comparativa CMOS TTLDocumento2 pagineComparativa CMOS TTLsonrasielNessuna valutazione finora

- Familia TTL Vs CmosDocumento8 pagineFamilia TTL Vs CmosGlauco DelgadoNessuna valutazione finora

- Presentacion CMOsDocumento19 paginePresentacion CMOsMarcelo P CerratoNessuna valutazione finora

- Preinforme 1Documento12 paginePreinforme 1JOSE LUIS PERDOMO ARDILANessuna valutazione finora

- Informe Final N°1 Laboratorio de C. DigitalesDocumento20 pagineInforme Final N°1 Laboratorio de C. DigitalesAmerico MedinaNessuna valutazione finora

- Circuitos Integrados TTL y CmosDocumento4 pagineCircuitos Integrados TTL y CmosStefani TercerosNessuna valutazione finora

- TP Area DigitalesDocumento10 pagineTP Area DigitalesCelesteCebedioNessuna valutazione finora

- Experi 1Documento9 pagineExperi 1Jesus Quintero EspinaNessuna valutazione finora

- Tarea1 PabloMelgarDocumento10 pagineTarea1 PabloMelgarPablo Melgar0% (1)

- PLL y VcoDocumento10 paginePLL y VcoDavid LemaNessuna valutazione finora

- Borrador Caracteristicas de Las Familias LogicasDocumento13 pagineBorrador Caracteristicas de Las Familias LogicasSilvana GetialNessuna valutazione finora

- Sol Lab 1Documento22 pagineSol Lab 1Michael PomaNessuna valutazione finora

- Cmos I Resumen Capitulo IiiDocumento7 pagineCmos I Resumen Capitulo IiiUlisesNessuna valutazione finora

- 100 circuitos de shields para arduino (español)Da Everand100 circuitos de shields para arduino (español)Valutazione: 3.5 su 5 stelle3.5/5 (3)

- Armónicas en Sistemas Eléctricos IndustrialesDa EverandArmónicas en Sistemas Eléctricos IndustrialesValutazione: 4.5 su 5 stelle4.5/5 (12)

- Prácticas de redes de datos e industrialesDa EverandPrácticas de redes de datos e industrialesValutazione: 4 su 5 stelle4/5 (5)

- Filtro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoDa EverandFiltro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoNessuna valutazione finora

- Cuaderno 7 - Sibila NúñezDocumento10 pagineCuaderno 7 - Sibila NúñezRaquel LeanizNessuna valutazione finora

- 1-1 Fundamentacion de ModaDocumento30 pagine1-1 Fundamentacion de Modaliliana arandaNessuna valutazione finora

- Manual de Uso para Samsung D5000 Serie 5 SMART TVDocumento191 pagineManual de Uso para Samsung D5000 Serie 5 SMART TVjmtexla68Nessuna valutazione finora

- MovimaDocumento10 pagineMovimaNicol ApNessuna valutazione finora

- Los Esencial de La Hipnosis PDFDocumento213 pagineLos Esencial de La Hipnosis PDFFaby RoHu100% (1)

- Trabajo Del OxigenoDocumento10 pagineTrabajo Del OxigenoLuis Alberto Tello CequeroNessuna valutazione finora

- SPA-1998-10-25-2 La Venida Del Senor Con Las nubes-SANCL-EDITADODocumento52 pagineSPA-1998-10-25-2 La Venida Del Senor Con Las nubes-SANCL-EDITADOAlexandra Valencia100% (1)

- BALSADocumento4 pagineBALSARODRIGO DE JESUS VARGAS MARTINEZNessuna valutazione finora

- Ggplot Graficos CalidadDocumento29 pagineGgplot Graficos CalidadAnonymous dQZRlcoLdhNessuna valutazione finora

- Dinámica-Unidad 2-Actividades-406bDocumento23 pagineDinámica-Unidad 2-Actividades-406bcristian lagunesNessuna valutazione finora

- Motor DSPICDocumento10 pagineMotor DSPICGustavo Choque CuevaNessuna valutazione finora

- Traduccion Guias ESPEN de NE PDFDocumento3 pagineTraduccion Guias ESPEN de NE PDFDavid M. Lesmes100% (1)

- Síndrome de BurnoutDocumento5 pagineSíndrome de BurnoutDaniel MocarroNessuna valutazione finora

- Elogio de La FilosofiaDocumento4 pagineElogio de La FilosofiaPatricia KingsleighNessuna valutazione finora

- Planta MedicinalDocumento11 paginePlanta MedicinalMaria Teresa HerreraNessuna valutazione finora

- 3° de Secundaria AP - 1° TrimestreDocumento17 pagine3° de Secundaria AP - 1° TrimestreAlem Amed Rojas UgarteNessuna valutazione finora

- Estudio de Impacto AmbientalDocumento12 pagineEstudio de Impacto AmbientalYersin Edison Machacuay CrispinNessuna valutazione finora

- Libro Apicultura HoyDocumento184 pagineLibro Apicultura HoySofía López OrtegaNessuna valutazione finora

- BM12093 0720Documento4 pagineBM12093 0720Ale MPNessuna valutazione finora

- CP1823 PB PR CP Presupuesto Ed1Documento117 pagineCP1823 PB PR CP Presupuesto Ed1eddragon877523Nessuna valutazione finora

- Responsabilidad Social Empresarial (RSE) : - Smith, CraigDocumento4 pagineResponsabilidad Social Empresarial (RSE) : - Smith, CraigEvelynNessuna valutazione finora

- Martin Memoria de Calculo EstructuraDocumento35 pagineMartin Memoria de Calculo EstructuraAAVANessuna valutazione finora

- Econsejo 4 Los ColoidesDocumento21 pagineEconsejo 4 Los ColoidesAsun ArribaNessuna valutazione finora

- Emisiones de Las Formas 1Documento4 pagineEmisiones de Las Formas 1GabrielInsua100% (2)

- Introduccion A La Electricidad ElectronicaDocumento55 pagineIntroduccion A La Electricidad ElectronicaOsvaldoOrNessuna valutazione finora

- Concepto: Propiedades Y CaracteristicasDocumento13 pagineConcepto: Propiedades Y CaracteristicasHEIDY CRISTEL AYALA TRUJILLONessuna valutazione finora

- El ProtectorDocumento3.319 pagineEl Protectormalemo7767% (3)

- Acido Nítrico 7697-37-2Documento12 pagineAcido Nítrico 7697-37-2Eduardo AvalosNessuna valutazione finora

- Plan de Gestion Integral de Residuos Solidos PMIRSDocumento24 paginePlan de Gestion Integral de Residuos Solidos PMIRSVivis SánchezNessuna valutazione finora

- La Formula de La Felicidad - Alvaro AsensioDocumento76 pagineLa Formula de La Felicidad - Alvaro AsensioPercy Vasquez100% (1)