Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

M.tech - Vlsi - 2014-15

Caricato da

KarthikChinna0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

25 visualizzazioni3 pagineReal time scenario: The students will be given the real time experience of preparing their own ideas and papers.

Thanks & Regards,

MSR PROJECTS(SSI Certify company),

ENTERPRENUERS’ MEMORAND NUMBER: 280062116408.

Head Office: #302, 3nd Floor, Gyan Arcade,

Ammerpet, HYDERABAD-500 082.

E-mail: m.s.r.projects.ieee@gmail.com,

Web: Facebook.com/m.s.r.project ,

Ring on: +91 9581464142.

Titolo originale

M.TECH -VLSI -2014-15

Copyright

© © All Rights Reserved

Formati disponibili

DOC, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoReal time scenario: The students will be given the real time experience of preparing their own ideas and papers.

Thanks & Regards,

MSR PROJECTS(SSI Certify company),

ENTERPRENUERS’ MEMORAND NUMBER: 280062116408.

Head Office: #302, 3nd Floor, Gyan Arcade,

Ammerpet, HYDERABAD-500 082.

E-mail: m.s.r.projects.ieee@gmail.com,

Web: Facebook.com/m.s.r.project ,

Ring on: +91 9581464142.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

25 visualizzazioni3 pagineM.tech - Vlsi - 2014-15

Caricato da

KarthikChinnaReal time scenario: The students will be given the real time experience of preparing their own ideas and papers.

Thanks & Regards,

MSR PROJECTS(SSI Certify company),

ENTERPRENUERS’ MEMORAND NUMBER: 280062116408.

Head Office: #302, 3nd Floor, Gyan Arcade,

Ammerpet, HYDERABAD-500 082.

E-mail: m.s.r.projects.ieee@gmail.com,

Web: Facebook.com/m.s.r.project ,

Ring on: +91 9581464142.

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato DOC, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 3

MSR PROJECTS

(AN SSI CERTIFIED INSTITUTION)

TRAINING | DEVELOPMENT |

PLACEMENTS

VLSI IEEE-2014 PROJECTS LIST (M.Tech)

CODE TITLE EAR

MSR01

A novel approach to realize Built-in-self-test(BIST) enabled

ART usin! "#$%

&01'

MSR0&

A h(brid-radi) approach for efficient i*ple*entation of unfolded

+,R$I+ architectures for -./A platfor*s0

&01'

MSR01

#i!h throu!hput architecture for the Advanced 2ncr(ption

Standard Al!orith* &01'

MSR0' Area-$ela( 2fficient Binar( Adders in 3+A &01'

MSR04

+o**ents on Self-+hec5in! +arr(-Select Adder $esi!n Based on

T6o-Rail 2ncodin!

&01'

MSR07

A $eci*al Binar( Multi-operand Adder usin! a -ast Binar( to

$eci*al +onverter

&01'

MSR08 .ipelined Architecture for "edic Multiplier &01'

MSR09

I*ple*entation of #i!h Speed %o6 .o6er +o*binational and

Se:uential +ircuits usin! Reversible lo!ic

&01'

MSR0; #i!h Speed +onvolution and $econvolution Al!orith* &01'

MSR010

$esi!n and Si*ulation of .o6er 2fficient Traffic

%i!ht +ontroller (.T%+)

&01'

MSR011

I*ple*entation of R</ in -./A usin! 2fficientResource

tilization

&011

MSR01& Multi operand Redundant Adders on -./As0 &011

MSR011 17-Bit =ave-.ipelined Sparse-Tree RS-3 Adder0 &011

MSR01'

A #i!h Speed Binar( -loatin! .oint Multiplier sin! $adda

Al!orith*0

&011

Head Ofce: #302, 3

nd

Floor, Gyan Arcade, Ammerpet, HYDERABAD-00 0!2"

E-ma#l: m"$"r"pro%ect$"#eee&'ma#l"com, (e): Face)oo*"com+m"$"r"pro%ect , R#n'

on: ,-. -!./0/./2

MSR PROJECTS

(AN SSI CERTIFIED INSTITUTION)

TRAINING | DEVELOPMENT |

PLACEMENTS

MSR014

An -./A Based #i!h Speed Ieee-84' $ouble .recision -loatin!

.oint Multiplier sin! "erilo! #$%0

&011

MSR017

I*ple*entation And +o*parison ,f 2ffective Area 2fficient

Architectures -or +S%A0

&011

MSR018 $esi!n A $S. ,perations sin! "edic Mathe*atics0 &011

MSR019

$esi!n of #i!h Speed %o6 .o6er Multiplier sin! Reversible

%o!ic> A "edic Mathe*atical Approach0

&011

MSR01;

<ovel #i!h Speed "edic Mathe*atics Multiplier sin!

+o*pressors0

&011

MSR0&0 $esi!n ,f hi!h .erfor*ance 7' Bit MA+ nit0 &011

&10%o6 po6er S:uare and +ube Architectures sin! "edic Sutras ( &01' I222 )

&0#i!h Speed "edic Multiplier $esi!ns ( &01' I222 )

10 Binar( $ivision .o6er Models for #i!h-%evel .o6er 2sti*ation of -./A-Based $S.

+ircuits ( &01' I222 )

'0$esi!n of $edicated Reversible 3uantu* +ircuitr( for S:uare +o*putation ( &01' I222 )

40ASI+ $esi!n of Reversible Multiplier +ircuit ( &01' I222 )

70All ,ptical Reversible Multiple)er $esi!n usin! Mach-?ehnder Interfero*eter ( &01'

I222 )

80+ircuit for Reversible 3uantu* Multiplier Based on Binar( Tree ,pti*izin! Ancilla and

/arba!e Bits ( &01' I222 )

90$esi!n of 2fficient Binar( +o*parators in 3uantu*-$ot +ellular Auto*ata ( &01' I222 )

;02li*inatin! S(nchronization %atenc( sin! Se:uenced %atchin! ( &01' I222 )

100Area-$ela( 2fficient Binar( Adders in 3+A ( &01' I222 )

110"%SI I*ple*entation ,f -ast Addition sin! 3uaternar( Si!ned $i!it <u*ber

S(ste*( &011 I222

Head Ofce: #302, 3

nd

Floor, Gyan Arcade, Ammerpet, HYDERABAD-00 0!2"

E-ma#l: m"$"r"pro%ect$"#eee&'ma#l"com, (e): Face)oo*"com+m"$"r"pro%ect , R#n'

on: ,-. -!./0/./2

MSR PROJECTS

(AN SSI CERTIFIED INSTITUTION)

TRAINING | DEVELOPMENT |

PLACEMENTS

1&0$esi!n And I*ple*entation ,f Truncated Multipliers -or .recision I*prove*ent0 ( &011

I222 )

Head Ofce: #302, 3

nd

Floor, Gyan Arcade, Ammerpet, HYDERABAD-00 0!2"

E-ma#l: m"$"r"pro%ect$"#eee&'ma#l"com, (e): Face)oo*"com+m"$"r"pro%ect , R#n'

on: ,-. -!./0/./2

Potrebbero piacerti anche

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

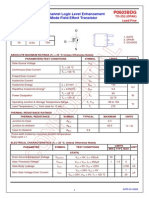

- P0603BDGDocumento5 pagineP0603BDGguvenelktNessuna valutazione finora

- Midterm II - Solutions: NameDocumento9 pagineMidterm II - Solutions: NameDGMCNessuna valutazione finora

- Data Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorDocumento13 pagineData Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorSsr ShaNessuna valutazione finora

- Field Effect TransistorDocumento26 pagineField Effect TransistorsalahuddinNessuna valutazione finora

- Cmos Inverter Cicuit Using PspiceDocumento4 pagineCmos Inverter Cicuit Using PspiceShreerama Samartha G Bhatta100% (2)

- SramDocumento31 pagineSramParth RamanujNessuna valutazione finora

- Field Effect Transistor (FET) : Dr. Gufran AhmadDocumento46 pagineField Effect Transistor (FET) : Dr. Gufran AhmadAnkit Meena100% (1)

- What Are The Advantages and Disadvantages of The FinFET TechnologyDocumento3 pagineWhat Are The Advantages and Disadvantages of The FinFET TechnologySajan BeheraNessuna valutazione finora

- MOS Circuit DesignDocumento46 pagineMOS Circuit Designdivyansh kaliaNessuna valutazione finora

- SMD-PHILIPS Marking Codes Small Signal Transistors and DiodesDocumento131 pagineSMD-PHILIPS Marking Codes Small Signal Transistors and Diodesmeng79865190% (10)

- TN 104: Introduction To Electronics Engineering: LECTURE # 3: Bipolar Junction Transistor (BJT)Documento43 pagineTN 104: Introduction To Electronics Engineering: LECTURE # 3: Bipolar Junction Transistor (BJT)Mtakatifu Wa IINessuna valutazione finora

- Dual N-Channel Enhancement Mode Field Effect Transistor: Absolute Maximum Ratings (T 25 C Unless Otherwise Noted)Documento7 pagineDual N-Channel Enhancement Mode Field Effect Transistor: Absolute Maximum Ratings (T 25 C Unless Otherwise Noted)miguel angel jaramilloNessuna valutazione finora

- EC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutDocumento12 pagineEC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutM KIRITI SAI KUMARNessuna valutazione finora

- Stacked Nanosheet Gate-All-Around Transistor Scaling Beyond FinFETDocumento2 pagineStacked Nanosheet Gate-All-Around Transistor Scaling Beyond FinFETGary Ryan DonovanNessuna valutazione finora

- MikrotikDocumento5 pagineMikrotikPrem KumarNessuna valutazione finora

- Chapter - 1 Bipolar Junction Transistor Transistor Principle of OperationDocumento45 pagineChapter - 1 Bipolar Junction Transistor Transistor Principle of OperationDeepak SharmaNessuna valutazione finora

- Kakatiya Institute of Technology & Science, Warangal-506015Documento2 pagineKakatiya Institute of Technology & Science, Warangal-506015WARRIOR GamingNessuna valutazione finora

- Lecture 1 - MOSFETsDocumento92 pagineLecture 1 - MOSFETsnqwvch8dcdNessuna valutazione finora

- ECE Lab ReportDocumento31 pagineECE Lab ReportChristian Laettner GarciaNessuna valutazione finora

- 13-Chapter 13 - TransistorsDocumento28 pagine13-Chapter 13 - Transistorssrinu247100% (3)

- PVT, RC Variation, OcvDocumento5 paginePVT, RC Variation, OcvmayurNessuna valutazione finora

- Common Emitter Transistor Characteristics PDFDocumento2 pagineCommon Emitter Transistor Characteristics PDFMayra100% (1)

- Power-Electronics Power-Transistors NotesDocumento37 paginePower-Electronics Power-Transistors NotesRAJ KUMAR SHIHINessuna valutazione finora

- Hikmat o Kalam K Imam Fazl e Haq by Mufti Abdul Hakeem Sharf QadriDocumento30 pagineHikmat o Kalam K Imam Fazl e Haq by Mufti Abdul Hakeem Sharf QadrisunnivoiceNessuna valutazione finora

- E MOSFET WorkingDocumento14 pagineE MOSFET WorkingSubhash YadavNessuna valutazione finora

- UntitledDocumento25 pagineUntitledAconatic tvhomeNessuna valutazione finora

- Bălan Mihai 342B2 Referat VLSIDocumento50 pagineBălan Mihai 342B2 Referat VLSIMihai BălanNessuna valutazione finora

- Ebin - Pub Digital Principles and Circuits 1nbsped 9789350433195 9788183184861Documento468 pagineEbin - Pub Digital Principles and Circuits 1nbsped 9789350433195 9788183184861vowan44398Nessuna valutazione finora

- Bipolar Junction Transistors (BJT) BasicsDocumento8 pagineBipolar Junction Transistors (BJT) BasicsApurva NagdeoteNessuna valutazione finora

- BSIM470 Manual PDFDocumento184 pagineBSIM470 Manual PDF高慶樺Nessuna valutazione finora