Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Description

Caricato da

greentea601Descrizione originale:

Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Description

Caricato da

greentea601Copyright:

Formati disponibili

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

1

OCTOBER 2009 MILITARY AND INDUSTRIAL TEMPERATURE RANGES

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2009 Integrated Device Technology, Inc. DSC-5496/6

FEATURES:

Std., A, and C grades

Low input and output leakage 1A (max.)

CMOS power levels

True TTL input and output compatibility:

VOH = 3.3V (typ.)

VOL = 0.3V (typ.)

High Drive outputs (-15mA IOH, 48mA IOL)

Meets or exceeds JEDEC standard 18 specifications

Military product compliant to MIL-STD-883, Class B and DESC

listed (dual marked)

Power off disable outputs permit "live insertion"

Available in the following packages:

Industrial: SOIC, SSOP, QSOP

Military: CERDIP, LCC

FUNCTIONAL BLOCK DIAGRAM

IDT54/74FCT373T/AT/CT FAST CMOS OCTAL

TRANSPARENT LATCH

DESCRIPTION:

The FCT373Tis an octal transparent latch built using an advanced dual

metal CMOS technology. These octal latches have 3-state outputs and are

intended for bus oriented applications. The flip-flops appear transparent to

the data when Latch Enable (LE) is high. When LE is low, the data that meets

the set-up time is latched. Data appears on the bus when the Output Enable

(OE) is low. When OE is high, the bus output is in the high-impedance state.

LE

D

G

O

O0

D0

D

G

O

O1

D1

D

G

O

O2

D2

D

G

O

O3

D3

D

G

O

O4

D4

D

G

O

O5

D5

D

G

O

O6

D6

D

G

O

O7

D7

OE

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

2

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

PIN CONFIGURATION

Symbol Description Max Unit

VTERM

(2)

Terminal Voltage with Respect to GND 0.5 to +7 V

VTERM

(3)

Terminal Voltage with Respect to GND 0.5 to VCC+0.5 V

TSTG Storage Temperature 65 to +150 C

IOUT DC Output Current 60 to +120 mA

ABSOLUTE MAXIMUM RATINGS

(1)

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability. No terminal voltage may exceed

Vcc by +0.5V unless otherwise noted.

2. Inputs and Vcc terminals only.

3. Output and I/O terminals only.

Pin Names Description

Dx Data Inputs

LE Latch Enable Input (Active HIGH)

OE Output Enable Input (Active LOW)

Ox 3-State Outputs

PIN DESCRIPTION

Symbol Parameter

(1)

Conditions Typ. Max. Unit

CIN Input Capacitance VIN = 0V 6 10 pF

COUT Output Capacitance VOUT = 0V 8 12 pF

CAPACITANCE (TA = +25C, F = 1.0MHz)

NOTE:

1. This parameter is measured at characterization but not tested.

NOTE:

1. H = HIGH Voltage Level

X = Dont Care

L = LOW Voltage Level

Z = High Impedance

FUNCTION TABLE

(1)

Inputs Outputs

Dx LE OE Ox

H H L H

L H L L

X X H Z

CERDIP/ SOIC/ SSOP/ QSOP

TOP VIEW

2

3

1

16

15

14

11

19

18

20

17

13

12

5

6

7

4

8

9

10

D1

O0

D0

VCC

O1

D3

O2

D2

O3

GND

O7

O6

D7

D6

O5

O4

D5

D4

LE

OE

1

2 3

4

5

7

9

6

8

10 11 12 13

14

15

16

17

18

19 20

O6

D7

D6

O5

D5

D

0

O

0

O

3

G

N

D

L

E

O

4

D

4

O

E

V

C

C

O

7 INDEX

D1

O1

D3

O2

D2

LCC

TOP VIEW

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

3

Symbol Parameter Test Conditions

(1)

Min. Typ.

(2)

Max. Unit

VIH Input HIGH Level Guaranteed Logic HIGH Level 2 V

VIL Input LOW Level Guaranteed Logic LOW Level 0.8 V

IIH Input HIGH Current

(4)

VCC = Max. VI = 2.7V 1 A

IIL Input LOW Current

(4)

VCC = Max. VI = 0.5V 1 A

IOZH High Impedance Output Current VCC = Max VO = 2.7V 1 A

IOZL (3-State output pins)

(4)

VO = 0.5V 1

II Input HIGH Current

(4)

VCC = Max., VI = VCC (Max.) 1 A

VIK Clamp Diode Voltage VCC = Min, IIN = -18mA 0.7 1.2 V

VH Input Hysteresis 200 mV

ICC Quiescent Power Supply Current VCC = Max., VIN = GND or VCC 0.01 1 mA

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: TA = 40C to +85C, VCC = 5.0V 5%; Military: TA = 55C to +125C, VCC = 5.0V 10%

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at VCC = 5.0V, +25C ambient.

3. Not more than one output should be tested at one time. Duration of the test should not exceed one second.

4. The test limit for this parameter is 5A at TA = 55C.

5. This parameter is guaranteed but not tested.

Symbol Parameter Test Conditions

(1)

Min. Typ.

(2)

Max. Unit

VOH Output HIGH Voltage VCC = Min IOH = 6mA MIL 2.4 3.3

VIN = VIH or VIL IOH = 8mA IND V

IOH = 12mA MIL 2 3

IOH = 15mA IND

VOL Output LOW Voltage VCC = Min IOL = 32mA MIL 0.3 0.5 V

VIN = VIH or VIL IOL = 48mA IND

IOS Short Circuit Current VCC = Max., VO = GND

(3)

60 120 225 mA

IOFF Input/Output Power Off Leakage

(5)

VCC = 0V, VIN or VO 4.5V 1 A

OUTPUT DRIVE CHARACTERISTICS

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

4

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

Symbol Parameter Test Conditions

(1)

Min. Typ.

(2)

Max. Unit

ICC Quiescent Power Supply Current VCC = Max. 0.5 2 mA

TTL Inputs HIGH VIN = 3.4V

(3)

ICCD Dynamic Power Supply VCC = Max. VIN = VCC 0.15 0.25 mA/

Current

(4)

Outputs Open VIN = GND MHz

OE = GND

One Input Toggling

50% Duty Cycle

IC Total Power Supply Current

(6)

VCC = Max. VIN = VCC 1.5 3.5 mA

Outputs Open VIN = GND

fi = 10MHz

50% Duty Cycle VIN = 3.4V 1.8 4.5

OE = GND VIN = GND

LE = VCC

One Bit Toggling

VCC = Max. VIN = VCC 3 6

(5)

mA

Outputs Open VIN = GND

fi = 2.5MHz

50% Duty Cycle VIN = 3.4V 5 14

(5)

OE = GND VIN = GND

LE = VCC

Eight Bits Toggling

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at VCC = 5.0V, +25C ambient.

3. Per TTL driven input; (VIN = 3.4V). All other inputs at VCC or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of ICC formula. These limits are guaranteed but not tested.

6. IC = IQUIESCENT + IINPUTS + IDYNAMIC

IC = ICC + ICC DHNT + ICCD (fCP/2+ fiNi)

ICC = Quiescent Current

ICC = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current caused by an Input Transition Pair (HLH or LHL)

fCP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

fi = Output Frequency

Ni = Number of Outputs at fi

All currents are in milliamps and all frequencies are in megahertz.

POWER SUPPLY CHARACTERISTICS

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

5

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. This parameter is guaranteed but not tested.

74FCT373AT 74FCT373CT

Symbol Parameter Condition

(1)

Min.

(2)

Max. Min.

(2)

Max. Unit

tPLH Propagation Delay CL = 50pF 1.5 5.2 1.5 4.2 ns

tPHL Dx to Ox RL = 500

tPLH Propagation Delay 2 8.5 2 5.5 ns

tPHL LE to Ox

tPZH Output Enable Time 1.5 6.5 1.5 5.5 ns

tPZL

tPHZ Output Disable Time 1.5 5.5 1.5 5 ns

tPLZ

tSU Set-up Time HIGH or LOW, Dx to LE 2 2 ns

tH Hold Time HIGH or LOW, Dx to LE 1.5 1.5 ns

tW LE Pulse Width HIGH

(3)

5 5 ns

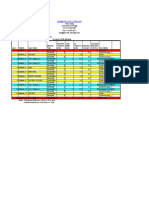

SWITCHING CHARACTERISTICS OVER OPERATING RANGE - INDUSTRIAL

54FCT373T 54FCT373AT 54FCT373CT

Symbol Parameter Condition

(1)

Min.

(2)

Max. Min.

(2)

Max. Min.

(2)

Max. Unit

tPLH Propagation Delay CL = 50pF 1.5 8.5 1.5 5.6 1.5 5.1 ns

tPHL Dx to Ox RL = 500

tPLH Propagation Delay 2 15 2 9.8 2 8 ns

tPHL LE to Ox

tPZH Output Enable Time 1.5 13.5 1.5 7.5 1.5 6.3 ns

tPZL

tPHZ Output Disable Time 1.5 10 1.5 6.5 1.5 5.9 ns

tPLZ

tSU Set-up Time HIGH or LOW, Dx to LE 2 2 2 ns

tH Hold Time HIGH or LOW, Dx to LE 1.5 1.5 1.5 ns

tW LE Pulse Width HIGH

(3)

6 6 6 ns

SWITCHING CHARACTERISTICS OVER OPERATING RANGE - MILITARY

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

6

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

Pulse

Generator

RT

D.U.T

.

VCC

VIN

C L

VOUT

50pF

500W

500W

7.0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

DATA

INPUT

TIMING

INPUT

ASYNCHRONOUS CONTROL

PRESET

CLEAR

ETC.

SYNCHRONOUS CONTROL

tSU tH

tREM

tSU

tH

HIGH-LOW-HIGH

PULSE

LOW-HIGH-LOW

PULSE

tW

1.5V

1.5V

SAME PHASE

INPUT TRANSITION

3V

1.5V

0V

1.5V

VOH

tPLH

OUTPUT

OPPOSITE PHASE

INPUT TRANSITION

3V

1.5V

0V

tPLH tPHL

tPHL

VOL

CONTROL

INPUT

3V

1.5V

0V

3.5V

0V

OUTPUT

NORMALLY

LOW

OUTPUT

NORMALLY

HIGH

SWITCH

CLOSED

SWITCH

OPEN

VOL

0.3V

0.3V

tPLZ tPZL

tPZH tPHZ

3.5V

0V

1.5V

1.5V

ENABLE DISABLE

VOH

PRESET

CLEAR

CLOCK ENABLE

ETC.

Octal Link

Octal Link

Octal Link

Octal Link

Octal Link

TEST CIRCUITS AND WAVEFORMS

Propagation Delay

Test Circuits for All Outputs

Enable and Disable Times

Set-Up, Hold, and Release Times

Pulse Width

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

2. Pulse Generator for All Pulses: Rate 1.0MHz; tF 2.5ns; tR 2.5ns.

Test Switch

Open Drain

Disable Low Closed

Enable Low

All Other Tests Open

SWITCH POSITION

DEFINITIONS:

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

MILITARY AND INDUSTRIAL TEMPERATURE RANGES

IDT54/74FCT373T/AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

7

ORDERING INFORMATION

XX

Temp. Range

FCT

XXXX

Device Type

XX

Package

X

Process

Fast CMOS Octal Transparent Latch

373T

373AT

373CT

SOG

PYG

QG

Industrial Options

Small Outline IC - Green

Shrink Small Outline Package - Green

Quarter-size Small Outline Package - Green

D

L

Military Options

CERDIP

Leadless Chip Carrier

Blank

B

Industrial

MIL-STD-883, Class B

54

74

55 C to +125 C

40 C to +85 C

CORPORATE HEADQUARTERS for SALES: for Tech Support:

6024 Silver Creek Valley Road 800-345-7015 or 408-284-8200 logichelp@idt.com

San Jose, CA 95138 fax: 408-284-2775

www.idt.com

Datasheet Document History

10/03/09 Pg. 7 Updated the ordering information by removing the "IDT" notation and non RoHS part.

Potrebbero piacerti anche

- IDT74FCT521AT/CT Fast Cmos 8-Bit Identity Comparator: Features: DescriptionDocumento6 pagineIDT74FCT521AT/CT Fast Cmos 8-Bit Identity Comparator: Features: DescriptionAnonymous T9HtUYccYANessuna valutazione finora

- DatasheetDocumento9 pagineDatasheetLuis Caba RamirezNessuna valutazione finora

- CMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionDocumento10 pagineCMOS Static RAM 256K (32K X 8-Bit) IDT71256S IDT71256L: Features DescriptionantoninoxxxNessuna valutazione finora

- DM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionDocumento6 pagineDM7414 Hex Inverter With Schmitt Trigger Inputs: General DescriptionGeorge Rahul PaulNessuna valutazione finora

- 74164Documento6 pagine74164luisalex87Nessuna valutazione finora

- Low Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesDocumento13 pagineLow Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesMohammad SoltanmohammadiNessuna valutazione finora

- Fast Cmos Octal Bus Transceiver (Open Drain) : Features: DescriptionDocumento6 pagineFast Cmos Octal Bus Transceiver (Open Drain) : Features: DescriptionEnéas BaroneNessuna valutazione finora

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocumento10 pagineCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNessuna valutazione finora

- 74LS73Documento5 pagine74LS73Cristin BarnesNessuna valutazione finora

- Mid Semester 2012 TID203Documento17 pagineMid Semester 2012 TID203peas002Nessuna valutazione finora

- 27C512Documento12 pagine27C512technicalavrNessuna valutazione finora

- 74LS573Documento6 pagine74LS573Sinué RamírezNessuna valutazione finora

- CMOS Static RAM 16K (2K X 8-Bit) IDT6116SA IDT6116LA: Features DescriptionDocumento11 pagineCMOS Static RAM 16K (2K X 8-Bit) IDT6116SA IDT6116LA: Features DescriptionFrancis Quintana JaramilloNessuna valutazione finora

- DM7486Documento6 pagineDM7486kenshinbhNessuna valutazione finora

- Data SheetDocumento6 pagineData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNessuna valutazione finora

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocumento6 pagineOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Nessuna valutazione finora

- 32kx8bit CMOS SRAM: HY62256B SeriesDocumento9 pagine32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieNessuna valutazione finora

- Octal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesDocumento11 pagineOctal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesIsaacNessuna valutazione finora

- Datasheet 74HCT14Documento7 pagineDatasheet 74HCT14Humberto AcostaNessuna valutazione finora

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocumento11 pagine74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNessuna valutazione finora

- Single Bilateral Switch: Order CodesDocumento11 pagineSingle Bilateral Switch: Order CodesGaryTechNessuna valutazione finora

- Uc 3845Documento23 pagineUc 3845Bahram RN100% (1)

- TL494 Pulse-Width-Modulation Control Circuits: Features DescriptionDocumento21 pagineTL494 Pulse-Width-Modulation Control Circuits: Features DescriptionMaria GhitaNessuna valutazione finora

- 74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and OutputsDocumento13 pagine74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputsfenixtec1Nessuna valutazione finora

- 27C020Documento11 pagine27C020technicalavrNessuna valutazione finora

- DatasheetDocumento8 pagineDatasheetMaizatul Hanisah RoziNessuna valutazione finora

- 74VHCT374A Octal D-Type Flip-Flop With 3-STATE Outputs: Features General DescriptionDocumento9 pagine74VHCT374A Octal D-Type Flip-Flop With 3-STATE Outputs: Features General DescriptionΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNessuna valutazione finora

- D D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And GatesDocumento8 pagineD D D D D D D D D D D D D: CD74HC08-Q1 Quadruple 2-Input Positive-And Gatesmalirezazadeh5549Nessuna valutazione finora

- 74LS86P PDFDocumento6 pagine74LS86P PDFOsman KoçakNessuna valutazione finora

- TC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderDocumento9 pagineTC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderAndrea DispoNessuna valutazione finora

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocumento7 pagineMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNessuna valutazione finora

- 74LS393-Dual 4-Bit Binary CounterDocumento6 pagine74LS393-Dual 4-Bit Binary Counterkakashi116Nessuna valutazione finora

- Dual D-Type Flip-Flop: Integrated CircuitsDocumento8 pagineDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNessuna valutazione finora

- 74 HC 138Documento5 pagine74 HC 138dlbplbNessuna valutazione finora

- 74ACT244Documento9 pagine74ACT244ThanhNessuna valutazione finora

- CD4047Documento9 pagineCD4047Haryadi VjNessuna valutazione finora

- DM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionDocumento6 pagineDM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionNicolas Yesenia VictorNessuna valutazione finora

- 74LS574Documento6 pagine74LS574aminotepNessuna valutazione finora

- High-Performance Ee PLD ATF16V8C: FeaturesDocumento18 pagineHigh-Performance Ee PLD ATF16V8C: FeaturesAmol LandgeNessuna valutazione finora

- Data SheetDocumento10 pagineData SheetMahua ChandaNessuna valutazione finora

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocumento7 pagineUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitEnica LiviaNessuna valutazione finora

- D D D D D: SN74CBT3126 Quadruple Fet Bus SwitchDocumento4 pagineD D D D D: SN74CBT3126 Quadruple Fet Bus SwitchRicky CoxNessuna valutazione finora

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocumento9 pagineHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProNessuna valutazione finora

- Datasheet CPLDDocumento16 pagineDatasheet CPLDFrancisco Ramferi García BedollaNessuna valutazione finora

- 7Z08Documento7 pagine7Z08André Frota PaivaNessuna valutazione finora

- 24AA512/24LC512/24FC512: 512K I C Cmos Serial EepromDocumento28 pagine24AA512/24LC512/24FC512: 512K I C Cmos Serial EepromAitor DuoNessuna valutazione finora

- Apl 5336Documento20 pagineApl 5336FlavianoSilvaNessuna valutazione finora

- 74LS175Documento3 pagine74LS175Yesenia RojoNessuna valutazione finora

- CLAA150XP01QDocumento21 pagineCLAA150XP01QSergio Alvarez BarajasNessuna valutazione finora

- Features: TL494 Pulse-Width-Modulation Control CircuitsDocumento20 pagineFeatures: TL494 Pulse-Width-Modulation Control Circuitskeyboard2014Nessuna valutazione finora

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocumento9 pagine74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionMalik Mian Manzer MithaNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDa EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNessuna valutazione finora

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Documento8 pagineMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Nessuna valutazione finora

- MC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: DescriptionDocumento8 pagineMC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: Descriptiongreentea601Nessuna valutazione finora

- MC14099B 8-Bit Addressable Latches: Marking DiagramsDocumento8 pagineMC14099B 8-Bit Addressable Latches: Marking Diagramsgreentea601Nessuna valutazione finora

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDocumento9 pagineNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601Nessuna valutazione finora

- MC14042B Quad Transparent Latch: Marking DiagramsDocumento7 pagineMC14042B Quad Transparent Latch: Marking Diagramsgreentea601Nessuna valutazione finora

- NL17SG373 Low-Power D-Type Transparent Latch With 3-State OutputDocumento10 pagineNL17SG373 Low-Power D-Type Transparent Latch With 3-State Outputgreentea601Nessuna valutazione finora

- 3-BIT 4:1 Mux-Latch: Features DescriptionDocumento4 pagine3-BIT 4:1 Mux-Latch: Features Descriptiongreentea601Nessuna valutazione finora

- Prices Are Subject To Change Without Prior Notice.: Mediapro TechnologyDocumento25 paginePrices Are Subject To Change Without Prior Notice.: Mediapro Technologygreentea601100% (1)

- Laser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008Documento9 pagineLaser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008greentea601Nessuna valutazione finora

- International Pte LTD: Asus R9 290 4GB GDDR5Documento6 pagineInternational Pte LTD: Asus R9 290 4GB GDDR5greentea601Nessuna valutazione finora

- SAF1562Documento97 pagineSAF1562greentea601Nessuna valutazione finora

- 74AHC259 74AHCT259: 1. General DescriptionDocumento17 pagine74AHC259 74AHCT259: 1. General Descriptiongreentea601Nessuna valutazione finora

- Cymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PRODocumento2 pagineCymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PROgreentea601Nessuna valutazione finora

- IPC 4101 B Slash Sheet MatrixDocumento4 pagineIPC 4101 B Slash Sheet Matrixgreentea601Nessuna valutazione finora

- ADC Driver Selection Guide FinalDocumento2 pagineADC Driver Selection Guide Finalgreentea601Nessuna valutazione finora

- Flash Memory TestingDocumento75 pagineFlash Memory Testinggreentea601Nessuna valutazione finora

- 2468 V 33 StackupDocumento1 pagina2468 V 33 Stackupgreentea601Nessuna valutazione finora

- Part 1 - Introduction To ARM and The Basics of Microcontroller ProgrammingDocumento61 paginePart 1 - Introduction To ARM and The Basics of Microcontroller ProgrammingjikruNessuna valutazione finora

- PIC16F628Documento30 paginePIC16F628Prince YehyaNessuna valutazione finora

- DLD ManualDocumento45 pagineDLD ManualMuhammad UmerNessuna valutazione finora

- High Performance Voltage Comparators: Semiconductor Technical DataDocumento9 pagineHigh Performance Voltage Comparators: Semiconductor Technical DataUlises AvellanedaNessuna valutazione finora

- Preliminary Assignment A1-001-A Izaidi Bin Wan Ibrahim - GIT 0763Documento2 paginePreliminary Assignment A1-001-A Izaidi Bin Wan Ibrahim - GIT 0763Adam CkNessuna valutazione finora

- MCQS - Mid CS302 Solved PDFDocumento19 pagineMCQS - Mid CS302 Solved PDFattiqueNessuna valutazione finora

- Digital Logic NotesDocumento79 pagineDigital Logic NotesRohini PendhariNessuna valutazione finora

- DSY2602-S1-2022-Major Test 2Documento2 pagineDSY2602-S1-2022-Major Test 2Tshepiso MaileNessuna valutazione finora

- LP621024D Series: 128K X 8 Bit Cmos SramDocumento16 pagineLP621024D Series: 128K X 8 Bit Cmos SramClaudiney BricksNessuna valutazione finora

- 5051 AppDocumento37 pagine5051 AppawemetalNessuna valutazione finora

- 16F54Documento90 pagine16F54SHAHID_71Nessuna valutazione finora

- Impresora CitizenDocumento50 pagineImpresora CitizenRUDILLA66Nessuna valutazione finora

- Sensor I18H008 Data SheetDocumento2 pagineSensor I18H008 Data SheetJose AyalaNessuna valutazione finora

- CXO 7050 Rev 14.3.13 PDFDocumento1 paginaCXO 7050 Rev 14.3.13 PDFrajaramghoshNessuna valutazione finora

- LOGIC GATES USING TRANSISTORS Digital TechniquesDocumento19 pagineLOGIC GATES USING TRANSISTORS Digital Techniquesmohit moreNessuna valutazione finora

- Rohini 74049417647Documento5 pagineRohini 74049417647Aakash SharmaNessuna valutazione finora

- UM245R USB - Parallel (LPT) FIFO PDFDocumento27 pagineUM245R USB - Parallel (LPT) FIFO PDFZip DriverNessuna valutazione finora

- Siemens PLM LMS Torsional Vibration WP Tcm78 228179Documento19 pagineSiemens PLM LMS Torsional Vibration WP Tcm78 228179liu123yongNessuna valutazione finora

- DCS Objective QuestionDocumento20 pagineDCS Objective QuestionravigwlNessuna valutazione finora

- DDPP4 TOCwebDocumento8 pagineDDPP4 TOCwebravindarsinghNessuna valutazione finora

- Specification of AS32 TTL 100Documento23 pagineSpecification of AS32 TTL 100thato69Nessuna valutazione finora

- KM 62256Documento9 pagineKM 62256roozbehxoxNessuna valutazione finora

- Characteristics of Digital IC'sDocumento2 pagineCharacteristics of Digital IC'ssudipta ghosh0% (1)

- Quantum Devices 2011 CatalogDocumento21 pagineQuantum Devices 2011 CatalogServo2GoNessuna valutazione finora

- Mc74hc02a DDocumento7 pagineMc74hc02a Ddaniel5morales5castaNessuna valutazione finora

- AlTek PickupsDocumento40 pagineAlTek PickupsLuis Alfonso Andler C.100% (1)

- Inf lm566cn PDFDocumento7 pagineInf lm566cn PDFCamilo andres Acosta romeroNessuna valutazione finora

- ADM705 ADM706 ADM707 ADM708: Low Cost Microprocessor Supervisory CircuitsDocumento12 pagineADM705 ADM706 ADM707 ADM708: Low Cost Microprocessor Supervisory CircuitsNicolae FeraruNessuna valutazione finora

- DS TTL-232RG Cables PDFDocumento18 pagineDS TTL-232RG Cables PDFBurak YılmazNessuna valutazione finora

- Driver HMI Red Lion G306A DatasheetDocumento11 pagineDriver HMI Red Lion G306A DatasheetDiego FernandezNessuna valutazione finora