Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

0.5-V Input Digital LDO With 98.7% Current Efficiency and 2.7-ΜA Quiescent Current in 65nm CMOS

Caricato da

Karim H. MohamedCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

0.5-V Input Digital LDO With 98.7% Current Efficiency and 2.7-ΜA Quiescent Current in 65nm CMOS

Caricato da

Karim H. MohamedCopyright:

Formati disponibili

0.

5-V Input Digital LDO

with 98.7% Current Efficiency and

2.7-A Quiescent Current in 65nm CMOS

Yasuyuki Okuma

1

, Koichi Ishida

2

, Yoshikatsu Ryu

1

, Xin Zhang

2

, Po-Hung Chen

2

,

Kazunori Watanabe

1

, Makoto Takamiya

2

, and Takayasu Sakurai

2

1

Semiconductor Technology Academic Research Center (STARC),

3-17-2 Shin Yokohama, Kohoku-ku, Yokohama 222-0033, J apan

2

The University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, J apan

Abstract- Digital LDO is proposed to provide the low noise and

tunable power supply voltage to the 0.5-V near-threshold logic

circuits. Because the conventional LDO feedback-controlled by

the operational amplifier fail to operate at 0.5V, the digital LDO

eliminates all analog circuits and is controlled by digital circuits,

which enables the 0.5-V operation. The developed digital LDO in

65nm CMOS achieved the 0.5-V input voltage and 0.45-V output

voltage with 98.7% current efficiency and 2.7-A quiescent

current at 200-A load current. Both the input voltage and the

quiescent current are the lowest values in the published LDOs,

which indicates the good energy efficiency of the digital LDO at

0.5-V operation.

I. INTRODUCTION

Very low-voltage operation of VLSI's is effective in

reducing both dynamic and leakage power and the maximum

energy efficiency is achieved at low power supply voltage

(V

DD

) below 0.5V (e.g., 340 mV [1] and 320 mV [2]). Thus,

many works have been carried out on the sub/near-threshold

logic circuits [1-5]. Stable and tunable V

DD

(e.g., 320 mV

50mV [2]) is required in the near-threshold logic circuits,

because the gate delay in the near-threshold logic circuits is

very sensitive to V

DD

and the process variations. Therefore, a

0.5-V LDO enabling the low ripple and tunable V

DD

is

strongly required. The conventional analog LDO, however,

fails to operate at 0.5V. In order to solve the problem, the

digital LDO enabling the 0.5-V operation is proposed and

demonstrated in this paper. The concept and the circuit

implementation of the proposed digital LDO is shown in

Section II. Measurement results from 65-nm CMOS test chips

are described in Section III.

II. PROPOSED DIGITAL LDO

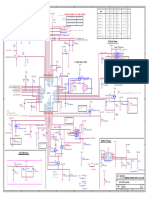

In order to explain the concept of the proposed digital

LDO, Fig. 1 shows the circuit schematic of the digital LDO in

contrast with the conventional analog LDO. The conventional

analog LDO shown in Fig. 1(a) consists of an operational

amplifier and a power transistor. The conventional LDO fails

to operate at 0.5V, because the operational amplifier does not

operate at 0.5V and can not control the analog gate voltage of

the power transistor. In order to solve the problem, the digital

LDO shown in Fig. 1(b) is proposed. The digital LDO

includes a switch array, a comparator, and a digital controller.

The analog controlled power transistor is replaced with the

switch array and the number of turned-on switches is changed

digitally by the controller. The output voltage (V

OUT

) is

monitored by the comparator instead of the operational

amplifier. Thus, the digital LDO eliminates all analog circuits

and is controlled by digital circuits, which enables the 0.5-V

LDO operation, because the digital circuits including the

comparator can operate at 0.5V.

Fig. 2 shows is the circuit schematic of the fabricated

digital LDO. The digital LDO consists of a comparator, a

serial-in parallel-out bi-directional shift register, and switch

array of 256 pMOS FETs. In order to reduce the ripple due to

the switching of the switches, in this implementation, the shift

register is used as the controller, because the number of

switching in the switch array is only one at each clock edge.

The typical input voltage (V

IN

) and V

OUT

are 0.5V and 0.45V,

respectively. The typical clock frequency of the comparator

and the shift register is 1MHz. The off-chip decoupling

V

REF

V

IN

V

OUT

L

o

a

d

Analog

(a)

V

IN

M

1

M

2

M

3

M

n

V

OUT

V

REF

C

o

n

t

r

o

l

l

e

r

n-bit

digital

L

o

a

d

Comparator

(b)

Fig. 1. (a) Conventional analog LDO. (b) Proposed digital LDO.

978-1-4244-5759-5/10/$26.00 2010 IEEE

capacitor is 100nF and the typical load current (I

LOAD

) is

200A.

Fig. 3 shows the circuit schematic of the clocked

comparator used in the digital LDO. In the design of LDO

with I

LOAD

of 200A, low quiescent current is very important,

because the large quiescent current degrades the current

efficiency of LDO. In order to reduce the quiescent current,

the clocked comparator is used in the digital LDO, because the

clocked comparator can operate at 0.5V and consumes no DC-

power.

Fig. 4(a) shows the operation of the bi-directional shift

register. At first, all 256 bits are set to 1 in order to turn off

all pMOS switches. After that, when the comparator output

(Compout) is low, which means V

OUT

is lower than the

reference voltage (V

REF

), all 256 bits are shifted toward right

in order to increase the number of turned-on switches. In

contrast, when Compout is high, which means V

OUT

is higher

than V

REF

, all 256 bits are shifted toward left in order to

decrease the number of turned-on switches.

Fig. 4(b) shows the circuit implementation of the serial-in

parallel-out bi-directional shift register. The bi-directional

shift register consists of selectors and D-FFs. The shift-right

or the shift-left operation of the bi-directional shift register is

determined by Compout. When Compout is low, each Q

K

except Q

1

moves to Q

K+1

, and Q

1

is set to 0, which achieves

the shift-right operation. In contrast, when Compout is high,

each Q

K

except Q

256

moves to Q

K-1

, and Q

256

is set to 1,

which achieves the shift-left operation.

Fig. 5 shows the schematic of the transient of the number

of turned-on switches in order to explain the feedback control

of the digital LDO. The digital LDO controls the number of

turned-on switches at each clock edge depending on Compout.

When V

OUT

equals to V

REF

, the number of turned-on switches

changes up and down by 1-bit, which determines the ripple of

the digital LDO.

III. MEASUREMENT RESULTS AND DISCUSSION

To demonstrate the advantage of the proposed digital LDO,

a test chip is fabricated in 65nm CMOS. Fig. 6 shows the chip

microphotograph and the layout. The total chip area including

pads is 0.90.8mm

2

and the active area of the digital LDO is

0.042mm

2

.

Fig. 7(a) shows measured V

OUT

V

IN

characteristics at

I

LOAD

of 200A. V

REF

is varied from 0.35V to 0.55V by 0.05-

V step. The digital LDO successfully regulates V

OUT

from

0.35 to 0.45V at V

IN

of 0.5V. At the design target of V

IN

of

0.5V and V

OUT

of 0.45V, the dropout voltage is 50mV and the

measured line regulation is 3.1mV/V. Fig. 7(b) shows

measured V

OUT

V

IN

characteristics at V

REF

of 0.45V. I

LOAD

is

varied from 20A to 200A. The LDO achieves a successful

load regulation of 0.65mV/mA with V

IN

from 0.5V to 1.2V.

Fig. 8 shows the measured I

LOAD

dependence of the current

efficiency and the quiescent currents at 1-MHz and 10-MHz

clock. Thanks to the digital LDO architecture, the measured

quiescent current does not depend on I

LOAD

, though the

quiescent current increases with I

LOAD

in the conventional

analog LDO. At 1-MHz clock, the measured quiescent current

Clk

V

OUT

V

REF

Compout

Fig. 3. Circuit schematic of clocked comparator used in digital LDO.

0 1

1

Q

1

Q

256

Q

k+1

Q

k+2

Q

k

Q

k-1

1 1 1 1 1

0 0 0 1 1 1

0 0 0 0 1 1

0 0 1 1 1 1

(ii) Step = x

(iii-a) Step = x+1

(when Compout = L)

(iii-b) Step = x+1

(when Compout = H)

All 1 = All switches are turned off.

Shift left

Shift right

(i) Initialize

(Step = 0)

(a)

D Q D Q D Q D Q

Q

1

Q

k+1

Q

k

Q

k-1

0

Q

1

Q

256

Q

k-1

Q

k+1

Q

255

Q

k

Q

255

Q

2

S S S S

Clk

Set

Compout

1

Q

k+2

(b)

Fig. 4. (a) Operation of bi-directional shift register. (b) Circuit

implementation of serial-in parallel-out bi-directional shift register.

Step

Number of turned-on switches

256

0

Target

Fig. 5. Schematic of the transient of the number of turned-on switches in

order to explain feedback control of digital LDO.

V

IN

(0.5V)

Q

1

Q

2

Q

3

Q

256

V

OUT

(0.45V)

V

REF

(0.45V)

Serial-in

parallel-out

bi-directional

shift register

(Fig. 4(b))

Compout

Switch array

100nF

On chip Off chip

I

LOAD

(200A)

Clk

(1MHz)

Fig. 2. Circuit schematic of the fabricated digital LDO.

is 2.7A, which is the smallest quiescent current in LDOs to

the authors knowledge. The current efficiency is 98.7% at

I

LOAD

of 200A.

Fig. 9 shows the measured transient waveform of V

OUT

when V

REF

changes from 0V to 0.45V at 1-MHz and 10-MHz

clock and I

LOAD

of 200A. The settling time of V

OUT

at 1-MHz

clock is 590s. By increasing the clock frequency from 1MHz

to 10-MHz, the settling time can be reduced by 60% from

590s to 240s at the cost of increasing quiescent current

from 2.7A to 15A and the corresponding degradation of the

current efficiency by 5% at I

LOAD

of 200A as shown in Fig. 8.

The tunable performance by changing the clock frequency is

the advantage of the digital LDO.

Fig. 10 shows the measured transient waveform of V

OUT

when V

REF

changes between 0.4V to 0.45V at 100Hz. The

clock frequency is 1MHz and I

LOAD

is 200A. Fig. 11 shows

the measured transient waveform of V

OUT

when I

LOAD

changes

between 0A to 200A at 100Hz. V

OUT

is 0.45V and the clock

frequency is 1MHz. The measured undershoot and overshoot

of V

OUT

are 40mV and 30mV, respectively. As shown in Figs.

10 and 11, these results show reasonable performance of the

digital LDO to be applied to the power supply for near-

threshold logic circuit.

Since the switch array in the digital LDO is switched

Switch array Shift register

Comparator

900m

8

0

0

m

Fig. 6. Chip microphotograph and layout.

0

0.1

0.2

0.3

0.4

0.5

0.6

V

REF

=0.55V

V

REF

=0.50V

V

REF

=0.45V

V

REF

=0.40V

V

REF

=0.35V

V

O

U

T

[

V

]

V

IN

[V]

0 0.2 0.4 0.6 0.8 1 1.2

I

LOAD

=200A

Target of this work

(a)

0

0.1

0.2

0.3

0.4

0.5

0 0.2 0.4 0.6 0.8 1 1.2

V

O

U

T

[

V

]

V

IN

[V]

I

LOAD

=200A

I

LOAD

=100A

I

LOAD

=20A

V

REF

=0.45V

(b)

Fig. 7. Measured V

OUT

V

IN

characteristics. (a) V

REF

is varied from0.35V

to 0.55V at I

LOAD

of 200A. (b) I

LOAD

is varied from10A to 200A at

V

REF

of 0.45V.

C

u

r

r

e

n

t

e

f

f

i

c

i

e

n

c

y

(

)

[

%

]

70

75

80

85

90

95

100

0 50 100 150 200 250

0

5

10

15

20

Q

u

i

e

s

c

e

n

t

c

u

r

r

e

n

t

(

I

Q

)

[

A

]

Load current (I

LOAD

) [A]

Clk=1MHz

Clk=10MHz

Clk=10MHz

Clk=1MHz

Fig. 8. Measured I

LOAD

dependence of the current efficiency and the

quiescent currents at 1-MHz and 10-MHz clock.

V

OUT

@Clk=10MHz

0V

0.45V

0V

0.45V

I

LOAD

=200A

V

REF

V

OUT

@Clk=1MHz

240s

590s

Fig. 9. Measured transient waveformof V

OUT

when V

REF

changes from0V

to 0.45V at 1-MHz and 10-MHz clock and I

LOAD

of 200A.

V

OUT

0.45V

0.4V

0.45V

0.4V

V

REF

10ms

I

LOAD

=200A

Fig. 10. Measured transient waveform of V

OUT

when V

REF

changes

between 0.4V to 0.45V at 100Hz. The clock frequency is 1MHz and I

LOAD

is 200A.

digitally, the clock-related digital noise may cause LDO

output ripple. To evaluate the ripple caused by the digital

noise, output ripple is measured as shown in Fig. 12. V

OUT

is

0.45V and the clock frequency is 1MHz. The ripple of V

OUT

is

less than 3mV. The measured V

OUT

shows no significant

ripple at clock edges and its harmonic tones, which indicates

that the clock-related digital noise does not affect the LDO

output ripple in the developed digital LDO.

The key performance summary of the proposed digital

LDO and comparison with some previous regulators are listed

in Table I. The digital control is proposed in [6]. The regulator

in [6], however, is not LDO but a half V

DD

generator. In this

paper, both the digital LDO and 0.5-V LDO are demonstrated

for the first time. The developed digital LDO achieved the 0.5-

V input voltage and 0.45-V output voltage with 98.7% current

efficiency and 2.7-A quiescent current at 200-A load

current. Both the input voltage and the quiescent current are

the lowest values in the published LDOs.

IV. CONCLUSION

In this paper, the digital LDO enabling the 0.5-V operation

is proposed and demonstrated for the first time. The developed

digital LDO in 65nm CMOS achieved the 0.5-V input voltage

and 0.45-V output voltage with 98.7% current efficiency and

2.7-A quiescent current at 200-A load current. Both the

input voltage and the quiescent current are the lowest values in

the published LDOs, which indicates the good energy

efficiency of the digital LDO at 0.5-V operation.

ACKNOWLEDGMENTS

The authors would like to thank Yu Pu for his help during

the design of this test chip and Hirofumi Shinohara for his

support and encouragement. This work was carried out as a

part of Extremely Low Power (ELP) project supported by the

New Energy and Industrial Technology Development

Organization (NEDO).

REFERENCES

[1] A. Agarwal, Amit, S. Mathew, S. Hsu, M. Anders, H. Kaul, F. Sheikh,

R. Ramanarayanan, S. Srinivasan, R. Krishnamurthy, and S. Borkar, "A

320mV-to-1.2V on-die fine-grained reconfigurable fabric for

DSP/Media accelerators in 32nmCMOS," IEEE International Solid-

State Circuits Conference, pp. 328-329, Feb. 2010.

[2] H. Kaul, M. Anders, S. Mathew, S. Hsu, A. Agarwal, R. Krishnamurthy,

and S. Borkar, "A 320mV 56W 411GOPS/Watt ultra-low voltage

motion estimation accelerator in 65nm CMOS," IEEE International

Solid-State Circuits Conference, pp. 316-317, Feb. 2008.

[3] B. Calhoun and A. Chandrakasan, "Ultra-dynamic voltage scaling

(UDVS) using sub-threshold operation and local voltage dithering,"

IEEE J ournal of Solid-State Circuits, Vol. 41, No. 1, pp. 238-245, J an.

2006.

[4] S. Hanson, B. Zhai, M. Seok, B. Cline, K. Zhou, M. Singhal, M.

Minuth, J . Olson, L. Nazhan-dali, T. Austin, D. Sylvester, and D.

Blaauw, "Performance and variability optimization strategies in a sub-

200mV, 3.5pJ /inst, 11nW subthreshold processor," IEEE Symposium

on VLSI Circuits, pp. 152-153, J une 2007.

[5] M. Hwang, A. Raychowdhury, K. Kim, and K. Roy, "A 85mV 40nW

process-tolerant subthreshold 8x8 FIR filter in 130nm technology,"

IEEE Symposiumon VLSI Circuits, pp. 154-155, J une 2007.

[6] P. Hazucha, S. T. Moon, G. Schrom, F. Paillet, D. S. Gardner, S.

Rajapandian, and T. Karnik, "A linear regulator with fast digital control

for biasing integrated DC-DC converters," IEEE International Solid-

State Circuits Conference, pp. 536 - 537, Feb. 2006.

[7] P. Hazucha, T. Karnik, B. A. Bloechel, C. Parsons, D. Finan, and S.

Borkar, Area-efficient linear regulator with ultra-fast load regulation,

IEEE J ournal of Solid-State Circuits, Vol.40, no.5, pp. 933-940, Apr.

2005.

[8] M. Al-Shyoukh, H. Lee, and R. Perez, "A transient-enhanced low-

quiescent current low-dropout regulator with buffer impedance

attenuation," IEEE J ournal of Solid-State Circuits, Vol.42, no.8, pp.

1732-1742, Aug. 2007.

[9] Y. H. Lamand W. H. Ki, "A 0.9V 0.35umadaptively biased CMOS

LDO regulator with fast transient response," IEEE International Solid-

State Circuits Conference, pp. 442-443, Feb. 2008.

V

OUT

=0.45V

Clk =1MHz

3mV

5mV

0.5V

1s

I

LOAD

=200A, V

REF

= 0.45V

Fig. 12. Measured waveforms of V

OUT

and 1-MHz clock. V

OUT

is 0.45V

and I

LOAD

is 200A.

V

OUT

=0.45V

I

LOAD

200A

0A

30mV

40mV

10ms

Fig. 11. Measured transient waveform of V

OUT

when I

LOAD

changes

between 0A to 200A at 100Hz. V

OUT

is 0.45V and the clock frequency is

1MHz.

TABLE I

KEY PERFORMANCE SUMMARY OF THE PROPOSED DIGITAL LDO AND

COMPARISON WITH PREVIOUS REGULATORS

LDO LDO LDO LDO

Half V

DD

generator

- Type of regulator

Digital Analog Analog Analog Digital - Control

0.2 50 200 100 1000 mA

Maximum load

current

98.7 99.7 99.8 94.3 97.5 % Current efficiency

2.7

4.02 to

164

20 to 320 6000 25700 A Quiescent current

0.1

(off-chip)

1

(off-chip)

1

(off-chip)

0.0006

(on-chip)

0.0024

(on-chip)

F

Decoupling

capacitor

0.65 0.06 0.17 1 - mV/mA Load regulation

3.1 1.1 2 - - mV/V Line regulation

0.45 0.9 1.8 0.9 1.2 V

Nominal output

voltage

0.5 1.05 2 1.2 2.4 V

Minimum input

voltage

0.042 0.053 0.264 0.008 0.03 mm

2

Acti ve area

65nm 350nm 350nm 90nm 90nm - CMOS Technology

This work [9] [8] [7] [6] Unit

LDO LDO LDO LDO

Half V

DD

generator

- Type of regulator

Digital Analog Analog Analog Digital - Control

0.2 50 200 100 1000 mA

Maximum load

current

98.7 99.7 99.8 94.3 97.5 % Current efficiency

2.7

4.02 to

164

20 to 320 6000 25700 A Quiescent current

0.1

(off-chip)

1

(off-chip)

1

(off-chip)

0.0006

(on-chip)

0.0024

(on-chip)

F

Decoupling

capacitor

0.65 0.06 0.17 1 - mV/mA Load regulation

3.1 1.1 2 - - mV/V Line regulation

0.45 0.9 1.8 0.9 1.2 V

Nominal output

voltage

0.5 1.05 2 1.2 2.4 V

Minimum input

voltage

0.042 0.053 0.264 0.008 0.03 mm

2

Acti ve area

65nm 350nm 350nm 90nm 90nm - CMOS Technology

This work [9] [8] [7] [6] Unit

Potrebbero piacerti anche

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- AutoRanging DMMDocumento8 pagineAutoRanging DMMPankaj VermaNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Sepic Converter Design and Operation: by Gregory SharpDocumento21 pagineSepic Converter Design and Operation: by Gregory SharpSingam SridharNessuna valutazione finora

- Sooho Cha, Chunseok Jeong, Changsik Yoo Joongsik Kih: Abstract - A Digitally Controlled Phase-Locked LoopDocumento4 pagineSooho Cha, Chunseok Jeong, Changsik Yoo Joongsik Kih: Abstract - A Digitally Controlled Phase-Locked LoopNguyen Tien HaiNessuna valutazione finora

- An02 001Documento7 pagineAn02 001Xuanwu KangNessuna valutazione finora

- ADC0809CCNDocumento16 pagineADC0809CCNFrancesca Castelar BenalcazarNessuna valutazione finora

- And8328 DDocumento8 pagineAnd8328 DJonatan LunaNessuna valutazione finora

- Smps For CRT Monitors With The L6565: AN1657 Application NoteDocumento9 pagineSmps For CRT Monitors With The L6565: AN1657 Application Noterdc02271Nessuna valutazione finora

- PLC AutomationDocumento13 paginePLC AutomationVamsi KumarNessuna valutazione finora

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDa EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsValutazione: 3.5 su 5 stelle3.5/5 (6)

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocumento16 pagineμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKasi ChinnaNessuna valutazione finora

- LM5085 PDFDocumento8 pagineLM5085 PDFSreeram PanigrahiNessuna valutazione finora

- Analog To Digital Converter and Vise VersDocumento7 pagineAnalog To Digital Converter and Vise VersSpyx MeniNessuna valutazione finora

- Electronic Circuits - II Lab ManualDocumento26 pagineElectronic Circuits - II Lab Manualbalabasker100% (1)

- Simple FSKDocumento6 pagineSimple FSKFaten AliNessuna valutazione finora

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocumento16 pagineμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNessuna valutazione finora

- Project Objective:: Simple AdcDocumento10 pagineProject Objective:: Simple AdcaravindnehaNessuna valutazione finora

- Chapter05 FinalDocumento55 pagineChapter05 FinalMuhammed I'zwanNessuna valutazione finora

- Implementation of A Single-Phase Unipolar Inverter Using DSP TMS320F241Documento5 pagineImplementation of A Single-Phase Unipolar Inverter Using DSP TMS320F241Pci ElectronicaNessuna valutazione finora

- Sliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranDocumento11 pagineSliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranInternational Organization of Scientific Research (IOSR)Nessuna valutazione finora

- Green-Mode PWM Controller: General Description FeaturesDocumento10 pagineGreen-Mode PWM Controller: General Description FeaturesLuis Luis GarciaNessuna valutazione finora

- Chapter Three2Documento12 pagineChapter Three2Fuh ValleryNessuna valutazione finora

- Application Examples: Optocouplers and Solid-State RelaysDocumento6 pagineApplication Examples: Optocouplers and Solid-State RelaysDinesh KumarNessuna valutazione finora

- Automotive LED Buck ConverterDocumento3 pagineAutomotive LED Buck Converternacional007100% (1)

- Implementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan KhalidDocumento7 pagineImplementation of NAND NOR AND Gates Using TTL - Asadullah Hussain & Faizan KhalidchachunasayanNessuna valutazione finora

- DC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Documento22 pagineDC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Harkishen SinghNessuna valutazione finora

- DiDocumento5 pagineDiByron DamaniaNessuna valutazione finora

- DPM 1as-BlDocumento4 pagineDPM 1as-BlNarendra BholeNessuna valutazione finora

- An Open-Loop Stepper Motor Driver Based On FPGADocumento5 pagineAn Open-Loop Stepper Motor Driver Based On FPGADivya JamesNessuna valutazione finora

- Design Ideas PDFDocumento5 pagineDesign Ideas PDFJohn Abrahim100% (1)

- Step-By-Step Design of The Digital Closed Loop System of The Boost Voltage ConverterDocumento6 pagineStep-By-Step Design of The Digital Closed Loop System of The Boost Voltage ConverterAMIR SOHAILNessuna valutazione finora

- Accurate, Fast Settling Analog Voltages From Digital PWM SignalsDocumento2 pagineAccurate, Fast Settling Analog Voltages From Digital PWM SignalsAdhi Ne CutcakrowoNessuna valutazione finora

- Traffic Light Control CircuitDocumento23 pagineTraffic Light Control Circuitgovind_sha2009Nessuna valutazione finora

- Design: IdeasDocumento5 pagineDesign: Ideasdcastrelos2000Nessuna valutazione finora

- Buck Boost ConverterDocumento32 pagineBuck Boost ConverterJanmejay MohapatraNessuna valutazione finora

- LD7750-DS Fuente TCL GermanDocumento20 pagineLD7750-DS Fuente TCL GermanAndres Alegria100% (1)

- DTC 19300Documento8 pagineDTC 19300Rafael Ricardo Zacarias CastilloNessuna valutazione finora

- EXP6Documento10 pagineEXP6fatih_ealNessuna valutazione finora

- Max 16841 Ev KitDocumento16 pagineMax 16841 Ev KitjorojoroNessuna valutazione finora

- CMOS Implemented VDTA Based Colpitt OscillatorDocumento4 pagineCMOS Implemented VDTA Based Colpitt OscillatorijsretNessuna valutazione finora

- ADC0808Documento15 pagineADC0808Ketan SalviNessuna valutazione finora

- Integrated Circuit Systems, IncDocumento11 pagineIntegrated Circuit Systems, Incroger marqNessuna valutazione finora

- Table of Content: Digital OhmmeterDocumento23 pagineTable of Content: Digital OhmmeterLow Koon Yee100% (1)

- Underground Cable Fault Distance Locator: Project OnDocumento31 pagineUnderground Cable Fault Distance Locator: Project OnsmartyNessuna valutazione finora

- Solns 29Documento102 pagineSolns 29ramprakash_rampelliNessuna valutazione finora

- DC-DC Boost Converter For Custom Application by LeenaDocumento4 pagineDC-DC Boost Converter For Custom Application by LeenaRekhamtrNessuna valutazione finora

- ICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesDocumento16 pagineICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesStefano Romeu ZeplinNessuna valutazione finora

- ICL7106 and ICL7107 VoltmeterDocumento16 pagineICL7106 and ICL7107 VoltmeterAntonino ScordatoNessuna valutazione finora

- Analog Switches and Multiplexers BasicsDocumento23 pagineAnalog Switches and Multiplexers BasicsOfir CzNessuna valutazione finora

- Converter & Timing CircuitDocumento16 pagineConverter & Timing Circuityoboiiii649Nessuna valutazione finora

- Elimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengDocumento4 pagineElimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengAlejandro Ospina0% (1)

- LD7552 DS 00Documento10 pagineLD7552 DS 00BRIGHT_SPARKNessuna valutazione finora

- ADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERDocumento17 pagineADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERTechreinnovate0% (1)

- Department of Electrical Engineering and Telecommunications TechnologiesDocumento35 pagineDepartment of Electrical Engineering and Telecommunications Technologiessuresh NamgiriNessuna valutazione finora

- UTC 2N3055 Silicon NPN TransistorDocumento2 pagineUTC 2N3055 Silicon NPN TransistorPCP MaprisNessuna valutazione finora

- Cb2Ce, Cb4Ce, Cb8Ce, Cb16Ce: 2-, 4-, 8-,16-Bit Cascadable Binary Counters With Clock Enable and Asynchronous ClearDocumento6 pagineCb2Ce, Cb4Ce, Cb8Ce, Cb16Ce: 2-, 4-, 8-,16-Bit Cascadable Binary Counters With Clock Enable and Asynchronous ClearzippolNessuna valutazione finora

- Mini Project Report FinalDocumento8 pagineMini Project Report FinalNAUZR100% (1)

- Negative Skew For Setup: Propagation Delays Load Delays Interconnect DelaysDocumento25 pagineNegative Skew For Setup: Propagation Delays Load Delays Interconnect DelaysRajni100% (1)

- Lab 08 Layout: "Design and Implementation of Full Adder at Layout Level in Microwind" 1. ObjectiveDocumento4 pagineLab 08 Layout: "Design and Implementation of Full Adder at Layout Level in Microwind" 1. ObjectiveSheikh Abdullah Al SalmanNessuna valutazione finora

- Analogue Electronic Design Module E EEE2039 / EEE2026 / EEE2042Documento36 pagineAnalogue Electronic Design Module E EEE2039 / EEE2026 / EEE2042Arvish RamseebaluckNessuna valutazione finora

- BGW 75 Prof. Power AmplifierDocumento2 pagineBGW 75 Prof. Power AmplifierEnrique PalacioNessuna valutazione finora

- Low Frequency Radio Receiver Circuit ProjectDocumento7 pagineLow Frequency Radio Receiver Circuit Projectpeccerini100% (1)

- Ei2353:Digital System Design: Question BankDocumento3 pagineEi2353:Digital System Design: Question BanknithyadeceNessuna valutazione finora

- Module05 PDFDocumento337 pagineModule05 PDFaaron89Nessuna valutazione finora

- Opa1632 Used in AMB Laboratories SchematicsDocumento35 pagineOpa1632 Used in AMB Laboratories SchematicscosNessuna valutazione finora

- S1A0426Documento4 pagineS1A0426German DfrNessuna valutazione finora

- Chapter 3Documento10 pagineChapter 3Eugine BalomagaNessuna valutazione finora

- OP AMPS HughesDocumento8 pagineOP AMPS Hughesmarkos_mylonas4152Nessuna valutazione finora

- HDL Lab Manual-1Documento102 pagineHDL Lab Manual-1maniaNessuna valutazione finora

- State Variable CrossoverDocumento6 pagineState Variable CrossoverECKO W (XcntrX)Nessuna valutazione finora

- Analog Electronics End Semester (Autumn) Question 2019Documento3 pagineAnalog Electronics End Semester (Autumn) Question 2019S.A.RAHMANNessuna valutazione finora

- Automatic Fan Speed Control Circuit Using PIC16F877A MicrocontrollerDocumento5 pagineAutomatic Fan Speed Control Circuit Using PIC16F877A MicrocontrollerPramillaNessuna valutazione finora

- ECE (249) SyllbusDocumento2 pagineECE (249) SyllbusNishant PathakNessuna valutazione finora

- Sequential Logic CircuitsDocumento10 pagineSequential Logic CircuitsNaveen MadushaNessuna valutazione finora

- 555 TimerDocumento12 pagine555 TimerShubhankar KunduNessuna valutazione finora

- Training Msi MS-7 - IDocumento1 paginaTraining Msi MS-7 - IadaofisicoNessuna valutazione finora

- REN R01an3817ej0100-Rl78 APN 20170531Documento30 pagineREN R01an3817ej0100-Rl78 APN 20170531Andrea FasatoNessuna valutazione finora

- 12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFDocumento23 pagine12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFAndy Espinosa GutiérrezNessuna valutazione finora

- Unit 3.1 Miller EffectDocumento3 pagineUnit 3.1 Miller EffectchettiyathNessuna valutazione finora

- V98XX Datasheet: Specifications Are Subject To Change Without NoticeDocumento264 pagineV98XX Datasheet: Specifications Are Subject To Change Without Noticeعلی رستمیNessuna valutazione finora

- Am ReceiversDocumento4 pagineAm ReceiversAldrinNessuna valutazione finora

- Wideband DTV UHF Antenna TV AmplifierDocumento3 pagineWideband DTV UHF Antenna TV AmplifierRaymond KandallNessuna valutazione finora

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDa EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonValutazione: 5 su 5 stelle5/5 (2)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDa EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeValutazione: 4.5 su 5 stelle4.5/5 (9)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDa EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesValutazione: 5 su 5 stelle5/5 (1)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosDa EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosValutazione: 5 su 5 stelle5/5 (1)

- Analog Design and Simulation Using OrCAD Capture and PSpiceDa EverandAnalog Design and Simulation Using OrCAD Capture and PSpiceNessuna valutazione finora

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialDa EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialValutazione: 3.5 su 5 stelle3.5/5 (3)

- ARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)Da EverandARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)Nessuna valutazione finora

- Upcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Da EverandUpcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Valutazione: 4.5 su 5 stelle4.5/5 (2)

- Current Interruption Transients CalculationDa EverandCurrent Interruption Transients CalculationValutazione: 4 su 5 stelle4/5 (1)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDa EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tValutazione: 4.5 su 5 stelle4.5/5 (27)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDa EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsValutazione: 3.5 su 5 stelle3.5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDa EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionValutazione: 4.5 su 5 stelle4.5/5 (543)

- Heat Transfer Engineering: Fundamentals and TechniquesDa EverandHeat Transfer Engineering: Fundamentals and TechniquesValutazione: 4 su 5 stelle4/5 (1)

- The Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesDa EverandThe Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesValutazione: 5 su 5 stelle5/5 (1)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDa Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersValutazione: 5 su 5 stelle5/5 (1)

- Wearable Sensors: Fundamentals, Implementation and ApplicationsDa EverandWearable Sensors: Fundamentals, Implementation and ApplicationsEdward SazonovNessuna valutazione finora