Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Simulationof Single Phase Full Bridge Converter Using PSPICE

Caricato da

Dhivya NCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Simulationof Single Phase Full Bridge Converter Using PSPICE

Caricato da

Dhivya NCopyright:

Formati disponibili

Experiment no: Date:

SIMULATION OF SINGLE PHASE FULL BRIDGE CONVERTER USING PSPICE

AIM

A. To simulate and analyze the circuit of a single phase full bridge converter connected to a 230V(rms)

!0 "z ac supply using the simulation pac#age $%$&'( )ith *+,+( load and

a) -or (./0V /00V *./.! ,.00m" observe the )aveforms )ith various values of

triggering angles (1) and plot the follo)ing )aveforms for three values of 1 such that the

load current is continuous discontinuous and 2ust continuous.

(i) &nstantaneous output voltage

(ii) the input current

(iii) the load current

(iv) -ind the T"3 and the input po)er factor in each case

b) 4bserve the effect of load inductance on the load current )ith (. /00 V *./.! for 1.!5

o

and find the inductance value at )hich the current becomes 2ust continuous.

c) To plot the follo)ing graphs for (. /00 V *./.! ,.00m"

/. T"3 Vs Triggering angle (1)

2. &nput po)er factor Vs Triggering angle (1).

d) 3etermine the average converter output voltage and load current )hen converter operates

in the inverting mode )ith ( . + /00V.

e) Verify &nput 4utput $o)er 6alance )ith direction of po)er flo) for (d).

6. To simulate and analyse the source current and voltage at $oint of 'ommon 'oupling ($'') )ith a

source inductance

i. Add 0.!m" source inductance in series )ith the source and a converter cable inductance of

0.2m" and 0.0m" at the converter input.

ii. 4bserve the source current and find the value of commutation angle.

iii. 4bserve the voltage )aveform at $'' and comment on the shape and the voltage T"3 in

each case.

THEOR

-ig7/

/

The circuit arrangement of a single+phase converter is as sho)n in the fig(/) )ith a highly inductive

load so that the load current is continuous and ripple free. 3uring the positive half cycle thyristors T

/

and T

2

are for)ard biased and )hen these t)o thyristors are triggered simultaneously at )t . 1 the load is connected

to the input supply through T/ and T2. 3ue to the inductive load the thyristors T/ and T2 )ill continue to

conduct even beyond )t . 8 even though the input voltage is already negative. 3uring the negative half cycle

the thyristors T3 and T5 are for)ard biased and triggering of these thyristors )ill apply a reverse bias voltage

across the thyristors T/ and T2. Thyristors T/ and T2 are turned off due to the line commutation or the natural

commutation and the load current )ill be transferred from T/ and T2 to T3 and T5. The regions of converter

operation are sho)n in the fig.2.

Hint: !ar"e tri""erin" an"!e# ma$e# a%era"e !oa& '(rrent to )a!!* Lar"e +E, %a!(e# in RLE !oa&# -i!! a!#o

ma$e a%era"e !oa& '(rrent to )a!!* I .ot/ t/e 'a#e# t/e operation ma0 .e'ome &i#'ontin(e#* So '/oo#e

appropriate 'om.ination o) tri""erin" an& E to o.tain t/e t/ree mo&e# o) operation#*

The )aveforms for input voltage output voltage input current and output current are sho)n in fig (3).

2

+V

o

V

o

&

3

-ig. 2

-ig.3

3uring the period from 1 to 8 the input voltage and input current are positive and the po)er flo)

from the supply to the load. The duration from 8 to 891 input voltage is negative and the input current

remains positive and these results in the reversal of the po)er flo). These #inds of converters are e:tensively

used in the industry up to a rating of /!;<. 3epending on the value of 1 the average output voltage could be

positive or negative and hence it provides 2 = >uadrant operation.

The average output voltage can be found from the e:pression

) cos(

2

) ( ) sin(

/

m

m dc

V

t d t V V = =

+

Thus V

dc

can be varied from 2V

m

? 8 to +2V

m

? 8 by varying the firing angle from 0 to 8. The ma:imum average

output voltage is V

dm

. V

m

? 8 and the normalized output voltage is V.V

dc

?Vd

m

.cos(1).

The rms value of the output voltage is given by the e:pression

2

) ( )) sin( (

/

2 m

m rms

V

t d t V V =

The output voltage contains harmonics and therefore the conventional definitions of po)er factor etc. defined

for the pure sinusoidal )aveforms cannot be applied.

The input displacement factor is defined as the cosine of the angle bet)een the fundamental of the input

current and the corresponding line to neutral input voltage.

The input po)er factor is defined as

&nput p.f . Total mean input po)er ? Total rms apparent po)er

.

rms rms

I V

VI

cos

/

-or a sinusoidal input voltage V.V

rms

The input po)er factor can be )ritten as . (&

/

cos@)?&

rms

EFFECT OF SOURCE INDUCTANCE:

3

-igure75

-igure 5 sho)s a practical arrangement )ith ,s/ and ,s2 )here ,s/ is the internal inductance of the

ac source and ,s2 is the inductance associated )ith the converter. The 2unction of ,s/ and ,s2 is the called as

the point of common coupling )here other loads may be connected as sho)n in figure 5.

Ao) )hen the ac side inductance is considered for a given triggering angle the current commutation from

one se to thyristors to another ta#es a finite commutation interval. 3uring the commutation interval all four

devices in the bridge conducts resulting zero converter output voltage. Thus due to the presence of ,s an

additional voltage drop is introduced in the output voltage.

&n addition to the reduction in output voltage a thyristor converter also results in line voltage noise consisting

of line notching and )aveform distortion. The line notching at the $'' is of concern. The notch depths and

the notch areas are influenced by factor B .,s/?(,s/9,s2). Therefore higher value of ,s2 )ill result in

smaller notches at the $''.

Ta.(!ar 'o!(mn

(. /00 V *./.! ,.00m"

&

/

(A) T"3(C) &

rms

(A) $hase (deg) i?p $-

, . (tan ) *D, . (tan ) *? .

-or ,.EEEEEm" current has continuous )ave.

&

/

(A) T"3(C) &

rms

(A) $hase (deg) i?p $-

SAMPLE CALCULATION

5

-or ./0F (/ ms) )ith ,.00m"

Total harmonic distortion (T"3) .

-undamental current amplitude .

-undamental current displacement angle .

&rms .

$o)er factor .

I

I

Srms

S

/

/

cos

Cir'(it )i!e )or #im(!ation o) #in"!e p/a#e .ri&"e 'on%erter

.$A*AG rs. /000

.param cs.0.2u

Vs / 0 sin (0 32!.2H !0"z)

V: / 2 0

V ! H /0

* 3 5 /.!

, 5 ! 00m

Vg/ I 3 pulse (0 /0 /m 0 0 /00u 20m)

Vg2 /0 0 pulse (0 /0 /m 0 0 /00u 20m)

Vg3 0 3 pulse (0 /0 //m 0 0 /00u 20m)

Vg5 J 2 pulse (0 /0 //m 0 0 /00u 20m)

K/ 2 3 I 3 %'*

K2 H 0 /0 0 %'*

K3 0 3 0 3 %'*

K5 H 2 J 2 %'*

r/00 2 /00 LrsM

c/00 /00 3 LcsM

r200 H 200 LrsM

c200 200 0 LcsM

r300 0 300 LrsM

c300 300 3 LcsM

r500 H 500 LrsM

c500 500 2 LcsM

.%N6';T %'* / 2 3 2

%/ / ! H 2 %G43

*g 3 5 !0

!

V: 5 2 3' 0

Vy ! I 3' 0

3t I 2 3G43

*t H 2 /

'f H 2 /0u

-/ 2 H $4,O(2) V: Vy 0 !0 //

.G43(, %G43 V%<&T'"(*on.0.0/2! *off./0(9! Von.0.! Voff.0)

.G43(, 3G43 3(&%.2.2(+/! 6V./000 TT.0 'P4.0)

.(A3% %'*

.T*AA /00N 3H0G 300G /0u

.$*46(

.-4N* !0"z &(V:)

.(A3

PROGRAM 1ITH SOURCE INDUCTANCE

.$A*AG rs. /000

.param cs.0.2u

Vs / 0 sin (0 32!.2H !0"z)

V: 2/ 2 0

,%/ / 20 0./0m

,%2 20 2/ 0.02m

V ! H /0

* 3 5 /.!

, 5 ! 00m

Vg/ I 3 pulse (0 /0 /m 0 0 /00u 20m)

Vg2 /0 0 pulse (0 /0 /m 0 0 /00u 20m)

Vg3 0 3 pulse (0 /0 //m 0 0 /00u 20m)

Vg5 J 2 pulse (0 /0 //m 0 0 /00u 20m)

K/ 2 3 I 3 %'*

K2 H 0 /0 0 %'*

K3 0 3 0 3 %'*

K5 H 2 J 2 %'*

r/00 2 /00 LrsM

c/00 /00 3 LcsM

r200 H 200 LrsM

c200 200 0 LcsM

r300 0 300 LrsM

c300 300 3 LcsM

r500 H 500 LrsM

c500 500 2 LcsM

.%N6';T %'* / 2 3 2

%/ / ! H 2 %G43

*g 3 5 !0

V: 5 2 3' 0

Vy ! I 3' 0

3t I 2 3G43

*t H 2 /

'f H 2 /0u

-/ 2 H $4,O(2) V: Vy 0 !0 //

.G43(, %G43 V%<&T'"(*on.0.0/2! *off./0(9! Von.0.! Voff.0)

.G43(, 3G43 3(&%.2.2(+/! 6V./000 TT.0 'P4.0)

H

.(A3% %'*

.T*AA /00N 3H0G 300G /0u

.$*46(

.-4N* !0"z &(V:)

.(A3

A .rie) intro&('tion to t/e t/0ri#tor mo&e!in" an& t/e (#e o) #(.2'ir'(it# i# "i%en .e!o-:

SUB CIRCUIT

The sub+circuit permits the user to define a bloc# of circuitry and then use the bloc# in several places

in the circuit under simulation. The synta: for the sub+circuit is

.%N6'&*'N&T subc#tname QRt)o or more nodesST

The spice symbol used for representing the sub+circuit is K the general statement call is of the form.

KRnameS Qt)o or more nodesT subc#tname

The usage of sub+circuit in $spice may be considered similar to the usage of U%ubroutinesV in -4*T*AA or

usage of Ufunction callsV in '. The sub+circuits in $spice can be nested but must not be circular or recursive.

A sub+circuit must end )ith a (A3% statement.

.(A3% subc#tname

T/e T/0ri#tor mo&e!:

&f our analysis does not concern )ith any particular thyristor type and if our intention is to study the

general behavior of the circuit then )e can use a simple and appro:imate model of a thyristor.

The thyristor is a latching device and it can be modeled by a voltage+controlled s)itch and a

polynomial current source as sho)n in the fig.2.

R g

C r

V x

V r

D 1

1

2

C 1

V g

g a t e

3

4

1

5

7

2

6

K

A

0 v

A n o d e

c a t h o d e

F 1

0 v

R r

S 1

-ig.!

<e ta#e the essential thyristor action to be

/) &t should turn on )ith a small positive gate to cathode voltage if the anode to cathode voltage is

positive.

2) &t should remain in the on state as long as anode current is positive.

3) &t should turn off if anode current changes to negative direction.

&n the statement for current controlled current source - )e have used a polynomial source.

The general synta: from a polynomial source controlled by WnX controlling variables is

$4,O(n)Rcontrolling nodes 9ve and =veS R co+efficient valuesS

&f )e ta#e an e:ample of a polynomial source controlled by t)o variables A and 6 then O.f(A6)

O ta#es the form O.$

0

9$

/

A9$

2

69$

3

A

2

9$

5

A69$

!

6

2

9YY.

Therefore in our e:ample if )e have )ritten

I

-/ 2 H $4,O(2) VK VO 0 !0 //

&t means that a '''% is connected bet)een the nodes 2 (9ve) and H(+ve) an it behaves li#e a polynomial )ith

t)o controlling variables ($4,O(2)) current through VK and VO. The polynomial function is

O.09!0:&(VK)9//:&(VO)

All the other statements are simple and for the elements used in the subcircuit. The voltage+controlled s)itch

and the diode are modeled using the G43(, statement.

The s)itching action of the thyristor can be modeled by a voltage+controlled s)itch and a polynomial

current source. The follo)ing steps can e:plain the turn on process7

/. -or a 9ve gate voltage Vg bet)een nodes 3 and 2 the gate current is &g . & (VK) . Vg?*

Z

.

2. The gate current &

g

activates the '''% -

/

and produces a current of value -

g

.$

/

&

g

.$

/

&(VK) such

that -

/

.-

g

9-

a

.

3. The current source -

g

produces a rapidly rising voltage V

*

across the resistance *

T

.

5. As the voltage V

*

increases above zero the resistance *

s

of the voltage controlled s)itch %

/

decreases

from *

4--

to)ards *

4A

.

!. As the s)itch resistance *

s

decreases the anode current &

a

. &(VO) increases provided that the anode

to cathode voltage is 9ve. This increasing anode current &

a

produces a current -

a

.$

2

&

a

.$

2

&(VO). This

cause an increased value of voltage V

*

.

H. This then produces a regenerative condition )ith the s)itch rapidly being driven into lo) resistance

(the 4A state). The s)itch remains on if the gate voltage Vg is removed.

I. The anode current &

a

continues to flo) as long as it is 9ve and the s)itch remain in the 4A state.

3uring turn+off the gate current is 4-- and &g.0. That is &g.0 and -g.0 -

/

.-g9-g.-g. The follo)ing steps

can e:plain the turn = off operation7

/. As the anode current &

a

goes =ve the current -

/

reverses provided that gate voltage V

g

is no longer

present.

2. <ith a =ve -/ the capacitor '

T

discharges through the current source -

/

and the resistance *

T.

3. <ith the fall of voltage V

*

to a lo) level the resistance *

s

of the s)itch %

/

from a lo) (*

4A

) value to a

high (*

4--

) value.

5. This is again a regenerative condition )ith the s)itch resistance being driven rapidly to an *

4--

value

as the voltage V

*

becomes zero.

The diode 3

T

prevents reverse current flo) through the thyristor resulting from the firing of another thyristor

in the circuit.

-or detailed information on the modeling and sub circuit parameters refer the boo# U%$&'( -4* $4<(*

(,('T*4A'&% AA3 (,('T*&' $4<(*V by Guhammad " *ashid.

PROCEDURE

+ Turn on the computer

+ (nter the directory '7[%TN3(AT%

+ &nvo#e $spice shell by typing $%

+ (nter the program and edit.

+ 3o the analysis and plot the necessary )aveforms.

+

RESULTS

The single phase full bridge converter )ith *+,+( load )as analyzed using pspice. &nstantaneous output

voltage Vo and input current &in load current &o are plotted.

/. The total harmonic distortion in

(i) 'ontinuous current mode for 1 .YYYYF isEEEEEEEE and po)er factor is EEEEE

(ii) 3iscontinuous current mode for 1 .YYYYF isEEEEEEEE and po)er factor is EEEEE

(iii) Pust continuous current mode for

2. The load inductance value at )hich at )hich the current becomes continuous is EEEEE

0

3. The average converter output voltage in inverter mode is YYYYYYand average load current

YYYYY..

5. Verification of the po)er balance $in YYYYY. $out YYYYYYYY.

!. 'ommutation angle )ith a total source inductance (,s/9,s2) of YYYYY.. is e>ual to YYYY..

o

.

H. T"3 of Voltage at $'' . YYYYYYYY.

&A-(*(A'(7

/.

2.

3.

NOTE

The above e:periment re>uires additional reading of $spice manuals. The program description given

above should be substituted by the actual program and detailed description by the students. The )aveforms

obtained should be submitted as printouts and the program listing along )ith -ourier analysis results should

also be submitted.

A BRIEF DESCRIPTION OF PSPICE

$%$&'( is a general+purpose circuit program is e:tensively used to simulate (lectrical and (lectronic

circuits. %pice is a short form of U%imulation $rogram )ith &ntegrated 'ircuit (mphasisV %pice is e:tensively

used for initial design validation and analysis.

The circuit has to be described in terms of (lement names (lement values nodes variable parameters

description etc.

Ta#ing an e:ample of the circuit given fig.5 )e )ant to find the voltage across the capacitor '

/

.

R 1

1 0 0

R 2

1 0 0

R 3

1 0 0

V 1

1 0 V

C 1

1 0 u

0

0

1

2

3

f i g . A

-ig.5

TRIAL PROGRAM

V

3'

/ 0 3' /0

*

/

/ 2 /00

*

2

2 3 /00

'

/

3 0 /0u ic.!

*

3

2 0 /00#

.$*46(

.T*AA /0u /00m uic

.(A3

J

The first line of the program is reserved for comments and is not processed during e:ecution.

The 3' voltage source is named V

3'

and is connected bet)een the nodes / and 0 )ith positive

terminal at node / and negative terminal at node 0. Additionally )e specify that it is a dc source )ith a value

of /0V.

The elements *

/

*

2

'

/

*

3

are mentioned )ith their respective nodes and values. These passive

elements can be connected in any order. -or the capacitor additional information regarding its initial charge is

provided as Uic.!V )hich indicates that the capacitor is initially charged to a potential of !V before analysis

begins.

$%$&'( command U.$*46(V loads a program $*46(.(K( )hich imitates the '*4 probe. This

program enables the current and voltage )aveforms to be graphically presented on the computer screen.

The command U.T*AAV indicates that transient analysis is to be done )ith the total times span of

/00ms )ith a sampling period of /0s. 3epending on the circuit parameters spice may override our sampling

period specification.

Various devices are modeled and they are available in a library file U(VA,.,&6V

Additional information on spice can be obtained from various te:tboo#s.

/0

Potrebbero piacerti anche

- TB 60 Repair Parts PDFDocumento282 pagineTB 60 Repair Parts PDFvatasa100% (2)

- Power System Protection (Vol 3 - Application) PDFDocumento479 paginePower System Protection (Vol 3 - Application) PDFAdetunji TaiwoNessuna valutazione finora

- Cadworx PidDocumento341 pagineCadworx Pidghallky2011Nessuna valutazione finora

- ManualDocumento50 pagineManualspacejung50% (2)

- ELG3311: Solutions For Assignment 1: Problem 2-6Documento14 pagineELG3311: Solutions For Assignment 1: Problem 2-6tesfayregs gebretsadik100% (1)

- Lab 3Documento7 pagineLab 3jisteeleNessuna valutazione finora

- Fluid Mechanics ÇENGELDocumento5 pagineFluid Mechanics ÇENGELNameis GhoffarNessuna valutazione finora

- R290 Propane: AJ AE HG VTCDocumento16 pagineR290 Propane: AJ AE HG VTCengmec12188Nessuna valutazione finora

- Affidavit of Co OwnershipDocumento2 pagineAffidavit of Co OwnershipEmer MartinNessuna valutazione finora

- 12 Air Starting of Diesel EnginesDocumento26 pagine12 Air Starting of Diesel EnginesCurtler PaquibotNessuna valutazione finora

- Flow Meter Sizing MOSDocumento11 pagineFlow Meter Sizing MOSra9622Nessuna valutazione finora

- Options:: Useful Formulas Formulas Transformer FormulasDocumento5 pagineOptions:: Useful Formulas Formulas Transformer FormulasDileep SettyNessuna valutazione finora

- Electrostatic Comsol 4.2Documento5 pagineElectrostatic Comsol 4.2Sophie Phan100% (1)

- Present Tenses ExercisesDocumento4 paginePresent Tenses Exercisesmonkeynotes100% (1)

- The Service FactorDocumento6 pagineThe Service FactorsxpNessuna valutazione finora

- Texto Guía Del Curso Integraph Cadworx 2016Documento20 pagineTexto Guía Del Curso Integraph Cadworx 2016adolfocles100% (1)

- Design Optimization of Fluid Machinery: Applying Computational Fluid Dynamics and Numerical OptimizationDa EverandDesign Optimization of Fluid Machinery: Applying Computational Fluid Dynamics and Numerical OptimizationNessuna valutazione finora

- Employee of The Month.Documento2 pagineEmployee of The Month.munyekiNessuna valutazione finora

- Partnership Digest Obillos Vs CIRDocumento2 paginePartnership Digest Obillos Vs CIRJeff Cadiogan Obar100% (9)

- SterlingDocumento11 pagineSterlingMohammed GomaaNessuna valutazione finora

- BSNL BillDocumento3 pagineBSNL BillKaushik GurunathanNessuna valutazione finora

- The New Art of Photographing Nature - ExcerptDocumento15 pagineThe New Art of Photographing Nature - ExcerptCrown Publishing GroupNessuna valutazione finora

- ASME Mfc-1m (Glossary of Terms Fluid Flow in A Pipe) )Documento37 pagineASME Mfc-1m (Glossary of Terms Fluid Flow in A Pipe) )Avr Chandana100% (2)

- Generalized Psychrometric ChartDocumento11 pagineGeneralized Psychrometric Chartshoukat14Nessuna valutazione finora

- Design of Fluid Systems PDFDocumento66 pagineDesign of Fluid Systems PDFVirendra KumarNessuna valutazione finora

- Loadcenter Eaton PDFDocumento107 pagineLoadcenter Eaton PDFBatzi LudNessuna valutazione finora

- Solenoid Lab ManualDocumento17 pagineSolenoid Lab Manualbrandon999Nessuna valutazione finora

- Corrected Momnetum and Energy Equations Disprove Betz's LimitDocumento25 pagineCorrected Momnetum and Energy Equations Disprove Betz's LimitLarry MansbergerNessuna valutazione finora

- IHP Pneumatic SymbolsDocumento4 pagineIHP Pneumatic SymbolsBIPIN SHARMANessuna valutazione finora

- Assignments StudentsDocumento2 pagineAssignments StudentsManju Chakraborty100% (1)

- A Textbook of Electrical Technology Vol. 2 - Theraja-P1Documento29 pagineA Textbook of Electrical Technology Vol. 2 - Theraja-P1Muhammad TaimoorNessuna valutazione finora

- Dfu - Upc PDFDocumento2 pagineDfu - Upc PDFlijo johnNessuna valutazione finora

- DC GENERATOR Final 1Documento9 pagineDC GENERATOR Final 1Jhess GaliciaNessuna valutazione finora

- Technical Service Manual: Section TSM 144 1 of 10 Issue DDocumento10 pagineTechnical Service Manual: Section TSM 144 1 of 10 Issue DHector_Cornejo_5673Nessuna valutazione finora

- TA CarburationDocumento5 pagineTA Carburationrajmalhotra167Nessuna valutazione finora

- Callendar Van DusenDocumento3 pagineCallendar Van DusenSidnei RodriguesNessuna valutazione finora

- CH4 2Documento55 pagineCH4 2Imran AbdullahNessuna valutazione finora

- Philips Analog Cross ReferenceDocumento2 paginePhilips Analog Cross Referencetbscri0% (1)

- Generation of High ImpulseDocumento12 pagineGeneration of High ImpulseNeel Gala90% (10)

- User Guide FlowscannerDocumento137 pagineUser Guide FlowscannerJDavid NavaNessuna valutazione finora

- Alciatore Mechatronics Solution Manual 5th EditionDocumento16 pagineAlciatore Mechatronics Solution Manual 5th Editionsajal agarwalNessuna valutazione finora

- LC Filter For Three Phase Inverter ReportDocumento19 pagineLC Filter For Three Phase Inverter ReportMuthuRajNessuna valutazione finora

- Error Function Table PDFDocumento1 paginaError Function Table PDFPoulami Saanjhbati DasguptaNessuna valutazione finora

- Work Bench VerificationDocumento220 pagineWork Bench Verificationchkarthiksai0% (1)

- P&ID Part ListDocumento11 pagineP&ID Part Listvijayns_250355172Nessuna valutazione finora

- Arrow Sensor Guide Digital A4 Apr 25Documento43 pagineArrow Sensor Guide Digital A4 Apr 25Tzouralas TheodorosNessuna valutazione finora

- A Theoretical and Practical Guide To The Basics of Designing Air Flow SystemsDocumento40 pagineA Theoretical and Practical Guide To The Basics of Designing Air Flow SystemsKagitha TirumalaNessuna valutazione finora

- SEPIC ConverterDocumento16 pagineSEPIC ConverterDina GaranNessuna valutazione finora

- Pulsating Heat Pipe ReportDocumento65 paginePulsating Heat Pipe ReportIdul Azharul HoqueNessuna valutazione finora

- Engineering Drawing: North South UniversityDocumento14 pagineEngineering Drawing: North South UniversityMD. Zobayer Ahmed 1610766642Nessuna valutazione finora

- (Metasol MCCB) Catalog en 202105Documento160 pagine(Metasol MCCB) Catalog en 202105LUATNessuna valutazione finora

- C Programming On The Determination of Shear Force, Bending Moment, Shear Stress and Bending Stress of A BeamDocumento9 pagineC Programming On The Determination of Shear Force, Bending Moment, Shear Stress and Bending Stress of A BeamMamun Mehedee100% (1)

- iPRF and iPRD Surge ArrestersDocumento36 pagineiPRF and iPRD Surge ArrestersRobert CamargoNessuna valutazione finora

- Valves and Regulators - Turndown RatioDocumento3 pagineValves and Regulators - Turndown RatioklashincoviskyNessuna valutazione finora

- Transducer Curriculum Manual PDFDocumento366 pagineTransducer Curriculum Manual PDFAugusto GarciaNessuna valutazione finora

- Thermal Engineering - I Jntua Question PapersDocumento15 pagineThermal Engineering - I Jntua Question PapersHimadhar SaduNessuna valutazione finora

- Half-Wave Rectifier DC Motor With Freewheeling DiodeDocumento5 pagineHalf-Wave Rectifier DC Motor With Freewheeling Diodehamza abdo mohamoudNessuna valutazione finora

- v1.0 Rishabh Engineering CS 37 Piping Stress Analysis Horizontal HeaterDocumento4 paginev1.0 Rishabh Engineering CS 37 Piping Stress Analysis Horizontal HeaterJasonChong212Nessuna valutazione finora

- Pneumatic Note UNIT 4Documento12 paginePneumatic Note UNIT 4Syazrin Aklili Ab RahmanNessuna valutazione finora

- Vector Analysis of A Three Phase Stator - OA - WebPgDocumento13 pagineVector Analysis of A Three Phase Stator - OA - WebPgIvan Contrreras QuispeNessuna valutazione finora

- Vacon NX OPTC2 C8 Modbus N2 Board User Manual DPD0Documento42 pagineVacon NX OPTC2 C8 Modbus N2 Board User Manual DPD0TanuTiganuNessuna valutazione finora

- SW-5.1 3005 Service ManualDocumento17 pagineSW-5.1 3005 Service ManualBizoo76Nessuna valutazione finora

- Product List: Product Name Image Category / Sub Category Price DiscountDocumento3 pagineProduct List: Product Name Image Category / Sub Category Price DiscountuyaiekanemNessuna valutazione finora

- Variable Speed DriveDocumento66 pagineVariable Speed DriveRamaNessuna valutazione finora

- High Pressure Phase Behaviour of Multicomponent Fluid MixturesDa EverandHigh Pressure Phase Behaviour of Multicomponent Fluid MixturesNessuna valutazione finora

- Process Control System A Complete Guide - 2020 EditionDa EverandProcess Control System A Complete Guide - 2020 EditionNessuna valutazione finora

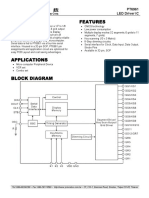

- Description Features: PT6964 LED Driver ICDocumento15 pagineDescription Features: PT6964 LED Driver ICDhivya NNessuna valutazione finora

- STLED316S: Serial-Interfaced 6-Digit LED Controller With KeyscanDocumento33 pagineSTLED316S: Serial-Interfaced 6-Digit LED Controller With KeyscanDhivya NNessuna valutazione finora

- Description Features: PT6961 LED Driver ICDocumento18 pagineDescription Features: PT6961 LED Driver ICDhivya NNessuna valutazione finora

- Description: Technical DataDocumento17 pagineDescription: Technical DataDhivya NNessuna valutazione finora

- The MOS TransistorDocumento49 pagineThe MOS TransistorLauraPiccinnoNessuna valutazione finora

- RX Family: User's Manual: Software Renesas 32-Bit Mcu RX FamilyDocumento278 pagineRX Family: User's Manual: Software Renesas 32-Bit Mcu RX FamilyDhivya NNessuna valutazione finora

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDocumento25 pagineMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NNessuna valutazione finora

- LCD-TFT Display Controller (LTDC) On STM32 MCUsDocumento91 pagineLCD-TFT Display Controller (LTDC) On STM32 MCUsamirmoh1992100% (1)

- LCD-TFT Display Controller (LTDC) On STM32 MCUsDocumento91 pagineLCD-TFT Display Controller (LTDC) On STM32 MCUsamirmoh1992100% (1)

- Description Features: PT6967 LED Driver ICDocumento22 pagineDescription Features: PT6967 LED Driver ICDhivya NNessuna valutazione finora

- Design and Implementation of Single-Phase Hybrid Active Power Filter Controller-LibreDocumento5 pagineDesign and Implementation of Single-Phase Hybrid Active Power Filter Controller-LibreDhivya NNessuna valutazione finora

- Sorting AlgorithmsDocumento17 pagineSorting AlgorithmsBilo BiloNessuna valutazione finora

- 2013 Arduino PID Lab 0Documento7 pagine2013 Arduino PID Lab 0Uma MageshwariNessuna valutazione finora

- Harmonics in Power Quality IssuesDocumento19 pagineHarmonics in Power Quality IssuesthomaswynnNessuna valutazione finora

- B.E. (Hons.) Electrical & Electronics: List of Discipline Core Courses: S. No. Course No. Course Title L P UDocumento4 pagineB.E. (Hons.) Electrical & Electronics: List of Discipline Core Courses: S. No. Course No. Course Title L P UDhivya NNessuna valutazione finora

- Assignment 3Documento2 pagineAssignment 3Dhivya NNessuna valutazione finora

- Ps Ex 1Documento2 paginePs Ex 1Dhivya NNessuna valutazione finora

- StringsDocumento6 pagineStringsDhivya NNessuna valutazione finora

- Daq Ni Usb 6009Documento30 pagineDaq Ni Usb 6009ramiro_vicente_6Nessuna valutazione finora

- Indian Electricity Act 2003Documento67 pagineIndian Electricity Act 2003Dhivya NNessuna valutazione finora

- Core Architecture:: Container BasedDocumento3 pagineCore Architecture:: Container BasedDhivya NNessuna valutazione finora

- Stacks and QueuesDocumento21 pagineStacks and QueuesDhivya NNessuna valutazione finora

- Resume Preparation Do's and Don'ts: Amrita Vishwa Vidyapeetham 2014Documento6 pagineResume Preparation Do's and Don'ts: Amrita Vishwa Vidyapeetham 2014Dhivya NNessuna valutazione finora

- Design of Active Harmonic Filter For A 3Documento10 pagineDesign of Active Harmonic Filter For A 3Dhivya NNessuna valutazione finora

- Electrical EngineeringDocumento2 pagineElectrical EngineeringSantosh SandyNessuna valutazione finora

- L01 ComputerSystemAnatomyDocumento14 pagineL01 ComputerSystemAnatomyDhivya NNessuna valutazione finora

- 9.speed Control of DC Motor Using Chopper DriveDocumento8 pagine9.speed Control of DC Motor Using Chopper DriveDhivya N100% (2)

- Theoretical Study On Active FiltersDocumento2 pagineTheoretical Study On Active FiltersDhivya NNessuna valutazione finora

- Soil AnalysisDocumento13 pagineSoil AnalysisDhivya NNessuna valutazione finora

- Core Architecture:: Container BasedDocumento3 pagineCore Architecture:: Container BasedDhivya NNessuna valutazione finora

- FINAL VERSION On Assessment Tool For CDCs LCs Sept. 23 2015Documento45 pagineFINAL VERSION On Assessment Tool For CDCs LCs Sept. 23 2015Edmar Cielo SarmientoNessuna valutazione finora

- Current Harmonics: Electric Power System Power QualityDocumento3 pagineCurrent Harmonics: Electric Power System Power QualityAlliver SapitulaNessuna valutazione finora

- Docket - CDB Batu GajahDocumento1 paginaDocket - CDB Batu Gajahfatin rabiatul adawiyahNessuna valutazione finora

- Institutions and StrategyDocumento28 pagineInstitutions and StrategyFatin Fatin Atiqah100% (1)

- ACC030 Comprehensive Project April2018 (Q)Documento5 pagineACC030 Comprehensive Project April2018 (Q)Fatin AkmalNessuna valutazione finora

- SHS G11 Reading and Writing Q3 Week 1 2 V1Documento15 pagineSHS G11 Reading and Writing Q3 Week 1 2 V1Romeo Espinosa Carmona JrNessuna valutazione finora

- TransistorsDocumento21 pagineTransistorsAhmad AzriNessuna valutazione finora

- Philippine Education Deteriorating - EditedDocumento3 paginePhilippine Education Deteriorating - EditedRukimi Yamato100% (1)

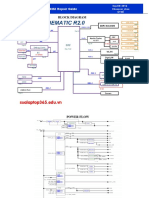

- Asus x453Documento5 pagineAsus x453Rhiry Ntuh AthryNessuna valutazione finora

- Ships Near A Rocky Coast With Awaiting Landing PartyDocumento2 pagineShips Near A Rocky Coast With Awaiting Landing PartyFouaAj1 FouaAj1Nessuna valutazione finora

- LU 5.1 ElectrochemistryDocumento32 pagineLU 5.1 ElectrochemistryNurAkila Mohd YasirNessuna valutazione finora

- Dependent ClauseDocumento28 pagineDependent ClauseAndi Febryan RamadhaniNessuna valutazione finora

- Work Sample 2 - Eoc and CrucibleDocumento35 pagineWork Sample 2 - Eoc and Crucibleapi-259791703Nessuna valutazione finora

- 9701 Nos Ps 23Documento5 pagine9701 Nos Ps 23Hubbak KhanNessuna valutazione finora

- Tax Havens IMF PDFDocumento59 pagineTax Havens IMF PDFClassic PhyXNessuna valutazione finora

- Overlay Control PlansDocumento1 paginaOverlay Control PlansSTS-SPARK GAMINGNessuna valutazione finora

- Chapter1 Intro To Basic FinanceDocumento28 pagineChapter1 Intro To Basic FinanceRazel GopezNessuna valutazione finora

- Advanced Herd Health Management, Sanitation and HygieneDocumento28 pagineAdvanced Herd Health Management, Sanitation and Hygienejane entunaNessuna valutazione finora

- An Enhanced Radio Network Planning Methodology For GSM-R CommunicationsDocumento4 pagineAn Enhanced Radio Network Planning Methodology For GSM-R CommunicationsNuno CotaNessuna valutazione finora

- Standard BMW PDFDocumento19 pagineStandard BMW PDFIna IoanaNessuna valutazione finora

- Level of Organisation of Protein StructureDocumento18 pagineLevel of Organisation of Protein Structureyinghui94Nessuna valutazione finora