Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

2012 Tese Racamara

Caricato da

rarison fortesTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

2012 Tese Racamara

Caricato da

rarison fortesCopyright:

Formati disponibili

UNIVERSIDADE FEDERAL DO CEAR

CENTRO DE TECNOLOGIA

PROGRAMA DE PS-GRADUAO EM ENGENHARIA ELTRICA

ANLISE COMPARATIVA DE DESEMPENHO DE

CONVERSORES CA-CC MONOFSICOS UTILIZANDO

FPGA PARA APLICAO EM NO-BREAKS

Raphael Amaral da Cmara

Fortaleza

Novembro de 2012

ii

RAPHAEL AMARAL DA CMARA

ANLISE COMPARATIVA DE DESEMPENHO DE

CONVERSORES CA-CC MONOFSICOS UTILIZANDO

FPGA PARA APLICAO EM NO-BREAKS

Tese submetida Universidade Federal do

Cear como parte dos requisitos para obteno

do grau de Doutor em Engenharia Eltrica.

Orientador: Prof. Dr. Ccero Marcos Tavares

Cruz

Co-orientador: Prof. Dr. Ren Pastor Torrico-

Bascop

Fortaleza

Novembro de 2012

Dados Internacionais de Catalogao na Publicao

Universidade Federal do Cear

Biblioteca de Ps-Graduao em Engenharia - BPGE

C174a Cmara, Raphael Amaral da.

Anlise comparativa de desempenho de conversores CA/CC monofsicos utilizando EPGA para

aplicao em no-breaks / Raphael Amaral da Cmara 2012.

205 f. : il. enc. ; 30 cm.

Tese (doutorado) Universidade Federal do Cear, Centro de Tecnologia, Programa de Ps-

Graduao em Engenharia Eltrica, Fortaleza, 2012

rea de Concentrao: Eletrnica de potncia e acionamento de mquinas.

Orientao: Prof. Dr. Ccero Marcos Tavares Cruz.

Coorientao: Prof. Dr. Ren Pastor Torrico-Bascop.

1. Engenharia Eltrica. 2. Eletrnica de potncia. 3. Conversores de corrente eltrica. I. Ttulo.

CDD 621.3

iii

iv

A persistncia realiza o impossvel.

(Ditado chins)

Tudo o que, na orao, perdirdes com f, vs o recebereis.

(Mt 21, 22)

v

A Deus,

Meu Criador, Salvador e Consolador!

Aos meus pais Edel e Wilson,

minha esposa Amanda

e nossos filhos Thvyne Sophia e Raphael Mikhail,

A todos os familiares e amigos,

Eu dedico esse trabalho.

vi

AGRADECIMENTOS

CAPES que contribuiu em parte com o apoio financeiro necessrio realizao

desse trabalho e desenvolvimento cientfico.

Ao professor Ccero Marcos Tavares Cruz por suas valiosas orientaes, amizade,

fora e disponibilidade durante todo este tempo, da graduao ao doutorado. Agradeo a

confiana em mim depositada. Quero tambm agradecer ao co-orientador professor Ren

Pastor Torrico-Bascop por todas as suas valiosas e criteriosas colaboraes desde o incio do

curso durante as disciplinas, passando pela concepo desta tese e grande auxlio em sua

execuo atravs de conselhos e disponibilidade fsica e material.

Aos professores do Departamento de Engenharia Eltrica da UFC, Fernando Antunes,

Luiz Henrique, Demercil, Artur, Bismarck e a todos os servidores Rafael, Mrio e

Geraldinho, responsveis diretamente ou indiretamente pela minha formao na graduao,

mestrado e doutorado. Deixo aqui meu agradecimento especial ao professor Paulo Praa pela

grande colaborao e incentivo no uso do controle digital, pelo companheirismo e enorme

amizade.

Aos meus amigos e colegas de ps-graduao (em ordem alfabtica): Andr, Davi

J oca, Elmano, Fabola, Hermnio, Lincoln, Ranoyca, Samuel J , Serginho, por todas as etapas

que foram vencidas, companheirismo e contribuies tcnicas. Ao tcnico do GPEC, Pedro

Augusto, um agradecimento especial pelas contribuies prticas e tcnicas e pela amizade.

Aos meus colegas professores da Universidade Federal Rural do Semirido (em ordem

alfabtica): Adelson, Adriano Aaron, Augusto Pavo, Bruno Emanuel, Fabiana, Francisco

Targino, Humberto, Idalmir, Patrocnio, pelo apoio, incentivo e compreenso para que eu

pudesse chegar a este momento de titulao e um agradecimento especial aos Profs. Gustavo

Henn e Victor Aguiar pelo companheirismo e amizade.

Aos meus amigos mais antigos (em ordem alfabtica): Aldiel, Babim, Branquim,

Deivid, Dielle, Gessi, Ivina, Iviane, J ackson, J onhny, J nior, Larissa, Mrcio, Ricardo, Trcio,

Tidy e Vilemar por todos os momentos de entretenimento, futebol e metal e, ao meus novos

amigos (em ordem alfabtica): Aclinton e Paula, Beron e Mrcia, Igor e Izabel, Rocha J nior

e Elen, Svio e Luzirane, por todos os momentos adultos de convivncia de casais e filhos.

A meus amigos de infncia Rondinelle, Mickaele, Marcelo, Liana, Rosa, Marquinhos,

Neto, Aritana, Narclio, Nen, Mrcio, Paulinho, Lano, Nilzinha, Marta, Marna, Wilame,

Sara, Samuel, Daniel, Hlio, Marciano, Rafael Coco, Rafael Pipoca, Ilton e Cntia por

todos os momentos de uma infncia feliz e formadora do meu carter.

vii

A todos os meus familiares, em especial, aos meus avs Alicio e Cidoca por sempre

incentivarem minha formao profissional e pelas grandes ajudas nos momentos de maiores

necessidades em minha vida.

minha amada esposa Amanda que sempre me apoiou para a concluso deste

trabalho com incentivo e muito amor e que compreendeu os momentos difceis. Aos meus

filhos Thvyne Sophia e Raphael Mikhail que me ensinam a cada dia com suas conquistas e

realizaes.

todas as pessoas que por motivo de esquecimento no foram citadas anteriormente,

vou deixando neste espao minhas sinceras desculpas.

viii

da Cmara, R. A. Anlise Comparativa de Desempenho de Conversores CA-CC

Monofsicos Utilizando FPGA para Aplicao em No-breaks, Universidade Federal do

Cear UFC, 2012, 232p.

Esta tese de doutorado apresenta duas novas topologias de conversores CA-CC com uso de

neutro comum: conversor de cinco nveis intercalado e conversor de cinco nveis tipo T. Alm

disso, uma nova forma de implementao da tcnica de controle indireto da corrente (Indirect

Current Control - ICC) apresentada. Assim, para comprovao da praticidade dos

conversores apresentados, toma-se como base o conversor CA-CC de trs nveis convencional

e ento realizada uma anlise comparativa de desempenho entre esses trs conversores CA-

CC monofsicos para aplicao em no-breaks. Os conversores analisados possuem como

caracterstica comum a correo do fator de potncia, o controle digital realizado por FPGA e

a conexo da fonte de alimentao com o estgio de sada, facilitando o uso de inversor e by-

pass para no-breaks. O primeiro conversor analisado o conversor de trs nveis

convencional que apresenta como principal caracterstica o reduzido nmero de componentes.

O segundo conversor analisado o conversor de cinco nveis intercalado que apresenta como

principal caracterstica as reduzidas perdas de comutao e conduo. Finalmente, o terceiro

conversor analisado o conversor de cinco nveis tipo T que apresenta como principais

caractersticas: reduzidas perdas de comutao e conduo; os elementos magnticos operam

com o dobro da frequncia de comutao reduzindo desta maneira o peso e o volume. A

anlise terica dos conversores monofsicos, os conceitos bsicos sobre o controle digital e a

tcnica de modulao, a metodologia de projeto, simulao e resultados experimentais dos

prottipos construdos so apresentados para validar o princpio de funcionamento dos

conversores propostos.

Palavras-Chave: anlise comparativa, clula de comutao tipo T, correo de fator de

potncia, FPGA, no-break, conversores CA-CC.

ix

da Cmara, R. A. Comparative Analysis of Performance of Single Phase AC-DC Converters

Using FPGA for UPS Applications, Universidade Federal do Cear UFC, 2012, 232p.

This thesis presents two novel topologies of AC-DC converters with common neutral: five-

level interleaved converter and five-level T type converter. Besides, a novel type of

implementation of Indirect Current Control (ICC) is also presented. Thus, a comparative

analysis of performance between three single phase AC-DC converters for UPS applications

is realized. The analyzed converters have as common characteristics: power factor correction,

digital control using FPGA and connection between input power supply and converter output

enabling the use of UPS inverter and by-pass. The first one analyzed converter is the

conventional three level converter which presents as main feature reduced numbers of power

semiconductors and components. The second one analyzed converter is the five level

interleaving converter which presents as main feature reduced conduction and commutation

losses. Finally, the last one analyzed converter is the T type five level converter which

presents as main features: reduced conduction and commutation losses and magnetic

components operating with the double of switching frequency reducing weight and volume.

Theoretical analysis of the single phase converters, basics concepts of digital control and

modulation technique, design procedure, simulation and experimental results of lab models

are presented in order to validate the principle of operation of the proposed converters.

Keywords: comparative analysis, T type switching cell, power factor correction,

FPGA, UPS, AC-DC converters

x

SUMRIO

LISTA DE FIGURAS .............................................................................................................xiv

LISTA DE TABELAS ...........................................................................................................xxii

SIMBOLOGIA......................................................................................................................xxiii

INTRODUO GERAL ........................................................................................................... 1

CAPTULO 1

CONVERSORES MONOFSICOS CA-CC COM CORREO DO FATOR DE

POTNCIA: TOPOLOGIAS E TCNICAS DE CONTROLE................................................. 4

1.1 Introduo.................................................................................................................... 4

1.2 Topologias de Conversores Monofsicos CA-CC....................................................... 5

1.3 Tcnicas de Controle para Conversores CA-CC....................................................... 11

1.4 Gerao da Clula de Comutao Tipo T.................................................................. 16

1.5 Motivao e Proposta de Tese de Doutorado............................................................ 19

1.6 Concluses................................................................................................................. 22

CAPTULO 2

TCNICA DE CONTROLE DIGITAL USANDO FPGA...................................................... 23

2.1 Introduo.................................................................................................................. 23

2.2 FPGAs (Field Programmable Gate Arrays) ............................................................. 23

2.2.1 Arquitetura do FPGA ....................................................................................... 24

2.2.2 Programao no FPGA.................................................................................... 28

2.2.3 O FPGA EP2C20F484C .................................................................................. 29

2.3 Tratamento de Sinais Utilizado para Aplicao ao FPGA........................................ 30

2.3.1 Amostragem...................................................................................................... 31

2.3.2 Circuitos Conversores A/D e D/A e de Interface ............................................. 33

2.4 Tcnica de Controle Aplicada ao FPGA................................................................... 35

2.5 Funes de Transferncia Discretizadas.................................................................... 38

2.6 Programao do FPGA.............................................................................................. 45

2.7 Circuitos de Drivers .................................................................................................. 48

2.8 Concluses................................................................................................................. 48

CAPTULO 3

CONVERSOR CA-CC MONOFSICO DE TRS NVEIS CONVENCIONAL ............. 50

3.1 Introduo.................................................................................................................. 50

3.2 Anlise Qualitativa .................................................................................................... 50

xi

3.2.1 Topologia e Princpio de Funcionamento........................................................ 50

3.2.2 Etapas de Operao Semiciclo Positivo da Tenso de Entrada ................... 52

3.2.3 Etapas de Operao Semiciclo Negativo da Tenso de Entrada.................. 54

3.3 Anlise Quantitativa do Estgio de Potncia............................................................. 57

3.3.1 Operao em Regime Permanente ................................................................... 57

3.3.2 Determinao do Ganho Esttico .................................................................... 58

3.3.3 Variao da Razo Cclica............................................................................... 58

3.3.4 Determinao da Ondulao de Corrente de Entrada .................................... 59

3.3.5 Determinao da Ondulao de Tenso no Capacitor C1 .............................. 61

3.3.6 Anlise dos Esforos de Tenso e Corrente no Conversor .............................. 65

3.4 Modelagem do Circuito de Potncia ......................................................................... 68

3.5 Exemplo de Projeto ................................................................................................... 72

3.5.1 Especificaes e Consideraes....................................................................... 72

3.5.2 Dimensionamento dos Componentes................................................................ 72

3.5.3 Projeto do Estgio de Controle........................................................................ 75

3.6 Rendimento Terico .................................................................................................. 80

3.6.1 Modelagem de Perdas ...................................................................................... 80

3.6.2 Clculo Trmico ............................................................................................... 85

3.7 Resultados de Simulao e Experimentais ................................................................ 85

3.8 Concluses................................................................................................................. 96

CAPTULO 4

CONVERSOR CA-CC MONOFSICO DE CINCO NVEIS INTERCALADO.................. 97

4.1 Introduo.................................................................................................................. 97

4.2 Anlise Qualitativa .................................................................................................... 97

4.2.1 Topologia e Princpio de Funcionamento........................................................ 97

4.2.2 Etapas de Operao para o Modo de No Sobreposio .............................. 100

4.2.3 Etapas de Operao para o Modo de Sobreposio...................................... 104

4.3 Anlise Quantitativa do Estgio de Potncia........................................................... 107

4.3.1 Operao em Regime Permanente ................................................................. 107

4.3.2 Determinao do Ganho Esttico .................................................................. 107

4.3.3 Variao da Razo Cclica............................................................................. 108

4.3.4 Determinao da Ondulao de Corrente de Entrada .................................. 109

4.3.5 Determinao da Ondulao de Tenso ........................................................ 111

4.3.6 Anlise dos Esforos de Tenso e Corrente no Conversor ............................ 112

xii

4.4 Modelagem do Circuito de Potncia ....................................................................... 115

4.5 Exemplo de Projeto ................................................................................................. 116

4.5.1 Especificaes e Consideraes..................................................................... 116

4.5.2 Dimensionamento dos Componentes.............................................................. 116

4.5.3 Projeto do Estgio de Controle...................................................................... 119

4.6 Rendimento Terico ................................................................................................ 120

4.7 Resultados de Simulao e Experimentais .............................................................. 123

4.8 Concluses............................................................................................................... 134

CAPTULO 5

CONVERSOR CA-CC MONOFSICO DE CINCO NVEIS TIPO T................................ 136

5.1 Introduo................................................................................................................ 136

5.2 Anlise Qualitativa .................................................................................................. 136

5.2.1 Topologia e Princpio de Funcionamento...................................................... 136

5.2.2 Etapas de Operao para o Modo de No Sobreposio .............................. 138

5.2.3 Etapas de Operao para o Modo de Sobreposio...................................... 142

5.3 Anlise Quantitativa do Estgio de Potncia........................................................... 145

5.3.1 Operao em Regime Permanente ................................................................. 145

5.3.2 Determinao do Ganho Esttico .................................................................. 145

5.3.3 Variao da Razo Cclica............................................................................. 146

5.3.4 Determinao da Ondulao de Corrente de Entrada .................................. 147

5.3.5 Determinao da Ondulao de Tenso ........................................................ 150

5.3.6 Anlise dos Esforos de Tenso e Corrente no Conversor ............................ 150

5.4 Modelagem do Circuito de Potncia ....................................................................... 154

5.5 Exemplo de Projeto ................................................................................................. 155

5.5.1 Especificaes e Consideraes..................................................................... 155

5.5.2 Dimensionamento dos Componentes.............................................................. 155

5.5.3 Projeto do Estgio de Controle...................................................................... 158

5.6 Rendimento Terico ................................................................................................ 159

5.7 Resultados de Simulao e Experimentais .............................................................. 163

5.8 Concluses............................................................................................................... 176

CAPTULO 6

ANLISE COMPARATIVA DE DESEMPENHO DOS TRS CONVERSORES CA-CC

MONOFSICOS ESTUDADOS........................................................................................... 178

6.1 Introduo................................................................................................................ 178

xiii

6.2 Anlise dos Principais Parmetros dos Conversores............................................... 178

6.3 Anlise do Rendimento ........................................................................................... 182

6.4 Anlise do Peso e Volume....................................................................................... 183

6.5 Anlise do Desempenho Dinmico ......................................................................... 184

6.6 Concluses............................................................................................................... 185

CONCLUSO GERAL ......................................................................................................... 186

REFERNCIAS BIBLIOGRFICAS................................................................................... 191

APNDICE A.........................................................................................................................197

APNDICE B.........................................................................................................................202

xiv

LISTA DE FIGURAS

Fig. 1.1 Topologia do conversor boost clssico com CFP. ..................................................... 6

Fig. 1.2 Topologias de conversores usando a tcnica de paralelismo de conversores: (a)

boost em paralelo [11]; (b) boost intercalado [12-14]. ............................................................... 6

Fig. 1.3 Aplicao de clulas de comutao PWM: (a) dois estados; (b) trs estados [16]. ... 7

Fig. 1.4 Topologia do conversor duplo boost com CFP: (a) indutor no lado CA [17]; .......... 8

Fig. 1.5 (a) Topologia do conversor duplo boost com um interruptor [19]; (b) aplicando a

clula de comutao de trs estados [20]. .................................................................................. 9

Fig. 1.6 Topologia do conversor boost bridgeless com CFP. ................................................. 9

Fig. 1.7 Topologia do conversor boost de trs nveis............................................................ 10

Fig. 1.8 Configuraes bsicas de interruptores bidirecionais (i), (ii) e (iii)......................... 10

Fig. 1.9 Topologia do conversor boost de trs nveis convencional com interruptor

bidirecional. .............................................................................................................................. 11

Fig. 1.10 Diagrama funcional da tcnica de controle por conduo descontnua. ................ 12

Fig. 1.11 Diagrama funcional da tcnica de controle por conduo crtica. ......................... 12

Fig. 1.12 Diagrama funcional do controle por histerese........................................................ 13

Fig. 1.13 Diagrama funcional do controle por corrente de pico............................................ 13

Fig. 1.14 Diagrama funcional do controle por corrente mdia.............................................. 14

Fig. 1.15 Diagrama funcional do autocontrole. ..................................................................... 15

Fig. 1.16 Diagrama funcional do controle em cada ciclo. ..................................................... 15

Fig. 1.17 Gerao da clula de comutao Tipo T. ............................................................... 17

Fig. 1.18 Gerao da clula de comutao Tipo T de 3 enrolamentos.................................. 18

Fig. 1.19 Clula de comutao multinvel de n estados. ....................................................... 19

Fig. 1.20 Configurao bsica de um no-break on-line com CFP. ....................................... 19

Fig. 1.21 Configurao de um no-break on-line no isolado com CFP. ............................... 20

Fig. 1.22 Topologia do conversor CA-CC boost de trs nveis convencional com CFP. ..... 21

Fig. 1.23 Topologia do conversor CA-CC boost intercalado de trs nveis com CFP. ......... 21

Fig. 1.24 Topologia do conversor CA-CC boost de cinco nveis aplicado a clula de

comutao tipo T. ..................................................................................................................... 21

Fig. 2.1 Arquitetura tpica de um FPGA. .............................................................................. 25

Fig. 2.2 - Estrutura da clula lgica do FPGA EP2C20F484C7. ............................................. 26

Fig. 2.3 Estrutura do bloco de multiplicao do FPGA EP2C20F484C7. ............................ 27

Fig. 2.4 Rede de distribuio de clock................................................................................... 27

xv

Fig. 2.5 Placa de desenvolvimento Cyclone II Starter Kit da Altera..................................... 30

Fig. 2.6 Diagrama de blocos da placa de desenvolvimento [61]. .......................................... 30

Fig. 2.7 (a) Sistema de controle analgico. (b) Sistema de controle digital. ......................... 31

Fig. 2.8 Discretizao de um sinal contnuo u(t) em sinal discreto u(kT). ............................ 32

Fig. 2.9 Circuitos de interface dos conversores A/D. ............................................................. 33

Fig. 2.10 Circuitos de interface de medio das tenses de sada. ........................................ 34

Fig. 2.11 Circuitos de interface de medio da corrente de entrada...................................... 35

Fig. 2.12 Conversor D/A tipo R-2R de 8 bits........................................................................ 35

Fig. 2.13 Diagrama funcional bsico do controle por corrente mdia de entrada para CFP e

suas principais formas de onda. ................................................................................................ 36

Fig. 2.14 Diagrama funcional do OCC e suas principais formas de onda............................. 36

Fig. 2.15 Diagrama funcional do controle ICC e suas principais formas de onda. ............... 37

Fig. 2.16 Principais formas de onda do ICC para CFP. ........................................................ 38

Fig. 2.17 Diagrama mostrando a correspondncia entre um caminho de pontos na faixa

primria do plano s e o caminho correspondente no crculo unitrio do plano z. .................... 40

Fig. 2.18 Sistema discreto em malha fechada. ...................................................................... 41

Fig. 2.19 Diagramas mostrando o mapeando do plano s para o plano z e do plano z para o

plano w. .................................................................................................................................... 42

Fig. 2.20 Diagrama de blocos completo do controle digital realizado no Quartus II Web

Edition. ..................................................................................................................................... 45

Fig. 2.21 Diagrama de blocos do gerenciamento de clock e gerao das portadoras............ 46

Fig. 2.22 Diagrama de blocos do compensador digital e tenso de controle. ....................... 47

Fig. 2.23 Diagrama de blocos dos multiplicadores e moduladores PWM. ........................... 47

Fig. 2.24 Esquemtico bsico do circuito de driver utilizado para o acionamento dos

interruptores.............................................................................................................................. 48

Fig. 3.1 Topologia do conversor CA-CC de trs nveis convencional com interruptores e

diodos em paralelo............................................................................................................ 51

Fig. 3.2 Formas de onda da tenso de entrada e tenso V

AO

para o conversor monofsico de

trs nveis.......................................................................................................................... 52

Fig. 3.3 1 etapa de operao do conversor para o semiciclo positivo da tenso de entrada. 53

Fig. 3.4 2 etapa de operao do conversor para o semiciclo positivo da tenso de entrada. 53

Fig. 3.5 Principais formas de onda idealizadas para o semiciclo positivo da tenso de

entrada. ............................................................................................................................. 54

Fig. 3.6 1 etapa de operao do conversor para o semiciclo negativo da tenso de entrada.

xvi

.......................................................................................................................................... 55

Fig. 3.7 2 etapa de operao do conversor para o semiciclo negativo da tenso de entrada.

.......................................................................................................................................... 55

Fig. 3.8 Principais formas de onda idealizadas para o modo de operao de sobreposio.. 56

Fig. 3.9 Circuito do conversor de trs nveis para o semiciclo positivo da tenso de entrada.

.......................................................................................................................................... 57

Fig. 3.10 Variao da razo cclica em funo do tempo para um perodo da tenso de

entrada. ............................................................................................................................. 59

Fig. 3.11 Variao da ondulao da corrente parametrizada para meio perodo da rede. ..... 60

Fig. 3.12 Circuito equivalente do estgio de sada do conversor para o semiciclo positivo da

tenso de entrada. ............................................................................................................. 62

Fig. 3.13 Forma de onda da corrente no capacitor de filtro C1 para um perodo da rede. .... 62

Fig. 3.14 Forma de onda das tenses parametrizadas nos capacitores C1 e C2 e da tenso de

sada total parametrizada para um perodo da rede. ......................................................... 65

Fig. 3.15 Diagrama de blocos do controle do conversor por ICC. ........................................ 69

Fig. 3.16 Modelo do conversor para determinao da funo de transferncia G(s). ........... 70

Fig. 3.17 Diagrama de Bode da funo de transferncia do compensador. .......................... 71

Fig. 3.18 Diagrama de blocos do controle do conversor. ...................................................... 75

Fig. 3.19 Diagrama de Bode da funo de transferncia FTMA(s). (a) Ganho, (b) Fase. .... 77

Fig. 3.20 Diagrama de Bode da funo de transferncia C(s). (a) Ganho, (b) Fase.............. 78

Fig. 3.21 Diagrama de Bode da funo de transferncia FTLA(s). (a) Ganho, (b) Fase. ..... 78

Fig. 3.22 Curva de sada caracterstica de sada do IGBT IRGP50B60PD........................... 82

Fig. 3.23 Formas de onda da tenso e corrente de entrada. ................................................... 86

Fig. 3.24 Formas de onda da tenso e da corrente de sada do conversor para plena carga.. 86

Fig. 3.25 Formas de onda da tenso e corrente no indutor L

b

na frequncia da rede............ 87

Fig. 3.26 Formas de onda da tenso e corrente no indutor L

b

na frequncia de comutao. 87

Fig. 3.27 Formas de onda da tenso e corrente no interruptor S1 na frequncia da rede...... 88

Fig. 3.28 Formas de onda da tenso e corrente no interruptor S1 na frequncia de

comutao. ........................................................................................................................ 88

Fig. 3.29 Formas de onda da tenso e corrente no diodo D1 na frequncia da rede. ............ 89

Fig. 3.30 Formas de onda da tenso e corrente no diodo D1 na frequncia de comutao... 89

Fig. 3.31 Formas de onda das tenses de sada e corrente de sada para um degrau de carga

de 50% para carga nominal. ............................................................................................. 90

Fig. 3.32 Formas de onda dos principais sinais de controle do conversor: v

m

, v

c

e V

iinamost

. 90

Fig. 3.33 Vista geral do prottipo implementado em laboratrio usando FPGA. ................. 91

Fig. 3.34 Resultados experimentais: 1. Tenso de entrada (100V/div); 2. Corrente de entrada

(50A/div); 3. Tenso de sada V

o1

(100V/div); 4. Tenso de sada V

o2

(100V/div); 5.

Tenso de sada total (100V/div). Tempo (5ms/div). ....................................................... 91

xvii

Fig. 3.35 Espectro harmnico da corrente de entrada. .......................................................... 92

Fig. 3.36 Formas de onda sobre L

b

. (a) na frequncia da rede: 1. Tenso (100V/div), 2.

Corrente (50A/div), tempo (5ms/div); (b) na frequncia de comutao: 1. Tenso

(100V/div), 2. Corrente (20A/div), tempo (20s/div). ..................................................... 92

Fig. 3.37 Formas de onda no interruptor S1. (a) na frequncia da rede: 1. Tenso

(100V/div); 2. Corrente (10A/div); tempo (5ms/div). (b) na frequncia de comutao: 1.

Tenso (100V/div); 2. Corrente (20A/div), tempo (20s/div).. ....................................... 93

Fig. 3.38 Detalhe da comutao (a) no acionamento do interruptor (100V/div, 10A/div); (b)

no bloqueio do interruptor (100V/div, 10A/div). Tempo (200ns/div). ............................ 93

Fig. 3.39 Formas de onda no diodo D1. (a) na frequncia da rede: 1. Tenso (100V/div); 2.

Corrente (5A/div); tempo (5ms/div). (b) na frequncia de comutao: 1. Tenso

(100V/div); 2. Corrente (5A/div); tempo (20s/div)........................................................ 94

Fig. 3.40 Detalhe da comutao (a) no acionamento do diodo (100V/div, 5A/div); (b) no

bloqueio do interruptor (100V/div, 5A/div). Tempo (500ns/div). ................................... 94

Fig. 3.41 Formas de onda das tenses de sada em cada capacitor, no barramento total e

corrente de carga (10A/div, 100V/div, 100V/div, 100V/div, 200ms/div)........................ 95

Fig. 3.42 Formas de onda dos principais sinais de controle do retificador: v

m

, v

isample

e v

c

. . 95

Fig. 3.43 Curva de rendimento do conversor de trs nveis convencional. ........................... 96

Fig. 4.1 - (a) conversor de trs nveis convencional; (b) clula de comutao intercalada; (c)

conversor de cinco nveis intercalado obtido. .................................................................. 98

Fig. 4.2 Topologia do conversor monofsico de cinco nveis intercalado proposto. ............ 98

Fig. 4.3 Modos de operao do conversor em um perodo da rede. ...................................... 99

Fig. 4.4 Formas de onda da tenso de entrada e tenses V

AO

e V

AO

para o conversor de

cinco nveis intercalado. ................................................................................................. 100

Fig. 4.5 - Formas de onda da tenso de entrada e tenso total (V

AO

+ V

AO

) para o conversor

de cinco nveis intercalado. ............................................................................................ 100

Fig. 4.6 1 etapa de operao. .............................................................................................. 101

Fig. 4.7 2 e 4 etapa de operao. ....................................................................................... 101

Fig. 4.8 3 etapa de operao. .............................................................................................. 102

Fig. 4.9 Principais formas de onda idealizadas para o modo de operao de no

sobreposio. .................................................................................................................. 103

Fig. 4.10 1 e 3 etapa de operao. ..................................................................................... 104

Fig. 4.11 2 etapa de operao. ............................................................................................ 105

Fig. 4.12 4 etapa de operao. ............................................................................................ 105

Fig. 4.13 Principais formas de onda idealizadas para o modo de operao de sobreposio.

........................................................................................................................................ 106

Fig. 4.14 Variao da razo cclica em funo do tempo para um perodo da tenso de

entrada. ........................................................................................................................... 108

xviii

Fig. 4.15 Variao da ondulao da corrente parametrizada para meio perodo da rede. ... 110

Fig. 4.16 Forma de onda da corrente no capacitor de filtro C1 para um perodo da rede. .. 111

Fig. 4.17 Diagrama de blocos do controle do conversor por ICC. ...................................... 115

Fig. 4.18 Diagrama de blocos do controle do conversor. .................................................... 119

Fig. 4.19 Formas de onda da tenso e corrente de entrada. ................................................. 123

Fig. 4.20 Formas de onda da tenso e da corrente de sada do conversor para plena carga.

........................................................................................................................................ 124

Fig. 4.21 Formas de onda da tenso e corrente no indutor L

b1

na frequncia da rede. ....... 124

Fig. 4.22 Formas de onda da tenso e corrente nos indutores e corrente de entrada na

frequncia de comutao: ............................................................................................... 125

Fig. 4.23 Formas de onda da tenso e corrente no interruptor S1 na frequncia da rede.... 125

Fig. 4.24 Formas de onda da tenso e corrente no interruptor S1 na frequncia de

comutao:...................................................................................................................... 126

Fig. 4.25 Formas de onda da tenso e corrente no diodo D1 na frequncia da rede. .......... 126

Fig. 4.26 Formas de onda da tenso e corrente no diodo D1 na frequncia de comutao: 127

Fig. 4.27 Formas de onda das tenses de sada e corrente de sada para um degrau de carga

de 50% para carga nominal. ........................................................................................... 127

Fig. 4.28 Formas de onda dos principais sinais de controle do retificador: v

m

, v

c

e V

iinamost

.

........................................................................................................................................ 128

Fig. 4.29 Vista geral do prottipo implementado em laboratrio. ...................................... 128

Fig. 4.30 Resultados experimentais: 1. Tenso de entrada (100V/div); 2. Corrente de entrada

(50A/div); 3. Corrente em L

b1

(100V/div); 4. Tenso de sada V

o1

(100V/div); 5. Tenso

de sada V

o2

(100V/div); 6. Tenso de sada total (100V/div). Tempo (5ms/div). ........ 129

Fig. 4.31 Espectro harmnico da corrente de entrada. ........................................................ 129

Fig. 4.32 Formas de onda sobre L

b1

na frequncia da rede: 1. Tenso (100V/div); 2.

Corrente (20A/div); Tempo (5ms/div). .......................................................................... 130

Fig. 4.33 Formas de onda nos indutores L

b1

e L

b2

e da corrente de entrada na frequncia de

comutao: 1. V

Lb1

(100V/div), 2. V

Lb2

(100V/div), 3. I

Lb1

(10A/div), 4. I

Lb2

(10A/div), 5.

I

in

(10A/div), tempo (20s/div). (a) modo de no-sobreposio; (b) modo de

sobreposio ................................................................................................................... 130

Fig. 4.34 Formas de onda sobre S1 na frequncia da rede: 1. Tenso (200V/div); 2. Corrente

(20A/div); Tempo (5ms/div) .......................................................................................... 131

Fig. 4.35 Formas de onda no interruptor S1 na frequncia de comutao: 1. Tenso

(100V/div), 2. Corrente (10A/div), tempo (20s/div). (a) modo de no-sobreposio; (b)

modo de sobreposio. ................................................................................................... 131

Fig. 4.36 Detalhe da comutao (a) no acionamento do interruptor (50V/div, 5A/div); (b) no

bloqueio do interruptor (50V/div, 5A/div). Tempo (200ns/div). ................................... 132

Fig. 4.37 Formas de onda sobre D1 na frequncia da rede: 1. Tenso (200V/div); 2.

xix

Corrente (10A/div); Tempo (5ms/div). .......................................................................... 132

Fig. 4.38 Formas de onda no diodo D1 na frequncia de comutao: 1. Tenso (100V/div),

2. Corrente (10A/div), tempo (20s/div). (a) modo de no-sobreposio; (b) modo de

sobreposio. .................................................................................................................. 132

Fig. 4.39 Detalhe da comutao (a) no acionamento do diodo (50V/div, 5A/div); (b) no

bloqueio do diodo (50V/div, 5A/div). Tempo (200ns/div). ........................................... 133

Fig. 4.40 Formas de onda das tenses de sada em cada capacitor, no barramento total e

corrente de carga para um degrau de carga de 50% para carga nominal (50V/div,

50V/div, 100V/div, 5A/div, 200ms/div)......................................................................... 133

Fig. 4.41 Formas de onda dos principais sinais de controle do conversor: v

isample

, v

m

e v

c

. 134

Fig. 4.42 Curva de rendimento do conversor intercalado de cinco nveis........................... 134

Fig. 5.1 - (a) conversor de trs nveis convencional; (b) clula de comutao tipo T; (c)

conversor de cinco nveis tipo T obtido. ........................................................................ 137

Fig. 5.2 Topologia do conversor monofsico de cinco nveis tipo T proposto. .................. 137

Fig. 5.3 Formas de onda da tenso de entrada e tenso V

AO

para o conversor monofsico de

cinco nveis. .................................................................................................................... 138

Fig. 5.4 1 etapa de operao. .............................................................................................. 139

Fig. 5.5 2 e 4 etapa de operao. ....................................................................................... 139

Fig. 5.6 3 etapa de operao. .............................................................................................. 140

Fig. 5.7 Principais formas de onda idealizadas para o modo de operao de no

sobreposio. .................................................................................................................. 141

Fig. 5.8 1 e 3 etapa de operao. ....................................................................................... 142

Fig. 5.9 2 etapa de operao. .............................................................................................. 143

Fig. 5.10 4 etapa de operao. ............................................................................................ 143

Fig. 5.11 Principais formas de onda idealizadas para o modo de operao de sobreposio.

........................................................................................................................................ 144

Fig. 5.12 Variao da razo cclica em funo do tempo para um perodo da tenso de

entrada. ........................................................................................................................... 147

Fig. 5.13 Variao da ondulao da corrente parametrizada para meio perodo da rede. ... 148

Fig. 5.14 Forma de onda da corrente no capacitor de filtro C1 para um perodo da rede. .. 150

Fig. 5.15 Diagrama de blocos do controle do conversor por ICC. ...................................... 154

Fig. 5.16 Diagrama de blocos do controle do conversor. .................................................... 159

Fig. 5.17 Formas de onda da tenso e corrente de entrada. ................................................. 164

Fig. 5.18 Formas de onda da tenso e da corrente de sada do conversor para plena carga.

........................................................................................................................................ 164

Fig. 5.19 Formas de onda da tenso e corrente no indutor na frequncia da rede............... 165

Fig. 5.20 Formas de onda da tenso e corrente no indutor na frequncia de comutao: ... 165

Fig. 5.21 Formas de onda da tenso e corrente no enrolamento T1 na frequncia da rede. 166

xx

Fig. 5.22 Formas de onda da tenso e corrente no enrolamento T1 na frequncia de

comutao:...................................................................................................................... 166

Fig. 5.23 Formas de onda da tenso e corrente no interruptor S1 na frequncia da rede.... 167

Fig. 5.24 Formas de onda da tenso e corrente no interruptor S1 na frequncia de

comutao:...................................................................................................................... 167

Fig. 5.25 Formas de onda da tenso e corrente no diodo D1 na frequncia da rede. .......... 168

Fig. 5.26 Formas de onda da tenso e corrente no diodo D1 na frequncia de comutao: 168

Fig. 5.27 Formas de onda das tenses de sada e corrente de sada para um degrau de carga

de 50% para carga nominal. ........................................................................................... 169

Fig. 5.28 Formas de onda dos principais sinais de controle do retificador: v

m

, v

c

e V

iinamost

.

........................................................................................................................................ 169

Fig. 5.29 Vista geral do prottipo implementado em laboratrio usando FPGA. ............... 170

Fig. 5.30 Resultados experimentais: 1. Tenso de entrada (100V/div); 2. Corrente de entrada

(50A/div); 3. Tenso de sada V

o1

(100V/div); 4. Tenso de sada V

o2

(100V/div); 5.

Tenso de sada total (100V/div). Tempo (5ms/div).. .................................................... 170

Fig. 5.31 Espectro harmnico da corrente de entrada. ........................................................ 171

Fig. 5.32 Formas de onda sobre L

b

na frequncia da rede: 1. Tenso (100V/div); 2. Corrente

(50A/div); Tempo (5ms/div). ......................................................................................... 171

Fig. 5.33 Formas de onda no indutor L

b

na frequncia de comutao: (a) modo de no-

sobreposio - 1. Tenso (100V/div), 2. Corrente (20A/div), tempo (10s/div); (b) modo

de sobreposio 1. Tenso (100V/div), 2. Corrente (10A/div),.tempo (10s/div). ..... 172

Fig. 5.34 Formas de onda no enrolamento T1 na frequncia de comutao: 1. Tenso

(100V/div), 2. Corrente (10A/div), tempo (10s/div). (a) modo de no-sobreposio; (b)

modo de sobreposio .................................................................................................... 172

Fig. 5.35 Formas de onda sobre S1 na frequncia da rede: 1. Tenso (200V/div); 2. Corrente

(20A/div); Tempo (5ms/div). ......................................................................................... 173

Fig. 5.36 Formas de onda no interruptor S1 na frequncia de comutao: (a) modo de no-

sobreposio - 1. Tenso (100V/div), 2. Corrente (20A/div), tempo (10s/div); (b) modo

de sobreposio 1. Tenso (100V/div), 2. Corrente (10A/div),.tempo (10s/div). ..... 173

Fig. 5.37 Detalhe da comutao (a) no acionamento do interruptor (50V/div, 5A/div); (b) no

bloqueio do interruptor (50V/div, 10A/div). Tempo (200ns/div). ................................. 173

Fig. 5.38 Formas de onda sobre D1 na frequncia da rede: 1. Tenso (200V/div); 2.

Corrente (20A/div); Tempo (5ms/div) ........................................................................... 174

Fig. 5.39 Formas de onda no diodo D1 na frequncia de comutao: (a) modo de no-

sobreposio - 1. Tenso (100V/div), 2. Corrente (10A/div), tempo (10s/div); (b) modo

de sobreposio 1. Tenso (100V/div), 2. Corrente (20A/div),.tempo (10s/div)...... 174

Fig. 5.40 Detalhe da comutao (a) no acionamento do diodo (50V/div, 20A/div); (b) no

bloqueio do interruptor (50V/div, 10A/div). Tempo (200ns/div). ................................. 175

xxi

Fig. 5.41 Formas de onda das tenses de sada em cada capacitor, no barramento total e

corrente de carga para um degrau de carga de 50% para carga nominal (50V/div,

50V/div, 100V/div, 5A/div, 100ms/div)......................................................................... 175

Fig. 5.42 Formas de onda dos principais sinais de controle do conversor: v

m

, v

isample

e v

c

. 176

Fig. 5.43 Curva de rendimento do conversor de cinco nveis. ............................................ 176

Fig. 6.1 Topologias dos conversores: (a) trs nveis convencional; (b) cinco nveis

intercalado; (c) cinco nveis tipo T. ................................................................................ 179

Fig. 6.2 Prottipos dos conversores: (a) trs nveis convencional; (b) cinco nveis

intercalado; (c) cinco nveis tipo T. ................................................................................ 180

Fig. 6.3 Curvas de rendimento dos trs conversores estudados. ......................................... 182

Fig. 6.4 Comparao das perdas nos trs conversores estudados........................................ 183

Fig. 6.5 Comparao do volume total nos elementos magnticos e peso nos trs conversores.

........................................................................................................................................ 184

Fig. 6.6 Degrau de carga de 50% para 100% da carga nominal: (a) conversor de trs nveis

convencional (10A/div, 100V/div, 100V/div, 100V/div, 200ms/div); (b) conversor de

cinco nveis intercalado (50V/div, 50V/div, 100V/div, 5A/div, 200ms/div); (c) conversor

de cinco nveis tipo T (50V/div, 50V/div, 100V/div, 5A/div, 100ms/div)..................... 185

Fig. B.1 - Esquemtico da placa de potncia dos conversores................................................203

Fig. B.2 - Esquemtico da placa de controle dos conversores................................................204

Fig. B.3 - Esquemtico da placa da fonte auxiliar..................................................................205

xxii

LISTA DE TABELAS

Tabela 2.1 Resumo das caractersticas da placa Cyclone II Starter Kit da Altera.................29

Tabela 3.1 Especificaes do projeto. ................................................................................... 72

Tabela 3.2 Parmetros adotados do projeto........................................................................... 72

Tabela 3.3 Resumo do projeto do indutor L

b

. ....................................................................... 73

Tabela 3.4 Parmetros necessrios para o clculo das perdas do indutor. ............................ 80

Tabela 3.5 Especificao do IGBT IRGP35B60PD. ............................................................. 81

Tabela 3.6 Especificao dos diodos. .................................................................................... 84

Tabela 4.1 Especificaes do projeto. ................................................................................. 116

Tabela 4.2 Parmetros adotados do projeto......................................................................... 116

Tabela 4.3 Resumo do projeto do indutor L

b

. ..................................................................... 117

Tabela 4.4 Parmetros necessrios para o clculo das perdas do indutor. .......................... 120

Tabela 5.1 Especificaes do projeto. ................................................................................. 155

Tabela 5.2 Parmetros adotados do projeto......................................................................... 155

Tabela 5.3 Resumo do projeto do indutor L

b

. ..................................................................... 156

Tabela 5.4 Resumo do projeto do autotransformador. ........................................................ 157

Tabela 5.5 Parmetros necessrios para o clculo das perdas do indutor. .......................... 160

Tabela 5.6 Parmetros necessrios para clculo das perdas do autotransformador. ........... 160

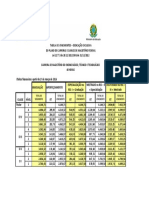

Tabela 6.1 Parmetros de projeto. ...................................................................................... 178

Tabela 6.2 Comparativa entre os resultados tericos, de simulao e experimentais obtidos

entre todos os conversores. ............................................................................................. 180

Tabela 6.3 Desempenho dos conversores............................................................................ 181

Tabela 6.4 Comparativa entre os pesos e volumes dos elementos magnticos dos

conversores. .................................................................................................................... 183

xxiii

SIMBOLOGIA

Smbolos utilizados no trabalho:

Smbolo Significado Unidade

Relao entre a tenso de sada e a tenso de pico da entrada -

Efeito pelicular dos condutores cm

Variao de fluxo Wb

B Variao da densidade do fluxo magntico T

in

I

Variao da corrente de entrada Ampre

1 C

I

Variao da corrente no capacitor C1 Ampre

L

I

Ondulao da corrente do indutor L Ampre

Q

Variao de carga no capacitor Coulomb

1 L

T

Elevao de temperatura no indutor L1 C

1 T

T

Elevao de temperatura no enrolamento T1 C

V Variao de tenso sobre o capacitor Volts

Vo Variao da tenso de sada Volt

Rendimento do conversor -

1 ngulo de transio entre os modos de operao do conversor rad

o

Permeabilidade do vcuo / H m

Resistividade do cobre cm

p

Frequncia do plo rad / s

z

Frequncia do zero rad / s

e

A

rea da janela da seo de um ncleo magntico

2

cm

e w

A A

Produto das reas de um ncleo magntico

4

cm

w

A

rea da janela de um ncleo magntico

2

cm

B Densidade de fluxo magntico T

C(s) Funo de transferncia do compensador

D

Razo cclica -

fio

d

Dimetro do fio cm

c

di

dt

Derivada da corrente de recuperao reversa do diodo intrseco do

IGBT

A

s

c

f

Freqncia de cruzamento Hertz

b

L

f

Freqncia de operao do indutor Hertz

r

f

Freqncia da rede de alimentao Hertz

xxiv

Smbolo Significado Unidade

s

f

Freqncia de comutao dos interruptores Hertz

1 T

f

Freqncia de operao dos transformadores Hertz

zi

f

Freqncia do zero do compensador de corrente Hertz

zv

f

Freqncia do zero do compensador de tenso Hertz

in

fp

Fator de potncia da entrada -

( ) FTLA s

Funo de transferncia de lao aberto do controle -

( ) FTMA s

Funo de transferncia de malha aberta do controle -

( ) G s

Funo de transferncia da planta -

est

G

Ganho esttico do conversor -

i

G

Ganho da malha de corrente -

( )

pv

G s

Funo de transferncia da malha de tenso -

( )

v

G s

Funo de transferncia do compensador de tenso -

1

( ) H s

Ganho do sensor de tenso de sada -

H

2

(s) Funo de transferncia do modulador MOCC

I

in

Corrente de entrada Ampre

1 1

( )

efC

i

Corrente eficaz instantnea no capacitor C1 para razo cclica

menor que 0,5

Ampre

2 1

( )

efC

i

Corrente eficaz instantnea no capacitor C1 para razo cclica maior

que 0,5

Ampre

C

I

Corrente de coletor do IGBT

Ampre

1

( )

C

i t

Corrente instantnea no capacitor C1 Ampre

2

( )

C

i t

Corrente instantnea no capacitor C2 Ampre

1

( )

D

i t

Corrente instantnea no diodo D1 Ampre

2

( )

D

i t

Corrente instantnea no diodo D2 Ampre

3

( )

D

i t

Corrente instantnea no diodo D3 Ampre

4

( )

D

i t

Corrente instantnea no diodo D4 Ampre

1 efC

I

Corrente eficaz no capacitor C1 Ampre

I

efD1

Corrente eficaz no diodo D1 Ampre

efin

I

Corrente eficaz de entrada Ampre

b

efL

I

Corrente eficaz no indutor Ampre

efS

I

Corrente eficaz atravs do interruptor S

Ampre

1 efS

I

Corrente eficaz atravs do interruptor S1 Ampre

1

( )

efT

i t

Corrente eficaz instantnea no enrolamento T1 Ampre

1 efT

I

Corrente eficaz no enrolamento T1 do transformador Ampre

xxv

Smbolo Significado Unidade

F

I

Corrente de conduo direta dos diodos Ampre

L

I

Corrente no indutor L Ampre

I

m

Corrente mnima do indutor L Ampre

I

M

Corrente mxima do indutor L Ampre

1 mdD

I

Corrente mdia no diodo D1 Ampre

1 mdS

I

Corrente mdia atravs do interruptor S1 Ampre

Io Corrente de sada do conversor Ampre

p

I

Corrente de pico da entrada Ampre

1 pD

I

Corrente de pico no diodo D1 Ampre

b

pL

I

Corrente de pico sobre o indutor Ampre

pS

I

Corrente de pico no interruptor S

Ampre

1 pS

I

Corrente de pico no interruptor S1 Ampre

1 pT

I

Corrente de pico no enrolamento T1 do transformador Ampre

( )

r

i

Corrente instantnea de entrada Ampre

rr

I

Corrente de recuperao do diodo intrnseco do IGBT Ampre

ref

I

Corrente de referncia do controle Ampre

1

( )

S

i t

Corrente instantnea no interruptor S1 Ampre

2

( )

S

i t

Corrente instantnea no interruptor S2 Ampre

1 T

I

Corrente no enrolamento T1 do transformador Ampre

2 T

I

Corrente no enrolamento T2 do transformador Ampre

3 T

I

Corrente no enrolamento T3 do transformador Ampre

4 T

I

Corrente no enrolamento T4 do transformador Ampre

1

( )

T

i t

Corrente instantnea no enrolamento T1 do transformador Ampre

J Densidade de corrente

2

/ A cm

K

E

Coeficiente de perdas por correntes parasitas -

K

H

Coeficiente de perdas por histerese -

K

o

Ganho do sensor de tenso -

k

p

Fator de utilizao do primrio -

k

t

Fator de topologia -

u

k

Fator de utilizao de um ncleo magntico -

K

vi

Ganho do compensador de tenso dB

w

k

Fator de utilizao da janela de um ncleo magntico -

xxvi

Smbolo Significado Unidade

g

l

Entreferro de um ncleo magntico cm

MLT Comprimento mdio de uma espira cm

fios

N

Nmero de fios em paralelo -

b

L

N

Nmero de espiras do indutor L

b

-

1 T

N

Nmero de espiras do enrolamento T1 -

in

P

Potncia mdia de entrada Watt

1 condD

P

Perda por conduo do diodo D1 Watt

1 condS

P

Perda por conduo do interruptor S1 Watt

b

cuL

P

Perdas no cobre do indutor Watt

1 cuT

P

Perdas no cobre do transformador Watt

lim

P

Potncia limite para o conversor Watt

b

magL

P

Perdas magnticas no ncleo de ferrite do indutor Watt

1 magT

P

Perdas magnticas no ncleo de ferrite do transformador Watt

Po Potncia mdia de sada Watt

1 offS

P

Perda por bloqueio do interruptor S1 Watt

1 onS

P

Perda por entrada em conduo do interruptor S1 Watt

t

P

Perdas totais nos semicondutores Watt

total

P

Perdas totais do conversor Watt

1 totalS

P

Perdas totais do interruptor S1 Watt

thcs

R

Resistncia trmica cpsula-dissipador / C W

thda

R

Resistncia trmica entre o dissipador e o ambiente / C W

thjc

R

Resistncia trmica juno-cpsula / C W

1 thL

R

Resistncia trmica do ncleo do indutor L1 / C W

1 thT

R

Resistncia trmica do ncleo do transformador / C W

T

Perodo de comutao dos interruptores s

T

a

Temperatura ambiente C

T

j

Temperatura da juno C

on

T

Perodo de conduo dos interruptores s

V

c

Tenso de controle Volt

1 C

V

Tenso sobre o capacitor C1 Volt

2 C

V

Tenso sobre o capacitor C2 Volt

V

CE

Tenso coletor-emissor IGBT Volt

xxvii

Smbolo Significado Unidade

V

CEO

Tenso de limiar do IGBT Volt

V

CEN

Tenso de saturao do IGBT Volt

1 D

V

Tenso sobre o diodo D1 Volt

e

V

Volume do ncleo de ferrite

3

cm

V

F

Queda de tenso direta Volt

V

GS

Tenso gate-source Volt

V

in

Tenso de entrada Volt

L

V

Tenso no indutor L Volt

Vo Tenso de sada Volt

V

o1

Tenso de sada 1 Volt

p

V

Tenso de pico de entrada Volt

pk

V

Amplitude da onda dente de serra Volt

1 S

V

Tenso sobre o interruptor S1 Volt

1 T

V

Tenso sobre o enrolamento T1 Volt

Acrnimos e Abreviaturas:

Smbolo Significado

CC Corrente Contnua

CA Corrente Alternada

IGBT Insulated Gate Bipolar Transsistor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

PFC Power Factor correction

PWM Pulse Width Modulation

THD Total Harmonic Distortion

UFC Universidade Federal do Cear

UPS Uninterruptible Power System

Raphael Amaral da Cmara Tese de Doutorado Introduo Geral

1

INTRODUO GERAL

A atual sociedade de consumo, aliada ao crescimento global econmico, social e de

avanos tecnolgicos e cientficos, apresenta uma grande e crescente demanda por

equipamentos que processam eletronicamente a energia eltrica. Dessa forma, esses

equipamentos processadores de energia eltrica podem ser aplicados, dentre outros lugares,

em: plantas industriais; sistemas de transporte de massa; no uso domstico, comercial e

hospitalar; em sistemas de informao e telecomunicaes.

na utilizao desses equipamentos que a Eletrnica de Potncia vem se destacando

com um importante lugar no desenvolvimento de novas tecnologias, onde as pesquisas

buscam a concepo de novas topologias de conversores estticos, tcnicas de controle e/ou

tcnicas de comutao que apresentem cada vez mais vantagens de ordem prtica, baixo peso,

baixo custo, pequeno volume e elevada eficincia associada com elevada robustez e

confiabilidade e, que interfiram de forma mnima nas fontes de energia e demais

equipamentos.

Um equipamento que se destaca dentro da eletrnica de potncia por sua capacidade de

fornecer energia eltrica de forma adequada e com qualidade para cargas crticas, mesmo com

os distrbios e interrupes da tenso de fornecimento da concessionria de energia eltrica,

o Sistema de Alimentao de Potncia Ininterrupta, traduo do nome em ingls

Uninterruptible Power System (UPS), definida por [1] e conhecida popularmente no Brasil

como No-break, mesmo nome adotado pela norma brasileira [2]. Esses equipamentos podem

ser compostos por unidades monofsicas ou trifsicas. Por serem ideais para estes tipos de

cargas, a demanda por sistemas no-break tanto no Brasil como no mundo grande. Com essa

demanda se desenvolveu uma forte e grande indstria para esse tipo de equipamento.

Os no-breaks, segundo [2, 3], podem ser classificados em trs tipos: On-line, Interativo

e Off-line. O no-break do tipo on-line amplamente reconhecido como uma topologia

superior em desempenho, condicionamento de energia e proteo carga, sendo o mais

indicado para cargas crticas por processar energia com qualidade durante todo seu

funcionamento [4]. Basicamente, um no-break on-line com correo de fator de potncia,

apresenta um estgio retificador de entrada (converso CA-CC), estgio pr-regulador, banco

de baterias, um estgio de sada composto por um inversor (converso CC-CA) e by-pass.

Raphael Amaral da Cmara Tese de Doutorado Introduo Geral

2

Diversas topologias de conversores estticos j foram estudadas e tm sido empregadas

como estgios retificadores e pr-reguladores com elevado fator de potncia em no-breaks.

Paralelo a isso, diferentes tcnicas de controle e/ou comutao tm sido utilizadas.

Outro fato que merece destaque so as mudanas e evolues crescentes em outras reas

da engenharia, especialmente na eletrnica digital. Esta vem disponibilizando ferramentas e

componentes que tm colaborado no controle de conversores estticos. O uso do controle

digital em microcontroladores como o PIC, dsPIC, DSP e FPGA, dentre outros, vm

assumindo um importante papel nas aplicaes que envolvem o processamento eletrnico de

energia, incluindo os no-breaks.

Dessa forma, a presente tese tem por objetivo apresentar duas novas topologias de

conversores CA-CC monofsicos com aplicao voltada ao estgio de entrada de um no-

break, onde uma topologia dita clssica ainda adicionada as outras duas para realizar uma

anlise comparativa entre esses trs tipos de topologias, capazes de operar com elevado fator

de potncia e baixa distoro harmnica da corrente de entrada. O controle utilizado ser

baseado em tcnicas digitais e implementado com o uso de um FPGA.

So estudados os conversores monofsicos CA-CC de trs nveis convencional, de cinco

nveis tipo T e de cinco nveis intercalados, cujas exigncias so:

Fluxo de potncia unidirecional;

Tenso de sada regulada;

Filtro de sada capacitivo;

Ausncia de indutores de baixa frequncia;

Sem isolamento.

Alm disso, a presente tese tem como objetivo o estudo e implementao, por meio de

tcnica de controle digital via FPGA, do controle dos conversores CA-CC monofsicos,

visando os seguintes aspectos:

Regulao da tenso total de sada;

Equilbrio das tenses de sada;

Alto fator de potncia.

Esse trabalho segue a seguinte estrutura:

Raphael Amaral da Cmara Tese de Doutorado Introduo Geral

3

No Captulo 1, apresentam-se as principais topologias e tcnicas de controle utilizadas

para correo do fator de potncia. apresentada a motivao do trabalho junto com as

topologias de conversores CA-CC a serem analisadas.

No Captulo 2, apresentam-se noes bsicas de conceitos a respeito do controlador

FPGA utilizado, circuitos de interface do controle com a potncia, a tcnica de controle

adotada com noes bsicas, mtodos convencionais para projetos em sistemas de controle

digital e programao do controle adotado no FPGA utilizado.

Nos Captulos 3, 4 e 5 so realizados os estudos tericos dos conversores CA-CC

monofsico de trs nveis convencional (Captulo 3), de cinco nveis intercalado (Captulo 4)

e o de cinco nveis tipo T (Captulo 5) apresentando o princpio de funcionamento, as

equaes que descrevem os esforos de tenso e corrente nos componentes de cada topologia,

a modelagem dinmica dos conversores, a modelagem de perdas e rendimento terico,

exemplos de projetos e resultados de simulao e experimental.

No Captulo 6, realizada uma anlise comparativa entre os trs conversores

monofsicos estudados anteriormente, apresentando uma anlise do rendimento, peso e

volume e desempenho dinmico.

Por fim, so apresentadas as principais concluses do presente trabalho e as referncias

bibliogrficas utilizadas.

Raphael Amaral da Cmara Tese de Doutorado Cap. 1

4

CAPTULO 1

CONVERSORES MONOFSICOS CA-CC COM CORREO DO

FATOR DE POTNCIA: TOPOLOGIAS E TCNICAS DE CONTROLE

1.1 Introduo

Um baixo fator de potncia na entrada de uma fonte de alimentao devido a alta

distoro harmnica na corrente de entrada pode causar uma srie de desvantagens como [5]:

A mxima potncia ativa absorvvel da rede fortemente limitada pelo fator de

potncia;

As harmnicas de corrente exigem um sobredimensionamento da instalao eltrica e

dos transformadores de distribuio, alm de aumentar as perdas;

A componente de 3 harmnica da corrente, em sistema trifsico com neutro, pode ser

muito maior do que o valor nominal;

O achatamento da onda de tenso, devido ao pico da corrente e da 5 harmnica, alm

da distoro da forma de onda, pode causar mal funcionamento de outros

equipamentos conectados rede;

As componentes harmnicas podem provocar ressonncias no sistema de potncia,

levando a picos de tenso e corrente, podendo danificar equipamentos conectados

rede.

Para resolver os problemas que um baixo fator de potncia pode causar, existem dois tipos

de solues para a correo do fator de potncia (CFP): solues passivas e ativas. Solues

passivas monofsicas para CFP, como as encontradas em [6-8], consistem na utilizao

apenas de elementos passivos, a base de indutores e capacitores (filtros L, LC ou LCD), entre

a fonte de entrada e o retificador. Essas estruturas oferecem caractersticas como robustez,

confiabilidade, insensibilidade a surtos e operao silenciosa e, sua principal vantagem a

ausncia de interruptores controlados. No entanto, vale destacar, as desvantagens da aplicao

dessas solues, tais como [9]:

Se comparados s solues ativas, so pesados e volumosos;

Afetam as formas de onda na frequncia fundamental;

No funcionalidade numa larga faixa de tenso de entrada;

Impossibilidade de regulao de tenso;

Resposta dinmica pobre;

Raphael Amaral da Cmara Tese de Doutorado Cap. 1

5

Complexidade no correto dimensionamento.

J as solues ativas, alm de empregarem elementos passivos menores, se utilizam de

conversores estticos com interruptores semicondutores controlados que impem corrente

de entrada drenada, atravs de tcnicas de controle adequadas, forma senoidal e em fase com

a tenso de alimentao. As tcnicas de correo ativa apresentam melhor qualidade na forma

de onda da corrente, melhor resposta dinmica com regulao da tenso de sada,

apresentando, no entanto, maior ndice de interferncia eletromagntica e complexidade de

circuito.

Dessa forma, neste captulo so apresentadas as principais topologias de conversores CA-

CC monofsicos com CFP que podem ser utilizados como estgio de entrada em no-breaks e

as principais tcnicas de controle que permitem a obteno de correntes de entrada

praticamente senoidais e em fase com a tenso de entrada com reduzidas taxas de distoro

harmnica.

Tambm so apresentados: o objetivo central, a motivao, as contribuies pretendidas

com esta tese de doutorado e uma breve abordagem sobre os conversores CA-CC

desenvolvidos ao longo deste trabalho.

1.2 Topologias de Conversores Monofsicos CA-CC

Em aplicaes como no-breaks ou fontes de alimentao para telecomunicaes, os

conversores CA-CC utilizados podem ser classificados pelas principais caractersticas de

estrutura que os identificam, como:

Modo de conduo contnua ou descontnua;

Topologias de dois ou trs nveis;

Topologias derivadas dos conversores clssicos boost, buck, buck-boost, etc.;

Topologias com ou sem isolao;

Nmero de interruptores controlados ativos;

Acesso ao neutro.

O retificador monofsico a diodos de ponte completa associado ao conversor boost

clssico [10] uma topologia amplamente utilizada para aplicaes com CFP por possuir

como principal vantagem a simplicidade no princpio de funcionamento e o pequeno nmero

de semicondutores necessrios. Esse conversor CA-CC apresentado na Fig. 1.1.

Raphael Amaral da Cmara Tese de Doutorado Cap. 1

6

Fig. 1.1 Topologia do conversor boost clssico com CFP.

As principais desvantagens da aplicao do conversor boost clssico so:

Circulao simultnea da corrente de entrada atravs de trs semicondutores de

potncia, causando excessivas perdas de conduo, reduzindo o rendimento do

conversor e exigindo semicondutores com maiores esforos de corrente e tenso;

Impossibilidade de uso do neutro comum entre a entrada da rede e a sada do

conversor boost para possibilitar a conexo de um inversor com neutro comum e do

by-pass do no-break.

Com o objetivo de se processar maiores potncias, o conversor boost apresentado no

seria indicado. Dessa forma, novas configuraes topolgicas com maior capacidade de

processamento de energia com reduzidas perdas por conduo podem ser geradas atravs de

vrias tcnicas de gerao de conversores, como: paralelismo de conversores e aplicao de

clulas de comutao PWM, entre outras [11-16].

Aplicando o paralelismo de conversores, na Fig. 1.2(a) tem-se o conversor boost em

paralelo com CFP [11] e na Fig. 1.2(b) tem-se o conversor boost intercalado [12-14].

(a) (b)

Fig. 1.2 Topologias de conversores usando a tcnica de paralelismo de conversores: (a) boost em paralelo [11];

(b) boost intercalado [12-14].

Raphael Amaral da Cmara Tese de Doutorado Cap. 1

7

Para o conversor boost em paralelo tem-se um indutor principal de armazenamento L

b1

e

um indutor de comutao L

b2

que bem menor que L

b1

. Como vantagens, essa topologia

apresenta um mesmo sinal de comando dos interruptores e um balanceamento esttico e

dinmico natural de corrente entre os componentes exigindo um layout de placa impressa

mais simplificado. Como desvantagens, tm-se um maior nmero de componentes utilizados

e a impossibilidade de uso do neutro comum.

Para o conversor boost intercalado, tem-se como vantagem as reduzidas perdas por

conduo e como desvantagens, uma maior complexidade no circuito de controle, a

possibilidade de desbalanceamento das correntes dos indutores e a impossibilidade de uso do

neutro comum.

Utilizando-se da aplicao de clulas de comutao PWM tem-se na Fig. 1.3(a) um

conversor boost aplicando a clula C de dois estados [15] e na Fig. 1.3(b) a aplicao da

clula de comutao de trs estados em um conversor boost com CFP [16].

(a) (b)

Fig.1.3 Aplicao de clulas de comutao PWM: (a) dois estados; (b) trs estados [16].

Na aplicao de clulas de comutao PWM nos conversores tem-se como principal

vantagem as reduzidas perdas por conduo e como desvantagens um aumento no nmero de

componentes e na complexidade dos circuitos de controle.

Analisando estas topologias apresentadas nas Figs. 1.2 e 1.3 observa-se que, mesmo

processando maiores potncias, todas essas topologias apresentadas possuem uma

desvantagem comum ao conversor boost clssico apresentado na Fig. 1.1: a impossibilidade

de uso do neutro comum entre a entrada da fonte de alimentao e a sada do conversor, o que

inviabilizaria a aplicao dessas topologias para sistemas no-breaks.

Ainda se utilizando dessas tcnicas para gerao de conversores com maior capacidade de

processamento de energia e com a caracterstica de possibilidade de uso do neutro comum

Raphael Amaral da Cmara Tese de Doutorado Cap. 1

8

facilitando o by-pass, podem ser encontradas na literatura, vrias topologias de conversores

monofsicos com CFP como em [17-20].

Atravs do paralelismo de conversores, na Fig. 1.4(a) tem-se o conversor duplo boost com

o indutor no lado CA [17] e na Fig. 1.4(b) com o indutor no lado CC [18]. Ambas as

topologias operam com a possibilidade de seleo de duas tenses de entrada. A diferena

que no conversor com o indutor no lado CA tem-se a necessidade de dois interruptores para a

seleo da tenso de entrada onde existe uma associao de indutores. Assim, dependendo da

tenso de entrada escolhida, os indutores estaro conectados em srie ou em paralelo. J para

o conversor com o indutor no lado CC, existe apenas um interruptor seletor de tenso de

entrada e no h a associao de indutores.

(a) (b)

Fig. 1.4 Topologia do conversor duplo boost com CFP: (a) indutor no lado CA [17];

(b) indutor no lado CC [18].

Na Fig. 1.5(a) tem-se o conversor duplo boost com apenas um interruptor [19] e na Fig.

1.5(b) esta mesma topologia de conversor com a aplicao da clula de comutao de trs

estados [20].

Carga

V

in

C

1

S1

D

b1

L