Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

EMC Design Guidelines

Caricato da

senkum812002Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

EMC Design Guidelines

Caricato da

senkum812002Copyright:

Formati disponibili

EMC DESIGN GUIDELINES

www.dc-dc.com

CONTENTS

1. Power supply considerations

2. Signal line considerations

3. PCB considerations

4. Component considerations

5. EMC specific components

6. Inductors

7. Common mode chokes

8. Transformers

9. Isolated DC-DC converters

10. Conclusion

11. Pre-compliance testing conducted

line emissions of DC supplied

circuits

12. Pre-compliance

13. Standard test method

14. Shielding

15. DC target circuit under test

16. Circuit conditions

17. Resolution bandwidth and spectra

obtained

18. Spectra detection method

19. Using the emissions spectra

information

20. Relevant standards

21. Abbreviations

The EC (European Community) re g u l a t i o n s

re g a rding electromagnetic compatibility (EMC)

a ffect many aspects of circuit and system

design. However, there are many

considerations that can be applied generally to

reduce both the emissions from and

susceptibility to, electromagnetic interf e re n c e

( E M I ) .

As a manufacturer of electronic components,

C&D Technologies is committed to minimising

emissions from its own components and to

helping its customers achieve EMC compliance

by correct component choice and design. To

this end C&D Technologies have compiled the

following list of general design considerations.

1 . POWER SUPPLY

C O N S I D E R AT I O N S

IEliminate loops in supply lines

(see figure 1).

IDecouple supply lines at local boundaries

(use RCL filters with low Q, see figure 2).

IPlace high speed sections close to the

power line input, slowest section furt h e s t

away (reduces power plane transients, see

f i g u re 3).

IIsolate individual systems where possible

(especially analogue and digital systems)

on both power supply and signal lines (see

f i g u re 4).

2 . SIGNAL LINE

C O N S I D E R AT I O N S

IUse low pass filters on signal lines to

reduce bandwidth to signal minimum.

IKeep feed and re t u rn loops close on wide

bandwidth signal lines.

ITe rminate lines carrying HF or RF signals

c o rrectly (this minimises reflection, ringing

and overshoot, see figure 5).

ITe rminate lines carrying signals external to

a board at the board edge, avoid lead ter-

minations within the board and loose leads

c rossing the board .

IAvoid cabling or tracking which is close to

the quarter wavelength of the signal

f re q u e n c y, this can produce re s o n a n c e

within the signal conductor.

ITrack all signals on the board, avoid flying

leads across the board .

IMinimise rise and fall times on signal and

clock edges (sharp edges produce wide hf

spectra), slew rate limiting also re d u c e s

c rosstalk (see figure 6).

3 . PCB CONSIDERAT I O N S

IAvoid slit apert u res in PCB layout, part i c u-

larly in ground planes or near curre n t

p a t h s .

IA reas of high impedance give rise to high

EMI, use wide tracks for power lines on the

trace side.

IMake signal tracks stripline and include a

Figure 1: Eliminate Loops in Supply Lines

Figure 4: Isolate Individual Systems

Figure 2: Decouple Supply Lines

at Local Boundaries

Figure 3: Place High Speed Circuits

Close to PSU

EMC DESIGN GUIDELINES

g round plane and power plane whenever

p o s s i b l e .

IKeep HF and RF tracks as short as

possible, lay out the HF tracks first (see

f i g u re 7).

IAvoid track stubs, these cause re f l e c t i o n

and harmonics (see figure 8).

IOn sensitive components and term i n a t i o n s

use surrounding guard ring and ground fill

w h e re possible (see figure 9).

IDo not leave any floating conductor are a s ,

these act as EMI radiators, if possible

connect to ground plane (often these

sections are placed for thermal dissipation,

hence polarity should be unimportant but

check component data sheet, see figure

1 3 ) .

4 . COMPONENT

C O N S I D E R AT I O N S

I

Locate biasing and pull up/down

components close to driver/bias points.

I

Minimise output drive from clock circ u i t s .

I

Use common mode chokes between curre n t

c a rrying and signal lines to incre a s e

coupling and cancel stray fields (see figure

1 4 ) .

I

Decouple close to chip supply lines,

reduces component noise and power line

transients (see figure 15).

IUse low impedance capacitors for

decoupling and bypassing (ceramic

multilayer types are pre f e rred due to high

resonant frequency and stability).

IUse discrete components for filters w h e re

possible (surface mount is preferable due to

lower parasitics and aerial effects of

t e rminations on through hole part s ) .

I

E n s u re filtering of cables and over voltage

p rotection at the terminations (this is

especially true of cabling that is external to

IA guard ring around trace layers re d u c e s

emission out of the board, only connect to

g round at single point and make no other

use of the guard ring (i.e. do not use to

c a rry ground re t u rn from a circ u i t ) .

IAvoid overlapping power planes, keep

separate over common ground (re d u c e s

system noise and power coupling, see

f i g u re 10).

IPower plane conductivity should be high,

t h e re f o re avoid localised concentrations of

via and through hole pads (surface mount

is the pre f e rred assembly technology)

ITrack mitring (bevelling the edges at

c o rners) reduces field concentration (see

f i g u re 11).

IIf possible make tracking run ort h o g o n a l l y

between adjacent layers (see figure 12).

IDo not loop tracks, even between layers,

this forms a receiving or radiating

a n t e n n a e .

Figure 5: Terminate Signal lines Correctly

Figure 10: Avoid Overlapping Power Planes

Figure 11: Mitre Track Corners

Figure 12: Orthogonal Tracking

on Seperate Layers

Figure 7: Keep HF Tracks Short

Figure 9: Use Guard Ring & Ground Fill

Figure 8: Avoid Track Stubs

Figure 6: Use Slow Rise & Fall Times

Reflection Coefficient =

Z

=

l Z

O

- Z

T

l

Z l Z

O

+ Z

T

l

EMC DESIGN GUIDELINES

within an existing circuit. The range of

components C&D Technologies produce which

can be used for specific EMC pro b l e m s

include transformer isolators, standard

inductors and common mode chokes.

6 . I N D U C T O R S

The range of inductors available from C&D

Technologies are targeted mainly at the power

market, and are useful for reducing EMI on

power lines and for filtering high curre n t

s i g n a l s .

In switched mode power supply (SMPS) circ u i t s

inductors for both the energy storage and line

filtering are available (see figure 16). It is

recommended that a toroidal or sheilded

inductor be used if EMC problems are

suspected of being emitted from this circ u i t

function. To roidal inductors maintain the

magnetic field within the core shape and

hence have virtually zero radiated field. The

susceptibility of a toroid is also negligible due

to the shape, since an applied magnetic field

would generate an equal and opposite curre n t

component in the wire (self cancelling).

At power sections of various circuit functions,

an inductor between the local supply and the

main feed provides good filtering of the supply

and reduces noise from localised circuits in the

system polluting the main power line (see

f i g u re 2). Since the inductor here re q u i res a

relatively high DC current during its usual

operation, axial inductors which have very a

high saturation current are re c o m m e n d e d .

Selection should be made on the curre n t

handling and relative switching speed of the

c i rcuit section. Generally low values of

inductance are pre f e rred due to the associated

low DC re s i s t a n c e .

In systems with a reactive load or driver a

matched termination may be re q u i red using a

passive reactive circuit. The fre q u e n c y

response of the load/driver needs to be

known, but can be matched by a re l a t i v e l y

simple and easily characterised RCL network

Another area where inductors can be used

with great benefit to the EMI of a circuit is in

an amplifier bias network (see figure 17). By

using an inductive element in the bias or

compensation arms, a filter can be added to

the circuit without loading the signal with

additional inductance. Careful choice of

inductance value is re q u i red and placement

close to the amplifier is essential. This method

is suitable for filtering HF noise, particularly on

video and VHF/UHF TV type signals.

7 . COMMON MODE CHOKES

Common mode chokes are best employed in

signal lines to eliminate common mode noise

or EMI on cables or induced in the signal

tracks (see figure 14). The choke should be

located as near to the driver/receiver circuit as

possible, or at the entry point of a signal to a

b o a rd. The choke works by cancelling

i n t e rf e rence appearing on both signal and

the system, if possible all external cabling

should be isolated at the equipment

b o u n d a ry ) .

I

Minimise capacitive loading on digital

output by minimising fan-out, especially on

CMOS ICs (this reduces current loading

and surge per IC).

IIf available, use shielding on fast switching

c i rcuits, mains power supply components

and low power circ u i t ry (shielding is

expensive and should be a last re s o rt

o p t i o n ) .

In general, keeping the bandwidth of all part s

of the system to a minimum and isolating

c i rcuits where possible reduces susceptibility

and emissions. Considerations which are

applicable to reducing noise levels are equally

applicable to EMC compliance, EMC

compliant circuits should obviously exhibit low

noise levels.

5 . EMC SPECIFIC COMPONENTS

As a supplier of isolator components, C&D

Technologies provide a range of parts which

can offer simple solutions to EMC pro b l e m s

re t u rn lines (i.e. induced EMI) while allowing

d i ff e rential mode signals and DC to pass.

Suitable choice of inductance will also help in

maintaining a match to the characteristic line

impedance and acts as a filter to bandwidth

limit the term i n a t i o n .

Any of C&D Technologies transformers with a

1:1 ratio can be employed as a common

mode signal choke. C&D Technologies also

have a portfolio of customer specific chokes

and can design a common mode choke for a

c u s t o m e r s circuit application.

8 . T R A N S F O R M E R S

The main EMC benefit of using a transform e r

is in providing an isolation barrier between a

signal line and the signal processing circ u i t

( p a rticularly where the signal line exits the

b o a rd or system). This is true of signals being

driven or received, since isolating the line

reduces common mode noise and eliminates

g round (or signal re t u rn) potential diff e re n c e s

between systems.

One particular area where high noise is

essential is in thyristor/triac driving circ u i t s ,

w h e re the transformer is providing an isolation

between a mains driven load and a logic

based controller (see figure 18). The isolating

pulse transformer provides much better noise

immunity than an insulated gate bipolar

transistor (IGBT) due to inherently lower

coupling capacitance (typically tens of pF for a

pulse transformer compared to nF for power

IGBT devices). The lower coupling capacitance

i m p roves the circuits immunity for noise on the

mains and from the power switching

d e v i c e .

T O R S DESIGN . 1 1 .

Figure 13: Do Not Leave Floating

Conductive Areas

Figure 16: Basic SMPS and Filter

Configuration

Figure 14: Use Common Mode Choke

Between Signal Lines

Figure 15: Decouple Close to IC Supply Lines

Figure 17: Amplifier Filtering with Inductors

9 . I S O L ATED DC-DC

C O N V E RT E R S

An isolated DC-DC converter can provide a

significant benefit to reducing susceptibility

and conducted emission due to isolating both

power rail and ground from the system supply

(see figure 4).

Isolated DC-DC converters are switching

devices and as such have a characteristic

switching frequency which may need some

additional filtering (see figure 21).

1 0 . C O N C L U S I O N

The above recommendations, if followed,

should allow completed systems to achieve CE

c e rtification first time. They should give a

designer more confidence in their circ u i t s

ability to meet the EC directive and offer good

advice for low noise circ u i t ry.

11 . PRE-COMPLIANCE TESTING

CONDUCTED LINE EMISSIONS

OF DC SUPPLIED CIRCUITS

Power supply (PSU) designers should be well

a w a re by now of the re q u i rement of their

power supply to provide clean DC voltage to

the target circuit and not to disturb the ac

mains voltage. However, often the PSU

designer may have no idea of the noise that

can potentially be introduced by the targ e t

c i rcuit, likewise the DC circuit designer (digital

or analogue) may not be aware of the

re q u i rements of the PSU as far as acceptable

noise levels are concern e d .

The aim of this section is to bridge this gap, to

p rovide a method for testing the DC circuit in

isolation from its final PSU and enable either

additional filtering to be specified, or PSU

immunity to conducted noise to be re q u e s t e d .

Either way it enables the two designers to

work towards a common goal; CE cert i f i c a t i o n

of the final pro d u c t .

12 . P R E - C O M P L I A N C E

T h e re are no specified EMC limit lines for DC

rails, hence there are no specified tests in the

EC or CENELEC regulations that can be

applied dire c t l y. Likewise the PSU and the DC

supplied circuit could only be considered as

sub-systems at best, possibly even components,

consequently on their own they are exempt

f rom the EC directive. The tests conducted can

1 4 . S H I E L D I N G

At all times the DC powered circuit under test

(CUT), LISN and all cables connecting any

m e a s u rement equipment, loads and supply

lines should be shielded. The shielding is to

p revent possible pick-up on cables and the

CUT from external EMC sources (e.g. other

equipment close by, radiated emissions fro m

the PSU etc). The shielding is again re f e re n c e d

to mains eart h .

When measuring small circuits or individual

components, the whole part can often be fitted

into a metal enclosure for testing. All power

and test entry points should be via shielded

connectors, preferably high frequency BNC

types. The LISN should be shielded and

e x t e rnal to the enclosure containing the test

c i rcuit (see figure 23).

1 5 . DC TARGET CIRCUIT

UNDER TEST

T h e re are innumerable circuit configurations

that could be used as a test circuit for an

example, however, it was decided instead to

use a board level DC-DC converter with a

resistive output load. Board level DC-DC

c o n v e rters are a common place item on many

PC boards, instrumentation and pro c e s s i n g

equipment. The advantage of using a DC-DC

c o n v e rter here is that it has a known

characteristic switching frequency (see figure

24), hence a stable well behaved noise

s p e c t rum can be obtained easily and the

vagaries of the actual circuit functionality can

be circ u m v e n t e d .

The DC-DC converter used was an NMS1212,

12V input, 12V dual output device delivering

a total 2W of power with a typical

characteristic switching frequency of 35kHz.

This device has a number of line spectra

below the EC EMC lower limit for conducted

emissions (150kHz), but no sub-harm o n i c s

below its fundamental switching fre q u e n c y.

1 6 . CIRCUIT CONDITIONS

To ensure that worst case conditions, as far as

EMC is concerned, are applied to the CUT it is

n e c e s s a ry to have some knowledge of the

c i rcuit operation, hence it is usually best

specified by the CUT designer.

In the case of the NMS DC-DC convert e r,

worst case is at full load (i.e. 2W output) with

maximum input voltage (see figure 25),

although the input voltage actually had a

minimal effect within its allowed tolerance.

Other worst case conditions may be difficult to

apply (e.g. high temperature, see figure 26)

due to the nature of the test enviro n m e n t ,

h o w e v e r, some gauge of how these may eff e c t

the EMC perf o rmance should be considere d .

W h e re circuit loading conditions and their

e ffect on EMC are not known, tests can be

done in-situ on the CUT prior to the

p recompliance test.

t h e re f o re only be considered as pre -

compliance tests, the end system would have

to be fully compliance tested for full CE

c e rtification. However, if the system is to be

c e rtified via the Technical Construction File

(TCF) route, the individual pre-compliance tests

may be used as part of the TCF.

1

1 3 . S TANDARD TEST METHOD

Having no EN standard relies on the user to

implement the closest equivalent test

s t a n d a rd to the existing EMC regulations for

mains borne emissions. One of the first

p roblems with a DC supply is removing the

test PSU noise from the target circuit noise

while perf o rming the test (assuming the test

PSU is not the same as the final system

P S U ) .

The removal of line noise is perf o rmed on

AC mains connected systems using a line

impedance stabilisation network (LISN) on

both live and neutral lines and re f e renced to

the mains earth as a ground plane. This has

been directly copied for the testing of DC

supplied circuits, using any DC PSU with an

e a rth terminal, both the positive and gro u n d

(or 0V) lines are filtered with a LISN

re f e renced to the mains earth terminal.

Each LISN is constructed in accordance with

CISPR 16 for 50/50H line impedance

(see figure 22).

T h e re are other reasons for using the mains

e a rth as a re f e rence than just the ability to

relate the test to the standard EN

specifications, in many systems the mains eart h

will in fact be the case ground plane.

If it is known that the 0V line is the gro u n d

plane re f e rence the earth re f e rence can be

connected to the 0V line at the supply, with

both LISNs still on the DC supply lines (the

LISN on the 0V line should still be connected

as this gives an indication of likely ground line

noise). Circuits supplied with multiple DC lines

will re q u i re a LISN on each power feed and

the noise measured on each of the power

l i n e s .

Figure 21: Filtering a DC-DC Converter

Figure 18: Triac/ Thyristor Firing Circuit

EMC DESIGN GUIDELINES

EMC DESIGN GUIDELINES

spectra (falling significantly at 5MHz, see

f i g u re 27). In the frequency range of intere s t

t h e re are there f o re 853 individual line spectra

if resolved at 9kHz RBW, variation in tolerance

of components, input voltage accuracy and

loading could change the operating fre q u e n c y

by as much as 20%, hence more than 200

additional lines could be added or subtracted

f rom the spectra. Overall the envelope tends to

remain fairly constant, hence simply widening

the RBW to 120kHz gives the envelope

function and not the individual line spectra

(see figure 28). The information is now easier

to use and understand and possible variations

should be encompassed by this envelope.

Widening the RBW should only be done in

situations where there is wideband noise or a

l a rge number of closely related individual

spectra. Most circuits will be able to use a

9kHz RBW. It should also be noted that when

using a spectrum analyzer the effective noise

floor is raised when the RBW is widened,

hence the lower level noise can be swamped

out by this effect. It is always worth trying the

n a rrowest RBW first then widening as and

when necessary.

1 8 . SPECTRA DETECTION METHOD

T h e re are essentially three methods of

measuring conducted line spectra; peak

detection, average detection and quasi-peak

detection. Peak detection is the instantaneous

m e a s u rement of the signal, this is essentially

best for continuous wave spectra and s n a p -

shots of the emissions. Average detection

m e a s u res the average over a time period, this

1 7 . RESOLUTION BANDWIDTH

AND SPECTRA OBTA I N E D

One of the first problems may be to decide on

the resolution re q u i red for the pre - c o m p l i a n c e

tests. To maintain compatibility with the EC

d i rective for mains emissions, a 9kHz

resolution bandwidth (RBW) should be used

for conducted line measurements. In circ u i t s

with only a few line emissions this may be

suitable, however, with analogue pro c e s s i n g

c i rcuits or asynchronous logic there are likely

to be some wideband spectra. It is also

possible that individual line spectra may

change with loading conditions but within a

p redefined envelope, hence widening the

RBW can encompass this envelope.

If we consider the NMS again, as a square

wave quasi-resonant converter there are two

main switching peaks, one at the re s o n a n t

f requency (35kHz) and another at twice the

resonant frequency (reflected full wave

rectification, see figure 24). There are also

h a rmonics of these across the whole emissions

can be achieved by reducing the video

bandwidth of the spectrum analyzer to less

than the RBW. Quasi-peak detection is

designed to simulate a subjective human type

response to a pulse type interf e rence. Quasi-

peak weights rise and fall times of the signal to

p roduce a given level.

A continuous wave signal would be identical

with all three detection methods, infre q u e n t

pulsed interf e rence would be higher via a

quasi-peak detection and lowest using peak

detection. It is up to the user to decide on the

most appropriate detection method for their

c i rcuit. If in doubt use the quasi-peak method.

H e re the spectra was produced by continuous

pulses from the DC-DC convert e r, peak

detection could have been used but average

detection was used as this gave a cleaner

envelope trace.

1 9 . USING THE EMISSIONS

SPECTRA INFORMAT I O N

T h e re are several uses for the spectra

obtained; the circuit could be redesigned or

the PCB layout changed to reduce the noise,

t h e re could be additional filtering added at the

PSU input to the DC circuit or the circuit could

p rove to have so little noise as to re q u i re no

c h a n g e s .

If considering redesign it is possible to

d e t e rmine which of multiple layouts are the

quietest or which components are quietest,

does filtering on the sensors or load points

Figure 22: CISPR16 LISN Circuit

Figure 23: Test Set-Up

Figure 24: Switching Spectra of NMS1212

Figure 26: Temperature Effect

on Switching Frequency

Figure 25: Input Voltage Effect

on Switching Frequency

C&D Technologies (NCL) Ltd

Tanners Drive, Blakelands North

Milton Keynes MK14 5BU, England

Tel: +44 (0)1908 615232

Fax:+44 (0)1908 617545

email: info@cdtechno-ncl.com

www: http://www.dc-dc.com

C&D Technologies (NCL), Inc.

5816 Creedmoor Road, Raleigh

NC 27612, USA

Tel: +1 (919) 571-9405

Fax: +1 (919) 571-9262

email: info@us.cdtechno-ncl.com

C&D Technologies (NCL) Limited reserve the right to alter or improve the

specification, internal design or manufacturing process at any time, without

notice. Please check with your supplier or visit our web site to ensure that

you have the current and complete specification for your product before use.

C&D Technologies (NCL) Limited 2001 AN010.1

No part of this publication may be copied, transmitted or stored in a

retrieval system or reproduced in any way including, but not limited to,

photography, photocopy, magnetic or other recording means, without prior

written permission from C&D Technologies (NCL) Limited.

Instructions for use are available from www.dc-dc.com

reduce noise? Does noise get to the PSU fro m

the logic, clock or interface circuits? All these

should be examinable on the circuit while still

in the pre - p roduction or design stages.

Filtering may be the lowest cost option of

getting the circuit through pre-compliance. If

redesign re p resents a major investment in time

and money, simply adding a capacitor and

inductor to the input line may only add

minimal cost and drop the noise by 20dB at

the problem fre q u e n c y. Alternatively you may

even have to specify to the PSU designer that

the PSU must give a specified noise re j e c t i o n ,

20dB to noise below 1MHz for example.

The standard EMC limit lines can be placed as

overlays on the noise emissions to determ i n e

what rejection the PSU re q u i res. Often this is

not quite as straight forw a rd as it sounds as

PSU output capacitors and CUT input

capacitors may result in a significantly higher

rejection than would be suggested by simply

using 50 noise sources (the PSU and CUT

a re unlikely to have 50 impedance, or even

matched impedances). As stated pre v i o u s l y,

C E N E L E C Comite European de

N o rmalisation Electro t e c h n i q u e

C I S P R Comite International Special des

P e rturbations Radioelectriques

C S A Canadian Standards Authority

D E M K O Dansk Standard (Denmark)

D I N Deutsches Institut fur Norm u n g

( G e rm a n y )

D T I D e p a rtment of Trade and Industry

( U K )

E C E u ropean Community

E I A E l e c t ronic Industries Association

E N E u ropean Standard (Norm e

E u ro p e a n )

E M C E l e c t roMagnetic Compatibility

E M I E l e c t roMagnetic Interf e re n c e

E T S I E u ropean Te l e c o m m u n i c a t i o n s

S t a n d a rds Institute

F C C Federal Communications

Commission (US)

H F High Fre q u e n c y

I E C I n t e rnational Electro t e c h n i c a l

C o m m i s i o n

I S O I n t e rnational Organisation for

S t a n d a rd i s a t i o n

I T U I n t e rnational Te l e c o m m u n i c a t i o n

U n i o n

J I S C Japanese Industrial Standard s

C o m m i t t e e

N S F N o rges Standard i s e r i n g s f o r b u n d

( N o rw a y )

R F Radio Fre q u e n c y

T C F Technical Construction File

S A A S t a n d a rds Australia

S C C S t a n d a rds Council of Canada

S FA Finnish Standards Association

S E M K O Svenska Elektviska Kommissionen

( S w e d e n )

U H F Ultra High Fre q u e n c y

U L U n d e rwriters Laboratory (USA)

U N I Ente azionale Italiano di

Unificazione (Italy)

V D E Verband Deutsche Electro t e c h n i k e r

( G e rm a n y )

V H F Ve ry High Fre q u e n c y

these tests are only precompliance and furt h e r

tests with the PSU and circuit in the targ e t

system will have to be conducted prior to

c e rtifying the completed pro d u c t .

2 0 . R E L E VANT STA N D A R D S

The following are some of the relevant EMC

s t a n d a rds applicable in various countries that

the above design notes are intended to

a d d re s s .

FCC 15J/SUB Part B

VDE 0871

CISPR 22

EN 60555-2/3

EC Directive 89/336/EEC

2 1 . A B B R E V I AT I O N S

A N S I American National Standard s

I n s t i t u t e

B S I British Standards Institute

C E C e rtificate of EMC Compliance

EMC DESIGN GUIDELINES

Figure 27: NMS1212 Spectra with 9kHz RBW

Figure 28: NMS1212 Spectra with 120kHz RBW

Potrebbero piacerti anche

- High Efficiency RF and Microwave Solid State Power AmplifiersDa EverandHigh Efficiency RF and Microwave Solid State Power AmplifiersValutazione: 1 su 5 stelle1/5 (1)

- Lord of The Board EMC How To Reduce RF EmissionsDocumento13 pagineLord of The Board EMC How To Reduce RF EmissionsLulu Sweet ThingNessuna valutazione finora

- EMC Design Considerations - ArticleDocumento4 pagineEMC Design Considerations - Articlethangaraj_icNessuna valutazione finora

- An-42007 AN42007 Safety, EMI and RFI ConsiderationsDocumento6 pagineAn-42007 AN42007 Safety, EMI and RFI ConsiderationsSunu PradanaNessuna valutazione finora

- Emi/Rfi Solutions: Vishay Intertechnology, IncDocumento16 pagineEmi/Rfi Solutions: Vishay Intertechnology, IncJesus LozanoNessuna valutazione finora

- Low Noise Printed Circuit Board DesignDocumento9 pagineLow Noise Printed Circuit Board DesignEmaxxSeverusNessuna valutazione finora

- Micrel PCB Design ConsiderationsDocumento0 pagineMicrel PCB Design Considerationstomscribd18Nessuna valutazione finora

- Noise Reduction TechniquesDocumento12 pagineNoise Reduction TechniquestamanogNessuna valutazione finora

- AP2402630 EMC Guidelines 1Documento63 pagineAP2402630 EMC Guidelines 1Tuấn Nguyễn TrungNessuna valutazione finora

- Thermal Pad GuidelinesDocumento7 pagineThermal Pad Guidelinessteviej85Nessuna valutazione finora

- UIT EMC StandardsDocumento139 pagineUIT EMC StandardsAmity2009Nessuna valutazione finora

- EMC Techniques in Electronic Design Part 1 - Circuit Design and Choice of ComponentsDocumento31 pagineEMC Techniques in Electronic Design Part 1 - Circuit Design and Choice of Componentsjax almarNessuna valutazione finora

- Minimizing RF PCB Electromagnetic Emissions: TutorialDocumento4 pagineMinimizing RF PCB Electromagnetic Emissions: TutorialsundarvrpNessuna valutazione finora

- EMC Techniques in Electronic Design Part 2 - Cables and ConnectorsDocumento40 pagineEMC Techniques in Electronic Design Part 2 - Cables and Connectorsjax almarNessuna valutazione finora

- EMC Fact FileDocumento2 pagineEMC Fact FilewjscoNessuna valutazione finora

- Design of High Speed Op Amp With DifferentDocumento54 pagineDesign of High Speed Op Amp With DifferentAbhishek MatNessuna valutazione finora

- Emc Design FundamentalsDocumento285 pagineEmc Design FundamentalsnekuNessuna valutazione finora

- EMC Coupling & Countermeasures GuideDocumento5 pagineEMC Coupling & Countermeasures GuideVigneswaran VigneshNessuna valutazione finora

- Shielding RF Components at The Package LeveDocumento12 pagineShielding RF Components at The Package LeveSebastian ReguanNessuna valutazione finora

- PCB Power Supply Design AlteraDocumento20 paginePCB Power Supply Design AlteraSdfsdfgn SdfndsiNessuna valutazione finora

- VHDL GuideDocumento30 pagineVHDL Guidelxz5101Nessuna valutazione finora

- PCB Design TipsDocumento14 paginePCB Design TipsShubham Kumar100% (1)

- High-speed serial links: Trends and challenges for achieving 100 Tb/s throughputDocumento39 pagineHigh-speed serial links: Trends and challenges for achieving 100 Tb/s throughputArvind HanumantharayappaNessuna valutazione finora

- Surface Mounting Guidelines For MEMS Sensors in An LGA PackageDocumento9 pagineSurface Mounting Guidelines For MEMS Sensors in An LGA PackagebobbyccwNessuna valutazione finora

- EMC Design and Interconnection Techniques: Cable Routing and ConnectionDocumento27 pagineEMC Design and Interconnection Techniques: Cable Routing and ConnectionMurali MohanNessuna valutazione finora

- PCB Material Selection For RF Microwave and Millimeter Wave Designs 1Documento61 paginePCB Material Selection For RF Microwave and Millimeter Wave Designs 1Umair IllahiNessuna valutazione finora

- High Frequency PCB LayoutDocumento26 pagineHigh Frequency PCB LayoutJaime Sebastian CardenasNessuna valutazione finora

- Basics of PCB Design and FabricationDocumento8 pagineBasics of PCB Design and Fabricationhungdee100% (1)

- Signal Integrity PDFDocumento21 pagineSignal Integrity PDFmosa totahNessuna valutazione finora

- EMI Filters - CeramicDocumento81 pagineEMI Filters - CeramicmetamendNessuna valutazione finora

- PCB Guidlines: Acronics Systems, IncDocumento19 paginePCB Guidlines: Acronics Systems, IncOri ONNessuna valutazione finora

- Proper PCB Layout Techniques Maximize Power Module PerformanceDocumento4 pagineProper PCB Layout Techniques Maximize Power Module PerformancesumalaglNessuna valutazione finora

- Do's and Don'ts For PCB Layer Stack-Up: by - Pragnesh Patel & Ronak ShahDocumento9 pagineDo's and Don'ts For PCB Layer Stack-Up: by - Pragnesh Patel & Ronak Shahbasit aliNessuna valutazione finora

- Grounding of Mixes Signal SystemsDocumento4 pagineGrounding of Mixes Signal SystemsPratik ShiroreNessuna valutazione finora

- EMIESD Protection Solutions For The CAN BusDocumento9 pagineEMIESD Protection Solutions For The CAN BusascensorimNessuna valutazione finora

- Embedded Software TestingDocumento25 pagineEmbedded Software TestingRomiSayagoNessuna valutazione finora

- High Speed Design Techniques PDFDocumento416 pagineHigh Speed Design Techniques PDFvpsampath100% (1)

- PCB Layout TipsDocumento34 paginePCB Layout TipsMallappa Patil100% (2)

- PCB Design Steps & Complete Guide - CirexxDocumento10 paginePCB Design Steps & Complete Guide - CirexxReetipragya SinghNessuna valutazione finora

- AVR-GCC and The PROGMEM AttributeDocumento10 pagineAVR-GCC and The PROGMEM AttributeleonttiNessuna valutazione finora

- Altium WP Designing For Testability WEBDocumento6 pagineAltium WP Designing For Testability WEBjagadees21Nessuna valutazione finora

- Designing Your Emi FilterDocumento8 pagineDesigning Your Emi FilterVictor Pastor RebolloNessuna valutazione finora

- Guidelines For RF PCB Design and Microwave Materials OptionsDocumento15 pagineGuidelines For RF PCB Design and Microwave Materials OptionsjackNessuna valutazione finora

- Simple RF PCB Layout Tips for 2.4GHz and 5GHzDocumento10 pagineSimple RF PCB Layout Tips for 2.4GHz and 5GHzDang Cao QuyenNessuna valutazione finora

- PCB Design For Fabrication IssuesDocumento45 paginePCB Design For Fabrication IssuesAndersonEmanuelOliveiraNessuna valutazione finora

- High Speed Design Techniques PDFDocumento416 pagineHigh Speed Design Techniques PDFbolermNessuna valutazione finora

- PCB Design Guide for EMC ComplianceDocumento62 paginePCB Design Guide for EMC ComplianceVishu VishwajaNessuna valutazione finora

- EMC Design Guide For PCBDocumento78 pagineEMC Design Guide For PCBFaruq AhmedNessuna valutazione finora

- EMC Fundamentals Sept 2006Documento63 pagineEMC Fundamentals Sept 2006goodgoliers01Nessuna valutazione finora

- Tutorial On FPGA RoutingDocumento11 pagineTutorial On FPGA RoutingAnshika SharmaNessuna valutazione finora

- ADS EM GuideDocumento162 pagineADS EM Guidemuhammadabid4uNessuna valutazione finora

- ADS2012 QuickRererenceGuideDocumento90 pagineADS2012 QuickRererenceGuidexubuliNessuna valutazione finora

- Automotive DSDocumento2 pagineAutomotive DShemuchandarNessuna valutazione finora

- Foxboro™ SCADA SCD6000 RoHS Dual Communication Modules - 41h8k4rDocumento14 pagineFoxboro™ SCADA SCD6000 RoHS Dual Communication Modules - 41h8k4rMuhd Nu'man HNessuna valutazione finora

- Low EMI For Power IsolationDocumento14 pagineLow EMI For Power IsolationSuvadip BanerjeeNessuna valutazione finora

- Tools2 PDFDocumento2 pagineTools2 PDFbacuoc.nguyen356Nessuna valutazione finora

- Multi-Drop Channel-Link OperationDocumento4 pagineMulti-Drop Channel-Link OperationBalan PalaniappanNessuna valutazione finora

- EMC Printed Circuit Board PCB TipsDocumento6 pagineEMC Printed Circuit Board PCB TipsCarlos TrustNessuna valutazione finora

- PCB Layout Stackup Guide - Component Placement, Traces, Layers & EMCDocumento16 paginePCB Layout Stackup Guide - Component Placement, Traces, Layers & EMCAjayPanickerNessuna valutazione finora

- EMI-EMC Engineering TipsDocumento6 pagineEMI-EMC Engineering TipsAbdullah RafiqueNessuna valutazione finora

- What Does MTBF Really Indicate?Documento1 paginaWhat Does MTBF Really Indicate?senkum812002Nessuna valutazione finora

- Input Filter Design For SMPSDocumento21 pagineInput Filter Design For SMPSsenkum812002Nessuna valutazione finora

- FundPicker Other OptionsDocumento2 pagineFundPicker Other Optionssenkum812002Nessuna valutazione finora

- Boeing 787 and Lithium Ion Battery FailureDocumento3 pagineBoeing 787 and Lithium Ion Battery Failuresenkum812002Nessuna valutazione finora

- Average Current Mode ControlDocumento15 pagineAverage Current Mode Controlsmart2986Nessuna valutazione finora

- Itr 62 Form 15 GDocumento2 pagineItr 62 Form 15 GAccounting & TaxationNessuna valutazione finora

- AB LetterDocumento14 pagineAB Lettersenkum812002Nessuna valutazione finora

- PFC Feedforward TermDocumento5 paginePFC Feedforward Termsenkum812002Nessuna valutazione finora

- Research Scorecard: December 2015Documento46 pagineResearch Scorecard: December 2015senkum812002Nessuna valutazione finora

- FundPicker Other OptionsDocumento2 pagineFundPicker Other Optionssenkum812002Nessuna valutazione finora

- 24 Op Amps3Documento17 pagine24 Op Amps3prasad357100% (1)

- Single-Stage Grid-Tied PV InverterDocumento159 pagineSingle-Stage Grid-Tied PV Invertersenkum812002Nessuna valutazione finora

- MGE UPS TopologiesDocumento11 pagineMGE UPS Topologiesoadipphone7031Nessuna valutazione finora

- AN166 Basic feedback theoryDocumento5 pagineAN166 Basic feedback theorySourik BharNessuna valutazione finora

- A Guide To Battery ChargingDocumento7 pagineA Guide To Battery Chargingsenkum812002Nessuna valutazione finora

- How to Size UPS BatteriesDocumento6 pagineHow to Size UPS BatteriesRupon RupNessuna valutazione finora

- Battery Backup Calculation For UPS RuntimeDocumento1 paginaBattery Backup Calculation For UPS Runtimeullaschaudhari100% (2)

- MIT OpenCourseWare Http://Ocw - Mit.eduDocumento13 pagineMIT OpenCourseWare Http://Ocw - Mit.edusnehithNessuna valutazione finora

- Voltage FolloweeDocumento16 pagineVoltage Followeesenkum812002Nessuna valutazione finora

- Analysis of The Sallen-Key ArchitectureDocumento18 pagineAnalysis of The Sallen-Key ArchitectureGerardo Amadeus HernándezNessuna valutazione finora

- Load Sharing PDFDocumento4 pagineLoad Sharing PDFsenkum812002Nessuna valutazione finora

- Inverter Battery Sizing FaqDocumento2 pagineInverter Battery Sizing Faqmaven3Nessuna valutazione finora

- H2PTodmbhjay1308 Design PowerELab PDFDocumento11 pagineH2PTodmbhjay1308 Design PowerELab PDFsenkum812002Nessuna valutazione finora

- Power Supply Design 1 PDFDocumento12 paginePower Supply Design 1 PDFsenkum812002Nessuna valutazione finora

- AN10273-Power FET Avalanche Ruggedness Rating PDFDocumento13 pagineAN10273-Power FET Avalanche Ruggedness Rating PDFsenkum812002Nessuna valutazione finora

- L-11 (GDR) (Et) ( (Ee) Nptel)Documento25 pagineL-11 (GDR) (Et) ( (Ee) Nptel)Mohammad Imran KhanNessuna valutazione finora

- Input EMI Filters For SMPS PDFDocumento8 pagineInput EMI Filters For SMPS PDFsenkum812002Nessuna valutazione finora

- ST-Rectifier Selection PDFDocumento20 pagineST-Rectifier Selection PDFsenkum812002Nessuna valutazione finora

- Snubbers Circuits - HHPDFDocumento24 pagineSnubbers Circuits - HHPDFsenkum812002Nessuna valutazione finora

- Power Saver for IndustriesDocumento13 paginePower Saver for IndustriesderejeNessuna valutazione finora

- Comparison XGSLab Vs CDEGS 2015 05Documento7 pagineComparison XGSLab Vs CDEGS 2015 05EshanNessuna valutazione finora

- Motion in A Straight LineDocumento26 pagineMotion in A Straight LineLord Siva100% (3)

- Projectile Motion TestDocumento7 pagineProjectile Motion Testjoan marie PeliasNessuna valutazione finora

- Final ProjectDocumento27 pagineFinal ProjectMohit KeshriNessuna valutazione finora

- Standard Terminology For Vehicle Dynamics SimulationDocumento14 pagineStandard Terminology For Vehicle Dynamics SimulationRam Krishan SharmaNessuna valutazione finora

- Spring Damping On Matlab PlatformDocumento3 pagineSpring Damping On Matlab PlatformShaharior AnikNessuna valutazione finora

- Circuitpages Light Dark Activated RelayDocumento14 pagineCircuitpages Light Dark Activated Relayalexwongks6118Nessuna valutazione finora

- Eddy current brake slows trains using electromagnetic inductionDocumento4 pagineEddy current brake slows trains using electromagnetic inductionAafreen MushtaqNessuna valutazione finora

- San Rank en Test-Phase 1 - Paper 1Documento15 pagineSan Rank en Test-Phase 1 - Paper 1grumNessuna valutazione finora

- Acceleration DLPDocumento3 pagineAcceleration DLPMark Anthony BesinalNessuna valutazione finora

- Coulombs Charges and Field Multiple QuestionsDocumento9 pagineCoulombs Charges and Field Multiple QuestionsjitenhrtNessuna valutazione finora

- Synchronous MachineDocumento24 pagineSynchronous MachineNur AinaqilahNessuna valutazione finora

- BioMechanics of Canine RetractionDocumento113 pagineBioMechanics of Canine Retractionarshabharata100% (5)

- Electrostatics ConceptsDocumento32 pagineElectrostatics ConceptsRichmond NyamadiNessuna valutazione finora

- Basic Electricity: Continuing Education Professional Development CourseDocumento298 pagineBasic Electricity: Continuing Education Professional Development CourseankitNessuna valutazione finora

- CM Inductor Analysis: Choosing the Proper Winding DesignDocumento7 pagineCM Inductor Analysis: Choosing the Proper Winding Designdebass3Nessuna valutazione finora

- MOCK-CET PHYSICS PAPER-1 REVIEWDocumento10 pagineMOCK-CET PHYSICS PAPER-1 REVIEWRohan G (Simplinovus)Nessuna valutazione finora

- IEEE Recommended Guide For Measuring Ground Resistance and Potential Gradients in The EarthDocumento20 pagineIEEE Recommended Guide For Measuring Ground Resistance and Potential Gradients in The EarthSOURAVNessuna valutazione finora

- Egg Drop Background InformationDocumento3 pagineEgg Drop Background Informationapi-449009025Nessuna valutazione finora

- LOFCADocumento35 pagineLOFCAAsghar BalochNessuna valutazione finora

- Chapter 1 Transmission LineDocumento87 pagineChapter 1 Transmission LinePhamHungNessuna valutazione finora

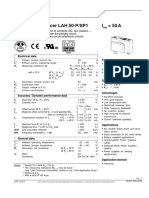

- Lah 50-P-SP1Documento3 pagineLah 50-P-SP1thanggimme.phanNessuna valutazione finora

- General Physics 1 Quarter 2 WEEK 2Documento5 pagineGeneral Physics 1 Quarter 2 WEEK 2Normal Fan100% (1)

- Hall Effect PDFDocumento26 pagineHall Effect PDFmangsureshNessuna valutazione finora

- Science 7 Module 7 3RD QuarterDocumento15 pagineScience 7 Module 7 3RD QuarterSarah DarriguezNessuna valutazione finora

- Code MATH Course Details PDFDocumento80 pagineCode MATH Course Details PDFAnees RahmanNessuna valutazione finora

- Negative and Zero Sequence Directional RelaysDocumento17 pagineNegative and Zero Sequence Directional RelaysSubhadeep PaladhiNessuna valutazione finora

- Solar-Powered Bicycle DesignDocumento16 pagineSolar-Powered Bicycle DesignjonNessuna valutazione finora

- Statics Course SyllabusDocumento5 pagineStatics Course Syllabusapi-404583863Nessuna valutazione finora

- University of Chicago Press Fall 2009 CatalogueDa EverandUniversity of Chicago Press Fall 2009 CatalogueValutazione: 5 su 5 stelle5/5 (1)

- University of Chicago Press Fall 2009 Distributed TitlesDa EverandUniversity of Chicago Press Fall 2009 Distributed TitlesValutazione: 1 su 5 stelle1/5 (1)