Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Design of 8 Bit Alu Using Microwind 3.1

Caricato da

ijaertTitolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Design of 8 Bit Alu Using Microwind 3.1

Caricato da

ijaertCopyright:

Formati disponibili

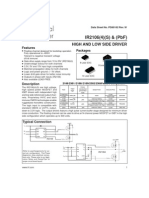

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

50

www.ijaert.org

DESIGN OF 8 BIT ALU USING MICROWIND 3.1

Prem Chandra Gupta

1

, Rajesh Mehra

2

1,

ME Scholar, Electronics & Comm., NITTTR, Chandigarh., India

2

Associate Professor, Electronics & Comm., NITTTR, Chandigarh. Ministry of HRD Govt. of India

ABSTRACT

In this paper 8-bit arithmetic logic unit (ALU) has been

designed using DSCH 3.5 and Microwind 3.1. Schemtic

for different operations like NOT, OR, XOR, Addition

Subtraction has been designed by using DSCH3.5 and

layout and analysis has been observed by using

Microwind3.1. ALU (Arithmetic logic unit) is a critical

component of a microprocessor and the core component

of central processing unit. [1] ALUs comprise the

combinational logic that implements logic operations,

such as AND, OR, EXOR and NOT and arithmetic

operations, such as ADD and SUBTRACT. An

arithmetic logic unit (ALU) is a digital circuit which

performs arithmetic, logic and shift operations on two n-

bit digital words.

Keywords: ALU, DSCH3.5, Microwind3.1, Logic Gate

I. INTRODUCTION

Functionally, an ALU can be divided into three circuits:

the arithmetic circuit, the logic circuit and the shift

circuit.

i)The arithmetic circuit performs typical arithmetic

operations such as addition, subtraction and increment or

decrement by one. The basic component of an arithmetic

circuit is the Full adder. By using a multiplexer to

control the data inputs to the adder, it is possible to

obtain different types of arithmetic

operations.[2]Depending on the selection inputs and the

input carry, the arithmetic circuit can generates the

different arithmetic micro operations listed Table 1.

ii) The ALU, logic circuit performs the basic logic micro

operations: NOT, AND, OR and XOR. From these four

micro operations all known logic micro operations can

be derived. The four gates generate the four logic

operations and the multiplexer select the desired

operation as shown in Table 2.

Table 1: Function table of the arithmetic Circuit

Table 2: Function table of the 2-bit Logic Circuit

iii) Shift circuit used to perform the shift micro

operations. The contents of a register can be shifted

serially to the left or to the right. The shift circuit

contains multiplexers. when the select line is 0 the 4-bit

input data are shifted right. When the select line is 1 the

input data are shifted left. There are two serial inputs one

for shift left and other one for shift right. The function

table shows the outputs of the multiplexers in each case.

Table 3.

Table 3: Function table of the 4-bit Shift Circuit

S H3

H3 H2 H1 H0

0 IR A3 A2 A1

1 A2 A1 A0 IL

Designing of ALU

ALU is designed by the following correct procedure,

some introductory part is given as, making the

S1 S0 Cin Inpu

t

Output Micro

operation

0 0 0 B A+B Add

0 0 1 B A+B+1 Add with cry

0 1 0 B A+B Sub with

borrow

0 1 1 B A-B Sub

1 0 0 0 A Transfer A

1 0 1 0 A+1 Increment by 1

1 1 0 1 A-1 Decrement A

by1

1 1 1 1 A Transfer A

S1 S0 Output Operation

0 0 AB AND

0 1 A+B OR

1 0 AB XOR

1 1 A Complement

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

51

www.ijaert.org

programming, draw the schematic diagram, and for the

layout diagram at each and every step check the DRC for

the proper designing [2]. The design of the 8-bit ALU is

based on the use of a carry select line. Once verification

was completed parasitic were extracted. To create a test

for finding the maximum operating frequency a pseudo-

random input stream was applied to each input of the

ALU and observed the circuit during the input transition.

If the switching of the transistors takes longer than the

period of the input then the ALU may give a erroneous

output.

II. MODULE

There are different circuit use for the designing of the

ALU, schematic and waveform (DC and AC Analysis)

some of them are as follows:

A) Inverter

An inverter or NOT gate is logic gate which an inverter

circuit outputs a voltage representing the opposite logic-

level to its input. Inverters can be constructed using a

single NMOS transistor or a single PMOS transistor

coupled with a resistor. Since this 'resistive-drain'

approach uses only a single type of transistor, it can be

fabricated at low cost. However, because current flows

through the resistor in one of the two states, the

resistive-drain configuration is disadvantaged for power

consumption and processing speed implements logical

negative.

The truth table is shown in table

Schematic

Layout

Fig1.Schematic and Layout of NOT

WAVEFORMS

i) DC Analysis

ii) AC Analysis

Fig2. DC and AC waveform of NOT

B) AND gate

Schematic

Layout

Fig3. Schematic and Layout of AND

WAVEFORMS

i) DC Analysis

ii) AC Analysis

Fig4. DC and AC waveform of AND

INPUT(A) OUTPUT(A

)

0 1

1 0

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

52

www.ijaert.org

C) OR gate

Schematic

Layout

Fig5.Schematic and Layout of OR

WAVEFORMS

i) DC Analysis

(ii) AC

Analysis

Fig6.DC and AC waveform of OR

D) XOR Gate

Schematic

Layout

Fig7. Schematic and Layout of XOR

Waveforms

i)DC Analysis

ii) AC Analysis

Fig8. DC and AC waveform of XOR

E) Full Adder

In ALU, full adder forms the core of the entire design.

The full adder performs the computing function of the

ALU. A full adder could be defined as a combinational

circuit that forms the arithmetic sum of three input bits

[4]. It consists of three inputs and two outputs. In our

design, we have designated the three inputs as A, B and

Cin. The third input Cin represents carry input to the

first stage. The outputs are SUM and CARRY. Figure

shows the logic level diagram of a full adder. The

Boolean expressions for the SUM and CARRY bits are

as shown below.

SUM= AB Cin

CARRY = A B + A Cin + B C

CARRY = A B + A Cin + B

Cin

SUM= AB Cin

FULL

ADDE

R

A

c

B

c

B

in

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

53

www.ijaert.org

Schematic

Layout

Fig9.Schematic and Layout of full adder

WAVEFORMS

i)DC Analysis

ii)AC Analysis

Fig10.DC and AC waveform of full adder

F)Full Subtractor

Full Subtractor is a combinational circuit with three

inputs A, B and B

in

and two outputs Difference(D) and

Borrow(B

0

).

D = ABB

in

B

0

= AB

in

+ AB + BB

in

Schematic

G)Multiplexer

Multiplexer (or MUX) is a device that selects one of

several analog or digital input signals and forwards the

selected input into a single line. A multiplexer of

2

n

inputs has n select lines, which are used to select

which input line to send to the output. Multiplexers are

mainly used to increase the amount of data that can be

sent over the network within a certain amount of time

and bandwidth. A multiplexer is also called a data

selector.

Schematic

Layout

Fig11. Schematic and Layout of MUX

WAVEFORMS

i)DCAnalysis

B

0

= AB

in

+AB + BB

in

D = A BB

in

FULL

SUBT

RACT

OR

A

c

B

c

B

in

InI

0

2:1 MUX

Fig 17:- Block of 2:1 MUX

InI

0

Sel

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

54

www.ijaert.org

ii) AC Analysis

Fig12.DC and AC waveform of MUX

H) Arithmetic Logic Unit

A 8-bit ALU has been designed for 3V operation. The

ALU can perform various arithmetic and logical

operations. The basic blocks of a computer are central

processing unit (CPU), memory unit, and input/output

unit.[5] CPU of the computer is basically the same as the

brain of a human being. It contains all the registers,

control unit and the arithmetic logic unit (ALU). ALU

considered as the most important subsystem in a digital

computer. An arithmetic logic unit (ALU) is a digital

circuit which performs arithmetic, logic and shift

operations on two n-bit digital words. Functionally, an

ALU can be divided up into three circuits: the arithmetic

circuit, the logic circuit and the shift circuit.[6] The 8-bit

ALU was formed by combining four Full Adder and

four Full Subtractor with five multiplexer as shown in

the schematic diagram.

Schematic

Layout

Fig13. Schematic and Layout of ALU

WAVEFORMS

i) AC Analysis

Fig14. AC waveform of ALU

III. CONCLUSIONS

Implementation of 8 bit arithmetic logic unit (ALU) is

presented. The design was implemented by using

DSCH3.5 and Microwind 3.1. ALU was designed to

perform arithmetic operations such as addition and

subtraction using 8-bit fast adder, logical operations such

as AND, OR, XOR and NOT operations, complement

operations and compare. The maximum operative

voltage is 1.2V and power dissipation is 0.852mW. The

ALU was designed for controller used in network

interface card.

REFERENCES

1. A design of low power 8-bit ALU ;Beom Seon

Ryu; Jung Sok Yi; Kie Young Lee; Tae Won

Cho TENCON 99. Proceedings of the IEEE

Region 10 Conference Volume: 2 Digital

ObjectIdentifier:10.1109/TENCON.1999.81855

6 ;Publication Year: 1999 , Page(s): 868 - 871

vol.2 ; IEEE Conference Publications .

2. Application Specific Low Power ALU Design

;Yu Zhou; Hui Guo Embedded and Ubiquitous

Computing, 2008. EUC '08. IEEE/IFIP

International Conference on Volume: 1 Digital

Object Identifier: 10.1109/EUC.2008.81

Publication Year: 2008 , Page(s): 214 - 220

Cited by: 1; IEEE Conference Publications.

3. The power dissipation comparison of different

ALU architectures; Junkai Sun; Anping

JiangMechanical and Electrical Technology

(ICMET), 2010 2nd International Conference on

Digital Object Identifier:

10.1109/ICMET.2010.5598395; Publication

Year: 2010 , Page(s): 430 - 433 ;IEEE

Conference Publications.

International Journal of Advanced Engineering Research and Technology (IJAERT)

Volume 2 Issue 2, May 2014, ISSN No.: 2348 8190

55

www.ijaert.org

4. Design of a high performance microcontroller;

Hu Yue-li; Cao Jia-lin; Ran Feng; Liang Zhi-

jian; High Density Microsystem Design and

Packaging and Component Failure Analysis,

2004. HDP '04. Proceeding of the Sixth IEEE

CPMT Conference on ;Digital Object Identifier:

10.1109/HPD.2004.1346667 ;Publication Year:

2004 , Page(s): 25 - 28 ; IEEE Conference

Publications.

5. Design of a superconducting ALU with a 3-input

XOR gate ; Takahashi, K.; Nagasawa, S.;

Hasegawa, H.; Miyahara, K.; Takai, H.;

Enomoto, Y.; Applied Superconductivity, IEEE

Transactions on Volume: 13, Issue: 2

,Part:1Digital Object Identifier:

10.1109/TASC.2003.813944 Publication Year:

2003 , Page(s): 551 - 554 Cited by: 3 ;IEEE

Journals & Magazines .

6. G P Pal, S Pal, A K Gupta, V Yadav Internal

Scan Test Methodology of Sequential Circuits,

pp- 059-062, IJSRET Volume 1 Issue 5, August

2012

7. The 8051 Microcontroller and Embedded

Systems; Second Edition; Muhammad Ali

Mazidi, Janice Gillispie Mazidi, Rolin D.

McKinlay.

8. Om Prakash, R.K.Prasad, B.S.Rai, Akhil

Kaushik, Analysis and Design of Logic Gates

Using Static and Domino Logic Technique,

IJSRET, Vol 1 Issue 5, pp- 179-183, August

2012

9. Om Prakash, Dr.B.S.Rai, Dr.Arun Kumar

Design and analysis of low power energy-

efficient, domino logic circuit for high speed

applications, pp- 1-4, IJSRET Volume 1 Issue

12, March 2013

10. Sunil Kumar Ojha ,Subrato Howlader Low-

Power CMOS SRAM Cell with Sleep

Transistors to Control Leakage Currents, pp-

37-40, IJSRET Volume 2 Issue 1, April 2013

11. U.Palani, M.Sujith,P.Pugazhendiran

Implementation of Memory Based

Multiplication Using Micro wind Software, pp-

45-50, IJSRET Volume 2 Issue 2, May 2013

12. Namrata Gupta Designing of Full Adder

Circuits for Low Power, pp- 215-219, IJSRET

Volume 2 Issue 4, July 2013

13. Neeraj Kumar Mishra Performance Evaluation

& Design Methodologies for Automated 32 Bit

CRC Checking for 32 bit address Using HDLC

Block pp- 242-246, IJSRET Volume 2 Issue

5, August 2013

Potrebbero piacerti anche

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsDa EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNessuna valutazione finora

- Engineering Optimization: An Introduction with Metaheuristic ApplicationsDa EverandEngineering Optimization: An Introduction with Metaheuristic ApplicationsNessuna valutazione finora

- Vlsi Project Report Arithmetic Logical Unit Using Verilog AluDocumento7 pagineVlsi Project Report Arithmetic Logical Unit Using Verilog AluAnurag KharwarNessuna valutazione finora

- System Simulation Using Matlab, State Plane PlotsDocumento7 pagineSystem Simulation Using Matlab, State Plane PlotsmosictrlNessuna valutazione finora

- HW1Documento11 pagineHW1Tao Liu YuNessuna valutazione finora

- Power System Simulation Lab ManualDocumento41 paginePower System Simulation Lab ManualgokulchandruNessuna valutazione finora

- AluDocumento10 pagineAluAbhishek PatraNessuna valutazione finora

- 1 Flexible Link ProjectDocumento15 pagine1 Flexible Link Projectprasaad08Nessuna valutazione finora

- Vlsi Implementation For High Speed AddersDocumento6 pagineVlsi Implementation For High Speed AddersPardha Saradhi Damarla100% (1)

- Project Report Arithmetic Logic Unit (ALU)Documento71 pagineProject Report Arithmetic Logic Unit (ALU)Hemant Sharma100% (1)

- 4bit Array MultiplierDocumento4 pagine4bit Array MultiplierRahul TiwariNessuna valutazione finora

- Bitwise OperatorsDocumento4 pagineBitwise OperatorsslspaNessuna valutazione finora

- ECE468 Computer Organization & Architecture The Design Process & ALU DesignDocumento16 pagineECE468 Computer Organization & Architecture The Design Process & ALU DesignchandruuncleNessuna valutazione finora

- DECO Lab FileDocumento101 pagineDECO Lab Fileshivam100% (1)

- Ec8691 - Microprocessors and Microcontrollers: Question BankDocumento5 pagineEc8691 - Microprocessors and Microcontrollers: Question Bankrkkumar07Nessuna valutazione finora

- ALU ReportDocumento11 pagineALU ReportAzad Kiyal100% (2)

- Ripple Carry and Carry Lookahead Adders: 1 ObjectivesDocumento8 pagineRipple Carry and Carry Lookahead Adders: 1 ObjectivesYasser RaoufNessuna valutazione finora

- Lab 12 Introduction To Simulink ObjectiveDocumento16 pagineLab 12 Introduction To Simulink Objectivesaran gulNessuna valutazione finora

- Unit2 Basic Structures of VHDLDocumento43 pagineUnit2 Basic Structures of VHDLRalph Anthony Constantino PlanterasNessuna valutazione finora

- Digital Lab Manual New PDFDocumento76 pagineDigital Lab Manual New PDFvmspraneethNessuna valutazione finora

- Design of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyDocumento22 pagineDesign of 16 Bit Alu: Prepared By: - Chandana - Mamatha - Praneeth ReddyChandanaNessuna valutazione finora

- Cadence Nclaunch LabDocumento86 pagineCadence Nclaunch Labsweety987Nessuna valutazione finora

- Arithmetic Logic Unit (ALU) MiniprojectDocumento3 pagineArithmetic Logic Unit (ALU) MiniprojectLuis AuquillaNessuna valutazione finora

- COA Lab Manual Experiment 1 PDFDocumento5 pagineCOA Lab Manual Experiment 1 PDFhimanshicNessuna valutazione finora

- Report On 4x1 MultiplexerDocumento17 pagineReport On 4x1 MultiplexerPRAVEEN KUMAWATNessuna valutazione finora

- Design and Simulation of 8 Bit Arithmetic Logic UnitDocumento88 pagineDesign and Simulation of 8 Bit Arithmetic Logic UnitBhuvnesh Kumar100% (1)

- MPMC Lab Manual To PrintDocumento138 pagineMPMC Lab Manual To PrintKasthuri SelvamNessuna valutazione finora

- Signals and SystemsDocumento3 pagineSignals and Systemsnisarg0% (1)

- Digital Logic NotesDocumento32 pagineDigital Logic Notesjadad50% (2)

- Ec - 501 - Microprocessor and Its ApplicationDocumento41 pagineEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivhareNessuna valutazione finora

- System Identification and Estimation in LabVIEWDocumento99 pagineSystem Identification and Estimation in LabVIEWDavidleonardo GalindoNessuna valutazione finora

- Cadence Basic SimulationDocumento10 pagineCadence Basic SimulationLarry FredsellNessuna valutazione finora

- 8086 Microprocessor Lab 1Documento7 pagine8086 Microprocessor Lab 1Tyler BarneyNessuna valutazione finora

- Unit 5 - VHDLDocumento15 pagineUnit 5 - VHDLMichael FosterNessuna valutazione finora

- Fuculty of Engineering Department: Instrumentoin and Control IDocumento15 pagineFuculty of Engineering Department: Instrumentoin and Control Ihappy sadNessuna valutazione finora

- Arithmetic and Logic Unit (ALU) PDFDocumento13 pagineArithmetic and Logic Unit (ALU) PDFnathulalusaNessuna valutazione finora

- Fuzzy Logic History and ApplicationsDocumento5 pagineFuzzy Logic History and ApplicationsYossry AwadNessuna valutazione finora

- Lab 5 Best First Search For SchedulingDocumento3 pagineLab 5 Best First Search For SchedulingchakravarthyashokNessuna valutazione finora

- DSP Question Paper April 2012Documento2 pagineDSP Question Paper April 2012Famida Begam100% (1)

- DLD Lab 1Documento5 pagineDLD Lab 1گيدوڙو ماڇيNessuna valutazione finora

- 05 FpgaDocumento54 pagine05 Fpgasoh_vakili100% (1)

- 4 Bit Cpu ReportDocumento16 pagine4 Bit Cpu ReportHarshil LodhiNessuna valutazione finora

- Shift RegisterDocumento25 pagineShift RegisterdianseptyaNessuna valutazione finora

- AddersDocumento5 pagineAddersShanuj GargNessuna valutazione finora

- Verilog Basic ExperimentsDocumento62 pagineVerilog Basic ExperimentsGaurav Soni0% (1)

- CSM&S 3-Queueing ModelsDocumento45 pagineCSM&S 3-Queueing Modelsnatnael abateNessuna valutazione finora

- Matlab Basics Tutorial: VectorsDocumento52 pagineMatlab Basics Tutorial: VectorsMohit Bathla MontyNessuna valutazione finora

- Combinational Logic: 7.1. Functional SpecificationsDocumento5 pagineCombinational Logic: 7.1. Functional SpecificationskapetanmichalisNessuna valutazione finora

- Control Tutorials For MATLAB and Simulink - Simulink Basics TutorialDocumento20 pagineControl Tutorials For MATLAB and Simulink - Simulink Basics TutorialManoj HandeNessuna valutazione finora

- RISC Vs CISC, Harvard V/s Van NeumannDocumento35 pagineRISC Vs CISC, Harvard V/s Van NeumannVRAJ PATELNessuna valutazione finora

- Labview File 5th SemDocumento20 pagineLabview File 5th Semvik9292Nessuna valutazione finora

- CS34 Digital Principles and System DesignDocumento107 pagineCS34 Digital Principles and System DesignSara PatrickNessuna valutazione finora

- DipTrace TutorialDocumento134 pagineDipTrace TutorialMetalloyNessuna valutazione finora

- Maxima Book Chapter 8Documento38 pagineMaxima Book Chapter 8prakush_prakushNessuna valutazione finora

- VHDL Concurrent Assignment ExamplesDocumento9 pagineVHDL Concurrent Assignment ExamplesFares H. Abuali100% (1)

- Introduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadDocumento117 pagineIntroduction To Control: Dr. Muhammad Aamir Assistant Professor Bahria University IslamabadEnGr Asad Hayat BanGashNessuna valutazione finora

- Digital Signal Processors Architectures Implementations and ApplicationsDocumento17 pagineDigital Signal Processors Architectures Implementations and ApplicationsAbirami Kannan0% (3)

- Application-Specific Integrated Circuit ASIC A Complete GuideDa EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNessuna valutazione finora

- An Introduction to MATLAB® Programming and Numerical Methods for EngineersDa EverandAn Introduction to MATLAB® Programming and Numerical Methods for EngineersNessuna valutazione finora

- Simulation and Analysis of LLC Resonant Converter Using Closed Loop PI ControllerDocumento3 pagineSimulation and Analysis of LLC Resonant Converter Using Closed Loop PI ControllerijaertNessuna valutazione finora

- Changes in The Physical State of Ceramics Materials Brought About by The Removal of Free WaterDocumento5 pagineChanges in The Physical State of Ceramics Materials Brought About by The Removal of Free WaterijaertNessuna valutazione finora

- Detection of Melanoma Using Asymmetric FeaturesDocumento7 pagineDetection of Melanoma Using Asymmetric FeaturesijaertNessuna valutazione finora

- A Review On Ceramics and Its Economic EmpowermentDocumento4 pagineA Review On Ceramics and Its Economic EmpowermentijaertNessuna valutazione finora

- Advancement in Knitted Structure For Industrial Applications - A ReviewDocumento8 pagineAdvancement in Knitted Structure For Industrial Applications - A ReviewijaertNessuna valutazione finora

- Characterization of Ezzodo Clay Deposit For Its Industrial PotentialsDocumento8 pagineCharacterization of Ezzodo Clay Deposit For Its Industrial PotentialsijaertNessuna valutazione finora

- Geological/survey of Clay MaterialDocumento9 pagineGeological/survey of Clay MaterialijaertNessuna valutazione finora

- Design of Robust Type-2 Fuzzy Logic Power System Stabilizer Using Hopf BifurcationsDocumento5 pagineDesign of Robust Type-2 Fuzzy Logic Power System Stabilizer Using Hopf BifurcationsijaertNessuna valutazione finora

- A Review On Synthesis, Characterization and Applications of Silica ParticlesDocumento7 pagineA Review On Synthesis, Characterization and Applications of Silica ParticlesijaertNessuna valutazione finora

- Behaviour of Concrete Partially Replacement of Cement by Steatite and Polypropylene FibreDocumento4 pagineBehaviour of Concrete Partially Replacement of Cement by Steatite and Polypropylene FibreijaertNessuna valutazione finora

- Comparative Analysis On Partial Replacement of Cement by Metakaolin and Fine Aggregate by Granite PowderDocumento5 pagineComparative Analysis On Partial Replacement of Cement by Metakaolin and Fine Aggregate by Granite PowderijaertNessuna valutazione finora

- Optimization of Gear To Improve Performance of GearboxDocumento4 pagineOptimization of Gear To Improve Performance of Gearboxijaert100% (1)

- Feature Selection Approach For Intrusion Detection System Based On Pollination AlgorithmDocumento5 pagineFeature Selection Approach For Intrusion Detection System Based On Pollination AlgorithmijaertNessuna valutazione finora

- Structural Optimization of Composite Railway SleepersDocumento6 pagineStructural Optimization of Composite Railway SleepersijaertNessuna valutazione finora

- Analysis of Gable Frame StructureDocumento7 pagineAnalysis of Gable Frame Structureijaert50% (2)

- Comparative Study of End Moments Regarding Application of Rotation Contribution Method (Kani's Method) & Moment Distribution Method For The Analysis of Viaduct FrameDocumento5 pagineComparative Study of End Moments Regarding Application of Rotation Contribution Method (Kani's Method) & Moment Distribution Method For The Analysis of Viaduct FrameijaertNessuna valutazione finora

- Mux & Demux - 19.9Documento31 pagineMux & Demux - 19.9j vanishreeNessuna valutazione finora

- SoC or System On Chip Seminar ReportDocumento28 pagineSoC or System On Chip Seminar ReportVivek PandeyNessuna valutazione finora

- IC and ECAD LabDocumento88 pagineIC and ECAD LabVeerayya JavvajiNessuna valutazione finora

- MTVL043Documento2 pagineMTVL043deepakkr22781Nessuna valutazione finora

- DLD Course FileDocumento15 pagineDLD Course FileJohn PaulNessuna valutazione finora

- TMS320F206 Digital Signal ProcessorDocumento57 pagineTMS320F206 Digital Signal ProcessorMiguel Ángel CoriaNessuna valutazione finora

- DSD Notes Unit 4 PDFDocumento15 pagineDSD Notes Unit 4 PDFVAISHAKA N RAJNessuna valutazione finora

- Vlsi Design Unit 2 2019Documento37 pagineVlsi Design Unit 2 2019Ishan Mahendra PatelNessuna valutazione finora

- A0260035U HE RUNZE ProjectDocumento13 pagineA0260035U HE RUNZE Project赵子杰Nessuna valutazione finora

- Tn2906 Nand Flash ControllerDocumento21 pagineTn2906 Nand Flash ControllerMark AbadiesNessuna valutazione finora

- E1 - Digital Logic GatesDocumento5 pagineE1 - Digital Logic GatesNEIL NADANessuna valutazione finora

- First Order Active Filters (LPF, HPF) : (A) Low Pass FilterDocumento12 pagineFirst Order Active Filters (LPF, HPF) : (A) Low Pass FilterVRNessuna valutazione finora

- Experiment#11 Clocked Sequential Circuits and CountersDocumento8 pagineExperiment#11 Clocked Sequential Circuits and CountersfahadNessuna valutazione finora

- Resume Arvind ShrivastavaDocumento2 pagineResume Arvind ShrivastavaArvind ShrivastavaNessuna valutazione finora

- TN005 Reset Synchronization v00Documento6 pagineTN005 Reset Synchronization v00Brahmam MadamanchiNessuna valutazione finora

- PIC16F716 Data Sheet: 8-Bit Flash-Based Microcontroller With A/D Converter and Enhanced Capture/Compare/PWMDocumento126 paginePIC16F716 Data Sheet: 8-Bit Flash-Based Microcontroller With A/D Converter and Enhanced Capture/Compare/PWMCarlos NavarroNessuna valutazione finora

- 74HC147Documento8 pagine74HC147Nelson RodriguezNessuna valutazione finora

- Ropez Extra Phase Stages: Connection To Main PCBDocumento1 paginaRopez Extra Phase Stages: Connection To Main PCBDiddi_86Nessuna valutazione finora

- Principles of CPU Architecture - Logic Gates, MOSFETS and VoltageDocumento8 paginePrinciples of CPU Architecture - Logic Gates, MOSFETS and VoltageAkmad AliNessuna valutazione finora

- Section C - Microprocessor MCQDocumento6 pagineSection C - Microprocessor MCQviki awsacNessuna valutazione finora

- Seminar Report Soumya.m 18130708Documento18 pagineSeminar Report Soumya.m 18130708shishiNessuna valutazione finora

- Cdnlive 2016 - Pspice - Matlab PaperDocumento38 pagineCdnlive 2016 - Pspice - Matlab PaperHoàng TrươngNessuna valutazione finora

- NAND Flash: Code Information (1/3)Documento3 pagineNAND Flash: Code Information (1/3)hoang_tuanNessuna valutazione finora

- C4300 NPNDocumento4 pagineC4300 NPNTrongtai PhamNessuna valutazione finora

- IR2106Documento23 pagineIR2106manchau717Nessuna valutazione finora

- VLSI Physical DesignDocumento7 pagineVLSI Physical DesignPinjare Sampatrao LNessuna valutazione finora

- Tutorial 03 Latch FF State Machines 1Documento81 pagineTutorial 03 Latch FF State Machines 1Andreea ChiriluşNessuna valutazione finora

- Training On EDT (1) - Copy (1) (3) 1Documento52 pagineTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- VGGVDocumento32 pagineVGGVpoiuret isthisgoodNessuna valutazione finora

- Dte Micro Project OriginalDocumento14 pagineDte Micro Project Originaljhjh25% (4)