Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Fabrication of TTL

Caricato da

Rohit Agrawal0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

154 visualizzazioni6 paginettl fab

Titolo originale

Fabrication of Ttl

Copyright

© © All Rights Reserved

Formati disponibili

TXT, PDF, TXT o leggi online da Scribd

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentottl fab

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato TXT, PDF, TXT o leggi online su Scribd

0 valutazioniIl 0% ha trovato utile questo documento (0 voti)

154 visualizzazioni6 pagineFabrication of TTL

Caricato da

Rohit Agrawalttl fab

Copyright:

© All Rights Reserved

Formati disponibili

Scarica in formato TXT, PDF, TXT o leggi online su Scribd

Sei sulla pagina 1di 6

1.

A process for fabricating a semiconductor device, comprising the steps of:

forming a second conductivity type well region over a first conductivity type si

licon semiconductor substrate;

forming successively a first oxide layer and a nitride layer over said substrate

;

selectively removing portions of said nitride layer over a first MOS transistor

region on said well region, a second transistor region on said substrate, and ch

annel-stop regions around said second transistor region;

forming a field oxide layer in the first MOS transistor, second transistor and c

hannel-stop regions exposed by said step of selectively removing portions of sai

d nitride layer,

forming drain and source of said first MOS transistor over said well region, and

stop-channel regions in said substrate;

forming ohmic contact regions in an edge of said well region, and drain and sour

ce of said second MOS transistor between said stop-channel regions over said sub

strate;

forming a second oxide layer on the whole surface of said substrate to form a ga

te oxide layer after removing said nitride layer and said first oxide layer of t

he gate regions of said first and second MOS transistors;

forming contact windows for contacting the source and drain of said first and se

cond MOS transistors;

forming a pattern of a first metal layer to form electrodes of said first and se

cond MOS transistors;

forming a pattern of low temperature oxide layer over said first metal layer to

insulate a specified portion;

forming a pattern of a second metal layer connected with first metal layer throu

gh said contact windows, being insulated from said first metal layer by said low

temperature oxide layer; and

forming a protection layer over said second metal layer.

2. A process as claimed in claim 1, further comprising the steps for concurrentl

y removing the nitride layers over the edge region of said second conductivity t

ype well region, a region to form said first MOS transistor on said well region,

a region to form said second transistor on said substrate, and the stop-channel

region to be formed around said second MOS transistor region, after said step o

f forming successively the first oxide layer and the nitride layer over said sub

strate, and then forming said field oxide layer in the regions exposed by removi

ng the nitride layers said nitride layer by a heat treatment process.

3. A process as claimed in claim 2, further comprised of forming said second con

ductivity type well by implanting second conductivity type ions in a dose of 2101

5 -31015 ions/cm2 with an energy of 40-50 KeV, and thereon heat-treating for the

junction depth to reach 5-6 m.

4. A process as claimed in claim 2, wherein the drain and source of said first M

OS transistor, and said stop-channel region are formed by ion-implanting phospho

rus and arsenic ions, and thereupon heat-treating for a predetermined junction d

epth.

5. A process as claimed in claim 2, wherein the drain and source of said second

MOS transistor, and said ohmic contact region of said well edge are formed by im

planting first conductivity N-type ions, and heat-treating for the junction dept

h to be deeper of the drain and source of said first MOS transistor.

6. A process for fabricating a semiconductor device, comprising the steps of:

forming a second conductivity type well region over a first conductivity type si

licon semiconductor substrate;

forming successively a first oxide layer and a nitride layer over said substrate

;

selectively removing portions of said nitride layer over a first MOS transistor

region on said well region, a second transistor region on said substrate, and ch

annel-stop regions around said second transistor region;

forming a field oxide layer in the first MOS transistor, second transistor and c

hannel-stop regions exposed by said step of selectively removing portions of sai

d nitride layer,

forming a drain and a source of a first MOS transistor over said well region, an

d stop-channel regions in said substrate;

forming ohmic contact regions in an edge of said well region, and drain and a so

urce of second MOS transistor between said stop-channel regions over said substr

ate;

forming a second oxide layer on the surface of said substrate to form a gate oxi

de layer after removing said nitride layer and said first oxide layer of the gat

e regions of said first and second MOS transistors;

forming contact windows to the source and drain of said first and second MOS tra

nsistors;

forming a pattern of a first metal layer to form electrodes of said first and se

cond MOS transistors; and

forming a pattern of low temperature oxide layer over said first metal layer.

7. A process as claimed in claim 6, further comprising the steps for concurrentl

y removing the nitride layer over the edge region of said second conductivity ty

pe well region, a region to form said first MOS transistor on said well region,

a region to form said second transistor on said substrate, and the stop-channel

region to be formed around said second MOS transistor region, after said step of

forming successively the first oxide and the nitride layer over said substrate,

and then forming said field oxide layer layer in the regions exposed by removin

g the nitride layers said nitride layer.

8. A process as claimed in claim 7, further comprised of forming said second con

ductivity type well by implanting second conductivity type ions in a dose of 2101

5 -31015 ions/cm2 with an energy of 40-50 KeV, and thereon heat-treating for the

junction depth to reach 5-6 m.

9. A process as claimed in claim 7, wherein the drain and source of said first M

OS transistor, and said stop-channel region are formed by ion-implanting phospho

rus and arsenic ions, which is thereupon heat-treating for a predetermined junct

ion depth.

10. A process as claimed in claim 7, wherein the drain and source of said second

MOS transistor, and said ohmic contact region of said well edge are formed by i

mplanting first conductivity N-type ions, and heat-treating for the junction dep

th to be more than that of the drain and source of said first MOS transistor.

Description:

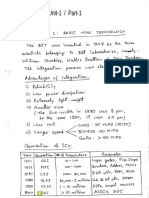

BACKGROUND OF THE INVENTION

The present invention concerns a process for fabricating a high-speed CMOS TTL (

hereinafter refered to as "HCT") semiconductor device and in particular a proces

s for adjusting the operational speed of the semiconductor device by capacitance

in the field region thereof.

Generally, the operational speed of a semiconductor device used in a logic circu

it is controlled by two factors, that are, circuit design and fabrication proces

s therein. The control of operational speed by the fabrication process can be ac

hieved by adjusting the parasitic capacitance resulting from the thickness of it

s field oxide layer. Because it becomes possible to change by adjustment of the

parasitic capacitance the time constant t of the time function which is determin

ed by the resistance component and the parasitic capacitance, the operational sp

eed of a semiconductor device can be to some extent controlled by adjusting the

thickness of the field oxide layer in the fabrication process.

FIG. 1 illustrates a conventional CMOS inverter comprising PMOS field effect tra

nsistor (PMOS) and NMOS field effect transistor (NMOS) wherein the input data Vi

are inverted to the output data Vo. Referring to FIG. 2, which is a cross-secti

onal view of field region a between NMOS and PMOS shaded by slant lines in FIG.

1, region 1 represents N-type semiconductor substrate, region 2 a P-type well re

gion to form NMOS, region 3 an ohmic contact of the P-well, region 4 a N+ region

of NMOS drain, region 5 a N+ stop-channel, region 6 P+ region of PMOS drain, re

gion 7 a field oxide layer, and region 8 a metal line for connecting the drains

of PMOS and NMOS, respectively. In such a CMOS construction, because the lower r

egion of the field oxide layer 7 is formed with a high concentration P+ region a

nd a low concentration N- region, it is difficult to adjust the capacitance of t

he field region. Hence, the prior art process generally requires two processing

sequences, one of which is, so called, an AHCT process increasing the thickness

of the field oxide layer, and the other is a HCTLS process decreasing the thickn

ess of the field oxide layer. Consequently, it makes the fabrication complicated

.

SUMMARY OF THE INVENTION

It is an object of the present invention to provide a process for fabricating a

semiconductor device whereby easy control of the thickness of field oxide layer

can be achieved through a unit processing sequence.

According to the present invention, there is provided a process for fabricating

a semiconductor device comprising the steps of forming a second conducting type

well in a predetermined region on the upper surface of a first conducting type s

ilicon semiconductor substrate, forming successively a first oxide layer and a n

itride layer on the upper surface of said substrate, forming stop-channel region

s in predetermined regions of said substrate and the drain and source of first M

OS transistor on the upper surface of said well, forming ohmic contact regions i

n the edge of said well and the drain and source of second MOS transistor betwee

n said stop-channel regions, forming an oxide layer on the whole surface of said

substrate to form a gate oxide layer after removing said nitride layer and said

first oxide layer of the gate regions of said first and second MOS transistors,

forming contact windows for contacting the source and drain of said first and s

econd MOS transistors, forming a pattern of first metal layer so as to form the

electrodes of said first and second MOS transistors, forming a pattern of a low

temperature oxide layer on said first metal layer in order to insulate it from a

predetermined portion, forming a pattern of a second metal layer connected with

first metal layer through said contact windows, said second metal layer being i

nsulated from said first metal layer by said low temperature oxide layer, and fo

rming a protection layer on said second metal layer.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a circuit diagram of a conventional CMOS inverter;

FIG. 2 is a cross-sectional view of the region of a FIG. 1; and

FIGS. 3A-3I illustrate the fabrication process according to the present inventio

n, respectively.

DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT OF THE INVENTION

Hereinafter, the present invention will be described in detail with reference to

the drawings, by way of example only. FIGS. 3A to 3I illustrate a cross-section

al view of the fabrication process according to the present invention of a CMOS

inverter. On N-silicon semiconductor substrate 10 is initially formed oxide laye

r 11 with the thickness of about 2000-3000 . In order to form a P-type well regio

n to make a NMOS, photoresist is deposited on the whole upper surface of the sub

strate 10, and by conventional photolithography, photoresist mask pattern 13 is

made to obtain window 12 over the underlying region to form the P-type well. Aft

er etching the portions of initial oxide layer 11 exposed through window 12 by t

aking photoresist mask pattern 13 as a mask, boron is ion-implanted into that po

rtions in the dose of 210 13 -310 13 ions/cm 2 with the energy of 40-50 KeV in ord

er to form P-type ion-implantation region 14, as shown in FIG. 3A, so that that

P-well can be formed. After removing the photoresist makes pattern, P-type ions

of P-type ion-implantation region 14 are re-distributed (or diffused) to form P-

well 15 by a conventional drive-in process. In this process, the junction depth

of the P-well should be 5-6 m, and on the upper surface of P-well 15 is grown an

oxide layer of about 5000-5500 .

Thereafter, initial oxide layer 11 on substrate 10, and the oxide layer grown in

the drive-in process not shown in the drawings are all removed. On the whole up

per surface of the substrate is deposited first oxide layer 16 having the thickn

ess of 150-200 , on the whole upper surface of which is deposited nitride layer 1

7 by a conventional CVD method. On the nitride layer 17 is deposited photoresist

, and by a conventional photolithography is formed mask pattern 22 as shown in F

IG. 3B, comprising P-well region 18 to form a NMOS, substrate upper region 19 to

form PMOS, P+ ohmic contact region 20 in the edge of the P-well region, and the

upper surface of N+ stop-channel region 21. After etching the portions of nitri

de layer 17 exposed through photoresist mask pattern 22, the mask pattern 22 is

removed from the substrate, and by the conventional heat treatment is grown fiel

d oxide layer 23 having the thickness of about 1100 . In this processing step, th

e thickness of field oxide layer 23 can be arbitrarily adjusted by controlling t

he diffusion heating cycle. According to the example, although the thickness of

the field oxide layer amounts to about 1100 to obtain a high-speed inverter, it

may be reduced to 700 , 500 , 300 , etc. to obtain low speed. Also, the field oxide

layer may not be grown.

On the whole upper surface of the substrate 10 is deposited photoresist, and by

the conventional photolithography is formed mask pattern 26 as shown FIG. 3C, wh

ich masks the regions except region 24 to form the drain and source of the NMOS,

and stop-channel region 25. After etching the portions of nitride layer 17 expo

sed through the mask pattern 26, into the etched portions phosphorous is ion-imp

lanted in the dose of 110 15 -310 15 ions/cm 2 with the energy of 50-60 KeV, and t

he arsenic is ion-implanted in the dose of 210 15 410 15 ions/cm with the energy o

f 70-80 KeV, thereby forming N+ ion implant regions 27 and 28.

As described above, if phosphorous and arsenic ions are successively implanted,

the junction breakdown voltage of NMOS is increased to improve the characteristi

c of NMOS.

After removing the mask pattern 26, N+ ion implantation regions 27 and 28 are ac

tivated by the conventional heat treatment to form the drain and source 29 of th

e NMOS stop-channel region 30. The junction depth of N+ region formed in this pr

ocess is about 0.5 m, and on the upper surface of N+ regions 29 and 30 is formed

oxide layer 31 of 1000 .

On the whole upper surface of the substrate is deposited photoresist to form mas

k pattern 34 by the conventional photolithography as shown in FIG. 3D, which mas

ks the regions except the region 32 to form the drain and source of PMOS, and P+

regions 33 for the ohmic contact of the P-well. Thereafter, the portions of nit

ride 17 exposed through mask pattern 34 are etched. Into the portions etched is

ion-implanted boron in the dose of 110 15 -210 15 ions/cm 2 with the energy of 30-

50 KeV so as to form P+ ion implantation regions 35 and 36. After removing the m

ask pattern 34, P+ ion implantation regions 35 and 36 are activated to form the

drain and source 37 of PMOS, and P+ region 38 for the ohmic contact of the P-wel

l by the conventional heat treatment. The junction depth of the P+ region formed

in this processing step is about 0.7 m, and on the upper surface of P+regions 37

and 38 is formed oxide layer 39 having the thickness of 1000 as the upper surfa

ce of N+ regions 29 and 30.

After removing the remaining nitride layer 17 and the portions of first oxide la

yer 16 existing in the regions to form the gates of the MOS transistors, gate ox

ide layer 40 is grown to have the thickness of 300-400 . On the whole upper surfa

ce of the substrate is deposited photoresist to form mask pattern 43 by the conv

entional photolithography, as shown in FIG. 3E, so that the contact regions can

be formed over the drain and source regions 29 and 37 of NMOS and PMOS. Etching

the portions of the gate oxide layer exposed through the mask pattern 43 provide

s contact windows 41 and 42 over N+ region 29 and P+ region 37. Thereafter, all

of the mask pattern 43 is removed from the substrate.

On the whole upper surface of the substrate is deposited a first metal layer by

conventional metallization deposition, on which metal layer is deposited photore

sist 45 to pattern the electrodes. After metal electrodes 44a, 44b, 44c, 44d, ar

e formed as shown in FIG. 3F by the conventional lithography, the remaining phot

oresist mask pattern 45 is removed from the substrate. Because the semiconductor

device shown in the drawings is a CMOS inverter, the electrode 44c is formed by

interconnection of the drain electrode of NMOS and the electrode of PMOS.

Thereafter, on the upper surface of the substrate is deposited low temperature o

xide layer 46, on the whole upper surface of which is deposited photoresist 47 t

o connect first and second metal layers, and the pattern of low temperature oxid

e layer 46 is made by the conventional photolithography, as shown in FIG. 3G. Th

en, the mask pattern 47 is removed from the substrate. Subsequently, on the whol

e upper surface of the substrate is deposited second metal layer 48 to connect w

ith first metal layer 44 by conventional metallization. Photoresist 49 is deposi

ted on second metal layer 48, which is patterned as shown in FIG. 3H by the conv

entional photolithography. After the mask pattern 49 is wholly removed from the

substrate, protection layer 50 is formed on the substrate, as shown in FIG. 3I,

to obtain the passivation of the semiconductor device.

As described above, the present invention facilities adjusting the capacitance o

f the field oxide layer, and therefore converts into an unity fabrication proces

s the conventional fabrication process using the duplicate steps. Consequently,

the operational speed of a semiconductor device can readily be adjusted accordin

g to the present invention. Further, the present invention may be employed in fa

bricating all the semiconductor devices used for a logic circuit.

While the invention has been particularly shown and described with reference to

a preferred embodiment, it will be understood by those skilled in the art that m

odifications in detail may be made without departing from the spirit and scope o

f the invention.

Potrebbero piacerti anche

- Lab Report VLSIDocumento24 pagineLab Report VLSIK Eerti Vyas0% (2)

- Power Semiconductor Applications - Philips-NXPDocumento609 paginePower Semiconductor Applications - Philips-NXPnanditonanaman100% (2)

- VLSI DesignDocumento301 pagineVLSI Designyucl_9879280% (5)

- (Razavi) Design of Analog Cmos Integrated CircuitsDocumento21 pagine(Razavi) Design of Analog Cmos Integrated CircuitsNiveditha Nivi100% (1)

- Complementary MetalDocumento5 pagineComplementary MetalesaidanNessuna valutazione finora

- Making TransistorsDocumento23 pagineMaking TransistorsRANGAM NAGARAJUNessuna valutazione finora

- Bec010 Vlsi - NotesDocumento109 pagineBec010 Vlsi - NotesFarukh ZafarNessuna valutazione finora

- Chapter 1: Cmos Circuits - A Brief IntroductionDocumento3 pagineChapter 1: Cmos Circuits - A Brief IntroductionbhannuNessuna valutazione finora

- Fabrication of MosfetDocumento19 pagineFabrication of Mosfetnarayana89% (9)

- Unit 2Documento33 pagineUnit 2Venky VellankiNessuna valutazione finora

- Unit 1 Basic MOS Technology: Figure 1. Moore's LawDocumento18 pagineUnit 1 Basic MOS Technology: Figure 1. Moore's LawSushruth SastryNessuna valutazione finora

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDocumento190 pagineFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiNessuna valutazione finora

- Unit I Cmos Technology An MOS (Metal-Oxide-Silicon) Structure Is Created by Superimposing Several Layers of ConductingDocumento2 pagineUnit I Cmos Technology An MOS (Metal-Oxide-Silicon) Structure Is Created by Superimposing Several Layers of ConductingIshita AggarwalNessuna valutazione finora

- ASB Magazin, Jun 2011Documento5 pagineASB Magazin, Jun 2011emediageNessuna valutazione finora

- Chapter 2: Operating Principles of MOS TransistorsDocumento5 pagineChapter 2: Operating Principles of MOS TransistorsRahul GoyalNessuna valutazione finora

- CMOS Fabrication Technologies and Process Design RulesDocumento14 pagineCMOS Fabrication Technologies and Process Design RulesPrashant SinghNessuna valutazione finora

- Vlsi NotesDocumento11 pagineVlsi NotesShowcase MarathiNessuna valutazione finora

- Robert Chau ICSICT Paper 101904Documento5 pagineRobert Chau ICSICT Paper 101904yassirkelNessuna valutazione finora

- Fabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariaDocumento6 pagineFabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariajamesNessuna valutazione finora

- A Review Paper On Cmos, Soi and Finfet TechnologyDocumento18 pagineA Review Paper On Cmos, Soi and Finfet TechnologyRamakrishnaRao SoogooriNessuna valutazione finora

- Vlsi Unit-IDocumento45 pagineVlsi Unit-Isuneelanubolu7Nessuna valutazione finora

- CMOS Fabrication and Layout RulesDocumento65 pagineCMOS Fabrication and Layout Rulessasindhur r100% (2)

- Microelectronic CircuitDocumento696 pagineMicroelectronic CircuitImtiaz AhmedNessuna valutazione finora

- CMOS FabricationDocumento7 pagineCMOS FabricationSubir MaityNessuna valutazione finora

- CMOS N-Well ProcessDocumento7 pagineCMOS N-Well ProcessGregory ThompsonNessuna valutazione finora

- MosfetDocumento5 pagineMosfetKancharana SarathchandraNessuna valutazione finora

- Designing and Characterization of 60nm p-well MOSFETDocumento4 pagineDesigning and Characterization of 60nm p-well MOSFETKathleen Zipora RahuellahNessuna valutazione finora

- A Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerDocumento10 pagineA Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerRohit JangidNessuna valutazione finora

- Surface Modification by Electric Discharge Implemented With Electrodes Composed of Carbon NanotubesDocumento6 pagineSurface Modification by Electric Discharge Implemented With Electrodes Composed of Carbon NanotubesDeak Ferenc-JozsefNessuna valutazione finora

- ijcsi-2021_v10-n4-p18Documento16 pagineijcsi-2021_v10-n4-p18ERplant RefinersNessuna valutazione finora

- Microelectronic Engineering: Alexander Vladimirov GrigorovDocumento9 pagineMicroelectronic Engineering: Alexander Vladimirov Grigorov135713571357Nessuna valutazione finora

- Vlsi Final Notes Unit1Documento31 pagineVlsi Final Notes Unit1RohitParjapatNessuna valutazione finora

- Fabrication of Multilayered Co/Pd Nano-Dot Arrays with 1 Tera-Dot DensityDocumento4 pagineFabrication of Multilayered Co/Pd Nano-Dot Arrays with 1 Tera-Dot DensityJose Manuel Hermosilla AvilaNessuna valutazione finora

- MosfetDocumento20 pagineMosfetMohammad Rameez100% (2)

- Understanding About CMOS Fabrication TechnologyDocumento8 pagineUnderstanding About CMOS Fabrication TechnologyAjay Kumar MattupalliNessuna valutazione finora

- Abstract 1Documento1 paginaAbstract 1Manasa UpadhyayaNessuna valutazione finora

- Ec8095-Vlsi Design-607796847-Ec 8095 NotesDocumento163 pagineEc8095-Vlsi Design-607796847-Ec 8095 Noteshmpudur1968Nessuna valutazione finora

- The CMOS Fabrication Process & Design RulesDocumento8 pagineThe CMOS Fabrication Process & Design RulesBhupender KumawatNessuna valutazione finora

- Fabrication of TransistorsDocumento10 pagineFabrication of TransistorsDurga PrasathNessuna valutazione finora

- MOS and VLSI Technology OverviewDocumento54 pagineMOS and VLSI Technology OverviewAndrews austinNessuna valutazione finora

- (I) Cmos Processing Technology:-: (A) OxidesDocumento7 pagine(I) Cmos Processing Technology:-: (A) Oxidesmukti450Nessuna valutazione finora

- CMOS Technology for 25 nm Channel LengthDocumento20 pagineCMOS Technology for 25 nm Channel LengthtbsuirNessuna valutazione finora

- Self-Aligned, Insulating-Layer Structure For Integrated Fabrication of Organic Self-Assembled Multilayer Electronic DevicesDocumento4 pagineSelf-Aligned, Insulating-Layer Structure For Integrated Fabrication of Organic Self-Assembled Multilayer Electronic DevicesemediageNessuna valutazione finora

- STRUCTURAL PROPERTIES OF NANOCRYSTALLINE TiN FILMDocumento7 pagineSTRUCTURAL PROPERTIES OF NANOCRYSTALLINE TiN FILMInternational Journal of Structronics & MechatronicsNessuna valutazione finora

- Vrouw, Jun 2011Documento6 pagineVrouw, Jun 2011emediageNessuna valutazione finora

- Vlsi Unit1Documento32 pagineVlsi Unit1venkatNessuna valutazione finora

- VLSI Unit 2 Technology - SDocumento52 pagineVLSI Unit 2 Technology - SIndrajeet GautamNessuna valutazione finora

- GATE 2022 MT Memory-Based QuestionsDocumento2 pagineGATE 2022 MT Memory-Based QuestionsAjeeth KumarNessuna valutazione finora

- Patents: Publication NumberDocumento14 paginePatents: Publication NumberAnkit GargNessuna valutazione finora

- Structure and Operation of Four Terminal MOS Transistor: Course Name: VLSI Design Code:18B11EC315 Lecture-5Documento13 pagineStructure and Operation of Four Terminal MOS Transistor: Course Name: VLSI Design Code:18B11EC315 Lecture-5MOHAMMED FAYEZ KHANNessuna valutazione finora

- Faculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106Documento15 pagineFaculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106KarimovaRaikhanovnaNessuna valutazione finora

- Chatelaine, Apr 2011Documento5 pagineChatelaine, Apr 2011emediageNessuna valutazione finora

- 00 PRB DuplicDocumento6 pagine00 PRB DuplicDaniel LacourNessuna valutazione finora

- Low-Volt Nanometer MOSDocumento6 pagineLow-Volt Nanometer MOSShane ComptonNessuna valutazione finora

- Sensors: Modeling and Fabrication of Micro FET Pressure Sensor With CircuitsDocumento13 pagineSensors: Modeling and Fabrication of Micro FET Pressure Sensor With CircuitsDhias Pratama LazuarfyNessuna valutazione finora

- VLSI CMOS Fabrication TechnologyDocumento15 pagineVLSI CMOS Fabrication TechnologyRamanaButterflyNessuna valutazione finora

- Mos FetDocumento45 pagineMos FetbhawnaNessuna valutazione finora

- VLSI Fabrication and CharacterizationDocumento40 pagineVLSI Fabrication and CharacterizationKarthik RamasamyNessuna valutazione finora

- Hans Cmos Vlsi Punith Gowda M BDocumento127 pagineHans Cmos Vlsi Punith Gowda M BPunith Gowda M BNessuna valutazione finora

- Two Dimensional Electron Gas, Quantum Wells & Semiconductor SuperlatticesDocumento41 pagineTwo Dimensional Electron Gas, Quantum Wells & Semiconductor SuperlatticesChang Jae LeeNessuna valutazione finora

- ReportDocumento8 pagineReportROMANCE FantasNessuna valutazione finora

- An Essential Guide to Electronic Material Surfaces and InterfacesDa EverandAn Essential Guide to Electronic Material Surfaces and InterfacesNessuna valutazione finora

- MOS Integrated Circuit DesignDa EverandMOS Integrated Circuit DesignE. WolfendaleNessuna valutazione finora

- November Hindu Review 2014Documento9 pagineNovember Hindu Review 2014Rohit AgrawalNessuna valutazione finora

- Question No. 1: View SolutionDocumento24 pagineQuestion No. 1: View SolutionRohit AgrawalNessuna valutazione finora

- Analog Elect BasicDocumento53 pagineAnalog Elect BasicRohit AgrawalNessuna valutazione finora

- Sr. No - Name of Shop Item Purchased/ Services Used Date Amount (In Rupees)Documento1 paginaSr. No - Name of Shop Item Purchased/ Services Used Date Amount (In Rupees)Rohit AgrawalNessuna valutazione finora

- J 88 12 (Elec Science)Documento8 pagineJ 88 12 (Elec Science)akv_303Nessuna valutazione finora

- Interview Capsule Ibps Po IIIDocumento10 pagineInterview Capsule Ibps Po IIIganeshsingh1Nessuna valutazione finora

- Recruitment Engineers 2014 Detail AdDocumento9 pagineRecruitment Engineers 2014 Detail AdShaharukh NadafNessuna valutazione finora

- Delhi Metro Rail Corporation Ltd. (A Joint Venture of Govt. of India & Govt. of Delhi) Advt No: DMRC / Om / HR /ii/ 2014 From 17/12/2014 (1800 HRS)Documento6 pagineDelhi Metro Rail Corporation Ltd. (A Joint Venture of Govt. of India & Govt. of Delhi) Advt No: DMRC / Om / HR /ii/ 2014 From 17/12/2014 (1800 HRS)Rohit AgrawalNessuna valutazione finora

- Aicl Reqruitment Details 2015Documento16 pagineAicl Reqruitment Details 2015Subhasis MishraNessuna valutazione finora

- Any TaleDocumento37 pagineAny TaleRohit AgrawalNessuna valutazione finora

- GK Power Capsule For Niacl & Uiic Exam 2015: InternationalDocumento21 pagineGK Power Capsule For Niacl & Uiic Exam 2015: InternationalParveen KumarNessuna valutazione finora

- December 1Documento10 pagineDecember 1Gurjinder SinghNessuna valutazione finora

- Nov 2014Documento61 pagineNov 2014Rohit AgrawalNessuna valutazione finora

- Longevity Characteristics of LEDsDocumento4 pagineLongevity Characteristics of LEDsRohit AgrawalNessuna valutazione finora

- Delhi Metro Rail Corporation Ltd. (A Joint Venture of Govt. of India & Govt. of Delhi) Advt No: DMRC / Om / HR /ii/ 2014 From 17/12/2014 (1800 HRS)Documento6 pagineDelhi Metro Rail Corporation Ltd. (A Joint Venture of Govt. of India & Govt. of Delhi) Advt No: DMRC / Om / HR /ii/ 2014 From 17/12/2014 (1800 HRS)Rohit AgrawalNessuna valutazione finora

- PLC Programmable Logic ControllerDocumento11 paginePLC Programmable Logic ControllerRohit AgrawalNessuna valutazione finora

- Youtube Download Replacem. With SsDocumento1 paginaYoutube Download Replacem. With SsRohit AgrawalNessuna valutazione finora

- HEX Code DetailsDocumento2 pagineHEX Code DetailsRohit AgrawalNessuna valutazione finora

- Some Good ProblemsDocumento1 paginaSome Good ProblemsHemanth VasudevanNessuna valutazione finora

- New Text DocumentDocumento8 pagineNew Text DocumentRohit AgrawalNessuna valutazione finora

- New Text DocumentDocumento1 paginaNew Text DocumentRohit AgrawalNessuna valutazione finora

- Line Follower With 4 Sensor01Documento1 paginaLine Follower With 4 Sensor01Rohit AgrawalNessuna valutazione finora

- Answers Screening RoundDocumento1 paginaAnswers Screening RoundRohit AgrawalNessuna valutazione finora

- Delay OscDocumento2 pagineDelay OscRohit AgrawalNessuna valutazione finora

- Program To Make A Code Lock With User Defined PasswordDocumento18 pagineProgram To Make A Code Lock With User Defined PasswordVasundhra AgarwalNessuna valutazione finora

- Mobile No Full Name Stream City GF Roll No Test ID Status Q1Documento5 pagineMobile No Full Name Stream City GF Roll No Test ID Status Q1vivekrahalkarNessuna valutazione finora

- DescriptionDocumento1 paginaDescriptionRohit AgrawalNessuna valutazione finora

- FAQs MHA RecruitmentDocumento6 pagineFAQs MHA RecruitmentRohit AgrawalNessuna valutazione finora

- MedicalDocumento2 pagineMedicalRohit AgrawalNessuna valutazione finora

- GATE2014 NotificationDocumento1 paginaGATE2014 Notificationajays2539Nessuna valutazione finora

- 70 72Documento3 pagine70 72mmmkNessuna valutazione finora

- 2 SK 2651Documento2 pagine2 SK 2651Maria ReinosoNessuna valutazione finora

- Nondissipative Clamping Benefits DC-DC ConvertersDocumento5 pagineNondissipative Clamping Benefits DC-DC ConvertersMateusz LiszczykNessuna valutazione finora

- Current Controlled OscillatorDocumento4 pagineCurrent Controlled OscillatorajaynkotiNessuna valutazione finora

- Study and Verification On The Latch-Up Path Between I/O pMOS and N-Type Decoupling Capacitors in 0.18Documento7 pagineStudy and Verification On The Latch-Up Path Between I/O pMOS and N-Type Decoupling Capacitors in 0.18KEVIN CHENNessuna valutazione finora

- Basic Applied Electronics by BalamuruganDocumento73 pagineBasic Applied Electronics by BalamuruganBalamurugan Thirunavukarasu100% (2)

- MOSFET As A Switch - Using Power MOSFET SwitchingDocumento12 pagineMOSFET As A Switch - Using Power MOSFET SwitchingchristopherNessuna valutazione finora

- Kreatryx Analog Circuits PDFDocumento43 pagineKreatryx Analog Circuits PDFbharatNessuna valutazione finora

- MOSFET Current Voltage Characteristics: V V V V 0Documento5 pagineMOSFET Current Voltage Characteristics: V V V V 0sathishkumarNessuna valutazione finora

- EEE1106 Course StructureDocumento2 pagineEEE1106 Course StructureKavinesh AnanthanNessuna valutazione finora

- A 09-V Input Discontinuous-Conduction-Mode Boost CDocumento12 pagineA 09-V Input Discontinuous-Conduction-Mode Boost CDanial RazaNessuna valutazione finora

- Logic Gates: Fundamental Building Blocks of Digital CircuitsDocumento17 pagineLogic Gates: Fundamental Building Blocks of Digital CircuitsElla Canonigo CanteroNessuna valutazione finora

- Analog Ic Layout 1 1385Documento54 pagineAnalog Ic Layout 1 1385v4vktryNessuna valutazione finora

- AlGaN/GaN HEMTsDocumento44 pagineAlGaN/GaN HEMTsGagandeep Singh KalerNessuna valutazione finora

- ENG-188 Rev5Documento38 pagineENG-188 Rev5LuisBritoNessuna valutazione finora

- Integrated Circuits Lecture NotesDocumento9 pagineIntegrated Circuits Lecture NotesJoanna Fabricante100% (1)

- Electronic Devices and Circuit Theory 11th Edition Boylestad Test Bank 1Documento13 pagineElectronic Devices and Circuit Theory 11th Edition Boylestad Test Bank 1julia100% (33)

- Dynamic Range and Accurate dB-Linear: A CMOS Variable Gain Amplifier With Wide CharacteristicDocumento5 pagineDynamic Range and Accurate dB-Linear: A CMOS Variable Gain Amplifier With Wide Characteristicapi-19755952Nessuna valutazione finora

- Mech ch3Documento7 pagineMech ch3Eric HenricksonNessuna valutazione finora

- Questions & Answers On Logic FamiliesDocumento26 pagineQuestions & Answers On Logic Familieskibrom atsbha50% (2)

- B.E. Degree Exam EC141 Electronic DevicesDocumento3 pagineB.E. Degree Exam EC141 Electronic DevicesKarthik JiiNessuna valutazione finora

- Eetop - CN - iSSCC 2022 T1 Analog in BCD TutorialDocumento169 pagineEetop - CN - iSSCC 2022 T1 Analog in BCD Tutoriallw1244561533Nessuna valutazione finora

- Online Test Feedback and InterviewsDocumento9 pagineOnline Test Feedback and InterviewsWINORLOSENessuna valutazione finora

- Electrical Characteristics of MOS Devices: V + "Metal" Oxide V +Documento36 pagineElectrical Characteristics of MOS Devices: V + "Metal" Oxide V +mohandossNessuna valutazione finora

- N Mosfet: Shenzhen Tuofeng Semiconductor Technology Co., LTDDocumento2 pagineN Mosfet: Shenzhen Tuofeng Semiconductor Technology Co., LTDJUANNessuna valutazione finora

- Introduction To CMOS VLSI Design: Credits: David HarrisDocumento62 pagineIntroduction To CMOS VLSI Design: Credits: David HarrisYashNessuna valutazione finora

- 65-nm CMOS TECHNOLOGYDocumento32 pagine65-nm CMOS TECHNOLOGYsumithmhNessuna valutazione finora