Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Short Circuit Studies in Transmission Networks

Caricato da

luhusapaDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Short Circuit Studies in Transmission Networks

Caricato da

luhusapaCopyright:

Formati disponibili

1

AbstractAccuracy of short circuit analysis depends on the

fault modelling. This paper addresses the implementation of a

new fault model consisted of a serial connection of the tower

footing resistance and arc resistance. In existing approaches

the value of the arc resistance at the fault location must be

known in advance, or it is totally neglected from the

consideration. The fault current and arc resistance are

mutually dependent, so the short circuit analysis cannot be

performed directly. A new solution for this problem is the use

of an iterative procedure, calculating fault current and arc

resistance iteratively. The new method presented in this paper

calculates short circuit currents and arc resistance

simultaneously. Results of fault analysis and arc resistance

calculation in two test network are presented and discussed in

the paper.

Index TermsTransmission networks, short circuit analysis,

fault modelling, arc resistance, iterative procedures.

I. INTRODUCTION

HORT circuit studies in transmission and distribution

networks is a standard step in planning of modern power

grids. Based on such studies, switchgear components are

constructed, manufactured and installed, protective device

co-ordination is being carried out etc. Fault current

calculation is provided in such a way, that the fault is

modelled either as a pure metallic fault, or as a lumped

resistance, modelling fault resistance. At the fault point on

the line, both the tower footing and the arc resistance must

be included into the calculation. Statistically, arcing faults

occur in over 80 % of all faults, so consideration of the arc

resistance in short circuit studies is essential. In Fig. 1, a

photograph of a real arcing fault on an overhead line is

presented.

Since the fault current depends on arc resistance, which is

itself, a non-linear function of the fault current, the

fundamental question here is how to calculate the unknown

arc resistance and fault current at the fault location

simultaneously and accurately.

By assuming a constant value for arc resistance, selected

from the experience, or handbooks (e.g. 1.5 ), or simply by

neglecting it, the problem is directly solvable. The currents

obtained in this case are larger than those obtained when the

arc resistance is included in the calculation procedure. It is

V. Terzija is with the School of Electrical and Electronic Engineering,

The University of Manchester, UK (e-mail: terzija@ieee.org).

Dj.Dobrijevic is with the Electricity Coordinating Center (EKC),

Belgrade, Serbia (e-mail: djolence@ieee.org)

obvious that the value of arc resistance determines the fault

current value. Thus, the selection of arc resistance is critical

from the accuracy of short circuit analysis point of view.

A solution for the above mentioned problem, which uses

an iterative procedure, is presented and thoroughly tested in

this paper. By this, a new iterative procedure for short

circuit current calculation in transmission networks, based

on an existing short circuit method and a new formula for

arc resistance, is developed and implemented. The iterative

procedure is the key point of the methodology proposed and

an efficient approach for solving the problem of the non-

linear relationship between the arc resistance and the fault

current. Compared to the existing methods in which the

phenomenon of arc resistance has been totally neglected, or

solved by assuming an arbitrary constant arc resistance

value, the new method offers a more accurate short circuit

analysis in transmission networks.

Fig. 1: Three-phase arcing fault on an overhead line.

Results of fault analysis and arc resistance calculation in

two test networks are presented and discussed in the paper.

The calculation errors, as a consequence of neglecting the

arc from the consideration are analyzed and discussed, too.

II. SHORT CIRCUIT METHOD

The short circuit analysis is performed in this paper by using

the existing software package developed according to the

well known methodology described in [1]. This method can

be applied for solving short circuit faults of any conceivable

complexity. The method assumed the use of lumped

parameters of power system elements. By this, classical

approaches for fault modelling are used:

Short Circuit Studies in Transmission Networks

Using Improved Fault Model

Vladimir V. Terzija, Senior Member, IEEE, Djordje M. Dobrijevic, Senior Member, IEEE

S

2

a) Metallic fault modelling (fault resistance equal to

zero).

b) Fault modelled as a pure resistance, in advance

arbitrary selected.

Obviously, real faults are neither pure metallic faults, nor

faults over in advance known resistance. Real faults can be

represented as a series connection of two resistances: the

tower footing resistance and the arc resistance. As it is

known, the arc resistance depends on arc current, so it is not

possible to set this value in advance. The solution is to use

realistic arc resistance models depending on arc/fault

current. By combining the fault current calculation and by

simultaneously determining the arc resistance, a much more

accurate method for short circuit analysis can be designed.

Based on the above discussion, the following fault model

can be assumed:

Fig. 2: Fault model including tower footing resistance RF and arc resistance

Ra.

Obviously, the arc resistance depends on arc current, so an

iterative algorithm for short circuit analysis can be the

solution for achieving the better calculation accuracy.

In the next Section the arc resistance formula used in the

short circuit method developed in this paper will be

presented.

III. ARC RESISTANCE FORMULA

Based on experimental testing in a high power test

laboratory and exhaustive analysis and processing of

digitized arc voltage and current signals, the following new

formula for arc resistance calculation is derived [2]:

I

L E

R

a

2 2

= (1)

where R is the arc resistance in [], L is the arc length in

[m], I is the arc current in [A], and E

a

is the arc voltage

gradient in [V/m]. The open literature [3, 4] offers the

following expressions for E

a

calculation:

( ) 1500 1200 =

a

E (V/m) (2)

I E

a

/ 5000 950+ = (V/m) (3)

Equations (2) and (3) can be included in (1), so the

following two equations for arc resistance can be obtained:

( )

I

L

R 5 . 1350 4 . 1080

1

= (4)

L

I I

R

+ =

2

2

6 . 4501 3 . 855

(5)

In this paper the equation (4) for arc resistance calculation is

used. It can be noticed that the arc resistance is a nonlinear

function of arc/fault current. In addition it depends on arc

length and suitable parameters originated from expressions

for arc voltage gradient.

IV. ITERATIVE PROCEDURE FOR SHORT CIRCUIT ANALYSIS

AND ARC RESISTANCE CALCULATION

From equations (4) and (5) it follows that fault currents

depend on arc resistance, which is a non-linear function of

fault current. The problem to be solved is how to calculate

the arc resistance and the fault current simultaneously and

accurately.

In this paper a new method for calculating short circuit

currents in transmission networks, based on an existing

short circuit method and a new formula for arc resistance, is

presented. An iterative procedure is the key point of the

methodology proposed and an efficient approach for solving

the problem of the non-linear relationship between the arc

resistance and the fault current. Through the iterative

procedure the new method calculates short circuit currents

and arc resistance simultaneously.

The proposed iterative procedure for fault currents and

arc resistance calculation can be presented through the

following iteration steps (here k is an iteration index):

1. Set the start value of arc resistance, R

a

(k =1)=0;

2. Calculate the fault current, I

f

(k =1), by using the

existing short circuit method and the arc resistance at

the fault location assumed in the k-th step;

3. Increment the iteration index: k =k +1;

4. Calculate the arc resistance R

a

(k) using equation (4)

and the fault current at the fault location calculated in

the previous step;

5. Calculate the new fault current, I

f

(k), using the updated

impedance matrix, Z

t

, which includes the arc resistance

R

a

(k) at the fault location;

6. Test the accuracy criterion, if |R

a

(k) - R

a

(k-1)| >

(=0.0001), then go to step 3, else stop the procedure

and print results.

In Fig. 3 the flowchart with steps 1-6 is presented.

R

F

fault point

R

a

=f(I)

3

Yes |R

a

(k) - R

a

(k-1)| >

(=0.0001) ?

Initialization

1.Set starting iteration index:

k =1

2. Set the start value of arc

resistance: R

a

(k =1)=0

Calculate the fault current

I

f

(k =1)

Increment the iteration index

k =k +1

Calculate the arc resistance

R

a

(k)

Calculate the new fault current

I

f

(k)

Stop calculation

Print results

No

Fig. 3: Flowchart of the new iterative algorithmfor short circuit analysis.

V. ALGORITHM TESTING

The algorithm presented is tested using two test networks.

The first network is a simple two node test network. Using

this network, the key idea and approach of providing short

circuit studies using iterative algorithm presented in this

paper are demonstrated.

In the second case, the new method is applied on a

realistic mashed network including three generators.

A. Two Nodes Network Demonstration Example

The proposed methodology for simultaneous calculation

of short circuit currents and arc resistance is firstly applied

on a very simple two node test network presented in Fig. 4.

In this network it is assumed that the faulty line is

connecting two active networks (networks including

generators).

Using iterative procedure described in Section IV,

currents I

1

and I

2

, as well as the unknown arc resistance R

a

,

are determined. Since the tower footing resistance R

F

is a

fault parameter which does not depend on fault current, it

4

was not included in the analysis. In all simulations it is

assumed that in equation (4) the arc length is L =1 m and

that it has a constant value.

Fig. 4: Single line diagramof the simple test network.

Firstly, a fault at the middle of the line is analysed. In

Figs. 5 and 6 the calculated fault currents I

1

and I

2

and arc

resistance, are respectively presented. Obviously, at the very

beginning, when the arc resistance is zero, fault currents are

larger than those obtained after several iterations, when arc

resistance becomes larger values. From Fig. 4 it can be also

concluded that for the case of a metallic fault (arc resistance

equal to zero) the calculated fault currents are essentially

larger than those obtained when arc resistance has been

taken into account. On the other hand, if assuming a certain

arc resistance, e.g. from handbooks, it is arguable which

results will be obtained. The approach presented has the

advantage that the arc resistance directly depends on the

corresponding arc current. This correlates to the physical

processes existing in the reality.

iteration step

0 4 8 12 16 20

I

(

A

)

8000

12000

16000

20000

24000

28000

I

a

=I

1

+I

2

I

1

I

2

Fig. 5: Short circuit currents (fault at the middle of the line).

iteration step

0 4 8 12 16 20

R

a

(

)

0.420

0.440

0.460

0.480

0.500

0.520

0.540

0.560

0.580

0.600

Fig. 6: Arc resistance (fault at the middle of the line).

In the next test example, a fault at 10% line distance

observed from the left line terminal A is considered. Results

for this case are presented in Figs. 7 and 8. As expected,

larger fault currents and smaller values for arc resistance are

obtained.

iteration step

0 4 8 12 16 20

I

(

A

)

0

10000

20000

30000

40000

50000

60000

70000

80000

I

a

=I

1

+I

2

I

1

I

2

Fig. 7: Short circuit currents (at 10% line distance observed fromthe left

line terminal A).

iteration step

0 4 8 12 16 20

R

a

(

)

0.000

0.050

0.100

0.150

0.200

Fig. 8: Arc resistance (at 10% line distance observed fromthe left line

terminal A).

B. Mashed Network Demonstration Example

The above simple test example demonstrated the essence

of the new short circuit method. In this test example, a

realistic network, presented in Fig. 9, is analyzed. The

configuration, in which at node 3 a generator was

connected, was considered. In Fig. 9 all network parameters

are given, as well.

Based on a large number of simulations and results

obtained, in Table I the results of fault current calculation

for the fault at node 1 are presented. Results for 3-phase and

single phase-to-ground faults are presented. It is obvious

that the subtransient, I

k

", transient, I

k

', and steady state, I

k

,

fault currents differ if arc resistance is taken into account, or

not. The corresponding arc resistance was in the range 0.16

to 0.6. For example, for the single line-to-ground fault

(steady state case), it has the value R

a

=0.55 .

Authors are currently running simulations of larger

networks, taking into account realistic scenarios and

investigating the opportunities of using the new method for

improving approaches for protection coordination. By this,

the setting of distance protection is in particular focus of the

current research.

A

B

I

1

I

2

R

a

5

VI. CONCLUSION

In this paper a new iterative method for short circuit

analysis of transmission networks, taking into account the

nonlinear arc resistance included in the fault model, is

presented. The proposed iterative method for simultaneous

calculation of arc resistance and fault currents is based on an

existing short circuit method and new expression for arc

resistance. The proposed method is successfully tested using

two test networks. In the first network, consisted of simple

two nodes, the fundamental advantages of the new iterative

algorithm are demonstrated. It is proved, that a higher

accuracy can be achieved if arc resistance is modelled

realistically. In the second test network, a more realistic case

was analysed. It is also proved that the new approach of arc

consideration in short circuit studies delivers much more

accurate results. Compared to the existing short circuit

methods, in which the phenomenon of arc resistance has

been totally neglected, or solved by assuming a suitable

constant arc resistance value, the new method considers

much more realistically the fault and gives a more accurate

solution

VII. REFERENCES

[1] Y. Brandwajn, W.F. Tinney, "Generalized Method of Fault Analysis",

IEEE Transactions on Power Apparatus and Systems, Volume PAS-

104,Issue 6, J une 1985. Page(s): 1301-1306.

[2] V.V. Terzija, H.-J . Koglin, "On the modeling of long arc in still air

and arc resistance calculation," IEEE Trans on Power Delivery, vol.

19, no. 3, J uly 2004.

[3] A.S. Maikapar, "Extinction of an open electric arc," Elektrichestvo,

Vol. 4, pp. 64-69, April 1960.

[4] Y. Goda at all, "Arc Voltage Characteristics of High Current Fault

Arcs in Long Gaps", IEEE Transactions on Power Delivery, Volume

15,Issue 2, April 2000 Page(s):791-795.

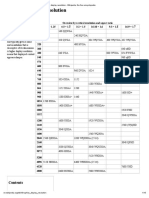

Table I: Fault at Node 1

Mashed Network 3-phase fault Single phase-to-ground fault

Fault at Node 1 Ik"(kA) Ik'(kA) Ik(kA) Ik"(kA) Ik'(kA) Ik(kA)

Ra =0 6.814 6.464 1.952 6.912 6.788 3.754

Ra =equation (4) 6.261 5.963 1.802 6.243 6.133 3.409

NODE 3 NODE 3

~ ~

~

GEN 1 GEN 2

GEN 3

NODE 1

NODE 2

NODE 3

LOAD 3

TERC 3

BT 1 BT 2

BT 3:

T3

a) b)

LINE 1

LINE 2 LINE 3

X"= 23%

X'= 30%

X = 100%

Vn= 15.75 kV

Sn= 115 MVA

X = 254%

Sn= 1455 MVA

Vn= 21 kV

X'= 28%

X"= 24%

X = 110%

Sn= 1140 MVA

Vn= 15.75 kV

X'= 28%

X"= 27%

400 kV, 98.7 km

Z = (2.9+j33.7)

Z0 = (27.5+j89.6)

Uk12 = (0.2+j12.2)%

Uk13 = (0.2+j14)%

Uk23 = (0.2+j9.3)%

m = 400/115/31.5 kV

Sn1 = Sn2 = 600 MVA

Sn3 = 200 MVA

m = 420/15.75 kV

Sn = 115 MVA

Uk = (0+j12.5)%

400 kV, 42.7 km

Z = (1.26+j14.56)

Z0 = (10.67+j43.68)

400 kV, 82.9 km

Z = (2.44+j28.27)

Z0 = (23.51+j77.43)

m = 410/21 kV

Sn = 1450 MVA

Uk = (0+j12.6)%

m = 420/15.75 kV

Sn = 1190 MVA

Uk = (0+j12)%

Fig. 9: Three generators test network.

6

VIII. BIOGRAPHIES

Vladimir Terzija (M95, SM00) is the EPSRC Chair

Professor in Power SystemEngineering in the School of

Electrical and Electronic Engineering, The University of

Manchester, where he has been since 2006. From1997 to

1999, he was an Assistant Professor at the University of

Belgrade. In 1999, he was Humboldt Research Fellow at

Saarland University. From2000 to 2006, he was with

ABB AG, Germany, as an expert for switchgears and

distribution automation. His main research interests are

application of intelligent methods to power systemmonitoring, control, and

protection, as well as switchgears, and DSP applications in power systems.

Djordje Dobrijevic (M'99, SM'02) graduated fromthe

University of Belgrade in 1992. After the graduation he

joined in The Institute of Electrical Engineering "Nikola

Tesla" Belgrade. Since 2004 he is with the Electricity

Coordinating Center (EKC), Belgrade. His major

research interests include power system analysis,

stability, control, dynamics and security, hydroelectric

power plants modelling, short circuit analysis, digital

and adaptive control and software development. At present time he is

postgraduate student at Belgrade University.

Potrebbero piacerti anche

- CrispprXV5 Fuse Blowing of Potential TransformersDocumento8 pagineCrispprXV5 Fuse Blowing of Potential TransformersluhusapaNessuna valutazione finora

- Combining The Best of Both Worlds Electrical SecurityDocumento6 pagineCombining The Best of Both Worlds Electrical SecurityluhusapaNessuna valutazione finora

- A Detecting Method For Active-Reactive - Negative-Sequence Powers and Its ApplicationDocumento8 pagineA Detecting Method For Active-Reactive - Negative-Sequence Powers and Its ApplicationJandfor Tansfg ErrottNessuna valutazione finora

- Transmission of Power - Polyphase System - Tesla Patents PDFDocumento263 pagineTransmission of Power - Polyphase System - Tesla Patents PDFtedineteNessuna valutazione finora

- Pitfalls of Fusing Power TransformersDocumento16 paginePitfalls of Fusing Power TransformersluhusapaNessuna valutazione finora

- A Digital Distance Relay Using Negative Sequence CurrentDocumento6 pagineA Digital Distance Relay Using Negative Sequence CurrentAlif Maulana FirdausNessuna valutazione finora

- 1ada6b ABB BR 33 ABBTEC SistMonitoracaoDocumento25 pagine1ada6b ABB BR 33 ABBTEC SistMonitoracaoluhusapaNessuna valutazione finora

- ABB HV Shunt ReactorDocumento30 pagineABB HV Shunt Reactortkdrt2166100% (1)

- Negative-Sequence Relay Protection For Blown High-Side Transformer Fuse DetectionDocumento7 pagineNegative-Sequence Relay Protection For Blown High-Side Transformer Fuse DetectionluhusapaNessuna valutazione finora

- Paper Mill Generator ProtectionDocumento11 paginePaper Mill Generator ProtectionluhusapaNessuna valutazione finora

- Stator Winding Protection of Synchronous GeneratorsDocumento11 pagineStator Winding Protection of Synchronous GeneratorsluhusapaNessuna valutazione finora

- Neutral Point Treatment and Earth Fault SuppressionDocumento6 pagineNeutral Point Treatment and Earth Fault SuppressionluhusapaNessuna valutazione finora

- Today's Large Generators Design, Performance and OperationDocumento10 pagineToday's Large Generators Design, Performance and OperationluhusapaNessuna valutazione finora

- Active - Reactive PDFDocumento0 pagineActive - Reactive PDFDinesh PanchalNessuna valutazione finora

- Considerations For Generator Ground-Fault Protection in Midsize Cogeneration PlantsDocumento7 pagineConsiderations For Generator Ground-Fault Protection in Midsize Cogeneration PlantsluhusapaNessuna valutazione finora

- Protective Device Coordination - Ideal and Practical PDFDocumento14 pagineProtective Device Coordination - Ideal and Practical PDFluhusapaNessuna valutazione finora

- Multi RelayDocumento27 pagineMulti RelaynitinpeNessuna valutazione finora

- 12 Synchronous Generator OperationDocumento5 pagine12 Synchronous Generator OperationluhusapaNessuna valutazione finora

- Application Aspects of Generator and Excitation System For Process PlantsDocumento10 pagineApplication Aspects of Generator and Excitation System For Process PlantsluhusapaNessuna valutazione finora

- Distance Relays During Faults and Power Swings - C. WarringtonDocumento14 pagineDistance Relays During Faults and Power Swings - C. WarringtonluhusapaNessuna valutazione finora

- Fortescue Original Paper Symmetrical ComponentsDocumento57 pagineFortescue Original Paper Symmetrical Componentsrian0201Nessuna valutazione finora

- Impedances Seen by Relays During Power Swings - E. ClarkeDocumento14 pagineImpedances Seen by Relays During Power Swings - E. ClarkeluhusapaNessuna valutazione finora

- Teleprotection Equipment NSD570: Utility CommunicationsDocumento8 pagineTeleprotection Equipment NSD570: Utility Communicationsadvar2314Nessuna valutazione finora

- IEEEPESTransformerProtection PDFDocumento43 pagineIEEEPESTransformerProtection PDFluhusapaNessuna valutazione finora

- 2000 Ga Tech PaperDocumento24 pagine2000 Ga Tech PaperAceel FitchNessuna valutazione finora

- 2000 Ga Tech PaperDocumento24 pagine2000 Ga Tech PaperAceel FitchNessuna valutazione finora

- An Investigation of Shaft Current in A Large Sleeve Bearing InducDocumento360 pagineAn Investigation of Shaft Current in A Large Sleeve Bearing InducluhusapaNessuna valutazione finora

- Teleprotection Equipment NSD570: Utility CommunicationsDocumento8 pagineTeleprotection Equipment NSD570: Utility Communicationsadvar2314Nessuna valutazione finora

- NEMA ABP 1 Selective CoordinationDocumento47 pagineNEMA ABP 1 Selective CoordinationMohammed Shareef ShaikhNessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (121)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- High Performance HTP eDocumento14 pagineHigh Performance HTP ejohnny_cashedNessuna valutazione finora

- Free Convection (Formulae & Problems)Documento15 pagineFree Convection (Formulae & Problems)ananth2012Nessuna valutazione finora

- IEC 60364-1 Electrical Installations in Buildings PDFDocumento80 pagineIEC 60364-1 Electrical Installations in Buildings PDFMarin PopescuNessuna valutazione finora

- Cii Sohrabji Godrej Green Business Center - SUSTAINABLE ARCHITECTUREDocumento23 pagineCii Sohrabji Godrej Green Business Center - SUSTAINABLE ARCHITECTUREBryson Solomon50% (2)

- DominosDocumento11 pagineDominosApril MartinezNessuna valutazione finora

- Pressure-Controlled Pumps CascadeDocumento2 paginePressure-Controlled Pumps Cascadecc_bauNessuna valutazione finora

- d350 Taper Lock End Anchor Tech Data SheetDocumento2 pagined350 Taper Lock End Anchor Tech Data SheetEdsantadNessuna valutazione finora

- Fallout New OrleansDocumento44 pagineFallout New Orleansender000Nessuna valutazione finora

- CatalogDocumento42 pagineCatalogOnerom LeuhanNessuna valutazione finora

- Attempt 1 OrgDocumento19 pagineAttempt 1 OrgMohammed Irfan SheriffNessuna valutazione finora

- Acoples Hidraulicos Serie 60 ParkerDocumento2 pagineAcoples Hidraulicos Serie 60 ParkerAntonio MoralesNessuna valutazione finora

- NNH4-65C-R6-V2: Electrical SpecificationsDocumento4 pagineNNH4-65C-R6-V2: Electrical SpecificationsAntony López GálvezNessuna valutazione finora

- HGU User ManualDocumento72 pagineHGU User Manuallomayani100% (1)

- 1 Calibrating The Venturi Meter and Orifice MeterDocumento5 pagine1 Calibrating The Venturi Meter and Orifice MeterRaghavanNessuna valutazione finora

- 9500MPR - MEF8 Circuit Emulation ServicesDocumento5 pagine9500MPR - MEF8 Circuit Emulation ServicesedderjpNessuna valutazione finora

- Service Pack 2Documento149 pagineService Pack 2billwong169Nessuna valutazione finora

- (EngineeringEBookspdf) Failure Investigation of Bolier PDFDocumento448 pagine(EngineeringEBookspdf) Failure Investigation of Bolier PDFcarlos83% (6)

- The Essentials of Directional Protection and SelectivityDocumento27 pagineThe Essentials of Directional Protection and SelectivityMarcus Figueroa100% (1)

- Relationship Between Organisations and Information SystemsDocumento16 pagineRelationship Between Organisations and Information SystemsJoan KuriaNessuna valutazione finora

- PROSIS Part Information: Date: Image Id: Catalogue: ModelDocumento2 paginePROSIS Part Information: Date: Image Id: Catalogue: ModelAMIT SINGHNessuna valutazione finora

- Solucionario Statistics For Business and Economics - David R. Anderson, Dennis J. Sweeney - 8edDocumento8 pagineSolucionario Statistics For Business and Economics - David R. Anderson, Dennis J. Sweeney - 8edTukumaneriko Filiponditoniko0% (1)

- TCE BE EEE RulesandRegulationsDocumento509 pagineTCE BE EEE RulesandRegulationsAplieNessuna valutazione finora

- RFQ - Tank DemuckingDocumento12 pagineRFQ - Tank Demuckingmuhamadrafie1975100% (1)

- The Impact of Greed On Academic Medicine and Patient CareDocumento5 pagineThe Impact of Greed On Academic Medicine and Patient CareBhawana Prashant AgrawalNessuna valutazione finora

- Inv INDIGO 22.11.2021 + TRDocumento1 paginaInv INDIGO 22.11.2021 + TRJunis MamedovNessuna valutazione finora

- Graphics Display Resolution - Wikipedia, The Free EncyclopediaDocumento15 pagineGraphics Display Resolution - Wikipedia, The Free EncyclopediaKarun KumarNessuna valutazione finora

- White BoxDocumento9 pagineWhite BoxAmitsonu222Nessuna valutazione finora

- Gas Plant Improves C3 Recovery With Lean Six Sigma ApproachDocumento9 pagineGas Plant Improves C3 Recovery With Lean Six Sigma ApproachganeshdhageNessuna valutazione finora

- Different Types of Steering Systems + ExamplesDocumento0 pagineDifferent Types of Steering Systems + ExamplesAbhilash NagavarapuNessuna valutazione finora