Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Merge

Caricato da

firststudentDescrizione originale:

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Merge

Caricato da

firststudentCopyright:

Formati disponibili

EECS 247 Lecture 1: Overview 2002 B.

Boser 1

A/D

DSP

EECS 247

Analog-Digital Interface

Integrated Circuits

2002

Bernhard E. Boser

Department of Electrical Engineering

and Computer Sciences

EECS 247 Lecture 1: Overview 2002 B. Boser 2

A/D

DSP

Administrative

Course web page:

http://www.eecs.berkeley.edu/~boser

(link to EECS 247)

Overview

Scope of course

Reference texts

Grade and homework policy

Office hours

Tuesday 2 to 3pm

Friday 11am to noon

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 3

A/D

DSP

Acknowledgement

Introduction to System Design and Modeling

course, developed by Eric Swanson

Notes from Prof. Gray for an earlier version of

this course

Countless books and articles

EECS 247 Lecture 1: Overview 2002 B. Boser 4

A/D

DSP

Analog-Digital Interface Circuits

Anatomy of analog processor

analog pre/post processing

A/D and D/A converters

digital signal processor

Analog

Postprocessing

D/A

Conversion

DSP

A/D

Conversion

Analog

Preprocessing

Analog Input

Analog Output

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 5

A/D

DSP

Why Digital Processing?

Digital circuitry:

Cost/function decreases by 29% each year

Thats 30X in 10 years

Analog circuitry:

Cost/function is constant

Dropping supply voltages threaten feasibility

Transition to DSP is inevitable!

Ref: International Technology Roadmap for Semiconductors,

http://public.itrs.net

EECS 247 Lecture 1: Overview 2002 B. Boser 6

A/D

DSP

Why Analog Processing?

The real or physical world is analog

Examples:

Digital Audio

RF receiver

Wireline communications

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 7

A/D

DSP

Example: Digital Audio

Goal

Lossless archival and transmission

of audio signals

Circuit functions:

Preprocessing

Amplification

Anti-alias filtering

A/D Conversion

>16Bits, >41kHz

DSP

Storage

Processing (e.g. recognition)

D/A Conversion

Postprocessing

Smoothing

Amplification

Analog

Postprocessing

D/A

Conversion

DSP

A/D

Conversion

Analog

Preprocessing

Analog Input

Analog Output

EECS 247 Lecture 1: Overview 2002 B. Boser 8

A/D

DSP

Example: RF Receiver

Goals

Wireless communication

Minimizing use of bandwidth

Immunity to interference

Circuit functions:

Preprocessing

Filtering

Amplification

Frequency translation

A/D Conversion

DSP

Demodulation

Decoding

D/A Conversion

Postprocessing

Smooting

Amplification

Analog

Postprocessing

D/A

Conversion

DSP

A/D

Conversion

Analog

Preprocessing

Analog Input

Analog Output

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 9

A/D

DSP

Example: Modem

Goals

Transmit data over inexpensive, noisy channel

Maximize distance, minimize errors

Circuit functions

Transmit DSP

Bandwidth efficient and error tolerant data encoding

Transmitter

Pulse shaping (minimize ISI)

Line driver

Noisy Channel

Frequency (and time) dependent attenuation

Noise

Receiver

Equalization

Clock recovery, slicing

Receive DSP

Decode data

Receive DSP

Receiver

Noisy

Channel

Transmitter

Transmit DSP

Digital

Clock and Data in

Digital

Clock and Data out

EECS 247 Lecture 1: Overview 2002 B. Boser 10

A/D

DSP

Signal Processing Fundamentals

EECS 247

Filtering

Data Conversion

Data detection, timing recovery

EECS 142, 242

RF amplification, mixing

Oscillators

Nonlinear circuits

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 11

A/D

DSP

System Modeling

Top-down design

Abstraction

Key for dealing with complexity (> 10

6

transistors)

Each level establishes requirements for next level down in

the hierarchy

Challenges

Unrealizable blocks

Physical constraints

Modeling errors

Number and complexity of blocks

Verification

EECS 247 Lecture 1: Overview 2002 B. Boser 12

A/D

DSP

Challenge of IC Fabrication

No other EE discipline is less forgiving of errors

You can change PLDs or software in a day

You can build and test a printed circuit board in a week

It takes months to tape out and fabricate a chip

Debugging and characterizing a (defective) chip also takes

months

State-of-the-art chips are never perfect

But they have to be good enough for someone to buy them

If you want to sell bugs, try a career in software

(quote from Eric Swanson)

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 1: Overview 2002 B. Boser 13

A/D

DSP

Modeling Tools

This is not a tool-centric course

Knowledge of design fundamentals lives through many

generations of tools

Behavioral modeling tools are not always effective:

long learning curve

Tools we will use

MATLAB / Simulink (student version is adequate)

SPICE

MathCAD, Excel,

EECS 247 Lecture 1: Overview 2002 B. Boser 14

A/D

DSP

EECS 247 versus 240

EECS 247

Macro-models, behavioral simulation, large systems

Signal processing fundamentals

High level of abstraction:

physical constraints (e.g. finite gain, supply, noise) added where

appropriate

Matlab

EECS 240

Transistor level, building blocks

Device and circuit fundamentals

Little abstraction

SPICE

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

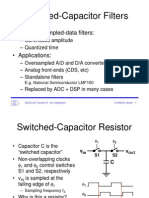

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 1

A/D

DSP

Introduction to Filters

Filtering = frequency-selective signal processing

Its the most common type of signal processing

Examples:

Extract desired signal from many (radio)

Separating signal and noise

Amplifier bandwidth limitations

Where to start

Perfectionist: ideal (low-pass) filter

Engineer: continuous time, first-order low-pass filter

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 2

A/D

DSP

First-Order RC Filter (LPF1)

Steady-state frequency response:

kHz

RC

s

s V

s V

s H

o

o

in

out

100 2

1

with

1

1

) (

) (

) (

= =

+

= =

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 3

A/D

DSP

Poles and Zeros

s-plane (pzmap):

=

+

=

z

p

s

s H

o

o

: Zero

: Pole

1

1

) (

j

p=-

o

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 4

A/D

DSP

Magnitude Response

- 5

0

5

x 10

5

-5

0

5

x 10

5

0

0.5

1

1.5

2

2.5

3

Frequency [Hz]

Magnitude Response (s-plane)

Sigma [Hz]

M

a

g

n

i

t

u

d

e

[

l

i

n

e

a

r

]

L02_bode3_lpf1.m

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 5

A/D

DSP

Frequency Response

Asymptotes:

- 20 dB/dec rolloff

- 90 degrees phase shift per 2 decades

Matlab code (L02_bode_lpf1.m):

wo = 2*pi*100e3;

s = tf('s');

h = 1 / (1+s/wo);

bodehz(h, logspace(1, 10, 100));

Note: bodehz is same as bode, but frequency axis

is in Hz, rather than rad/s.

-120

-100

-80

-60

-40

-20

0

Bode Diagram

Frequency [Hz]

P

h

a

s

e

(

d

e

g

)

M

a

g

n

itu

d

e

(

d

B

)

10

1

10

2

10

3

10

4

10

5

10

6

10

7

10

8

10

9

10

10

-90

-60

-30

0

0 ) (

1 ) (

0

= =

= =

=

j s H

j s H

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 6

A/D

DSP

Parasitics

Can we really get 100dB attenuation at 10GHz?

Probably not

Parasitics limit the performance of analog

components

E.g.

Shunt capacitance

Feed-through capacitance

Finite inductor, capacitor Q

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 7

A/D

DSP

LPF2

( )

P

P

C C sR

sRC

s H

+ +

+

=

1

1

) (

( )

P

P

RC

z

RC C C R

p

1

: Zero

1 1

: Pole

=

+

=

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 8

A/D

DSP

Frequency Response

dB

C

C

C C

C

j H

j H

P

P

P

60

10

) (

1 ) (

3

0

=

=

+

=

=

LPF2

Frequency [Hz]

P

h

a

s

e

(

d

e

g

)

M

a

g

n

itu

d

e

(

d

B

)

-80

-70

-60

-50

-40

-30

-20

-10

0

10

2

10

3

10

4

10

5

10

6

10

7

10

8

10

9

10

10

-90

-45

0

Why not just make C larger?

Beware of other parasitics not included in this model

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 9

A/D

DSP

Continuous Time Analog

Analog passive components arent ideal

Extra real poles/zeroes result from parasitics

Parasitic effects begin to appear 50dB beyond desired

component characteristics

Common sense helps you anticipate them

Digital filters do not suffer from these effects

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 10

A/D

DSP

Second-Order LPF

Improved attenuation (compared to 1

st

order)

Complex poles (rather than multiple real ones)

Why?

Visualize 3D s-plane plot!

Biquadratic (2

nd

order) transfer function:

2

2

1

1

) (

P P P

s

Q

s

s H

+ +

=

P

Q j H

j H

j H

P

=

=

=

=

=

) (

0 ) (

1 ) (

0

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 11

A/D

DSP

Biquad Poles

( )

otherwise complex real, are poles for

4 1 1

2

s at poles has

1

1

) (

2

1

2

2

2

=

+ +

=

P

P

P

P

P P P

Q

Q

Q

s

Q

s

s H

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 12

A/D

DSP

Complex Poles

( ) 1 4 1

2

s

2

2

1

=

>

P

P

P

P

Q j

Q

Q

Distance from origin in s-plane:

( )

2

2

2

2

1 4 1

2

P

P

P

P

Q

Q

d

=

+

=

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 13

A/D

DSP

s-Plane

poles

j

P

radius =

P

2Q

- part real

P

=

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 14

A/D

DSP

LPF3

10

100 2

=

=

P

P

Q

kHz

- 2

-1

0

1

2

x 10

5

-2

-1

0

1

2

x 10

5

0

0.5

1

1.5

2

2.5

3

Frequency [Hz]

Magnitude Response (s-plane)

Sigma [Hz]

M

a

g

n

i

t

u

d

e

[

l

i

n

e

a

r

]

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 15

A/D

DSP

Bode Diagram

Frequency (rad/sec)

P

h

a

s

e

(

d

e

g

)

M

a

g

n

it

u

d

e

(

d

B

)

-200

-150

-100

-50

0

50

10

2

10

3

10

4

10

5

10

6

10

7

10

8

10

9

10

10

-180

-135

-90

-45

0

Frequency Response

-40 dB/dec

-180

o

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 16

A/D

DSP

Varying Q Magnitude

Gain at

p

:

20 log Q [dB]

10

4

10

5

10

6

-50

-40

-30

-20

-10

0

10

20

30

40

LPF3 Magnitude Response

Frequency [Hz]

M

a

g

n

it

u

d

e

[

d

B

]

Q = 0.5

Q = 10.0

Q = 100.0

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 17

A/D

DSP

Phase

Slope at

p

:

-45 Q deg/decade

10

4

10

5

10

6

-180

-160

-140

-120

-100

-80

-60

-40

-20

0

LPF3 Phase Response

Frequency [Hz]

P

h

a

s

e

[

d

e

g

r

e

e

s

]

Q = 0.5

Q = 10.0

Q = 100.0

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 18

A/D

DSP

Implementation of Biquads

Passive RC: only real poles

Terminated LC

lowest power (well its passive!)

No noise (except load and source)

Active Biquad

Filter texts give you dozens of topologies.

Who needs or wants that many choices?

Single-opamp biquad: Sallen-Key

Two-opamp biquad: Tow-Thomas

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 19

A/D

DSP

Sallen-Key LPF

Single gain element

Parasitic sensitive

Versions for LPF, HPF, BP,

Ref: K. L. Su, Analog Filters, Chapman & Hall, 1996, pp. 215.

2 2 1 2 1 1

2 2 1 1

2

2

1 1 1

1

1

) (

C R

G

C R C R

Q

C R C R

s

Q

s

G

s H

P

P

P

P P P

+ +

=

=

+ +

=

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 20

A/D

DSP

Component Sizing Choice 1

4 unknowns: R

1

, R

2

, C

1

, C

2

2 knowns:

P

, Q

P

problem is underdetermined

Choice 1: minimum component spread

9 . 2

1

3

6 . 1

1

1

1

2 1

2 1

= =

= = =

= =

P

P

Q

G

k

C

R R

nF C C

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 21

A/D

DSP

SK Magnitude Response 1

10% increase of R

1

more than doubles Q

P

!

The circuit is very sensitive

to component variations.

10

4

10

5

10

6

-50

-40

-30

-20

-10

0

10

20

30

40

Sallen-Key Choice 1 Magnitude Response

Frequency [Hz]

M

a

g

n

it

u

d

e

[

d

B

]

nominal R1

R1 10% large

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 22

A/D

DSP

Component Sizing Choice 2

Choice 2: minimum sensitivity

pF

R Q

C

nF

R

Q

C

k R R

G

P P

P

P

40

2

1

16

2

2

1

1

2

1

1

2 1

= =

= =

= =

=

400 4

2

2

1

= =

P

Q

C

C

Note also:

Huge element spread

This topology is suitable only for

low-Q filter implementations.

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 23

A/D

DSP

SK Magnitude Response 2

10% increase of R

1

has only small

effect on response!

The circuit is NOT very sensitive

to component variations.

10

4

10

5

10

6

-50

-40

-30

-20

-10

0

10

20

30

Sallen-Key Choice 2 Magnitude Response

Frequency [Hz]

M

a

g

n

it

u

d

e

[

d

B

]

nominal R1

R1 10% large

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 24

A/D

DSP

Sensitivity

Implementation and component

sizing have huge impact on

sensitivity

High-sensitivity circuits are

problems in practice

No theory for finding a low-

sensitivity architecture

Ladder filters are usually low

sensitivity

Use proven circuits & check!

0 2 Choice

% 95 5 . 9

5 . 9 5 . 0 1 Choice

Example

with

Definition

1

1

1

1

1

1

1

=

=

= =

P

P

P

Q

R

P

P

P

Q

R

Q

R

P

P

y

x

y

x

S

R

R

Q

Q

Q S

R

R

S

Q

Q

dx

dy

y

x

S

x

x

S

y

y

Common sense: Sensitivity is a first order approximation,

correct only for infinitesimally small errors

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 2: Introduction to Filters 2002 B. Boser 25

A/D

DSP

Summary

Frequency Response

Poles and zeros are like tent poles and pegs

Frequency response is evaluated on j axis

Poles and zeros close to j axis dominate resonse

Practical Implementation Constraints

Components are not ideal

Avoid solutions requiring large element spread

Beware of high-sensitivity architectures

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 1

A/D

DSP

2

nd

Order Transfer Functions

Imaginary axis zeroes

Tow-Thomas Biquad

Example

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 2

A/D

DSP

Imaginary Axis Zeros

Sharpen transition band

notch out interference

High-pass filter (HPF)

Band-reject filter

2

2

2

) (

1

1

) (

+ +

+

=

Z

P

P P P

Z

K j H

s

Q

s

s

K s H

Note: Always represent transfer functions as a product of a gain

term, poles, and zeros (pairs if complex). Then all

coefficients have a physical meaning, reasonable

magnitude, and easily checkable unit.

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 3

A/D

DSP

Imaginary Axis Zeros

-5

0

5

x 10

5

-5

0

5

x 10

5

0

0.5

1

1.5

2

Sigma [Hz]

Magnitude Response (s-plane)

Frequency [Hz]

M

a

g

n

itu

d

e

[lin

e

a

r

]

-5

0

5

x 10

5

-5

0

5

x 10

5

0

0.5

1

1.5

2

Sigma [Hz]

Magnitude Response (s-plane)

Frequency [Hz]

M

a

g

n

itu

d

e

[lin

e

a

r

]

No finite zeros With finite zeros

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 4

A/D

DSP

Imaginary Zeros

Zeros substantially sharpen

transition band

At the expense of reduced stop-

band attenuation at high frequency

P Z

P

P

f f

Q

kHz f

3

2

100

=

=

=

Pole-Zero Map

Real Axis

Im

a

g

A

x

is

-2 -1.5 -1 -0.5 0 0.5 1 1.5 2

x 10

6

-2

-1.5

-1

-0.5

0

0.5

1

1.5

2

x 10

6

10

4

10

5

10

6

10

7

-50

-40

-30

-20

-10

0

10

Frequency [Hz]

M

a

g

n

itu

d

e

[d

B

]

With zeros

No zeros

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 5

A/D

DSP

Moving the Zeros

P Z

P

P

f f

Q

kHz f

=

=

=

2

100

Pole-Zero Map

Real Axis

Im

a

g

A

x

is

-6 -4 -2 0 2 4 6

x 10

5

-6

-4

-2

0

2

4

6

x 10

5

10

4

10

5

10

6

10

7

-50

-40

-30

-20

-10

0

10

20

Frequency [Hz]

M

a

g

n

itu

d

e

[d

B

]

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 6

A/D

DSP

Tow-Thomas Biquad

Ref: P. E. Fleischer and J. Tow, Design Formulas for biquad active filters using

three operational amplifiers, Proc. IEEE, vol. 61, pp. 662-3, May 1973.

Parasitic insensitive

Multiple outputs

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 7

A/D

DSP

Frequency Response

( ) ( )

( ) ( )

0 1

2

1 0 0 1 0 2 0

0 1

3

0 1

2

0 1

2

2 2

0 1

2

0 0 2 1 1 2

2

1

1

a s a s

b a b a s a b b

a k V

V

a s a s

b s b s b

V

V

a s a s

b a b s b a b

k

V

V

in

o

in

o

in

o

+ +

+

=

+ +

+ +

=

+ +

+

=

V

o2

implements a general biquad section with arbitrary poles and zeros

V

o1

and V

o3

realize the same poles but are limited to at most one finite zero

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 8

A/D

DSP

Component Values

8

7

2

1 7 3

2 8 2

1

1 1

1

2 1 7 3 2

8

0

6

8

2

7 4

8 1

6

8

1 1

1

2 1 7 5 3

8

0

1

1

R

R

k

C R R

C R R

k

C R

a

C C R R R

R

a

R

R

b

R R

R R

R

R

C R

b

C C R R R

R

b

=

=

=

=

=

=

=

8 2 7

2

8

6

2 0

0 1

5

1 1 2 1 2

4

1 0 2 1

3

2 0

1

2

1 1

1

1 1 1

1 1

1

R k R

b

R

R

C b

a k

R

C b b a k

R

C a k k

R

C a

k

R

C a

R

=

=

=

=

=

=

=

8 2 1

and , , , , given R C C k b a

i i i

that follows it

1 1

2 1 7 3 2

8

C R Q

C C R R R

R

P P

P

=

=

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 9

A/D

DSP

Filter Design Example

Application: testing of ultra-linear ADC

Problem: sinusoidal source has higher distortion than

the ADC!

Solution

Filter source with bandpass before converting

Check resulting source with spectral analyzer

Twist: the analyzer is not sufficiently linear either

notch out sinusoid and look just at harmonics

Implementation

Bandpass & Notch at 1kHz

Use V

o2

for bandpass (only possibility),

V

o1

for notch

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 10

A/D

DSP

Filter Design Example

1kHz

Generator

1kHz

BPF

1kHz

Notch

spectrum

analyzer

ADC under

test

Principle: IC test circuits are useless if you cant

verify their performance!

Our filter

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 11

A/D

DSP

Filter Coefficients

( ) ( )

( ) ( )

0 1

2

1 0 0 1 0 2 0

0 1

3

0 1

2

0 1

2

2 2

0 1

2

0 0 2 1 1 2

2

1

1

a s a s

b a b a s a b b

a k V

V

a s a s

b s b s b

V

V

a s a s

b a b s b a b

k

V

V

in

o

in

o

in

o

+ +

+

=

+ +

+ +

=

+ +

+

=

( )

1 k

outputs) other below

slightly V unused keep (to 05 . 1 k

: levels signal reasonable Choose

bandpass) a in want we as (just 0

: free" " for ss Get Bandpa

1

0

1 2

: Notch Design

2

o3 1

0 0 2

1 1 1 2

2

1

2 2

0 0

=

=

=

=

=

=

= = =

b a b

a b a b

b

b

kHz a b

P

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 12

A/D

DSP

Final Filter

0 1

2

0 1 3

0 1

2

0

2

2

0 1

2

1 1

05 . 1

1

a s a s

a a

V

V

a s a s

a s

V

V

a s a s

s a

V

V

in

o

in

o

in

o

+ +

=

+ +

+

=

+ +

=

Choose:

C1=C2=112nF (large to minimize noise)

R8=1k

f

P

=1kHz, Q

P

=30 (check sensitivity!)

Solve equations

R1=42.631k

R2=1.4921k

R3=1.3534k

R4=42.631k

R5=1.4921k

R6=R7=R8

Lets order the parts

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 13

A/D

DSP

Capacitors

C0G capacitors

Vishay Vitramon, C0G Dielectric Capacitor datasheet, 2000.

http://www.vishay.com/document/45002/45002.pdf

Negligible voltage coefficient (for linearity)

Excellent tempco (30ppm/C)

2% initial accuracy is easy to get

No high-value capacitors are trimmable

Resistors will be trimmed to compensate for capacitor

variations

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 14

A/D

DSP

Resistors

Trimmed resistors combine fixed metal film resistors and

precision trim potentiometers in series

1%-accurate, 5ppm/C, lab grade metal film resistors provide 90%

of the nominal resistance

Ref: Caddock Electronics, Type TN Lab Grade Low TC Precision Film Resistor

datasheet, 1999.

50ppm/C trim pots provide between 0% and 20% of the nominal

resistance

Ref: Vishay Foil Resistors, Model 1268 Precision Trimming Potentiometers datasheet

Use two fixed resistors in series with the trimpot to minimize trimpot

value and optimize overall tempco

R6-R8 are 0.1%-accurate, 5ppm/C metal film

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 15

A/D

DSP

Opamps

For opamps, well use the Burr-Brown OPA627

Ref: Texas Instruments / Burr-Brown, OPA627 and OPA604

datasheets, 1989.

The finest audio opamp in the world, and, at $15/each,

priced accordingly!

But money is no object when designing IC test fixtures (only

a few are ever built)

Adequate speed for this application

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 16

A/D

DSP

Bandpass/Bandstop Responses

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 17

A/D

DSP

Filter Design Example (cont.)

Note that the bandpass output H

1

provides

>30dB attenuation to all harmonics present in

the 1kHz generator output

Opamp outputs have 0.00.5dB peak gain

This maximizes each opamps output swing for

best dynamic range

Lets magnify the frequency axis for the two

responses of interest

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 18

A/D

DSP

Bandpass/Bandstop Responses

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 19

A/D

DSP

Filter Design Example

Temperature changes wont change these

responses too much

Lab temperatures are stable to 253C

Our lab-grade RC products move <100ppm/C

Initial component values are another story

What if C1=114nF and C2=113nF?

Thats within their 2% accuracy specifications

Whats ?

P

C

S

1

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 20

A/D

DSP

Bandpass/Bandstop Responses

Frequency (kHz)

G

a

i

n

(

d

B

)

20

0

- 20

- 40

- 60

0.9 1.1

H

1

H

2

C1=.114F

C2=.113F

Rs nominal

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 21

A/D

DSP

Filter Design Example

Obviously, weve got to tune the filter

back to its original specification

How is that tuning done?

Do you tell your technician to twiddle pots

randomly until it works?

Or do you document a robust tuning

procedure?

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 22

A/D

DSP

RC Filter Tuning Strategy

Famous biquads like the Tow-Thomas come

complete with their own tuning strategies

The circuit topologies allow 1 trim operation to adjust 1

design parameter (such as f

P

, f

Z

, Q

P

, Q

Z

, gain) without

changing the others

Rationale for a biquads tuning strategy becomes

apparent when studying design equations such as

the Tow-Thomas equations on slide 6

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 23

A/D

DSP

Tow-Thomas Tuning Strategy

R3 will be set to a fixed value to keep the

unused OPAMP3 output below 0dB

Tuning involves the following steps performed

in the specified sequence:

Adjust R2 to center the bandpass at 1kHz

Adjust R5 to center the notch at 1kHz

Adjust R1 to set the bandpass Q to 30

Adjust R4 to deepen the notch

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 24

A/D

DSP

Tow-Thomas Tuning Strategy

The design equations also provide the range of

adjustment required for a given resistor

Remember that an excessively large adjustment range

translates into excessively large tempco

R1 tuning range (from slide 7):

a

1

1

R

1

C

1

1

a

1

C

1MAX

1

a

1

C

1MIN

< R

1

<

known set by capacitor tolerances

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 25

A/D

DSP

Tow-Thomas Tuning Strategy

An even simpler way to determine

resistor ranges is to:

Set all capacitors to their high tolerance

limit (nominal+2% in this case)

Calculate Rs for these capacitances

(these will be the minimum resistance

values)

Set capacitors to their low tolerance limit

Calculate maximum Rs

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 26

A/D

DSP

Tow-Thomas Biquad

C

2

(0.112)

v

IN

R

7

(1K)

R

1

(40K+5K)

R

5

(1.4K+200)

R

6

(1K)

R

8

(1K)

R

3

(1.35K)

R

4

(40K+5K)

OPAMP1 OPAMP2 OPAMP3

C

1

(0.112)

R

2

(1.4K+200)

resistors: metal film + trimpot

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 27

A/D

DSP

Tow-Thomas Tuning Strategy

If youve left your filter unattended for a while,

assume that its trim potentiometers are

completely misadjusted

Adjust all trimpots to 0 and start over

Lets return to our C1=114nF, C2=113nF example

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 28

A/D

DSP

Bandpass/Bandstop Responses

Frequency (kHz)

G

a

i

n

(

d

B

)

20

0

- 20

- 40

- 60

0.9 1.1

H

1

H

2

C1=114nF

C2=113nF

Rs nominal

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 29

A/D

DSP

Bandpass/Bandstop Responses

Frequency (kHz)

G

a

i

n

(

d

B

)

20

0

- 20

- 40

- 60

0.9 1.1

H

1

H

2

C1=114nF

C2=113nF

trimpots=0

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 30

A/D

DSP

Tow-Thomas Tuning Strategy

For most Rs and Cs in this biquad

Hence,

This means a +2% change in R

2

will cause a

1% change in f

P

Note that f

Z

sensitivities are also 1/2

A 4% increase in R

5

will shift our notch (currently at

1.02kHz) back to the right place

x

f

P

1

~

2

1

=

P

f

x

S

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 31

A/D

DSP

Bandpass/Bandstop Responses

Frequency (kHz)

G

a

i

n

(

d

B

)

20

0

- 20

- 40

- 60

0.9 1.1

H

1

H

2

C1=114nF

C2=113nF

R1=41k

R2=1456

R3=1350

R4=41k

R5=1456

R6=R7=R8=1k

EECS 247 Lecture 3: Second Order Transfer Functions 2002 B. Boser 32

A/D

DSP

Summary

General 2

nd

order transfer function

Imaginary axis zeros

General purpose biquad

Large selection in literature

Tow-Thomas biquad:

3 opamps

Parasitic insensitive

Multiple outputs

Tuning strategy

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 1

A/D

DSP

Electronic Noise

Dynamic range in the analog domain

Resistor noise

Amplifier noise

Maximum signal levels

Tow-Thomas Biquad noise example

Implications on power dissipation

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 2

A/D

DSP

Analog Dynamic Range

Finite precision effects in digital filters are

rapidly becoming negligible

Floating point digital filters with huge mantissas

will be reduced to negligible cost

The only fixed-point numbers will come from

ADCs

But we will always have thermal noise

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 3

A/D

DSP

Analog Dynamic Range

Lets say youve selected the poles and

zeroes of your analog filter transfer

function

Of the infinitely many ways to build a

filter with a given transfer function, each

of those ways has a different output

noise!

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 4

A/D

DSP

Analog Dynamic Range

The job of a high-performance analog filter

designer is to get reasonably close to the

optimal noise for a given transfer function

Not the absolute minimum noise, just close

The job of a mixed-signal chip architect is to

appreciate filter noise and to be able to model

filters well enough to know that a given

dynamic range objective is feasible

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 5

A/D

DSP

Analog Dynamic Range

Well begin our adventure in analog filter

implementation by looking at the noise

in resistors and simple RC filters

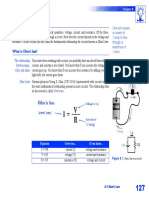

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 6

A/D

DSP

Resistor Noise

Capacitors are

noiseless

Resistors have

thermal noise

This noise is

uniformly distributed

from dc to infinity

Frequency-

independent noise is

called white noise

R

C

v

IN

v

OUT

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 7

A/D

DSP

f R T k v

r B n

= 4

2

Resistor Noise

Resistor noise has

A mean value of zero

A mean-squared value

R

C

v

IN

v

OUT

measurement bandwidth (Hz)

absolute temperature (K)

Boltzmanns constant = 1.38e-23 J/K

ohms

Volts

2

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 8

A/D

DSP

Resistor Noise

Resistor rms noise voltage in

a 10Hz band centered at

1kHz is the same as resistor

rms noise in a 10Hz band

centered at 1GHz

Resistor noise spectral

density, N

0

, is the rms noise

per Hz of bandwidth:

R

C

v

IN

v

OUT

R T k

f

v

N

r B

n

4

2

0

=

=

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 9

A/D

DSP

Resistor Noise

Dont bother to remember

Boltzmanns constant

Instead, remember forever that N

0

for a 1k resistor at room

temperature is 4nV/Hz

Scaling R,

A 10M resistor gives 400nV/Hz

A 50 resistor gives 0.9nV/Hz

Or, remember that

k

B

T

r

= 4x10

-21

J (T

r

= 17

o

C)

R

C

v

IN

v

OUT

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 10

A/D

DSP

Resistor Noise

Resistor noise gives our filter

a non-zero output when

v

IN

=0

In this simple example, both

the input signal and the

resistor noise obviously have

the same transfer functions

to the output

Since noise has random

phase, we can use any

polarity convention for a

noise source (but we have to

use it consistently)

R

C

v

IN

v

OUT

e

+ -

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 11

A/D

DSP

Resistor Noise

What is the thermal noise of the

RC filter?

Lets ask SPICE!

Netlist:

Noise from RC LPF

vin vin 0 ac 1V

r1 vin vout 8kOhm

c1 vout 0 1nF

.ac dec 100 10Hz 1GHz

.noise V(vout) vin

.end

R=8k

C=1nF

v

IN

v

OUT

e

+ -

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 12

A/D

DSP

LPF1 Output Noise Density

[Hz]

N

o

i

s

e

S

p

e

c

t

r

a

l

D

e

n

s

i

t

y

(

n

V

/

H

z

)

100

0.01

0.1

1

10

10

1

10

3

10

7

10

5

10

9

20 kHz corner

Hz

Hz

R T k N

r B

nV

3 . 11

nV

4 8

4

0

=

=

=

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 13

A/D

DSP

Total Noise

Suppose we want to know the value of v

o

now,

whats the standard deviation error?

(E.g. on the display of a volt-meter connected to v

o

).

Answer:

df jf H TR k v

B o

2

0

2

) 2 ( 4

=

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 14

A/D

DSP

Total Noise

Note that noise is integrated in the mean-

squared domain, because noise in a

bandwidth df around frequency f

1

is

uncorrelated with noise in a bandwidth df

around frequency f

2

Powers of uncorrelated random variables add

Squared transfer functions appear in the mean-

squared integral

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 15

A/D

DSP

Total Noise

C

T k

df

jfRC

TR k

df jf H TR k v

B

B

B o

=

+

=

=

2

0

2

0

2

2 1

1

4

) 2 ( 4

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 16

A/D

DSP

Total Noise

This interesting and somewhat counterintuitive result

means that even though resistors provide the noise

sources, capacitors set the total noise

For a given capacitance, as resistance goes up, the

increase in noise density is balanced by a decrease

in noise bandwidth

C

T k

v

B

o

=

2

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 17

A/D

DSP

kT/C Noise

The rms noise voltage of the simplest possible (first

order) filter is k

B

T/C

For 1pF, k

B

T/C = 64 V-rms (at 298K)

1000pF gives 2 V-rms

The noise of a more complex filter is K x k

B

T/C

K depends on implementation and features such as

filter order

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 18

A/D

DSP

LPF1 Output Noise

[Hz]

100

0.01

0.1

1

10

10

1

10

3

10

7

10

5

10

9

N

o

i

s

e

S

p

e

c

t

r

a

l

D

e

n

s

i

t

y

(

n

V

/

H

z

)

I

n

t

e

g

r

a

t

e

d

N

o

i

s

e

(

V

r

m

s

)

2Vrms

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 19

A/D

DSP

LPF1 Output Noise

Note that the integrated noise essentially

stops growing above 100kHz for this 20kHz

lowpass filter

Beware of faulty intuition which might tempt

you to believe that an 80, 1000pF filter has

lower integrated noise than our 8000,

1000pF filter

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 20

A/D

DSP

LPF1 Output Noise

[Hz]

100

0.01

0.1

1

10

10

1

10

3

10

7

10

5

10

9

N

o

i

s

e

S

p

e

c

t

r

a

l

D

e

n

s

i

t

y

(

n

V

/

H

z

)

I

n

t

e

g

r

a

t

e

d

N

o

i

s

e

(

V

r

m

s

)

80, 1000pF

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 21

A/D

DSP

LPF1 Output Noise

Of course, an 80, 100,000pF filter has

both the same bandwidth AND lower

integrated noise than our 8000,

1000pF filter

In the analog filter dynamic range game,

the highest capacitance wins

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 22

A/D

DSP

LPF1 Output Noise

[Hz]

100

0.01

0.1

1

10

10

1

10

3

10

7

10

5

10

9

N

o

i

s

e

S

p

e

c

t

r

a

l

D

e

n

s

i

t

y

(

n

V

/

H

z

)

I

n

t

e

g

r

a

t

e

d

N

o

i

s

e

(

V

r

m

s

)

80, 100000pF

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 23

A/D

DSP

Analog Circuit Dynamic Range

The biggest signal we can ever expect at the output of a circuit

is limited by the supply voltage, V

DD

hence (for sinusoids)

The noise is

So the dynamic range in dB is:

2 2

1

) (

max

DD

V

rms V =

C

T k

K rms V

B

n

= ) (

[pF] in C with [dB] 75 20log

[V/V]

8 ) (

) (

10

max

+

=

= =

K

C

V

T Kk

C V

rms V

rms V

DR

DD

B

DD

n

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 24

A/D

DSP

Analog Circuit Dynamic Range

For integrated circuits built in modern CMOS

processes, V

DD

< 3V and C < 1nF (K = 1)

DR < 110dB

For PC board circuits built with old-fashioned 30V

opamps and discrete capacitors of < 100nF

DR < 140dB

A 30dB advantage!

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 25

A/D

DSP

Dynamic Range versus Bits

Bits and dB are related:

see quantization noise, later in the course

Hence

110 dB 18 Bits

140 dB 23 Bits

[dB] 6 2 N DR + =

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 26

A/D

DSP

Dynamic Range versus Power

Each extra bit corresponds to 6dB

6dB means cutting noise power by 4!

This translates into 4x larger capacitors

To drive these at the same speed, G

m

must increase 4x

Power is proportional to G

m

(for fixed supply and V

dsat

)

In analog circuits that are limited by thermal noise,

1 extra bit costs 4x power

E.g. 16Bit ADC at 200mW 17Bit ADC at 800mW

Do not overdesign the dynamic range of analog circuits!

P.S. What is the cost of an extra bit in a 64Bit adder?

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 27

A/D

DSP

Active Filter Example

C

v

IN

v

OUT

R

R

2

2

2

=

=

K

C

T k

v

B

o

( )

sRC

s H

+

=

1

1

Frequency response:

Total noise (see EE240):

Noise depends on filter topology

Opamps contribute yet more noise

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 28

A/D

DSP

Behavioral Opamp Model

Specification Example

Gain G 100k

Unity-gain bandwidth f

u

100 MHz

Input refd thermal noise 5 nV/Hz

Beware of flicker noise and input current noise (BJTs).

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 29

A/D

DSP

SPICE Analysis

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 30

A/D

DSP

Noise Analysis

Opamp noise

dominates in this

example

Opamp adds

significant noise above

filter roll-off

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 31

A/D

DSP

Opamp Bandwidth

Minimize opamp bandwidth:

f

u

= 1MHz 7V-rms

f

u

= 10MHz 20V-rms

Of course, the opamp has to

be fast enough to faithfully

realize the 20kHz corner!

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 32

A/D

DSP

Frequency Response

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 33

A/D

DSP

Tow-Thomas Noise Analysis

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 34

A/D

DSP

Tow-Thomas Biquad

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 35

A/D

DSP

Bandpass Noise

Noise from the passband

dominates this integral.

Unfortunately the opamp adds

significant additional noise at high frequency

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 36

A/D

DSP

RC Filter Reduces BP Noise

We cannot reduce the opamp noise or bandwidth lets filter its noise!

1k / 5nF RC LPF

corner at 32kHz

0.9V rms noise from 5nF is negligible

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 37

A/D

DSP

BP Response with RC Filter

RC provides negligible attenuation.

But thats not the point.

Lets look at the noise

Without RC

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 38

A/D

DSP

BP Noise after RC Filter

RC filter reduces total noise

from 20V to 5V rms.

(Without opamp noise is 3V rms).

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 39

A/D

DSP

BP Dynamic Range

Maximum sinewave input: 7.8V rms

(limited by opamp)

Noise: 5.2V rms (with RC)

Dynamic range: 123dB

No IC with integrated capacitors can

get close to this dynamic range

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 40

A/D

DSP

Bandstop Noise

Much lower than at 1kHz,

but much higher bandwidth!

Noise above notch dominates.

Opamp doubles total noise

No notch in the noise response

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 41

A/D

DSP

Noise versus Pole Q

R

1

= R

4

= 42k 10k:

Q drops from 30 to 7

R = 10k

R = 42k

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 42

A/D

DSP

Noise versus Pole Q

Noise drops by 30/7

from 2.8mV to 1.2mV rms.

rms total noise is approximately

proportional to Q

of course in this circuit the opamp noise

swamps this effect

(this simulation uses noiseless opamps)

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 4: Dynamic Range 2002 B. Boser 43

A/D

DSP

Noise Summary

Thermal noise is a fundamental property of

(electronic) circuits

Noise is closely related to

Capacitor size and

Power dissipation

In filters, noise is proportional to order, Q, and

depends on implementation

Operational amplifiers can contribute

significantly to overall filter noise

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 1

A/D

DSP

Filter Synthesis

Analog filter synthesis

IIR filters

LP, HP, BP, BS

Magnitude response templates

Filter prototypes

Synthesis with biquads

Phase response

Group delay

Step response

All-pass filters

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 2

A/D

DSP

Filter Approximation

Objective: Magnitude specification H(s)

Classic IIR Filters

Chebychev 2

Uses zeros for good attenuation but has no passband

ripples. A good all-round combination.

Butterworth

Poles only and no passband ripple. Less ringing in step

response than Chebychev 2.

Elliptic

Passband and stopband ripples. Use this when only

magnitude response counts. Large overshoot in step

response. High Q poles result in high sensitivity.

Bessel

Great step response at the cost of poor attenuation.

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 3

A/D

DSP

Design Example

10

4

10

5

10

6

10

7

-120

-100

-80

-60

-40

-20

0

Rp = 3 dB

Rs = 80 dB

fp = 100kHz fs = 1MHz

Frequency [Hz]

M

a

g

n

it

u

d

e

[

d

B

]

Butterworth (N = 5)

Chebychev 2 (N = 4)

Elliptic (N = 3)

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 4

A/D

DSP

Matlab Code

fp = 1.0e5; wp = 2*pi*fp;

fs = 1.0e6; ws = 2*pi*fs;

rp = 3;

rs = 80;

% filter prototype

[Nb, Wb] = buttord(wp, ws, rp, rs, 's');

[b, a] = butter(Nb, Wb, 's');

Hb = tf(b, a);

[Nc, Wc] = cheb2ord(wp, ws, rp, rs, 's');

[b, a] = cheby2(Nc, rs, Wc, 's');

Hc = tf(b, a);

[Ne, We] = ellipord(wp, ws, rp, rs, 's');

[b, a] = ellip(Ne, rp, rs, We, 's');

He = tf(b, a);

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 5

A/D

DSP

Step response

Slow rise time

Overshoot

Acceptable in some

applications, problematic

in others.

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

x 10

-5

0

0.2

0.4

0.6

0.8

1

1.2

1.4

Butterworth

Chebychev 2

Elliptic

Step Response

Time (sec)

A

m

p

l

i

t

u

d

e

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 6

A/D

DSP

2

out

1

i n

Random Data

H

Filter Binary

Data Transmission

0 0.5 1 1.5

x 10

-3

-1.5

-1

-0.5

0

0.5

1

1.5

input

output

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 7

A/D

DSP

Eye Diagram

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

x 10

-4

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 8

A/D

DSP

Increased Data Rate

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6

x 10

-4

-1.5

-1

-0.5

0

0.5

1

1.5

input

output

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

x 10

-5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 9

A/D

DSP

Group Delay

Nonuniform group delay is one source

of eye closure

Group delay?

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 10

A/D

DSP

Consider a continuous time filter with s-

domain transfer function G(s):

The filter input is the sum of two sinewaves at

slightly different frequencies (<<):

Amplitude and Phase Distortion

v

IN

(t) = A

1

sin(t) + A

2

sin[(+) t]

G(j) G(j)e

j()

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 11

A/D

DSP

Amplitude and Phase Distortion

The filter output is:

v

OUT

(t) = A

1

G(j) sin[t+()] +

A

2

G[ j(+)] sin[(+)t+ (+)]

{ ]} [

= A

1

G(j) sin

t +

()

+

{ ]} [

+ A

2

G[ j(+)] sin (+) t +

(+)

+

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 12

A/D

DSP

Amplitude and Phase Distortion

{ ]} [

v

OUT

(t) = A

1

G(j) sin

t +

()

+

{ ]} [

+ A

2

G[ j(+)] sin (+) t +

(+)

+

(+)

+

()+

d()

d

[ ][

1

) ( ]

1 -

d()

d

()

+

()

-

( )

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 13

A/D

DSP

Amplitude and Phase Distortion

If the second term in this equation is non-

zero, then the filters output at frequency

+ is time-shifted differently than the

filters output at frequency

Phase distortion

(+)

+

d()

d

()

+

()

( )

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 14

A/D

DSP

Amplitude and Phase Distortion

If the second term in this equation is zero,

then the filters output at frequency + and

the output at frequency are each delayed in

time by -()/

PD

-()/ is called the phase delay and

has units of time

(+)

+

d()

d

()

+

()

( )

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 15

A/D

DSP

Since 0, phase distortion is avoided only if:

Clearly, if ()=k, k a constant, we avoid

phase distortion

This type of filter phase response is called

linear phase

Phase shift varies linearly with frequency

Amplitude and Phase Distortion

d()

d

()

-

= 0

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 16

A/D

DSP

Amplitude and Phase Distortion

GR

-d()/d=k is called the group delay

and also has units of time

GR

=

PD

implies linear phase

Note: Filters with ()=k+c are also called linear

phase filters, but theyre not free of phase distortion

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 17

A/D

DSP

Amplitude and Phase Distortion

If

GR

=

PD

,

[ )] (

v

OUT

(t) = A

1

G(j) sin t -

GR

+

[

+ A

2

G[ j(+)] sin (+)

)] (

t -

GR

If G( j)=G[ j(+)] for all inputs within the

signal-band, v

OUT

is a scaled, time-shifted replica of

the input, with no amplitude distortion

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 18

A/D

DSP

Amplitude and Phase Distortion

No amplitude distortion:

G( j)=G[ j(+)]

No phase distortion:

GR

=

PD

Neither of these conditions are realizable exactly in

continuous time filters

Real passbands cant have flat amplitude responses

Derivatives of sums of arctangents arent constant

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 19

A/D

DSP

Group Delay Comparison

100kHz corner frequency

Chebychev II versus Bessel

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 20

A/D

DSP

Magnitude Response

Bode Magnitude Diagram

Frequency [Hz]

M

a

g

n

i

t

u

d

e

(

d

B

)

10

4

10

5

10

6

10

7

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

4th Order Chebychev 2

4th Order Bessel

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 21

A/D

DSP

Phase Response

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

x 10

5

-300

-250

-200

-150

-100

-50

0

Frequency [Hz]

P

h

a

s

e

[

d

e

g

r

e

e

s

]

4th Order Chebychev 2

4th Order Bessel

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 22

A/D

DSP

Group Delay

10

4

10

5

10

6

10

7

0

1

2

3

4

5

6

7

Frequency [Hz]

G

r

o

u

p

D

e

la

y

[

s

]

4th Order Chebychev 2

4th Order Bessel

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 23

A/D

DSP

Normalized Group Delay

10

4

10

5

10

6

10

7

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

Frequency [Hz]

G

r

o

u

p

D

e

l

a

y

[

n

o

r

m

a

l

i

z

e

d

]

4th Order Chebychev 2

4th Order Bessel

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 24

A/D

DSP

Step Response

Step Response

Time (sec)

A

m

p

l

i

t

u

d

e

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

x 10

-5

0

0.2

0.4

0.6

0.8

1

1.2

1.4

4th Order Chebychev 2

4th Order Bessel

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 25

A/D

DSP

Eye Diagrams

Note: the Chebychev output should be scaled to the same peak amplitude as the

output from the Bessel. The Bessel has a clear advantage.

-1 0 1 2 3 4 5 6

x 10

-5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

4th Order Bessel

-1 0 1 2 3 4 5 6

x 10

-5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

4th Order Chebychev

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 26

A/D

DSP

Allpass Filters

Delay equalization

Unity magnitude response

arbitrary delay

Can compensate arbitrary phase

distortion (e.g. from a given channel)

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 27

A/D

DSP

Second-Order All Pass Filter

j

radius =

P

P

2Q

P

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 28

A/D

DSP

Second-Order All Pass Filter

From graphical considerations alone, the

second-order all pass filter has unity

magnitude response at all frequencies

Its phase shift is twice that of its pole

All pass sections cant cancel out the delay of

other filter sections,

But they can add strategic delay to improve the

phase response of a companion filter

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 29

A/D

DSP

All Pass Filters

An all pass filter used to make a companion

filters group delay more constant in the filter

passband is called a phase equalizer or

delay equalizer

Group-delay-critical applications frequently

devote as many poles to phase response

reshaping as they devote to magnitude

response shaping

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 30

A/D

DSP

All Pass Filters

Phase equalizers are commonly used in

digital data receivers

If youre not sure whether or not you need a

phase equalizer, build one

Start with just as many poles as your magnitude

shaper

CAD tools like MATLABs iirgrpdelay help

synthesize optimal phase equalizers

Unfortunately iirgrpdelay is for sampled data filters

only use the bilinear transform (see later)

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 31

A/D

DSP

Magnitude Response

Bode Magnitude Diagram

Frequency [Hz]

M

a

g

n

it

u

d

e

(

d

B

)

10

4

10

5

10

6

10

7

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

4th Order Chebychev 2

Allpass

Cheby+Allpass

8th Order Bessel

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 32

A/D

DSP

Phase Response

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

x 10

5

-900

-800

-700

-600

-500

-400

-300

-200

-100

0

Frequency [Hz]

P

h

a

s

e

[

d

e

g

r

e

e

s

]

4th Order Chebychev 2

Allpass

Cheby+Allpass

8th Order Bessel

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 33

A/D

DSP

Normalized Group Delay

10

4

10

5

10

6

10

7

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

Frequency [Hz]

G

r

o

u

p

D

e

l

a

y

[

n

o

r

m

a

l

i

z

e

d

]

4th Order Chebychev 2

Cheby+Allpass

8th Order Bessel

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 34

A/D

DSP

Step Response

Step Response

Time (sec)

A

m

p

l

i

t

u

d

e

0 0.5 1 1.5 2 2.5 3

x 10

-5

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

1.2

4th Order Chebychev 2

Allpass

Cheby+Allpass

8th Order Bessel

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 35

A/D

DSP

Eye Diagrams

-1 0 1 2 3 4 5 6

x 10

-5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

8th Order Bessel

-1 0 1 2 3 4 5 6

x 10

-5

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

Time

4th Order Chebychev with 4th Order Allpass

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 36

A/D

DSP

FIR Filter Phase Response

A significant advantage of FIR over IIR filters

is that FIR filters can be realized with linear

phase response

But (with few exceptions) FIR filters are only

practical in the digital domain

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 5: Filter Syntesis & Group Delay 2002 B. Boser 37

A/D

DSP

Summary

Filter design:

Magnitude response

Template

Approximation (matlab) H(s)

Realization with

Cascades of biquads

Sensitivity limits practical designs to <3 sections

Ladder filters next lecture

Phase / group delay

Phase equalization (allpass)

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 6: Ladder Filters 2002 B. Boser 1

A/D

DSP

Higher Order Filter Options

Cascade of Biquads

High-Q poles

High component sensitivity

Ladders

Low sensitivity (Orchard)

Synthesize from LC prototypes

Digital filters

Preferred solution when possible

EECS 247 Lecture 6: Ladder Filters 2002 B. Boser 2

A/D

DSP

Cascade of Biquads

LPF with

f

pass

= 20 kHz r

pass

= 0.5 dB

f

stop

= 22.05 kHz r

stop

= 50 dB

8

th

order Elliptic Filter

Implementation with Biquads

Goal: maximize dynamic range

Pair poles and zeros

highest Q poles with closest zeros is a good starting point, but not

necessarily optimum

Ordering

lowest Q poles is a good start

Simpo PDF Merge and Split Unregistered Version - http://www.simpopdf.com

EECS 247 Lecture 6: Ladder Filters 2002 B. Boser 3

A/D

DSP

Bode Diagram

Frequency [Hz]

P

h

a

s

e

(

d

e

g

)

M

a

g

n

it

u

d

e

(

d

B

)

-120

-100

-80

-60

-40

-20

0

10

4

10

5

-720

-540

-360

-180

0

180

Filter Response

Bode Magnitude Diagram

Frequency [Hz]

M

agnitude (dB

)

10

4.1

10

4.2

10

4.3

-0.6

-0.5

-0.4

-0.3

-0.2

-0.1

0

EECS 247 Lecture 6: Ladder Filters 2002 B. Boser 4

A/D

DSP

Pole-Zero Map

Q

pole

f

pole

[kHz]

38. 4389 20.0501

8.2903 19.0959

2.4134 16.0142

0.7130 9.4282

f

zero

[kHz]

70.6923

28.7992

22.8585

21.4663

Pole-ZeroMap

Real Axis

I

m

a

g

A

x

is

-5 -4 -3 -2 -1 0 1 2 3 4 5

x 10

4

-5

-4