Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

DS1803

Caricato da

zektorCopyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

DS1803

Caricato da

zektorCopyright:

Formati disponibili

1 of 11 110706

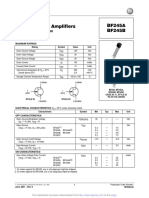

FEATURES

3V or 5V Operation

Ultra-Low Power Consumption

Two Digitally Controlled, 256-Position

Potentiometers

14-Pin TSSOP (173 mil) and 16-Pin SO (150

mil) Packaging Available for Surface-Mount

Applications

Addressable Using 3 Address Inputs

2-Wire Serial Interface

Operating Temperature Range:

- Industrial: -40C to +85C

Standard Resistance Values:

- DS1803-010 10k

- DS1803-050 50k

- DS1803-100 100k

PIN ASSIGNMENT

PIN DESCRIPTION

L0, L1 - Low End of Resistor

H0, H1 - High End of Resistor

W0,W1 - Wiper terminal of Resistor

V

CC

- 3V/5V Power Supply Input

A0, A1, A2 - Chip Select Inputs

SDA - Serial Data I/O

SCL - Serial Clock Input

GND - Ground

NC - No Connection

DESCRIPTION

The DS1803 addressable dual digital potentiometer features two independently controlled 256-position

potentiometers. Device control is achieved through a 2-wire serial interface. Three address pins allow up

to 8 DS1803s to share the same 2-wire interface. The exact wiper position of each potentiometer can be

written or read. The DS1803 is available in a 16-pin DIP, 16-pin SO, and 14-pin TSSOP package. The

device is available in three standard resistance values: 10k, 50k, and 100k and is specified over the

industrial temperature range.

DS1803

Addressable Dual Digital Potentiometer

www.maxim-ic.com

H1 1 14 VCC

L1 2 13 NC

W1 3 12 H0

A2 4 11 L0

A1 5 10 W0

A0 6 9 SDA

GND 7 8 SCL

DS1803 14-PIN TSSOP (173 MIL)

H1 1 16 VCC

NC 2 15 NC

L1 3 14 H0

W1 4 13 L0

A2 5 12 W0

A1 6 11 NC

A0 7 10 SDA

GND 8 9 SCL

DS1803Z 16-PIN SO (150 MIL)

DS1803 16-PIN DIP (300 MIL)

See Mech. Drawings Section on Website

DS1803

2 of 11

DEVICE OPERATION

The DS1803 is an addressable, digitally controlled device which has two 256-position potentiometers. A

functional block diagram of the part is shown in Figure 1. Communication and control of the device is

accomplished via a 2-wire serial interface. Address inputs A0, A1, and A2 allow up to 8 DS1803s to

share the same 2-wire interface.

Each potentiometer is composed of a 256 position resistor array. Two 8-bit registers, each assigned to a

respective potentiometer, are used to set the wiper position on the resistor array. The wiper terminal is

multiplexed to one of 256 positions on the resistor array based on its corresponding 8-bit register value.

For example, the high-end terminals, H0 and H1, have wiper position values FFh while the low-end

terminals, L0 and L1, have wiper position values 00h.

The DS1803 is a volatile device that does not maintain the position of the wiper during power-down or

loss of power. On power-up, the DS1803 wipers position will be set to position 00h - the low-end

terminals. The user may then set the wiper value to a desired position.

Communication with the DS1803 takes place over the 2-wire serial interface consisting of the bi-

directional pin, SDA, and the serial clock input, SCL. Complete details of the 2-wire interface are

discussed in the section entitled 2-wire Serial Data Bus.

Application Considerations

The DS1803 is offered in three standard resistor values, which include 10k, 50k, and 100k. The

resolution of the potentiometer is defined as R

TOT

/255, where R

TOT

is the total resistor value of the

potentiometer. The DS1803 is designed to operate using 3V or 5V power supplies over the industrial

(-40C to +85C) temperature range. Maximum input signal levels across the potentiometer cannot

exceed the operating power supply of the device.

2-WIRE SERIAL DATA BUS

The DS1803 supports a bi-directional 2-wire bus and data transmission protocol. A device that sends data

on the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls

the message is called a master. The devices that are controlled by the master are slaves. The bus must

be controlled by a master device which generates the serial clock (SCL), controls the bus access, and

generates the START and STOP conditions. The DS1803 operates as a slave on the 2-wire bus.

Connections to the bus are made via the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined (see Figure 2).

Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in

the data line while the clock line is high will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is

HIGH, defines a START condition.

DS1803

3 of 11

Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is

HIGH, defines the STOP condition.

Data valid: The state of the data line represents valid data when, after a START condition, the data line

is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed

during the LOW period of the clock signal. There is one clock pulse per bit of data. Figure 2 details how

data transfer is accomplished on the 2-wire bus. Depending upon the state of the R/ W* bit, two types of

data transfer are possible.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions is not limited, and is determined

by the master device. The information is transferred byte-wise and each receiver acknowledges with a

ninth bit.

Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse which is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

1. Data transfer from a master transmitter to a slave receiver: The first byte transmitted by the

master is the control byte (slave address). Next follows a number of data bytes. The slave returns an

acknowledge bit after each received byte.

2. Data transfer from a slave transmitter to a master receiver: The first byte (the slave address) is

transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of data

bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received

bytes other than the last byte. At the end of the last received byte, a not acknowledge is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A

transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START

condition is also the beginning of the next serial transfer, the bus will not be released.

The DS1803 may operate in the following two modes:

1. Slave receiver mode: Serial data and clock are received through SDA and SCL. After each byte is

received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the

beginning and end of a serial transfer. Address recognition is performed by hardware after reception

of the slave address and direction bit.

2. Slave transmitter mode: The first byte is received and handled as in the slave receiver mode.

However, in this mode the direction bit will indicate that the transfer direction is reversed. Serial data

is transmitted on SDA by the DS1803 while the serial clock is input on SCL. START and STOP

conditions are recognized as the beginning and end of a serial transfer.

DS1803

4 of 11

SLAVE ADDRESS

The control byte is the first byte received following the START condition from the master device. The

control byte consists of a four bit control code; for the DS1803, this is 0101 binary. The next three bits of

the control byte are the device select bits (A2, A1, A0). They are used by the master device to select

which of the devices on the bus are to be accessed. The last bit of the control byte (R/ W*) defines the

operation to be performed. When set to a one a read operation is selected, and when set to a zero a write

operation is selected. Figure 3 shows the control byte for the DS1803.

Following the START condition, the DS1803 monitors the SDA bus for the control byte being

transmitted. Upon receiving a matching control byte, the DS1803 outputs an acknowledge signal on the

SDA line.

COMMAND AND PROTOCOL

The command and protocol structure of the DS1803 allows the user to read or write the potentiometer(s).

The command structures for the part are presented in Figures 4 and 5. Data is transmitted most significant

bit (MSB) first. During communication, the receiving unit always generates the acknowledge.

Reading the DS1803

As shown in Figure 4, the DS1803 provides one read command operation. This operation allows the user

to read both potentiometers. Specifically, the R/ W bit of the control byte is set equal to a 1 for a read

operation. Communication to read the DS1803 begins with a START condition which is issued by the

master device. The control byte from the master device will follow the START condition. Once the

control byte has been received by the DS1803, the part will respond with an ACKNOWLEDGE. The

R/ W bit of the control byte as stated should be set equal to 1 for reading the DS1803.

When the master has received the ACKNOWLEDGE from the DS1803, the master can then begin to

receive potentiometer wiper data. The value of the potentiometer-0 wiper position will be the first

returned from the DS1803. Once the eight bits of the potentiometer-0 wiper position has been transmitted,

the master will need to issue an ACKNOWLEDGE, unless it is the only byte to be read, in which case the

master issues a NOT ACKNOWLEDGE. If desired the master may stop the communication transfer at

this point by issuing the STOP condition. However, if the value of the potentiometer-1 wiper position

value is needed, communication transfer can continue by clocking the remaining eight bits of the

potentiometer-1 value, followed by an NOT ACKNOWLEDGE. Final communication transfer is

terminated by issuing the STOP command.

Writing the DS1803

A data flow diagram for writing the DS1803 is shown in Figure 5. The DS1803 has three write

commands. These include write pot-0, write pot-1, and write pot-0/1. The write pot-0 command allows

the user to write the value of potentiometer-0 and as an option the value of potentiometer-1. The write-1

command allows the user to write the value of potentiometer-1 only. The last write command, write-0/1,

allows the user to write both potentiometers to the same value with one command and one data value

being issued.

All the write operations begin with a START condition. Following the START condition, the master

device will issue the control byte. The read/write bit of the control byte will be set to 0 for writing the

DS1803. Once the control byte has been issued and the master receives the acknowledgment from the

DS1803, the command byte is transmitted to the DS1803. As mentioned above, there exist three write

DS1803

5 of 11

operations that can be used with the DS1803. The binary value of each write command is shown in Figure

5 and also in the Table 1.

2-WIRE COMMAND WORDS Table 1

COMMAND COMMAND VALUE

Write Potentiometer-0 101010 01

Write Potentiometer-1 101010 10

Write Both Potentiometers 101011 11

DS1803

6 of 11

ABSOLUTE MAXIMUM RATINGS*

Voltage on Any Pin Relative to Ground -1.0V to +7.0V

Operating Temperature -40 to +85C; industrial

Storage Temperature -55C to +125C

Soldering Temperature 260C for 10 seconds

* This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated in the operation sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods of time may affect reliability.

RECOMMENDED OPERATING CONDITIONS (-40C to +85C)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

Supply Voltage V

CC

+2.7 5.5 V 1

Resistors Inputs L,H,W GND-0.5 V

CC

+0.5 V 1

DC ELECTRICAL CONDITIONS (-40C to +85C; V

CC

=2.7V to 5.5V)

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS NOTES

Supply Current (Active) I

CC

200 A 3

Input Leakage I

LI

-1 +1 A

Wiper Resistance R

W

400 1000 ohms

Wiper Current I

W

1 mA

Input Logic 1 V

IH

0.7V

CC

V

CC

+0.5 V 2

Input Logic 0 V

IL

-0.5 0.3V

CC

V 2

Input Logic Levels A0, A1,

A2

Input Logic 1

Input Logic 0

0.7V

CC

-0.5

V

CC

+0.5

0.3V

CC

V 12

Input Current each I/O Pin 0.4<V

I/O

<0.9V

CC

-10 +10 A

Standby Current I

STBY

20 40 A 4

V

OL1

3 mA sink

current

0.0 0.4 V Low Level Output Voltage

V

OL2

6 mA sink

current

0.0 0.6 V

I/O Capacitance C

I/0

10 pF

Pulse Width of Spikes

which must be suppressed

by the input filter

t

SP

Fast Mode 0 50 ns

DS1803

7 of 11

ANALOG RESISTOR CHARACTERISTICS (-40C to +85C;V

CC

=2.7V to 5.5V)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

End-to-End Resistor Tolerance -20 +20 % 17

Absolute Linearity

0.75

LSB

13

Relative Linearity

0.3

LSB

14

-3 dB Cutoff Frequency f

CUTOFF

Hz 11

Temperature Coefficient 750 ppm/C

Capacitance C

I

5

pF

AC ELECTRICAL CHARACTERISTICS (-40C to +85C;V

CC

=2.7V to 5.5V)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

SCL Clock Frequency f

SCL

0

0

400

100

kHz

15

16

Bus Free Time Between

STOP and START Condition

t

BUF

1.3

4.7

s

15

16

Hold Time (Repeated)

START Condition

t

HD:STA

0.6

4.0

s 5

Low Period of SCL Clock t

LOW

1.3

4.7

s

High Period of SCL Clock t

HIGH

0.6

4.0

s

Data Hold Time t

HD :DAT

0

0

0.9 s 6,7

Data Setup Time t

SU :DAT

100

250

ns 8

Rise Time of both SDA and

SCL Signals

t

R

20+1C

B

300

1000

ns 9

Fall Time of both SDA and

SCL Signals

t

F

20+1C

B

300

300

ns 9

Setup Time for STOP

Condition

t

SU:STO

0.6

4.0

s

Capacitive Load for each Bus

Line

C

B

400 pF 9

NOTES:

1. All voltages are referenced to ground. Currents flowing into device pins are positive. Currents out of

the device pins are negative.

2. I/O pins of fast mode devices will not obstruct SDA and SCL even if V

CC

is switched off.

3. I

CC

specified with SDA pin open, SCL = 400 kHz clock rate.

4. I

STBY

specified with V

CC

at 5.0V and SDA, SCL = 5.0V.

DS1803

8 of 11

5. After this period, the first clock pulse is generated.

6. A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the

V

IHMIN

of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

7. The maximum t

HD:DAT

has only to be met if the device does not stretch the LOW period (t

LOW

) of the

SCL signal.

8. A fast mode device can be used in a standard mode system, but the requirement t

SU:DAT

> 250 ns must

then be met. This will automatically be the case if the device does not stretch the LOW period of the

SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next

data bit to the SDA line t

RMAX

+ t

SU:DAT

= 1000 + 250=1250 ns before the SCL line is released.

9. C

B

- total capacitance of one bus line in picofarads, timing referenced to (0.9)(V

CC

) and (0.1)(V

CC

).

10. Typical values are for t

A

= 25C and nominal supply voltage.

11. -3 dB cutoff frequency characteristics for the DS1803 depend on potentiometer total resistance:

DS1803-010; 1 MHz, DS1803-50; 200 kHz, DS1803-100; 100 kHz.

12. Address Inputs, A0, A1, and A2, should be tied to either V

CC

or GND depending on the desired

address selections.

13. Absolute linearity is used to determine wiper voltage versus expected voltage as determined by wiper

position. Device test limits are 1.6 LSB.

14. Relative linearity is used to determine the change in voltage between successive tap positions. Device

test limits 0.5 LSB.

15. Fast mode.

16. Standard mode.

17. Valid at 25C only.

DS1803

9 of 11

DS1803 BLOCK DIAGRAM Figure 1

2WIRE DATA TRANSFER OVERVIEW Figure 2

DS1803

10 of 11

CONTROL BYTE Figure 3

2WIRE READ PROTOCOL Figure 4

2WIRE WRITE PROTOCOL Figure 5

Write Pot-0

DS1803

11 of 11

TIMING DIAGRAM Figure 6

DS1803 ORDERING INFORMATION

ORDERING

NUMBER

PACKAGE

OPERATING

TEMPERATURE

VERSION

DS18030-010 16L DIP -40C TO +85C 10 k

DS18030-050 16L DIP -40C TO +85C 50 k

DS18030-100 16L DIP -40C TO +85C 100 k

DS1803E-010 14L TSSOP (173 MIL) -40C TO +85C 10 k

DS1803E-050 14L TSSOP (173 MIL) -40C TO +85C 50 k

DS1803E-100 14L TSSOP (173 MIL) -40C TO +85C 100 k

DS1803Z-010 16L SOIC (150 MIL) -40C TO +85C 10 k

DS1803Z-050 16L SOIC (150 MIL) -40C TO +85C 50 k

DS1803Z-100 16L SOIC (150 MIL) -40C TO +85C 100 k

DS1803E-010+ 14L TSSOP (173 MIL) LEAD FREE -40C TO +85C 10 k

DS1803E-50+ 14L TSSOP (173 MIL) LEAD FREE -40C TO +85C 50 k

DS1803E-100+ 14L TSSOP (173 MIL) LEAD FREE -40C TO +85C 100 k

DS1803E-010+T&R

14L TSSOP (173 MIL) LEAD FREE

T&R

-40C TO +85C 10 k

DS1803E-50+T&R

14L TSSOP (173 MIL) LEAD FREE

T&R

-40C TO +85C 50 k

DS1803Z-010+ 16L SOIC (150 MIL) LEAD FREE -40C TO +85C 10 k

DS1803Z-050+ 16L SOIC (150 MIL) LEAD FREE -40C TO +85C 50 k

DS1803Z-100+ 16L SOIC (150 MIL) LEAD FREE -40C TO +85C 100 k

DS1803Z-010+T&R

16L SOIC (150 MIL) LEAD FREE

T&R

-40C TO +85C 10 k

DS1803Z-050+T&R

16L SOIC (150 MIL) LEAD FREE

T&R

-40C TO +85C 50 k

DS1803Z-100+T&R

16L SOIC (150 MIL) LEAD FREE

T&R

-40C TO +85C 100 k

DS1803-100+T&R 16L DIP T&R -40C TO +85C 100 k

DS1803E-10/T&R 14L TSSOP (173 MIL) T&R -40C TO +85C 10 k

DS1803E-50/T&R 14L TSSOP (173 MIL) T&R -40C TO +85C 50 k

DS1803E-100/T&R 14L TSSOP (173 MIL) T&R -40C TO +85C 100 k

DS1803Z-010/T&R 16L SOIC (150 MIL) T&R -40C TO +85C 10 k

DS1803Z-050/T&R 16L SOIC (150 MIL) T&R -40C TO +85C 50 k

DS1803Z-100/T&R 16L SOIC (150 MIL) T&R -40C TO +85C 100 k

Potrebbero piacerti anche

- DS1624Documento17 pagineDS1624superpuma86Nessuna valutazione finora

- DS1624Documento15 pagineDS1624jnax101Nessuna valutazione finora

- DS1801 Dual Audio Taper Potentiometer: Features Pin AssignmentDocumento10 pagineDS1801 Dual Audio Taper Potentiometer: Features Pin AssignmentnicolaunmNessuna valutazione finora

- Ntroduction: Real Time Clock Serial Interface I/ODocumento17 pagineNtroduction: Real Time Clock Serial Interface I/ORahul SarangleNessuna valutazione finora

- DS1307 64 X 8 Serial Real-Time Clock: FeaturesDocumento8 pagineDS1307 64 X 8 Serial Real-Time Clock: FeaturesCarlos ArangurenNessuna valutazione finora

- Dual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationDocumento12 pagineDual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationManuel NolascoNessuna valutazione finora

- 512 Kbit Serial I C Bus EEPROM: DescriptionDocumento19 pagine512 Kbit Serial I C Bus EEPROM: DescriptionJavier MainarNessuna valutazione finora

- Interfacing The DS1307 With An 8051-Compatible MicrocontrollerDocumento20 pagineInterfacing The DS1307 With An 8051-Compatible MicrocontrollerHUNGDTK37Nessuna valutazione finora

- DS1307Documento13 pagineDS1307Ezaú TalamantesNessuna valutazione finora

- DS1624 Digital Thermometer and Memory: Features Pin AssignmentDocumento16 pagineDS1624 Digital Thermometer and Memory: Features Pin AssignmentJhónatan JuárezNessuna valutazione finora

- PCF8582C-2: 1. DescriptionDocumento21 paginePCF8582C-2: 1. DescriptionroozbehxoxNessuna valutazione finora

- 24C02Documento27 pagine24C02Biswajit SarkarNessuna valutazione finora

- CD 00003131Documento24 pagineCD 000031314131etasNessuna valutazione finora

- LS7366 PulseCounter PDFDocumento10 pagineLS7366 PulseCounter PDFJoan WascNessuna valutazione finora

- EDN Design Ideas 1998Documento166 pagineEDN Design Ideas 1998chag1956100% (4)

- MAX232&RS232Documento6 pagineMAX232&RS232api-19786583Nessuna valutazione finora

- 16K 1.8V I C Serial EEPROM: FeaturesDocumento12 pagine16K 1.8V I C Serial EEPROM: FeaturesKrzysztof BondkaNessuna valutazione finora

- Interfacing The DS1307/1308 With An 8051-Compatible MicrocontrollerDocumento23 pagineInterfacing The DS1307/1308 With An 8051-Compatible Microcontrollernik_n_89100% (2)

- 09 - I2C Serial CommunicationsmDocumento10 pagine09 - I2C Serial CommunicationsmSorabh DungNessuna valutazione finora

- Data SheetDocumento18 pagineData SheetJonas AldaoNessuna valutazione finora

- Hi-fi stereo audio processor I2C-bus specDocumento24 pagineHi-fi stereo audio processor I2C-bus specAriel NavarreteNessuna valutazione finora

- Presentation PDFDocumento17 paginePresentation PDFvinodNessuna valutazione finora

- MC Unit 4Documento42 pagineMC Unit 4Kalai VaniNessuna valutazione finora

- 8086 Pin ConfigurationDocumento83 pagine8086 Pin ConfigurationVenkata Krishnakanth ParuchuriNessuna valutazione finora

- 24C02-8 EepromDocumento16 pagine24C02-8 EepromJesus Almanzar SantosNessuna valutazione finora

- Good Data SheetDocumento20 pagineGood Data SheetNipuna Thushara WijesekaraNessuna valutazione finora

- 24 LC 32Documento14 pagine24 LC 32Shuchi Raju AgrawalNessuna valutazione finora

- Unit 2-3Documento38 pagineUnit 2-3vidhya sNessuna valutazione finora

- Inter Integrated CircuitDocumento6 pagineInter Integrated CircuitkamelNessuna valutazione finora

- MK41T56 MKI41T56: 512 Bit (64b x8) Serial Access TIMEKEEPER SramDocumento16 pagineMK41T56 MKI41T56: 512 Bit (64b x8) Serial Access TIMEKEEPER SramzdravkorrNessuna valutazione finora

- ANALOG TO DIGITAL AND DIGITAL TO ANALOG INTERFACINGDocumento28 pagineANALOG TO DIGITAL AND DIGITAL TO ANALOG INTERFACINGsatyanarayana12Nessuna valutazione finora

- I2C Bus Overview - The Inter-Integrated Circuit Communication ProtocolDocumento19 pagineI2C Bus Overview - The Inter-Integrated Circuit Communication ProtocolMohamed Ali100% (3)

- Remote Controlled Digital Audio Processor - Full Project AvailableDocumento3 pagineRemote Controlled Digital Audio Processor - Full Project AvailableK Raja SekarNessuna valutazione finora

- RF-Based Multiple Device Control Using MicrocontrollerDocumento7 pagineRF-Based Multiple Device Control Using Microcontrollermv mvNessuna valutazione finora

- The I C-Bus Specification: 6 Bit TransferDocumento54 pagineThe I C-Bus Specification: 6 Bit Transferprasanth_vedanthamNessuna valutazione finora

- ST24 25C04, ST24 25W04Documento16 pagineST24 25C04, ST24 25W04Zoran KovacevicNessuna valutazione finora

- DS1302 Real-Time Clock Chip with 31-Byte RAMDocumento16 pagineDS1302 Real-Time Clock Chip with 31-Byte RAMJuan Isaac Rodriquez MaldonadoNessuna valutazione finora

- Data Sheet: ADJD-S311-CR999Documento20 pagineData Sheet: ADJD-S311-CR999Milo LatinoNessuna valutazione finora

- Quadrature To Rs232 CardDocumento8 pagineQuadrature To Rs232 Cardtomjordan12321Nessuna valutazione finora

- NXP I2Cbus Elements SASEDocumento79 pagineNXP I2Cbus Elements SASEPablo Cotan100% (2)

- DS1804Documento6 pagineDS1804jnax101Nessuna valutazione finora

- 24 LC 16 BDocumento12 pagine24 LC 16 BAnonymous UxrPsIVNessuna valutazione finora

- 24C64 BMDocumento10 pagine24C64 BMdonghungstbNessuna valutazione finora

- Advanced Microprocessors Pin DetailsDocumento39 pagineAdvanced Microprocessors Pin DetailsVinoda DhayanitheNessuna valutazione finora

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocumento13 pagine24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsJose Antonio Lopez JuradoNessuna valutazione finora

- An 124Documento4 pagineAn 124Ank Electro FuzzNessuna valutazione finora

- 24C02 24C04 24C08 24C16: Bookly MicroDocumento10 pagine24C02 24C04 24C08 24C16: Bookly MicroHùng Nguyễn VănNessuna valutazione finora

- DS1804 PDFDocumento10 pagineDS1804 PDFhelveciotfNessuna valutazione finora

- I2C Protocol Design For ReusabilityDocumento8 pagineI2C Protocol Design For ReusabilityAkshay KashyapNessuna valutazione finora

- Mp&i Course File - unit-IIIDocumento23 pagineMp&i Course File - unit-IIIvenkateshrachaNessuna valutazione finora

- DS1804Documento10 pagineDS1804Brzata PticaNessuna valutazione finora

- Embedded C Module 4Documento29 pagineEmbedded C Module 4Sampath ShettyNessuna valutazione finora

- Cat5113 DDocumento13 pagineCat5113 DVolkan YılmazNessuna valutazione finora

- 7 A H-Bridge for DC-Motor ApplicationsDocumento29 pagine7 A H-Bridge for DC-Motor ApplicationsJoão JoséNessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Nessuna valutazione finora

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Da EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Valutazione: 2.5 su 5 stelle2.5/5 (3)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDa EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsValutazione: 3 su 5 stelle3/5 (2)

- 9619 Sony KDL-22BX300 KDL-32BX300 Chassis AZ1-FK Televisor LCD Manual de ServicioDocumento32 pagine9619 Sony KDL-22BX300 KDL-32BX300 Chassis AZ1-FK Televisor LCD Manual de ServicioFavgFavgNessuna valutazione finora

- 5-Mode Preset EQ IC with Bass Boost & 3DDocumento5 pagine5-Mode Preset EQ IC with Bass Boost & 3DzektorNessuna valutazione finora

- Tpa 3113Documento33 pagineTpa 3113zektorNessuna valutazione finora

- TLC 5925Documento27 pagineTLC 5925zektorNessuna valutazione finora

- Rotel Ra-1000 SMDocumento12 pagineRotel Ra-1000 SMzektorNessuna valutazione finora

- Top242 250 9213Documento53 pagineTop242 250 9213zektor100% (1)

- Rotel RB-1090 Service ManualDocumento10 pagineRotel RB-1090 Service ManualzektorNessuna valutazione finora

- 2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio AmplifierDocumento4 pagine2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio Amplifiercris_powerNessuna valutazione finora

- BF245ADocumento8 pagineBF245Acreed1000Nessuna valutazione finora

- DAC08Documento20 pagineDAC08Severiano Jaramillo QuintanarNessuna valutazione finora

- FSQ311Documento24 pagineFSQ311zektorNessuna valutazione finora

- TO-220 Plastic-Encapsulate Transistors: FeaturesDocumento1 paginaTO-220 Plastic-Encapsulate Transistors: FeatureszektorNessuna valutazione finora

- 1N5817Documento3 pagine1N5817Gallego OrtizNessuna valutazione finora

- FSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocumento12 pagineFSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionJohan BeckersNessuna valutazione finora

- 2sb649a PDFDocumento9 pagine2sb649a PDFperro sNessuna valutazione finora

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocumento3 pagineSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationzektorNessuna valutazione finora

- 2N4036 2N4037 PNP Silicon Transistor DescriptionDocumento2 pagine2N4036 2N4037 PNP Silicon Transistor DescriptionzektorNessuna valutazione finora

- Bs 170Documento4 pagineBs 170zektorNessuna valutazione finora

- PT2258Documento15 paginePT2258zektor100% (1)

- 2 N 2219 ADocumento8 pagine2 N 2219 Aaaa55603Nessuna valutazione finora

- 2N3053 2N3053A Silicon NPN Transistors DescriptionDocumento2 pagine2N3053 2N3053A Silicon NPN Transistors DescriptionzektorNessuna valutazione finora

- Max 5492Documento8 pagineMax 5492zektorNessuna valutazione finora

- LCD AddressingDocumento10 pagineLCD AddressingzektorNessuna valutazione finora

- 2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio AmplifierDocumento4 pagine2sa1941 & 2SC5198 - 140V - 10a - 100W - Audio Amplifiercris_powerNessuna valutazione finora

- 2N3053 2N3053A Silicon NPN Transistors DescriptionDocumento2 pagine2N3053 2N3053A Silicon NPN Transistors DescriptionzektorNessuna valutazione finora

- 2N4036 2N4037 PNP Silicon Transistor DescriptionDocumento2 pagine2N4036 2N4037 PNP Silicon Transistor DescriptionzektorNessuna valutazione finora

- Power Integrations LNK304PNDocumento16 paginePower Integrations LNK304PNnicelio_alvesNessuna valutazione finora

- Old Company Name in Catalogs and Other DocumentsDocumento10 pagineOld Company Name in Catalogs and Other DocumentszektorNessuna valutazione finora

- PT 2256Documento4 paginePT 2256zektorNessuna valutazione finora

- Quiz UtpDocumento7 pagineQuiz UtplesterNessuna valutazione finora

- Private Security Industry ReportDocumento40 paginePrivate Security Industry ReportkarndeNessuna valutazione finora

- Paper 19 Revised PDFDocumento520 paginePaper 19 Revised PDFAmey Mehta100% (1)

- Unit 4: A World of Ideas: Learning CompassDocumento3 pagineUnit 4: A World of Ideas: Learning CompassRica Mae Lepiten MendiolaNessuna valutazione finora

- TROOP - of - District 2013 Scouting's Journey To ExcellenceDocumento2 pagineTROOP - of - District 2013 Scouting's Journey To ExcellenceAReliableSourceNessuna valutazione finora

- Manual de Motores Vol 4Documento75 pagineManual de Motores Vol 4Gabriel Piñon Conde100% (1)

- About Kia Motors Corporation: All-NewDocumento19 pagineAbout Kia Motors Corporation: All-NewWessam FathiNessuna valutazione finora

- Lesson 3 - Subtract Two 4-Digit Numbers - More Than One Exchange 2019Documento2 pagineLesson 3 - Subtract Two 4-Digit Numbers - More Than One Exchange 2019mNessuna valutazione finora

- Portfolio Management Banking SectorDocumento133 paginePortfolio Management Banking SectorNitinAgnihotri100% (1)

- Cough: by Dr. Meghana Patil (Intern Batch 2016)Documento24 pagineCough: by Dr. Meghana Patil (Intern Batch 2016)Meghana PatilNessuna valutazione finora

- Module 1 (Social Innovation)Documento7 pagineModule 1 (Social Innovation)Marinette Medrano50% (2)

- Y-Site Drug Compatibility TableDocumento6 pagineY-Site Drug Compatibility TableArvenaa SubramaniamNessuna valutazione finora

- IEEE Registration StuffDocumento11 pagineIEEE Registration StuffsegeluluNessuna valutazione finora

- The Mpeg Dash StandardDocumento6 pagineThe Mpeg Dash Standard9716755397Nessuna valutazione finora

- Caterpillar Cat 330L EXCAVATOR (Prefix 8FK) Service Repair Manual (8FK00001 and Up)Documento27 pagineCaterpillar Cat 330L EXCAVATOR (Prefix 8FK) Service Repair Manual (8FK00001 and Up)kfm8seuuduNessuna valutazione finora

- A Study of Arcing Fault in The Low-Voltage Electrical InstallationDocumento11 pagineA Study of Arcing Fault in The Low-Voltage Electrical Installationaddin100% (1)

- Optimization TheoryDocumento18 pagineOptimization TheoryDivine Ada PicarNessuna valutazione finora

- Dhilshahilan Rajaratnam: Work ExperienceDocumento5 pagineDhilshahilan Rajaratnam: Work ExperienceShazard ShortyNessuna valutazione finora

- OspndDocumento97 pagineOspndhoangdo11122002Nessuna valutazione finora

- Emmanuel James Oteng, F. Inst. L. Ex. Legal Executive LawyerDocumento3 pagineEmmanuel James Oteng, F. Inst. L. Ex. Legal Executive Lawyeremmanuel otengNessuna valutazione finora

- Error 500 Unknown Column 'A.note' in 'Field List' - Joomla! Forum - Community, Help and SupportDocumento1 paginaError 500 Unknown Column 'A.note' in 'Field List' - Joomla! Forum - Community, Help and Supportsmart.engineerNessuna valutazione finora

- Tutorial: Energy Profiles ManagerDocumento6 pagineTutorial: Energy Profiles ManagerDavid Yungan GonzalezNessuna valutazione finora

- Frito LaysDocumento6 pagineFrito LaysElcamino Torrez50% (2)

- Integrated Building Management Platform for Security, Maintenance and Energy EfficiencyDocumento8 pagineIntegrated Building Management Platform for Security, Maintenance and Energy EfficiencyRajesh RajendranNessuna valutazione finora

- Deploy A REST API Using Serverless, Express and Node - JsDocumento13 pagineDeploy A REST API Using Serverless, Express and Node - JszaninnNessuna valutazione finora

- Climate Smart Agriculture Manual FINAL 2 2 Sent in Sierra Leones PDFDocumento201 pagineClimate Smart Agriculture Manual FINAL 2 2 Sent in Sierra Leones PDFKarthikNessuna valutazione finora

- Jan 2023 CL1Documento9 pagineJan 2023 CL1loai allam100% (2)

- Dimetra Tetra System White PaperDocumento6 pagineDimetra Tetra System White PapermosaababbasNessuna valutazione finora

- Solar Winds OrionAPM DatasheetDocumento4 pagineSolar Winds OrionAPM DatasheetArun J D'SouzaNessuna valutazione finora

- Task Based Risk Assesment FormDocumento2 pagineTask Based Risk Assesment FormKolluri SrinivasNessuna valutazione finora