Documenti di Didattica

Documenti di Professioni

Documenti di Cultura

Layout Manual

Caricato da

karnika143Titolo originale

Copyright

Formati disponibili

Condividi questo documento

Condividi o incorpora il documento

Hai trovato utile questo documento?

Questo contenuto è inappropriato?

Segnala questo documentoCopyright:

Formati disponibili

Layout Manual

Caricato da

karnika143Copyright:

Formati disponibili

Steps for CMOS Inverter layout design:-

1. Login to Xmanager3

2. Create a directory of layout by following these steps

[your name@mentor ~] $ cd work

[your name@mentor work] $ mkdir layout

[your name@mentor work] $ csh

[your name@mentor work] $ source homesoftwarecshrcams!""#$cshrc

[your name@mentor work] $ adk%ic

&hen '() is open

3. *pen a new layout

4. +ut name of of layout design,- Like inverter1

+rocess,-$A!"te#$nology"i#"pro#ess"a%i&'

.ules,- $A!"te#$nology"i#"pro#ess"a%i&'.rules

+ress O!

'. Layout editor window will appear on your screen

(. /elect /etup0'rid

1nd /et the grid coordinates accordingly

). 'o to )C palettes on right-bottom toolbar

/elect *dit+,-. 2for ruler selection it will help measuring dimensions of

layout3

/. 4ow from layer palette choose different layers$ 1n e5ample of first layer design is

here same step is following to drag the different layers with different dimensions

and positions$

/elect CO01AC121O2AC1I3* with path width of 2.&

4. Length of contact to acti6e !7 i$e$ /i8e of !9!

1&. /elect edit and flatten this block$ )f you want you can use this option at each stage

after design a block$

11. 4ow select :;&1L< of si8e =9=

12. Copy both block by selecting and paste by press C at a distance of >$"

13. ?raw AC1I3* block of si8e 1/54 and copy this block because these steps are

common for both pmos and nmos

14. 4ow for 4mos 2the lower one 3

?raw 0267-S2S*7*C1 of si8e 22513 and 628*77 of si8e 2(51)

1'. 4ow for +mos 2the upper one 3

?raw 6267-S2S*7*C1 of si8e 22513 and 628*77 of si8e 3&521

1(. 4ow draw a 6O79 link of width !$" between the pmos and nmos of same

distance i$e$ <$" from acti6e block

1). 4ow draw a M*1A721 link of width 3$" for right side for connecting acti6e of

both pmos and nmos

1/. 4ow draw a M*1A721 block of si8e <"9= for making output contacts and in the

same way for input draw block of <=9= according to figure

14. 4ow draw a M*1A721 block of width of 1&.& abo6e the +:*/ and below the

4:*/

2&. 4ow draw a M*1A722 block of si8e =9= according the figure 2> places37upper

and lower metal%! block should be abo6e and below of pmos and nmos

21. 4ow draw a M*1A721 block of width 3$" for connecting acti6e and metal%! of

pmos and nmos

22. 4ow draw a 6O79 block of si8e=9= at the input side

23. 4ow draw a 3IA block of si8e !9! for connecting metal%< and metal%!

according the figure 2> places3

24. 4ow draw a CO01AC121O26O79 block of si8e !9! for connecting metal%<

and poly according the figure 2< place3 at the input side

2'. press space on screen and type n:# for n-well contact and making contact of n-

well and metal%<$)n the same way type p:# for p-well contact$

2(. 'o to right bottom side IC26alettes select A!2*I1 and select M;6ort

for port declaration$ 1nd for 6iew port name select 6ort 1e<t

+ort type direction

@dd +ower )n

'nd +ower )n

@in /ignal )n

6out /ignal *ut

2). 'o to &ools0Calibre0.un ?.C 2Aor ?esign .ule Checking3

2/. Cancel .unset Aile +ath $ click on the rules and pro6ide the following path for

rules 2you can also browse by folder3

"$o%e"soft:are"=O-0,9"ad;321"te#$nology"i#"pro#ess"a%i&'.rules

24. ,un ,C

)n the abo6e e5ample we find no errors$ )f any error is found in layout according to

design rule you can click on that and correct the layout accordingly7 then sa6e the layout

and check for ?.C again until it found no errors$

3&. 1ools+Cali>re+,un 6*?

31. /et the rules

"$o%e"soft:are"=O-0,9"ad;321"te#$nology"i#"pro#ess"a%i&'.rules

32. *utput set to 7A9O-1 according to figure and finally ,un 6*?

33. *utput set to 7A9O-1 according to figure and finally ,un 6*?

1 +;X file is generated as shown in figure

34. &his is a pre generated file which used for arranging the position of @?? '4?

)4 and *(&

99999999999999999999999999999999999999

9 Aile, in6erter$pe5$netlist$sp

9 Created, Ari :ar <B <=,!",>! !"<!

9 +rogram CCalibre 5.CC

9 @ersion C6!"<"$<%3"$!>C

99999999999999999999999999999999999999

$L)D homesoftwareA*(4?.Eadk3%<technologyicmodelsami"=$mod

$temp !# 9 /et *perating temperature to !# degree celcius

$global @?? '4?

@A*.C;%%@?? @?? '4? dc =

$C*44;C& '4? "

$option post

99999999999999999999999999999999999999

9)4CL(?; C1L)D.; 4;&L)/&

99999999999999999999999999999999999999

$include Cin6erter$pe5$netlistC

99999999999999999999999999999999999999

91?? &*+ L;@;L /):(L1&)*4 4;&L)/&

99999999999999999999999999999999999999

X< '4? )4 @?? *(& )4@;.&;.

99999999999999999999999999999999999999

9 )4+(& /&):(L(/

99999999999999999999999999999999999999

@< )4 '4? pulse2" = !="n <n <n !="n =""n3

99999999999999999999999999999999999999

9 141LE/)/

99999999999999999999999999999999999999

$tran <"ns <"""ns

3'. .un the command on linu5 window

gedit in6erter<!$pe5$netlist

2put your design name in place of in6erter<!3

&he below screen will appear7 change the location in this file according to abo6e

pre-generated file$ 1nd for transient analysis add in this file

@< )4 '4? pulse2" = !="n <n <n !="n =""n3

3(. .un the command

g6im in6erter<!$pe5$netlist$sp

3). .un the command

eldo inverter12.pe<.netlist.sp

1nd gi6e command e@:ave in linu5 window

3/. +lot the @)4 and @*(&

&his process is of transient analysis$ Eou can do other analysis by gi6ing other inputs$

;5it the tool after completing the process$

Potrebbero piacerti anche

- Shoe Dog: A Memoir by the Creator of NikeDa EverandShoe Dog: A Memoir by the Creator of NikeValutazione: 4.5 su 5 stelle4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDa EverandGrit: The Power of Passion and PerseveranceValutazione: 4 su 5 stelle4/5 (587)

- Layout ManualDocumento25 pagineLayout Manualkarnika143Nessuna valutazione finora

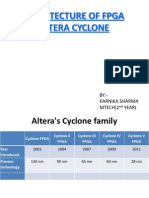

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Documento29 pagineArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- Vlsi TestingDocumento79 pagineVlsi Testingkarnika143Nessuna valutazione finora

- FPGADocumento27 pagineFPGAkarnika143Nessuna valutazione finora

- FPGADocumento27 pagineFPGAkarnika143Nessuna valutazione finora

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDa EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceValutazione: 4 su 5 stelle4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Da EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Valutazione: 4 su 5 stelle4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDa EverandThe Little Book of Hygge: Danish Secrets to Happy LivingValutazione: 3.5 su 5 stelle3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDa EverandOn Fire: The (Burning) Case for a Green New DealValutazione: 4 su 5 stelle4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDa EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeValutazione: 4 su 5 stelle4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDa EverandNever Split the Difference: Negotiating As If Your Life Depended On ItValutazione: 4.5 su 5 stelle4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDa EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureValutazione: 4.5 su 5 stelle4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDa EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryValutazione: 3.5 su 5 stelle3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDa EverandThe Emperor of All Maladies: A Biography of CancerValutazione: 4.5 su 5 stelle4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDa EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreValutazione: 4 su 5 stelle4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDa EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyValutazione: 3.5 su 5 stelle3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDa EverandTeam of Rivals: The Political Genius of Abraham LincolnValutazione: 4.5 su 5 stelle4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDa EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersValutazione: 4.5 su 5 stelle4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDa EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaValutazione: 4.5 su 5 stelle4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDa EverandThe Unwinding: An Inner History of the New AmericaValutazione: 4 su 5 stelle4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Da EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Valutazione: 4.5 su 5 stelle4.5/5 (119)

- Her Body and Other Parties: StoriesDa EverandHer Body and Other Parties: StoriesValutazione: 4 su 5 stelle4/5 (821)

- Laser Module 5Documento25 pagineLaser Module 5Luis Enrique B GNessuna valutazione finora

- ECE Laws and Ethics NotesDocumento29 pagineECE Laws and Ethics Notesmars100% (1)

- Daftar PustakaDocumento3 pagineDaftar PustakaNurha ZizahNessuna valutazione finora

- Confirmation Form: Pillar Regional Conference (NCR)Documento1 paginaConfirmation Form: Pillar Regional Conference (NCR)Llano Multi-Purpose CooperativeNessuna valutazione finora

- U1L2 - Definitions of 21st Century LiteraciesDocumento19 pagineU1L2 - Definitions of 21st Century LiteraciesJerry Glenn Latorre CastilloNessuna valutazione finora

- G String v5 User ManualDocumento53 pagineG String v5 User ManualFarid MawardiNessuna valutazione finora

- Timeline of Internet in The PhilippinesDocumento29 pagineTimeline of Internet in The PhilippinesJhayson Joeshua Rubio100% (1)

- READING 4.1 - Language and The Perception of Space, Motion, and TimeDocumento10 pagineREADING 4.1 - Language and The Perception of Space, Motion, and TimeBan MaiNessuna valutazione finora

- CommunicationDocumento5 pagineCommunicationRyan TomeldenNessuna valutazione finora

- 7 C's of Business LetterDocumento3 pagine7 C's of Business LetterGladys Forte100% (2)

- REFLEKSI KASUS PLASENTADocumento48 pagineREFLEKSI KASUS PLASENTAImelda AritonangNessuna valutazione finora

- Main Sulci & Fissures: Cerebral FissureDocumento17 pagineMain Sulci & Fissures: Cerebral FissureNagbhushan BmNessuna valutazione finora

- 199-Article Text-434-1-10-20200626Documento11 pagine199-Article Text-434-1-10-20200626ryan renaldiNessuna valutazione finora

- UN Habitat UPCL Myanmar TranslationDocumento254 pagineUN Habitat UPCL Myanmar TranslationzayyarNessuna valutazione finora

- 9-Lesson 5 Direct and Indirect SpeechDocumento8 pagine9-Lesson 5 Direct and Indirect Speechlaiwelyn100% (4)

- Shop SupervisionDocumento38 pagineShop SupervisionSakura Yuno Gozai80% (5)

- Lab 1 Handout Electrical MachinesDocumento23 pagineLab 1 Handout Electrical Machinesvishalsharma08Nessuna valutazione finora

- TSR Cyl Tilt Cab LD 110Documento2 pagineTSR Cyl Tilt Cab LD 110Ferry AndisNessuna valutazione finora

- HRM Assignment Final - Case StudyDocumento7 pagineHRM Assignment Final - Case StudyPulkit_Bansal_2818100% (3)

- Seminar - Review 2 FinalDocumento12 pagineSeminar - Review 2 FinalBhaskaruni Sai TarunNessuna valutazione finora

- DAFTAR PUSTAKA Generik vs Branded Drug ReferencesDocumento4 pagineDAFTAR PUSTAKA Generik vs Branded Drug ReferencesRika MardiahNessuna valutazione finora

- 21st Century Literature Exam SpecsDocumento2 pagine21st Century Literature Exam SpecsRachel Anne Valois LptNessuna valutazione finora

- Be3000 Manual 2016Documento77 pagineBe3000 Manual 2016Itzel JuárezNessuna valutazione finora

- CorentineDocumento559 pagineCorentinejames b willardNessuna valutazione finora

- ISO 17000 2004 Terms & DefintionsDocumento6 pagineISO 17000 2004 Terms & DefintionsSelvaraj SimiyonNessuna valutazione finora

- ST326 - Irdap2021Documento5 pagineST326 - Irdap2021NgaNovaNessuna valutazione finora

- The Effects of Self-Esteem On Makeup InvolvementDocumento9 pagineThe Effects of Self-Esteem On Makeup InvolvementMichelle Nicole Tagupa SerranoNessuna valutazione finora

- Use DCP to Predict Soil Bearing CapacityDocumento11 pagineUse DCP to Predict Soil Bearing CapacitysarvaiyahimmatNessuna valutazione finora

- Timothy Prehn CV 021209Documento4 pagineTimothy Prehn CV 021209Jason GomezNessuna valutazione finora

- E 74 - 06 - For Force Measuring InstrumentsDocumento12 pagineE 74 - 06 - For Force Measuring InstrumentsSarvesh MishraNessuna valutazione finora